5

4

3

2

1

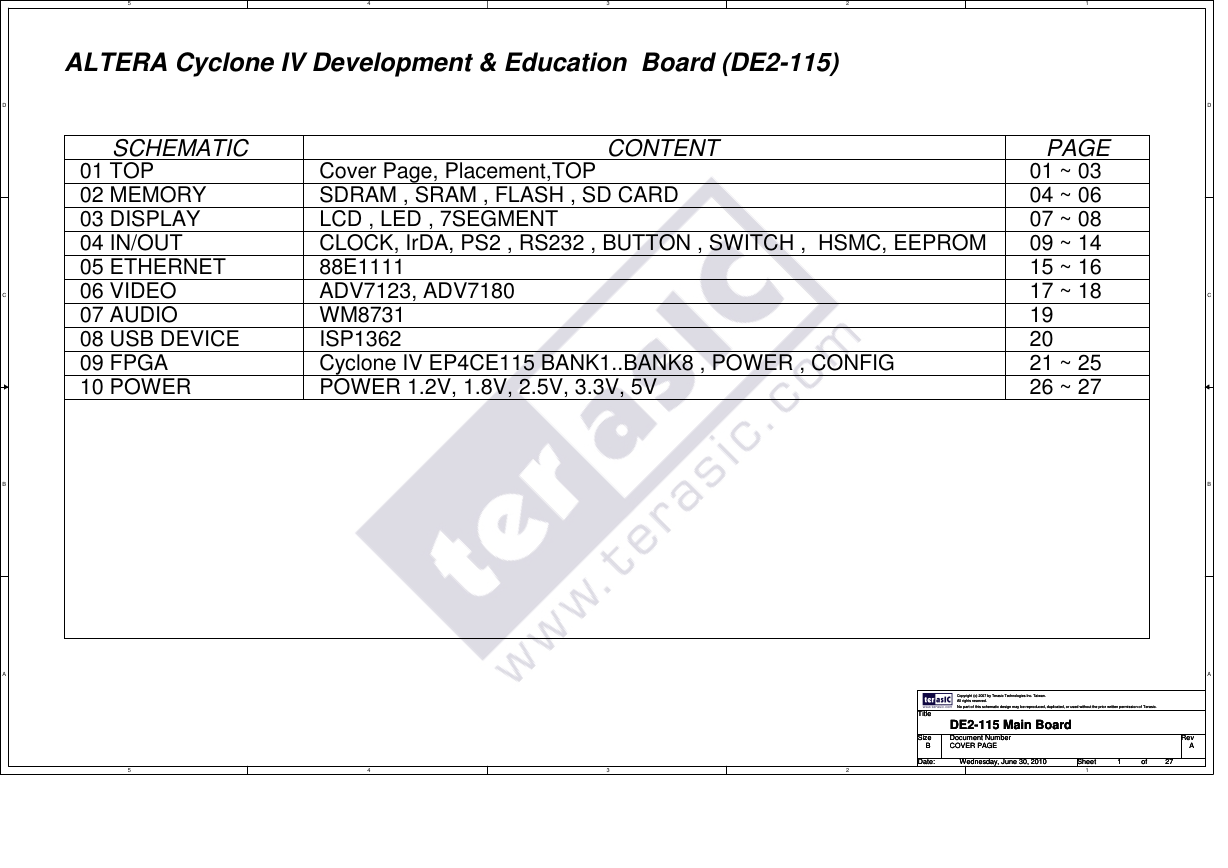

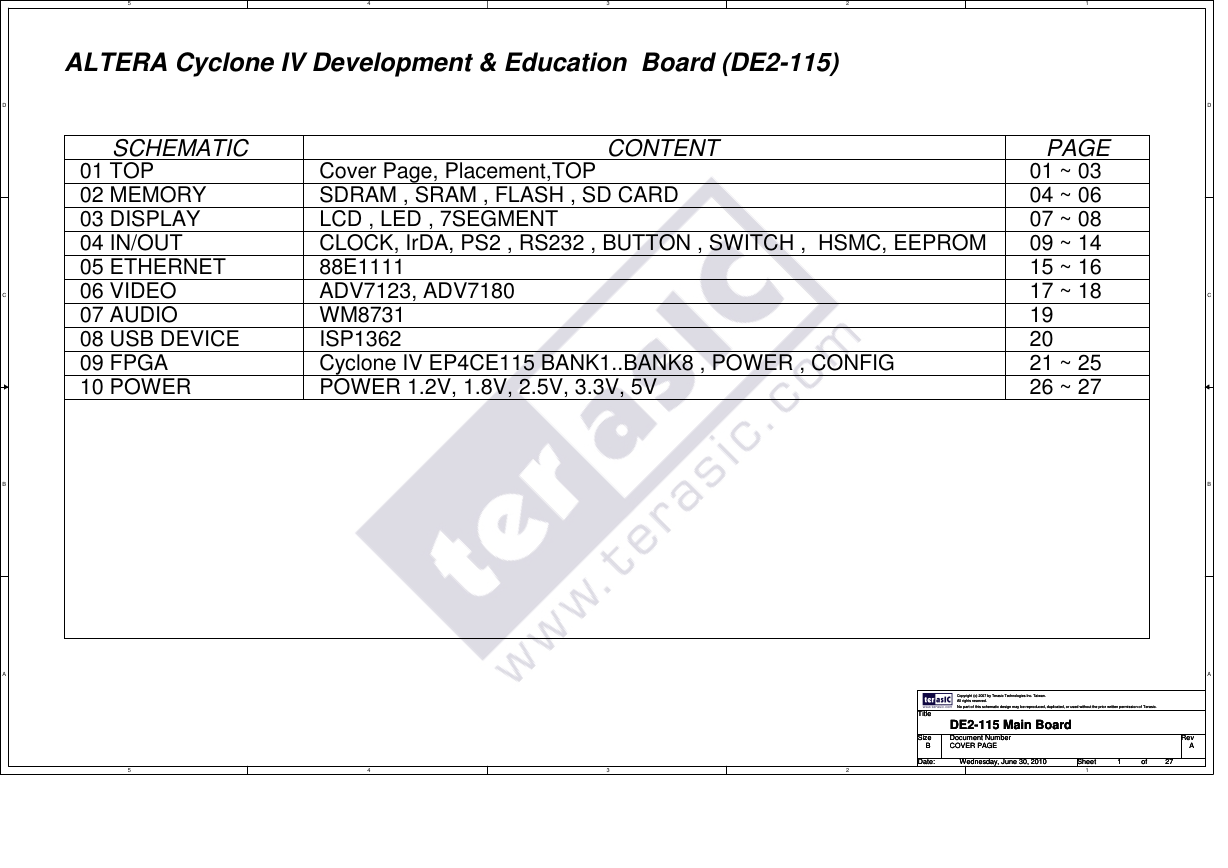

ALTERA Cyclone IV Development & Education Board (DE2-115)

SCHEMATIC

01 TOP

02 MEMORY

03 DISPLAY

04 IN/OUT

05 ETHERNET

06 VIDEO

07 AUDIO

08 USB DEVICE

09 FPGA

10 POWER

CONTENT

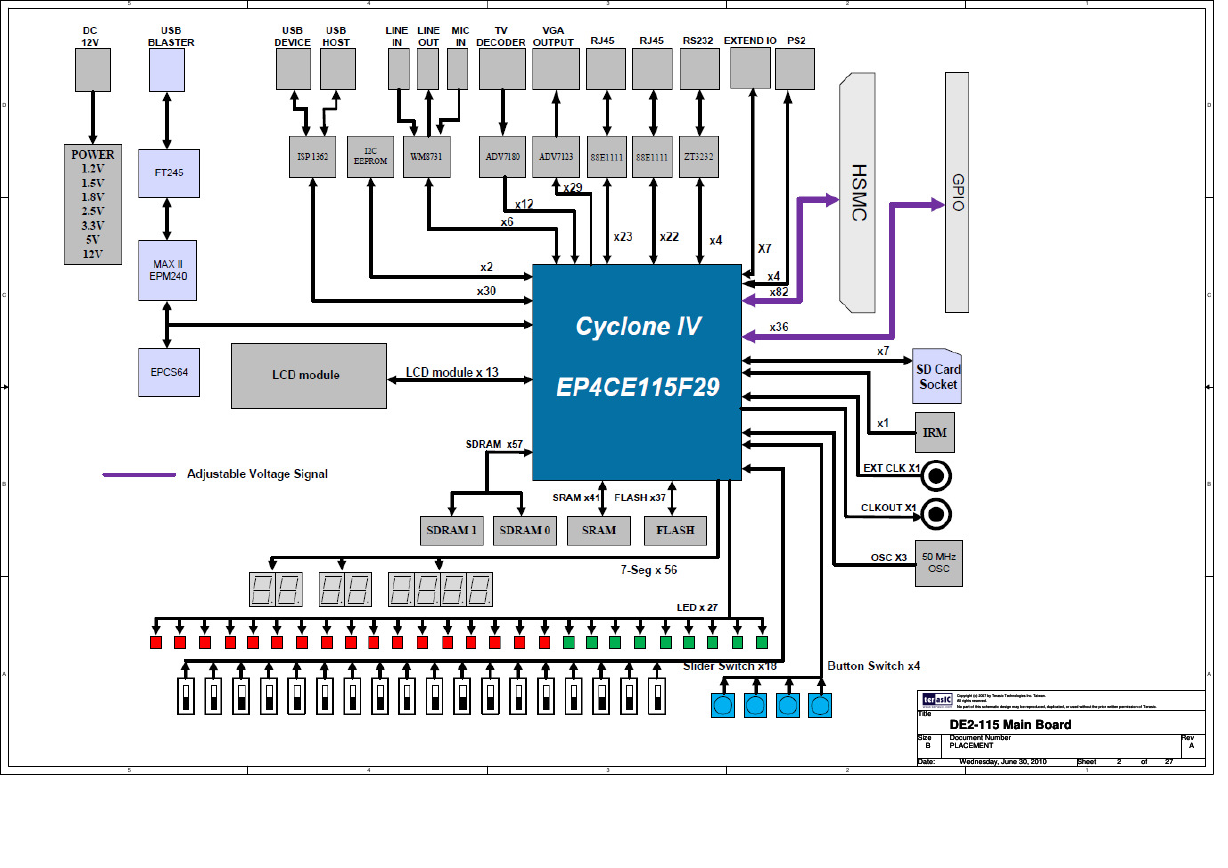

Cover Page, Placement,TOP

SDRAM , SRAM , FLASH , SD CARD

LCD , LED , 7SEGMENT

CLOCK, IrDA, PS2 , RS232 , BUTTON , SWITCH , HSMC, EEPROM

88E1111

ADV7123, ADV7180

WM8731

ISP1362

Cyclone IV EP4CE115 BANK1..BANK8 , POWER , CONFIG

POWER 1.2V, 1.8V, 2.5V, 3.3V, 5V

PAGE

01 ~ 03

04 ~ 06

07 ~ 08

09 ~ 14

15 ~ 16

17 ~ 18

19

20

21 ~ 25

26 ~ 27

D

C

B

A

D

C

B

A

5

4

3

2

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

Title

Title

Size

Size

Size

B

B

B

DE2-115 Main Board

DE2-115 Main Board

DE2-115 Main Board

Document Number

Document Number

Document Number

COVER PAGE

COVER PAGE

COVER PAGE

Rev

Rev

Rev

A

A

A

Date:

Date:

Date:

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Sheet

Sheet

Sheet

1

1

1

1

of

of

of

27

27

27

�

5

4

3

2

1

D

C

B

A

D

C

B

A

5

4

3

2

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

Title

Title

Size

Size

Size

B

B

B

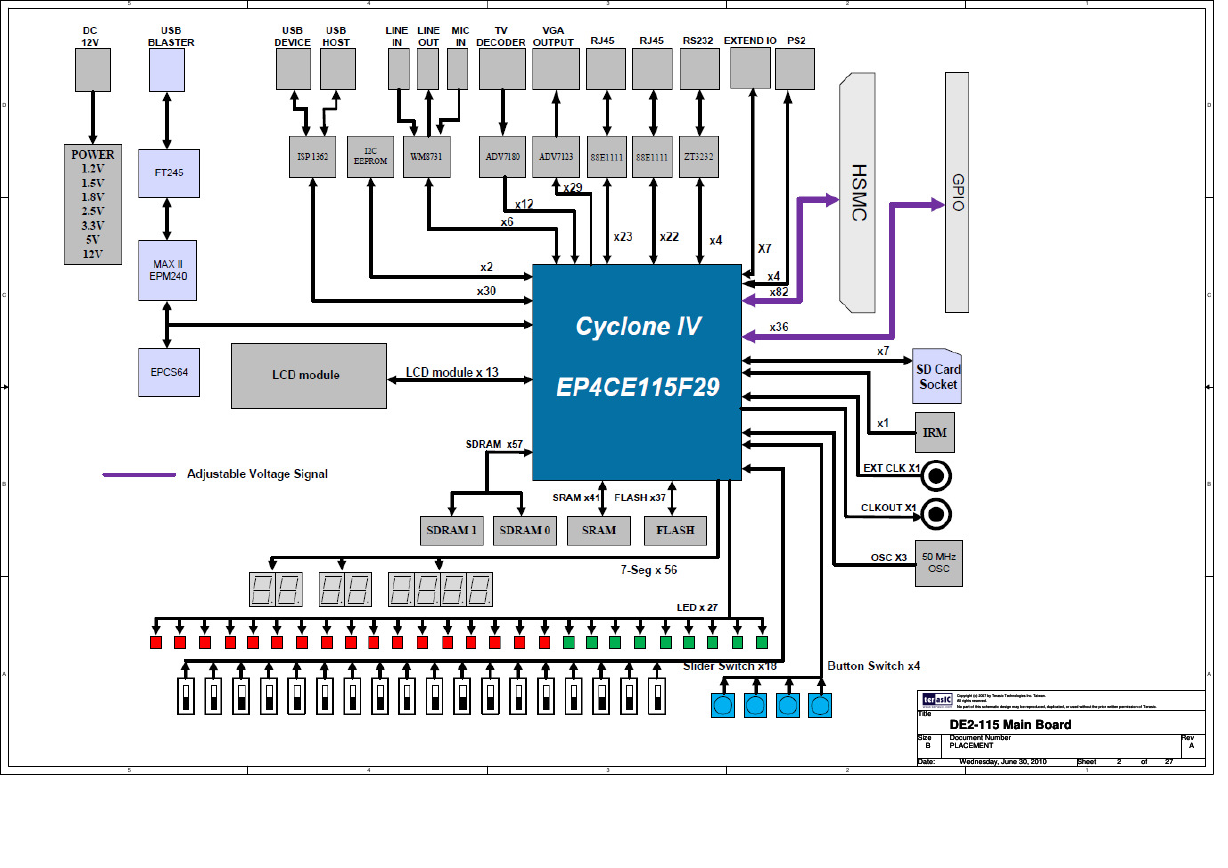

DE2-115 Main Board

DE2-115 Main Board

DE2-115 Main Board

Document Number

Document Number

Document Number

PLACEMENT

PLACEMENT

PLACEMENT

Rev

Rev

Rev

A

A

A

Date:

Date:

Date:

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Sheet

Sheet

Sheet

1

2

2

2

of

of

of

27

27

27

�

5

4

3

2

1

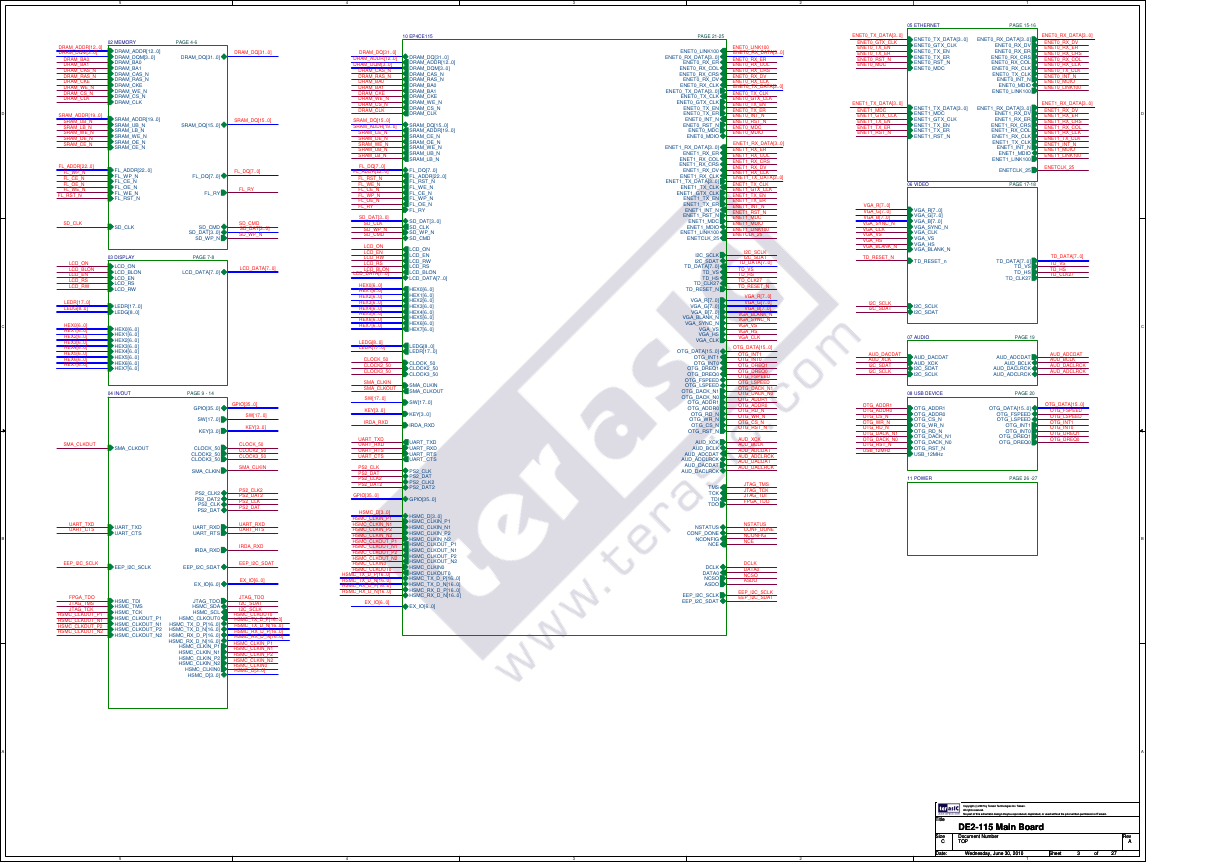

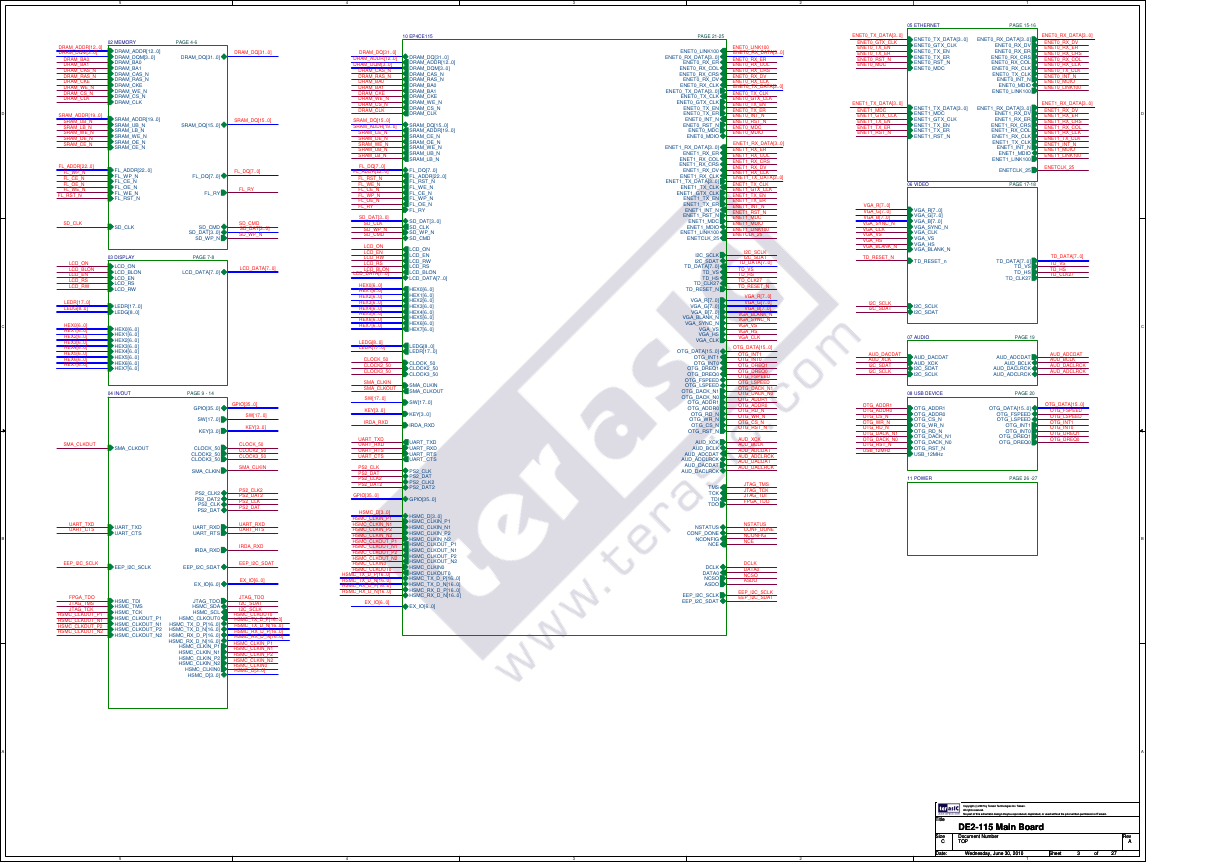

02 MEMORY

PAGE 4-6

10 EP4CE115

PAGE 21-25

DRAM_DQ[31..0]

DRAM_ADDR[12..0]

DRAM_DQM[3..0]

DRAM_CAS_N

DRAM_RAS_N

DRAM_BA0

DRAM_BA1

DRAM_CKE

DRAM_WE_N

DRAM_CS_N

DRAM_CLK

SRAM_DQ[15..0]

SRAM_ADDR[19..0]

SRAM_CE_N

SRAM_OE_N

SRAM_WE_N

SRAM_UB_N

SRAM_LB_N

FL_DQ[7..0]

FL_ADDR[22..0]

FL_RST_N

FL_WE_N

FL_CE_N

FL_WP_N

FL_OE_N

FL_RY

SD_DAT[3..0]

SD_CLK

SD_WP_N

SD_CMD

LCD_ON

LCD_EN

LCD_RW

LCD_RS

LCD_BLON

LCD_DATA[7..0]

HEX0[6..0]

HEX1[6..0]

HEX2[6..0]

HEX3[6..0]

HEX4[6..0]

HEX5[6..0]

HEX6[6..0]

HEX7[6..0]

LEDG[8..0]

LEDR[17..0]

CLOCK_50

CLOCK2_50

CLOCK3_50

SMA_CLKIN

SMA_CLKOUT

SW[17..0]

KEY[3..0]

IRDA_RXD

UART_TXD

UART_RXD

UART_RTS

UART_CTS

PS2_CLK

PS2_DAT

PS2_CLK2

PS2_DAT2

GPIO[35..0]

DRAM_DQ[31..0]

DRAM_ADDR[12..0]

DRAM_DQM[3..0]

DRAM_CAS_N

DRAM_RAS_N

DRAM_BA0

DRAM_BA1

DRAM_CKE

DRAM_WE_N

DRAM_CS_N

DRAM_CLK

SRAM_DQ[15..0]

SRAM_ADDR[19..0]

SRAM_CE_N

SRAM_OE_N

SRAM_WE_N

SRAM_UB_N

SRAM_LB_N

FL_DQ[7..0]

FL_ADDR[22..0]

FL_RST_N

FL_WE_N

FL_CE_N

FL_WP_N

FL_OE_N

FL_RY

SD_DAT[3..0]

SD_CLK

SD_WP_N

SD_CMD

LCD_ON

LCD_EN

LCD_RW

LCD_RS

LCD_BLON

LCD_DATA[7..0]

HEX0[6..0]

HEX1[6..0]

HEX2[6..0]

HEX3[6..0]

HEX4[6..0]

HEX5[6..0]

HEX6[6..0]

HEX7[6..0]

LEDG[8..0]

LEDR[17..0]

CLOCK_50

CLOCK2_50

CLOCK3_50

SMA_CLKIN

SMA_CLKOUT

SW[17..0]

KEY[3..0]

IRDA_RXD

UART_TXD

UART_RXD

UART_RTS

UART_CTS

PS2_CLK

PS2_DAT

PS2_CLK2

PS2_DAT2

GPIO[35..0]

HSMC_D[3..0]

HSMC_CLKIN_P1

HSMC_CLKIN_N1

HSMC_CLKIN_P2

HSMC_CLKIN_N2

HSMC_CLKOUT_P1

HSMC_CLKOUT_N1

HSMC_CLKOUT_P2

HSMC_CLKOUT_N2

HSMC_CLKIN0

HSMC_CLKOUT0

HSMC_TX_D_P[16..0]

HSMC_TX_D_N[16..0]

HSMC_RX_D_P[16..0]

HSMC_RX_D_N[16..0]

HSMC_D[3..0]

HSMC_CLKIN_P1

HSMC_CLKIN_N1

HSMC_CLKIN_P2

HSMC_CLKIN_N2

HSMC_CLKOUT_P1

HSMC_CLKOUT_N1

HSMC_CLKOUT_P2

HSMC_CLKOUT_N2

HSMC_CLKIN0

HSMC_CLKOUT0

HSMC_TX_D_P[16..0]

HSMC_TX_D_N[16..0]

HSMC_RX_D_P[16..0]

HSMC_RX_D_N[16..0]

EX_IO[6..0]

EX_IO[6..0]

DRAM_ADDR[12..0]

DRAM_DQM[3..0]

DRAM_BA0

DRAM_BA1

DRAM_CAS_N

DRAM_RAS_N

DRAM_CKE

DRAM_WE_N

DRAM_CS_N

DRAM_CLK

D

SRAM_ADDR[19..0]

SRAM_UB_N

SRAM_LB_N

SRAM_WE_N

SRAM_OE_N

SRAM_CE_N

FL_ADDR[22..0]

FL_WP_N

FL_CE_N

FL_OE_N

FL_WE_N

FL_RST_N

DRAM_ADDR[12..0]

DRAM_DQM[3..0]

DRAM_BA0

DRAM_BA1

DRAM_CAS_N

DRAM_RAS_N

DRAM_CKE

DRAM_WE_N

DRAM_CS_N

DRAM_CLK

SRAM_ADDR[19..0]

SRAM_UB_N

SRAM_LB_N

SRAM_WE_N

SRAM_OE_N

SRAM_CE_N

FL_ADDR[22..0]

FL_WP_N

FL_CE_N

FL_OE_N

FL_WE_N

FL_RST_N

DRAM_DQ[31..0]

DRAM_DQ[31..0]

SRAM_DQ[15..0]

SRAM_DQ[15..0]

FL_DQ[7..0]

FL_DQ[7..0]

FL_RY

FL_RY

SD_CLK

SD_CLK

SD_CMD

SD_DAT[3..0]

SD_WP_N

SD_CMD

SD_DAT[3..0]

SD_WP_N

03 DISPLAY

PAGE 7-8

LCD_DATA[7..0]

LCD_DATA[7..0]

LCD_ON

LCD_BLON

LCD_EN

LCD_RS

LCD_RW

LEDR[17..0]

LEDG[8..0]

HEX0[6..0]

HEX1[6..0]

HEX2[6..0]

HEX3[6..0]

HEX4[6..0]

HEX5[6..0]

HEX6[6..0]

HEX7[6..0]

LCD_ON

LCD_BLON

LCD_EN

LCD_RS

LCD_RW

LEDR[17..0]

LEDG[8..0]

HEX0[6..0]

HEX1[6..0]

HEX2[6..0]

HEX3[6..0]

HEX4[6..0]

HEX5[6..0]

HEX6[6..0]

HEX7[6..0]

04 IN/OUT

PAGE 9 - 14

SMA_CLKOUT

SMA_CLKOUT

UART_TXD

UART_CTS

UART_TXD

UART_CTS

GPIO[35..0]

SW[17..0]

KEY[3..0]

CLOCK_50

CLOCK2_50

CLOCK3_50

SMA_CLKIN

PS2_CLK2

PS2_DAT2

PS2_CLK

PS2_DAT

UART_RXD

UART_RTS

IRDA_RXD

GPIO[35..0]

SW[17..0]

KEY[3..0]

CLOCK_50

CLOCK2_50

CLOCK3_50

SMA_CLKIN

PS2_CLK2

PS2_DAT2

PS2_CLK

PS2_DAT

UART_RXD

UART_RTS

IRDA_RXD

EEP_I2C_SCLK

EEP_I2C_SCLK

EEP_I2C_SDAT

EEP_I2C_SDAT

FPGA_TDO

JTAG_TMS

JTAG_TCK

HSMC_CLKOUT_P1

HSMC_CLKOUT_N1

HSMC_CLKOUT_P2

HSMC_CLKOUT_N2

HSMC_TDI

HSMC_TMS

HSMC_TCK

HSMC_CLKOUT_P1

HSMC_CLKOUT_N1

HSMC_CLKOUT_P2

HSMC_CLKOUT_N2

EX_IO[6..0]

JTAG_TDO

HSMC_SDA

HSMC_SCL

HSMC_CLKOUT0

HSMC_TX_D_P[16..0]

HSMC_TX_D_N[16..0]

HSMC_RX_D_P[16..0]

HSMC_RX_D_N[16..0]

HSMC_CLKIN_P1

HSMC_CLKIN_N1

HSMC_CLKIN_P2

HSMC_CLKIN_N2

HSMC_CLKIN0

HSMC_D[3..0]

EX_IO[6..0]

JTAG_TDO

I2C_SDAT

I2C_SCLK

HSMC_CLKOUT0

HSMC_TX_D_P[16..0]

HSMC_TX_D_N[16..0]

HSMC_RX_D_P[16..0]

HSMC_RX_D_N[16..0]

HSMC_CLKIN_P1

HSMC_CLKIN_N1

HSMC_CLKIN_P2

HSMC_CLKIN_N2

HSMC_CLKIN0

HSMC_D[3..0]

C

B

A

ENET0_LINK100

ENET0_RX_DATA[3..0]

ENET0_RX_ER

ENET0_RX_COL

ENET0_RX_CRS

ENET0_RX_DV

ENET0_RX_CLK

ENET0_TX_DATA[3..0]

ENET0_TX_CLK

ENET0_GTX_CLK

ENET0_TX_EN

ENET0_TX_ER

ENET0_INT_N

ENET0_RST_N

ENET0_MDC

ENET0_MDIO

ENET1_RX_DATA[3..0]

ENET1_RX_ER

ENET1_RX_COL

ENET1_RX_CRS

ENET1_RX_DV

ENET1_RX_CLK

ENET1_TX_DATA[3..0]

ENET1_TX_CLK

ENET1_GTX_CLK

ENET1_TX_EN

ENET1_TX_ER

ENET1_INT_N

ENET1_RST_N

ENET1_MDC

ENET1_MDIO

ENET1_LINK100

ENETCLK_25

ENET0_LINK100

ENET0_RX_DATA[3..0]

ENET0_RX_ER

ENET0_RX_COL

ENET0_RX_CRS

ENET0_RX_DV

ENET0_RX_CLK

ENET0_TX_DATA[3..0]

ENET0_TX_CLK

ENET0_GTX_CLK

ENET0_TX_EN

ENET0_TX_ER

ENET0_INT_N

ENET0_RST_N

ENET0_MDC

ENET0_MDIO

ENET1_RX_DATA[3..0]

ENET1_RX_ER

ENET1_RX_COL

ENET1_RX_CRS

ENET1_RX_DV

ENET1_RX_CLK

ENET1_TX_DATA[3..0]

ENET1_TX_CLK

ENET1_GTX_CLK

ENET1_TX_EN

ENET1_TX_ER

ENET1_INT_N

ENET1_RST_N

ENET1_MDC

ENET1_MDIO

ENET1_LINK100

ENETCLK_25

I2C_SCLK

I2C_SDAT

TD_DATA[7..0]

TD_VS

TD_HS

TD_CLK27

TD_RESET_N

VGA_R[7..0]

VGA_G[7..0]

VGA_B[7..0]

VGA_BLANK_N

VGA_SYNC_N

VGA_VS

VGA_HS

VGA_CLK

OTG_DATA[15..0]

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

OTG_FSPEED

OTG_LSPEED

OTG_DACK_N1

OTG_DACK_N0

OTG_ADDR1

OTG_ADDR0

OTG_RD_N

OTG_WR_N

OTG_CS_N

OTG_RST_N

AUD_XCK

AUD_BCLK

AUD_ADCDAT

AUD_ADCLRCK

AUD_DACDAT

AUD_DACLRCK

TMS

TCK

TDI

TDO

NSTATUS

CONF_DONE

NCONFIG

NCE

I2C_SCLK

I2C_SDAT

TD_DATA[7..0]

TD_VS

TD_HS

TD_CLK27

TD_RESET_N

VGA_R[7..0]

VGA_G[7..0]

VGA_B[7..0]

VGA_BLANK_N

VGA_SYNC_N

VGA_VS

VGA_HS

VGA_CLK

OTG_DATA[15..0]

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

OTG_FSPEED

OTG_LSPEED

OTG_DACK_N1

OTG_DACK_N0

OTG_ADDR1

OTG_ADDR0

OTG_RD_N

OTG_WR_N

OTG_CS_N

OTG_RST_N

AUD_XCK

AUD_BCLK

AUD_ADCDAT

AUD_ADCLRCK

AUD_DACDAT

AUD_DACLRCK

JTAG_TMS

JTAG_TCK

JTAG_TDI

FPGA_TDO

NSTATUS

CONF_DONE

NCONFIG

NCE

DCLK

DATA0

NCSO

ASDO

DCLK

DATA0

NCSO

ASDO

EEP_I2C_SCLK

EEP_I2C_SDAT

EEP_I2C_SCLK

EEP_I2C_SDAT

05 ETHERNET

PAGE 15-16

ENET0_TX_DATA[3..0]

ENET0_GTX_CLK

ENET0_TX_EN

ENET0_TX_ER

ENET0_RST_N

ENET0_MDC

ENET0_TX_DATA[3..0]

ENET0_GTX_CLK

ENET0_TX_EN

ENET0_TX_ER

ENET0_RST_N

ENET0_MDC

ENET1_TX_DATA[3..0]

ENET1_MDC

ENET1_GTX_CLK

ENET1_TX_EN

ENET1_TX_ER

ENET1_RST_N

ENET1_TX_DATA[3..0]

ENET1_MDC

ENET1_GTX_CLK

ENET1_TX_EN

ENET1_TX_ER

ENET1_RST_N

ENET0_RX_DATA[3..0]

ENET0_RX_DV

ENET0_RX_ER

ENET0_RX_CRS

ENET0_RX_COL

ENET0_RX_CLK

ENET0_TX_CLK

ENET0_INT_N

ENET0_MDIO

ENET0_LINK100

ENET1_RX_DATA[3..0]

ENET1_RX_DV

ENET1_RX_ER

ENET1_RX_CRS

ENET1_RX_COL

ENET1_RX_CLK

ENET1_TX_CLK

ENET1_INT_N

ENET1_MDIO

ENET1_LINK100

ENETCLK_25

ENET0_RX_DATA[3..0]

ENET0_RX_DV

ENET0_RX_ER

ENET0_RX_CRS

ENET0_RX_COL

ENET0_RX_CLK

ENET0_TX_CLK

ENET0_INT_N

ENET0_MDIO

ENET0_LINK100

ENET1_RX_DATA[3..0]

ENET1_RX_DV

ENET1_RX_ER

ENET1_RX_CRS

ENET1_RX_COL

ENET1_RX_CLK

ENET1_TX_CLK

ENET1_INT_N

ENET1_MDIO

ENET1_LINK100

ENETCLK_25

06 VIDEO

PAGE 17-18

VGA_R[7..0]

VGA_G[7..0]

VGA_B[7..0]

VGA_SYNC_N

VGA_CLK

VGA_VS

VGA_HS

VGA_BLANK_N

TD_RESET_N

VGA_R[7..0]

VGA_G[7..0]

VGA_B[7..0]

VGA_SYNC_N

VGA_CLK

VGA_VS

VGA_HS

VGA_BLANK_N

TD_RESET_n

I2C_SCLK

I2C_SDAT

I2C_SCLK

I2C_SDAT

TD_DATA[7..0]

TD_VS

TD_HS

TD_CLK27

TD_DATA[7..0]

TD_VS

TD_HS

TD_CLK27

07 AUDIO

PAGE 19

AUD_DACDAT

AUD_XCK

I2C_SDAT

I2C_SCLK

AUD_DACDAT

AUD_XCK

I2C_SDAT

I2C_SCLK

AUD_ADCDAT

AUD_BCLK

AUD_DACLRCK

AUD_ADCLRCK

AUD_ADCDAT

AUD_BCLK

AUD_DACLRCK

AUD_ADCLRCK

08 USB DEVICE

PAGE 20

OTG_ADDR1

OTG_ADDR0

OTG_CS_N

OTG_WR_N

OTG_RD_N

OTG_DACK_N1

OTG_DACK_N0

OTG_RST_N

USB_12MHz

OTG_ADDR1

OTG_ADDR0

OTG_CS_N

OTG_WR_N

OTG_RD_N

OTG_DACK_N1

OTG_DACK_N0

OTG_RST_N

USB_12MHz

OTG_DATA[15..0]

OTG_FSPEED

OTG_LSPEED

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

OTG_DATA[15..0]

OTG_FSPEED

OTG_LSPEED

OTG_INT1

OTG_INT0

OTG_DREQ1

OTG_DREQ0

11 POWER

PAGE 26 -27

D

C

B

A

5

4

3

2

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

Title

Title

Size

Size

Size

C

C

C

DE2-115 Main Board

DE2-115 Main Board

DE2-115 Main Board

Document Number

Document Number

Document Number

TOP

TOP

TOP

Rev

Rev

Rev

A

A

A

Date:

Date:

Date:

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Sheet

Sheet

Sheet

3

3

3

of

of

of

27

27

27

1

�

5

4

3

2

1

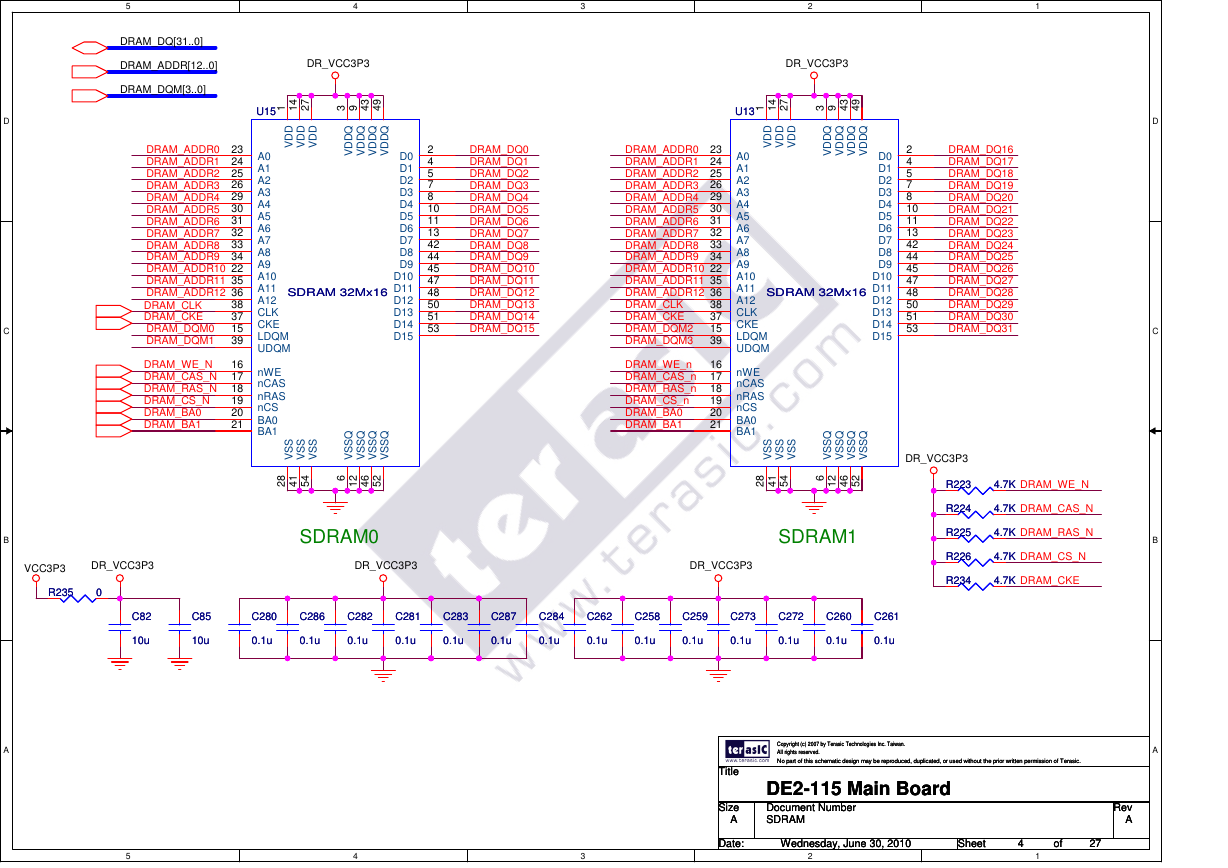

DR_VCC3P3

DR_VCC3P3

4

1

7

2

1

3

9

3

4

9

4

U15

U15

4

1

7

2

1

3

9

3

4

9

4

U13

U13

D

D

V

D

D

V

D

D

V

Q

D

D

V

Q

D

D

V

Q

D

D

V

Q

D

D

V

D

D

V

D

D

V

D

D

V

Q

D

D

V

Q

D

D

V

Q

D

D

V

Q

D

D

V

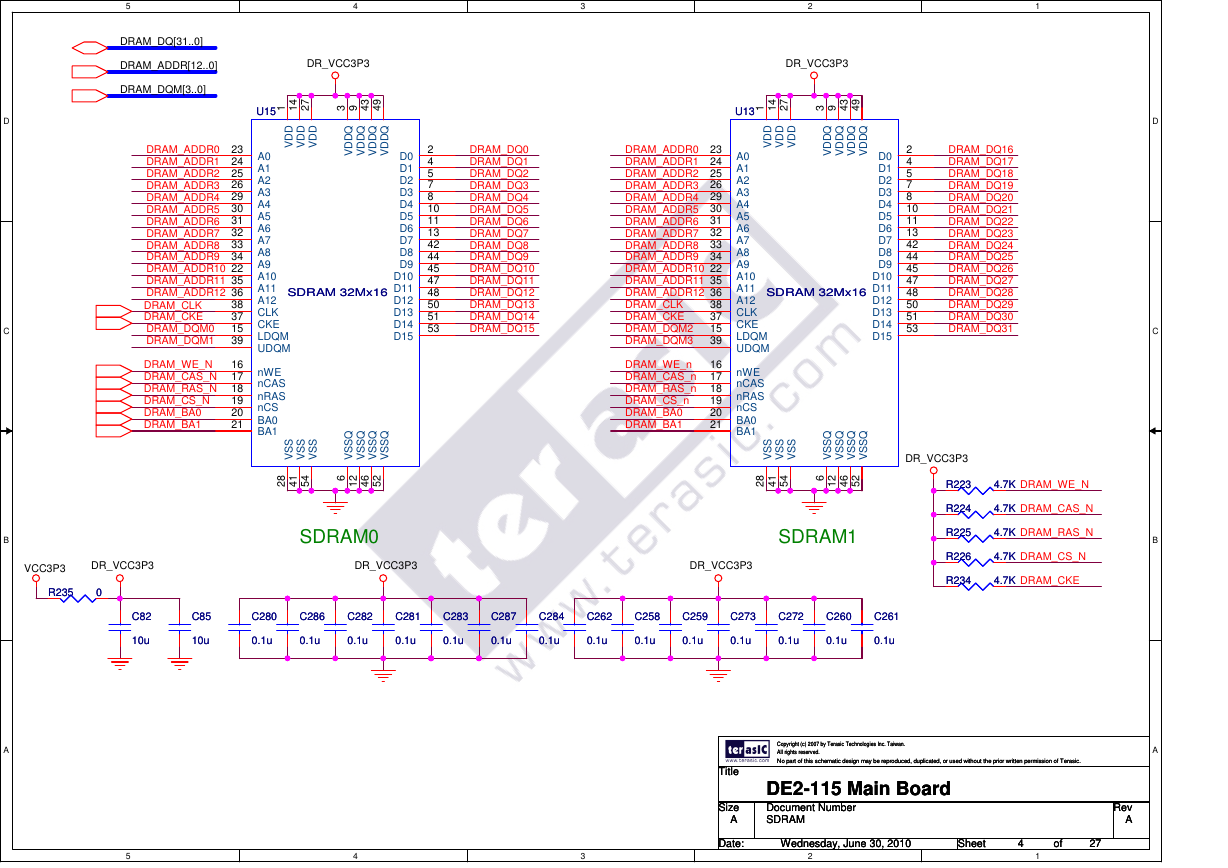

DRAM_DQ[31..0]

DRAM_ADDR[12..0]

DRAM_DQM[3..0]

DRAM_ADDR0

DRAM_ADDR1

DRAM_ADDR2

DRAM_ADDR3

DRAM_ADDR4

DRAM_ADDR5

DRAM_ADDR6

DRAM_ADDR7

DRAM_ADDR8

DRAM_ADDR9

DRAM_ADDR10

DRAM_ADDR11

DRAM_ADDR12

DRAM_CLK

DRAM_CKE

DRAM_DQM0

DRAM_DQM1

23

A0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10

35

A11

36

A12

38

37 CLK

CKE

15

LDQM

39

UDQM

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

DRAM_DQ0

DRAM_DQ1

DRAM_DQ2

DRAM_DQ3

DRAM_DQ4

DRAM_DQ5

DRAM_DQ6

DRAM_DQ7

DRAM_DQ8

DRAM_DQ9

DRAM_DQ10

DRAM_DQ11

DRAM_DQ12

DRAM_DQ13

DRAM_DQ14

DRAM_DQ15

DRAM_ADDR0

DRAM_ADDR1

DRAM_ADDR2

DRAM_ADDR3

DRAM_ADDR4

DRAM_ADDR5

DRAM_ADDR6

DRAM_ADDR7

DRAM_ADDR8

DRAM_ADDR9

DRAM_ADDR10

DRAM_ADDR11

DRAM_ADDR12

DRAM_CLK

DRAM_CKE

DRAM_DQM2

DRAM_DQM3

23

A0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10

35

A11

36

A12

38

37 CLK

CKE

15

LDQM

39

UDQM

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

DRAM_DQ16

DRAM_DQ17

DRAM_DQ18

DRAM_DQ19

DRAM_DQ20

DRAM_DQ21

DRAM_DQ22

DRAM_DQ23

DRAM_DQ24

DRAM_DQ25

DRAM_DQ26

DRAM_DQ27

DRAM_DQ28

DRAM_DQ29

DRAM_DQ30

DRAM_DQ31

SDRAM 32Mx16

SDRAM 32Mx16

SDRAM 32Mx16

SDRAM 32Mx16

DRAM_WE_N

DRAM_CAS_N

DRAM_RAS_N

DRAM_CS_N

DRAM_BA0

DRAM_BA1

16

17

18

19

20

21

nWE

nCAS

nRAS

nCS

BA0

BA1

S

S

V

S

S

V

S

S

V

Q

S

S

V

Q

S

S

V

Q

S

S

V

Q

S

S

V

DRAM_WE_n

DRAM_CAS_n

DRAM_RAS_n

DRAM_CS_n

DRAM_BA0

DRAM_BA1

16

17

18

19

20

21

nWE

nCAS

nRAS

nCS

BA0

BA1

S

S

V

S

S

V

S

S

V

Q

S

S

V

Q

S

S

V

Q

S

S

V

Q

S

S

V

DR_VCC3P3

8

2

1

4

4

5

6

2

1

6

4

2

5

8

2

1

4

4

5

6

2

1

6

4

2

5

SDRAM0

SDRAM1

DR_VCC3P3

DR_VCC3P3

R223

R223

4.7K

4.7K

DRAM_WE_N

R224

R224

4.7K

4.7K

DRAM_CAS_N

R225

R225

4.7K

4.7K

DRAM_RAS_N

R226

R226

4.7K

4.7K

DRAM_CS_N

R234

R234

4.7K

4.7K

DRAM_CKE

C280

C280

C286

C286

C282

C282

C281

C281

C283

C283

C287

C287

C284

C284

C262

C262

C258

C258

C259

C259

C273

C273

C272

C272

C260

C260

C261

C261

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

0.1u

VCC3P3

DR_VCC3P3

R235

R235

0

0

C82

C82

10u

10u

C85

C85

10u

10u

5

4

3

2

1

Date:

Date:

Date:

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Sheet

Sheet

Sheet

4

4

4

of

of

of

27

27

27

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

Title

Title

Size

Size

Size

A

A

A

DE2-115 Main Board

DE2-115 Main Board

DE2-115 Main Board

Document Number

Document Number

Document Number

SDRAM

SDRAM

SDRAM

Rev

Rev

Rev

A

A

A

D

C

B

A

D

C

B

A

�

D

C

B

A

5

4

3

2

1

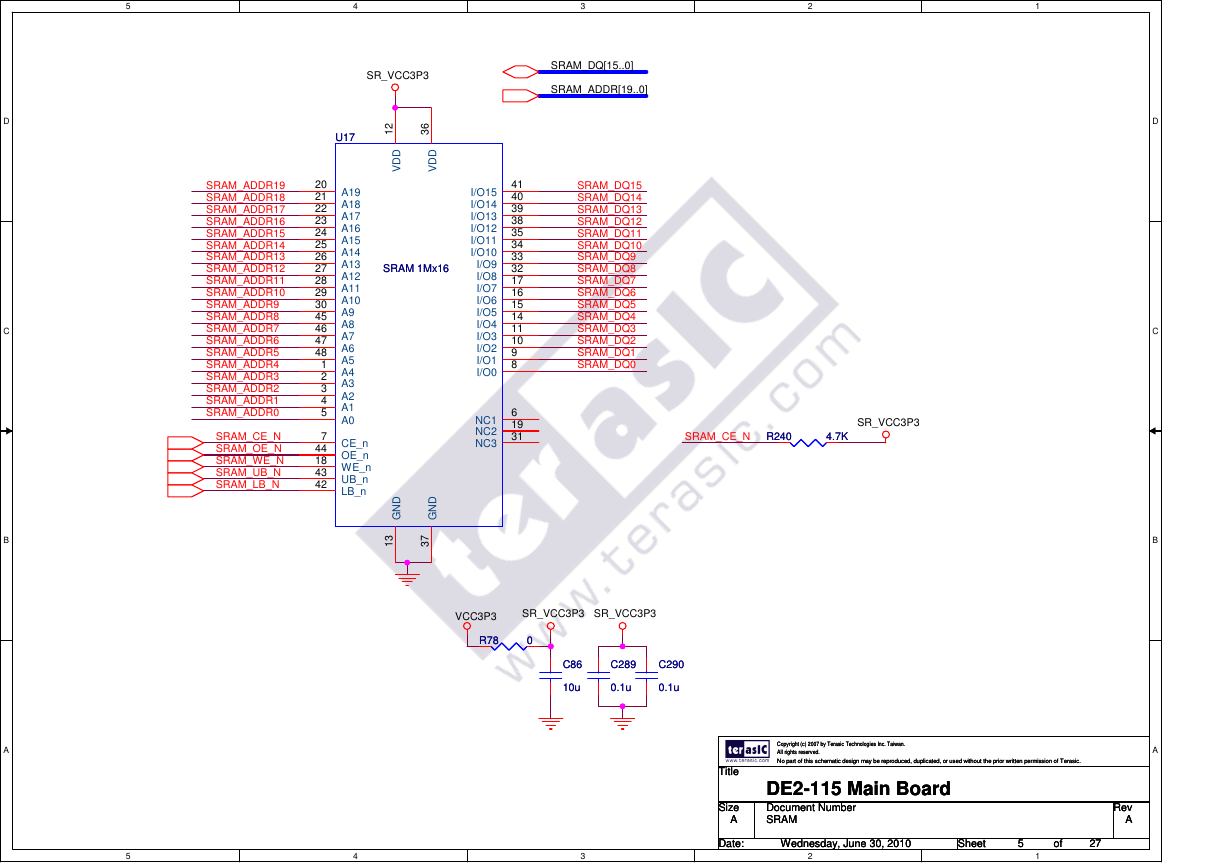

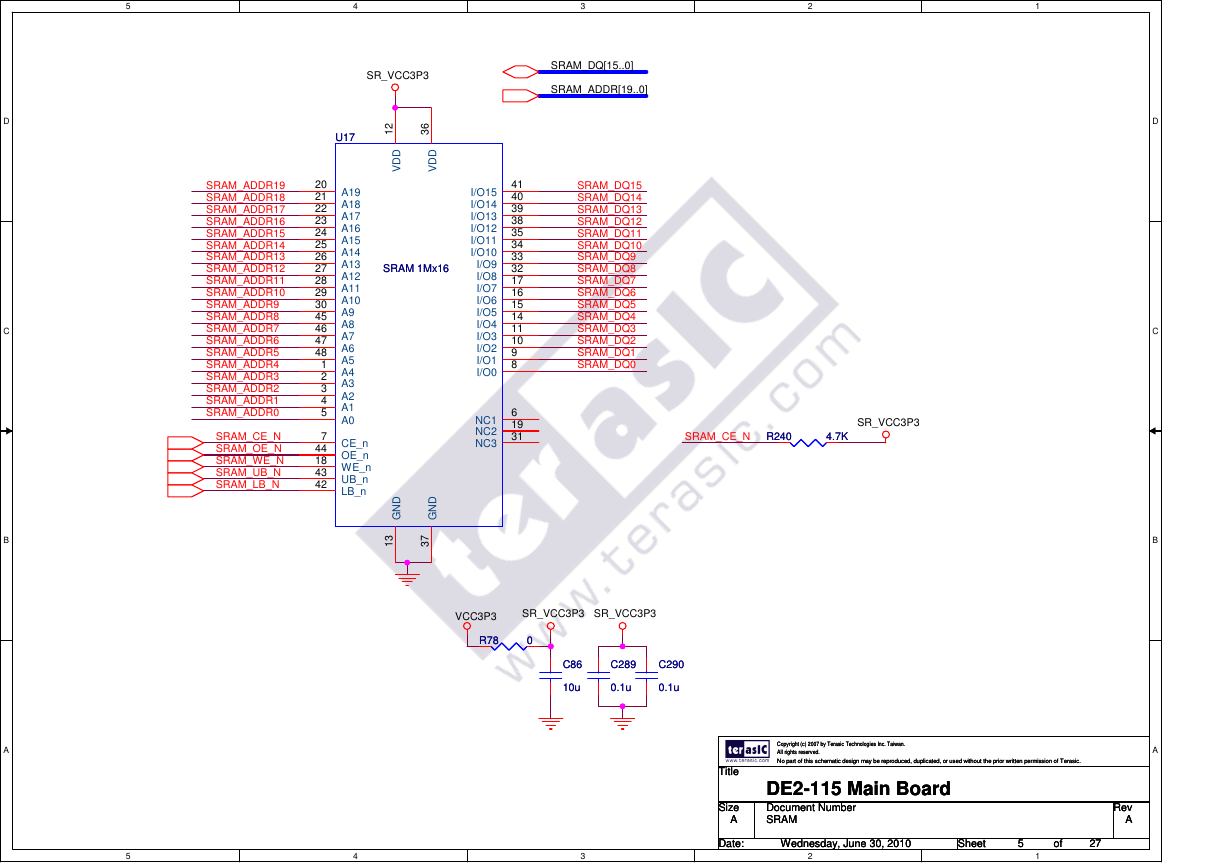

SRAM_DQ[15..0]

SRAM_ADDR[19..0]

SRAM_DQ15

SRAM_DQ14

SRAM_DQ13

SRAM_DQ12

SRAM_DQ11

SRAM_DQ10

SRAM_DQ9

SRAM_DQ8

SRAM_DQ7

SRAM_DQ6

SRAM_DQ5

SRAM_DQ4

SRAM_DQ3

SRAM_DQ2

SRAM_DQ1

SRAM_DQ0

SR_VCC3P3

U17

U17

2

1

6

3

D

D

V

D

D

V

41

40

39

38

35

34

33

32

17

16

15

14

11

10

9

8

6

19

31

I/O15

I/O14

I/O13

I/O12

I/O11

I/O10

I/O9

I/O8

I/O7

I/O6

I/O5

I/O4

I/O3

I/O2

I/O1

I/O0

NC1

NC2

NC3

SRAM_ADDR19

SRAM_ADDR18

SRAM_ADDR17

SRAM_ADDR16

SRAM_ADDR15

SRAM_ADDR14

SRAM_ADDR13

SRAM_ADDR12

SRAM_ADDR11

SRAM_ADDR10

SRAM_ADDR9

SRAM_ADDR8

SRAM_ADDR7

SRAM_ADDR6

SRAM_ADDR5

SRAM_ADDR4

SRAM_ADDR3

SRAM_ADDR2

SRAM_ADDR1

SRAM_ADDR0

SRAM_CE_N

SRAM_OE_N

SRAM_WE_N

SRAM_UB_N

SRAM_LB_N

20

21

22

23

24

25

26

27

28

29

30

45

46

47

48

1

2

3

4

5

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

7

CE_n

44

18 OE_n

WE_n

43

UB_n

42

LB_n

SRAM 1Mx16

SRAM 1Mx16

D

N

G

D

N

G

3

1

7

3

VCC3P3

SR_VCC3P3

SR_VCC3P3

R78

R78

0

0

C86

C86

10u

10u

C289

C289

C290

C290

0.1u

0.1u

0.1u

0.1u

SRAM_CE_N

R240

R240

4.7K

4.7K

SR_VCC3P3

5

4

3

2

1

Date:

Date:

Date:

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Sheet

Sheet

Sheet

5

5

5

of

of

of

27

27

27

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

Title

Title

Size

Size

Size

A

A

A

DE2-115 Main Board

DE2-115 Main Board

DE2-115 Main Board

Document Number

Document Number

Document Number

SRAM

SRAM

SRAM

Rev

Rev

Rev

A

A

A

D

C

B

A

�

5

4

3

2

1

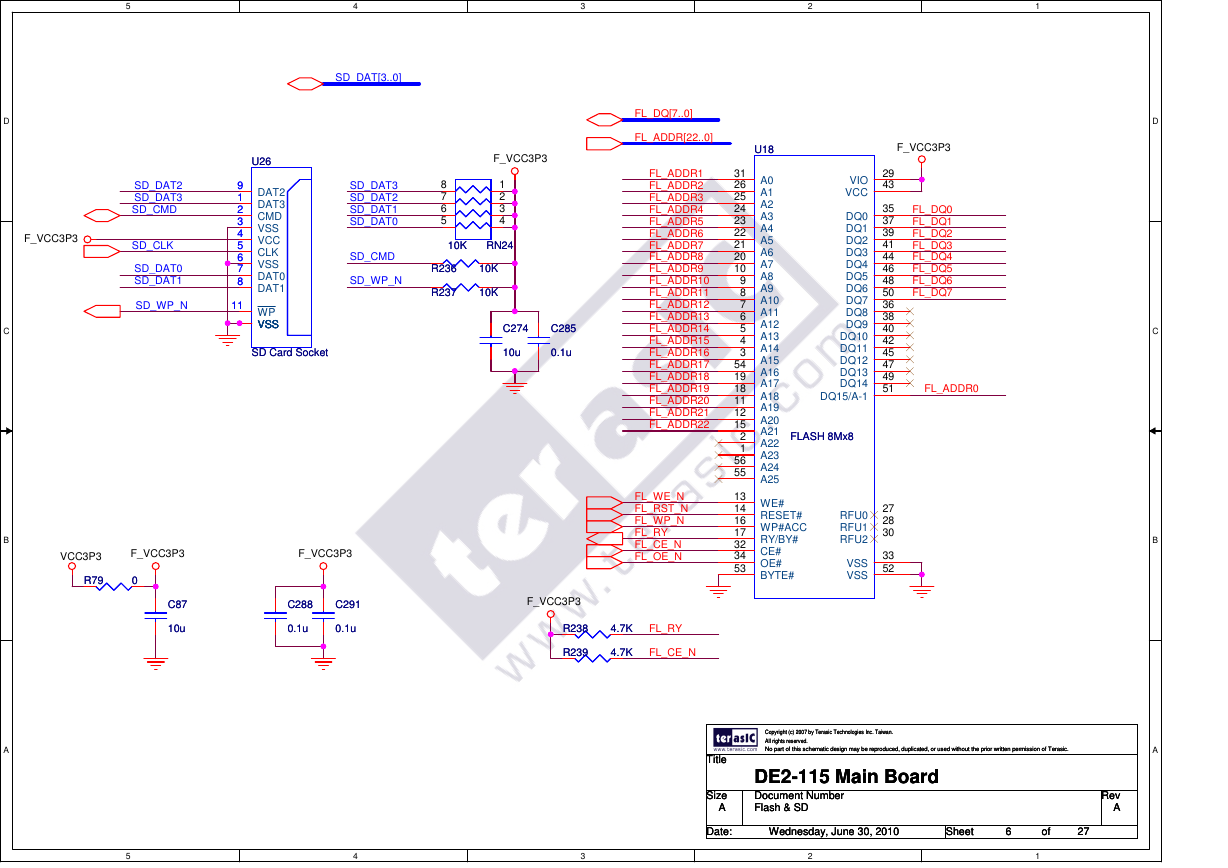

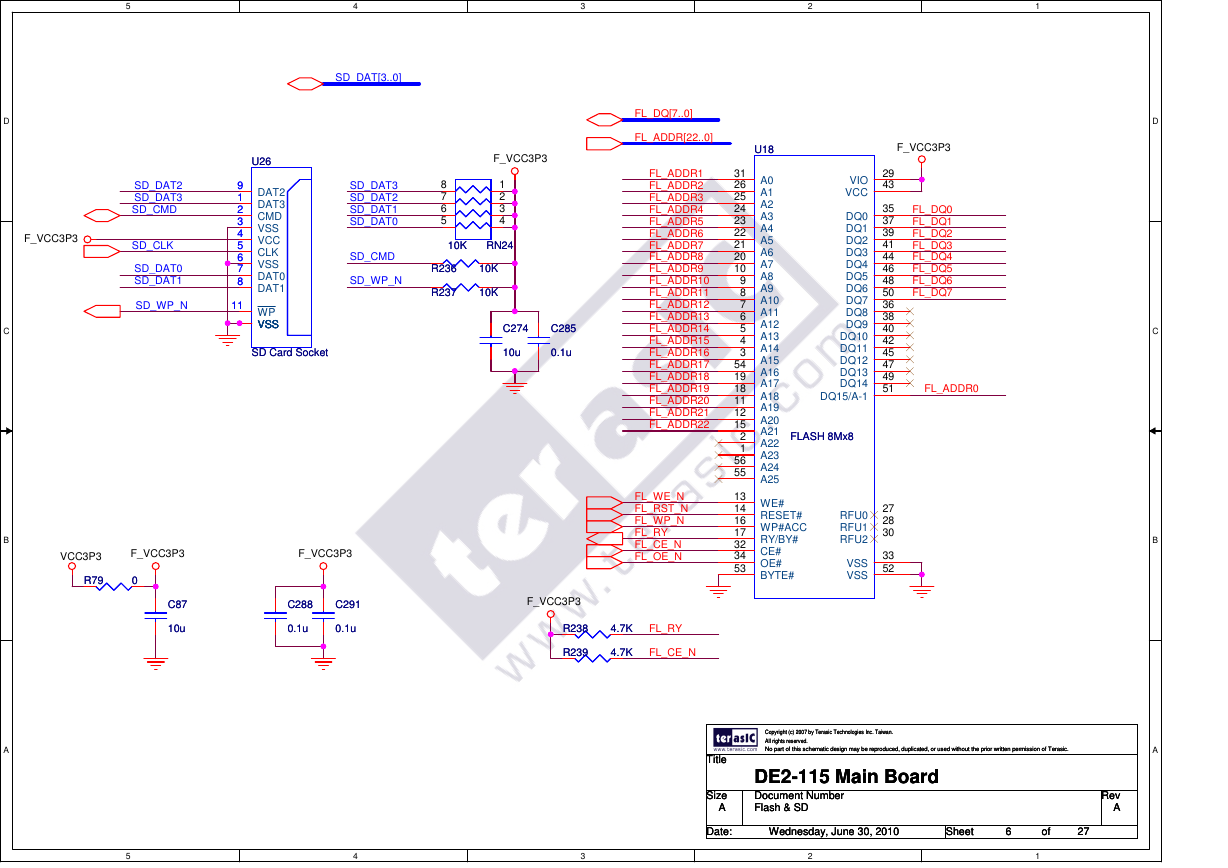

SD_DAT[3..0]

F_VCC3P3

SD_DAT2

SD_DAT3

SD_CMD

SD_CLK

SD_DAT0

SD_DAT1

9

9

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

SD_WP_N

11

11

U26

U26

DAT2

DAT3

CMD

VSS

VCC

CLK

VSS

DAT0

DAT1

WP

VSS

VSSVSSVSSVSS

SD Card Socket

SD Card Socket

F_VCC3P3

SD_DAT3

SD_DAT2

SD_DAT1

SD_DAT0

SD_CMD

SD_WP_N

8

7

6

5

1

2

3

4

10K

10K

RN24

RN24

R236

R236

10K

10K

R237

R237

10K

10K

C274

C274

C285

C285

10u

10u

0.1u

0.1u

FL_DQ[7..0]

FL_ADDR[22..0]

FL_ADDR1

FL_ADDR2

FL_ADDR3

FL_ADDR4

FL_ADDR5

FL_ADDR6

FL_ADDR7

FL_ADDR8

FL_ADDR9

FL_ADDR10

FL_ADDR11

FL_ADDR12

FL_ADDR13

FL_ADDR14

FL_ADDR15

FL_ADDR16

FL_ADDR17

FL_ADDR18

FL_ADDR19

FL_ADDR20

FL_ADDR21

FL_ADDR22

FL_WE_N

FL_RST_N

FL_WP_N

FL_RY

FL_CE_N

FL_OE_N

U18

U18

F_VCC3P3

FL_DQ0

FL_DQ1

FL_DQ2

FL_DQ3

FL_DQ4

FL_DQ5

FL_DQ6

FL_DQ7

FL_ADDR0

31

26

25

24

23

22

21

20

10

9

8

7

6

5

4

3

54

19

18

11

12

15

2

1

56

55

13

14

16

17

32

34

53

VIO

VCC

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15/A-1

FLASH 8Mx8

FLASH 8Mx8

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

WE#

RESET#

WP#ACC

RY/BY#

CE#

OE#

BYTE#

RFU0

RFU1

RFU2

VSS

VSS

29

43

35

37

39

41

44

46

48

50

36

38

40

42

45

47

49

51

27

28

30

33

52

VCC3P3

F_VCC3P3

F_VCC3P3

R79

R79

0

0

C87

C87

10u

10u

C288

C288

C291

C291

0.1u

0.1u

0.1u

0.1u

F_VCC3P3

R238

R238

4.7K

4.7K

FL_RY

R239

R239

4.7K

4.7K

FL_CE_N

5

4

3

2

1

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

Title

Title

Size

Size

Size

A

A

A

DE2-115 Main Board

DE2-115 Main Board

DE2-115 Main Board

Document Number

Document Number

Document Number

Flash & SD

Flash & SD

Flash & SD

Rev

Rev

Rev

A

A

A

Date:

Date:

Date:

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Sheet

Sheet

Sheet

6

6

6

of

of

of

27

27

27

D

C

B

A

D

C

B

A

�

5

4

3

2

1

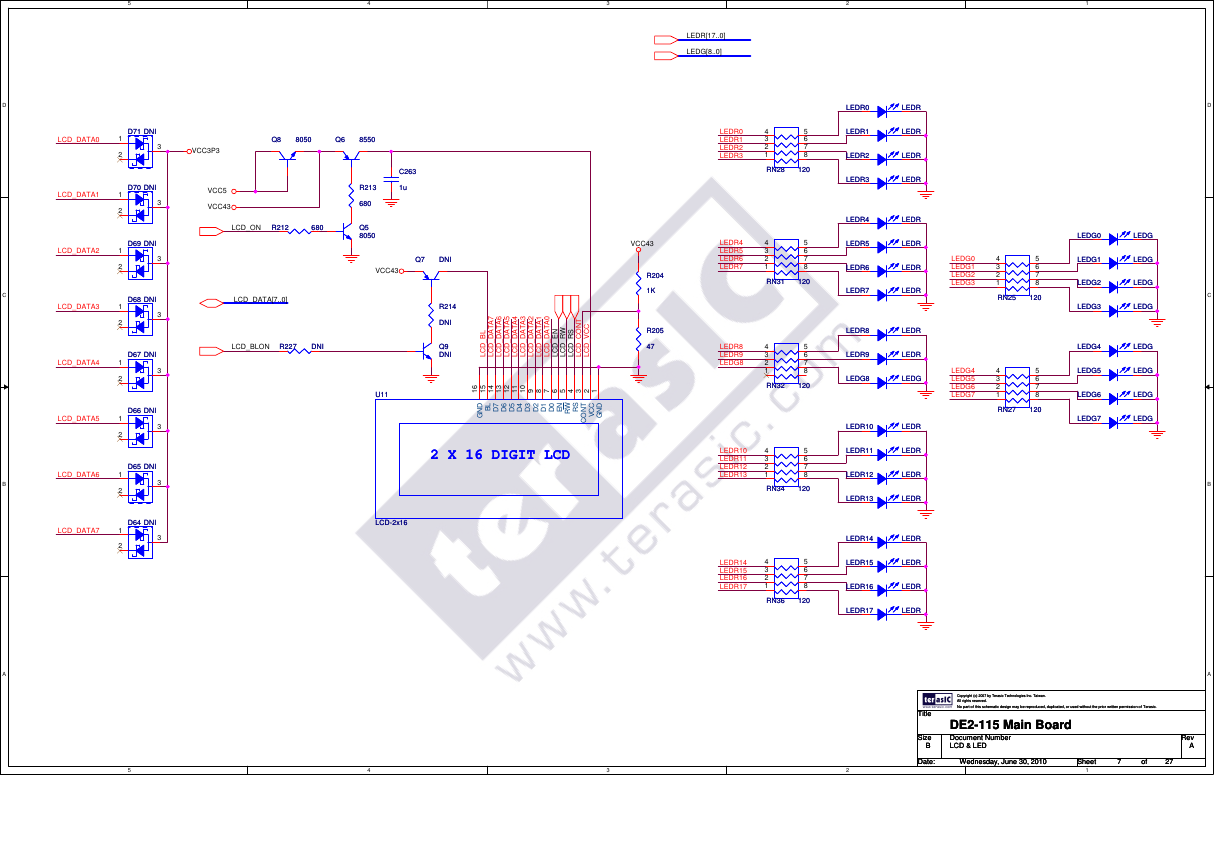

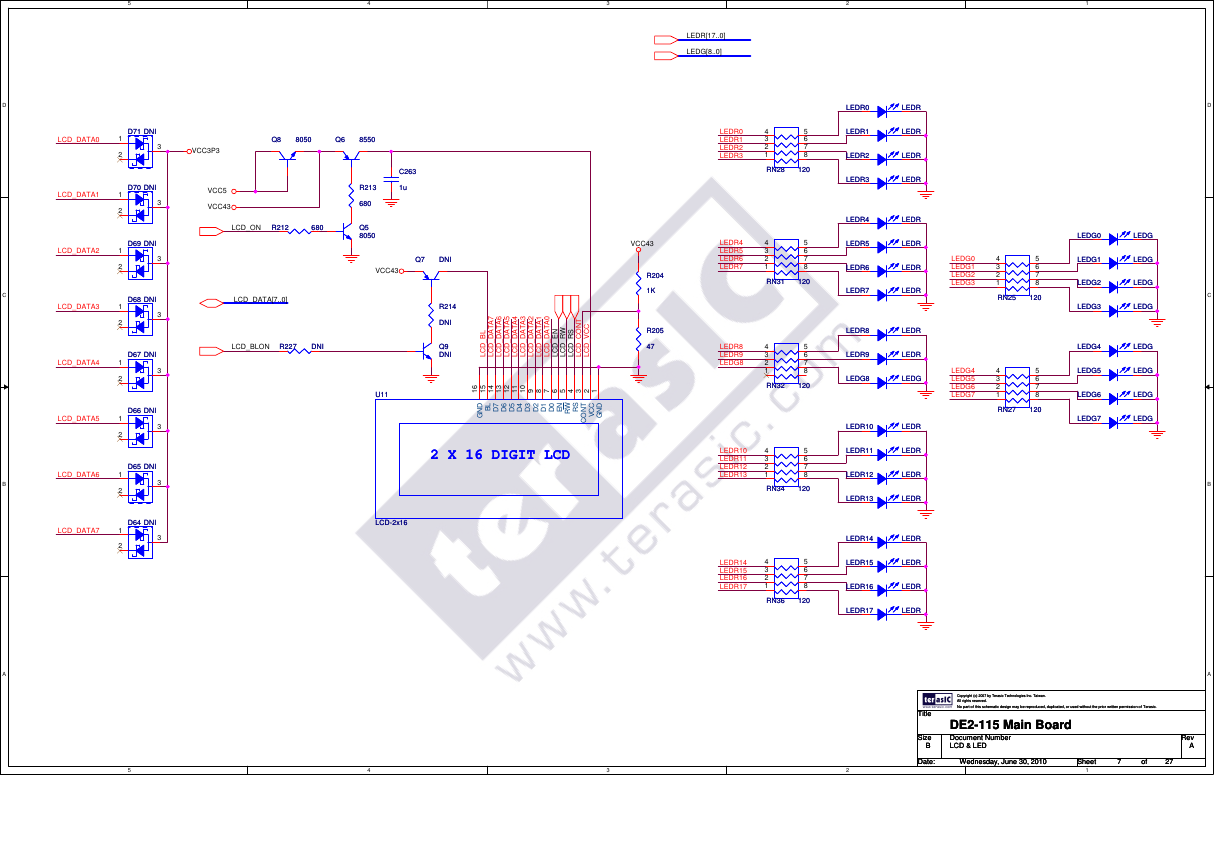

LCD_DATA0

LCD_DATA1

LCD_DATA2

LCD_DATA3

LCD_DATA4

LCD_DATA5

LCD_DATA6

LCD_DATA7

D71 DNI

D71 DNI

D70 DNI

D70 DNI

D69 DNI

D69 DNI

D68 DNI

D68 DNI

D67 DNI

D67 DNI

D66 DNI

D66 DNI

D65 DNI

D65 DNI

D64 DNI

D64 DNI

3

3

3

3

3

3

3

3

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

Q8

Q8

8050

8050

Q6

Q6

8550

8550

VCC3P3

VCC5

VCC43

LCD_ON

R212

R212

680

680

LCD_DATA[7..0]

LCD_BLON

R227

R227

DNI

DNI

VCC43

R204

R204

1K

1K

R205

R205

47

47

C263

C263

R213

R213

1u

1u

680

680

Q5

Q5

8050

8050

Q7

Q7

DNI

DNI

VCC43

R214

R214

DNI

DNI

Q9

Q9

DNI

DNI

7

A

T

A

D

_

D

C

L

6

A

T

A

D

_

D

C

L

5

A

T

A

D

_

D

C

L

4

A

T

A

D

_

D

C

L

3

A

T

A

D

_

D

C

L

2

A

T

A

D

_

D

C

L

1

A

T

A

D

_

D

C

L

0

A

T

A

D

_

D

C

L

L

B

_

D

C

L

T

N

O

C

_

D

C

L

C

C

V

_

D

C

L

N

E

_

D

C

L

W

R

_

D

C

L

S

R

_

D

C

L

U11

U11

6

1

5

1

4

1

3

1

2

1

1

1

0

1

9

8

7

6

5

4

3

2

1

L

B

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

D

N

G

N

E

W

R

S

R

C

C

V

D

N

G

T

N

O

C

2 X 16 DIGIT LCD

2 X 16 DIGIT LCD

LCD-2x16

LCD-2x16

D

C

B

A

LEDR[17..0]

LEDG[8..0]

LEDR0

LEDR1

LEDR2

LEDR3

4

3

2

1

5

6

7

8

RN28

RN28

120

120

LEDR4

LEDR5

LEDR6

LEDR7

4

3

2

1

5

6

7

8

RN31

RN31

120

120

LEDR8

LEDR9

LEDG8

4

3

2

1

5

6

7

8

RN32

RN32

120

120

LEDR10

LEDR11

LEDR12

LEDR13

4

3

2

1

5

6

7

8

RN34

RN34

120

120

LEDR14

LEDR15

LEDR16

LEDR17

4

3

2

1

5

6

7

8

RN36

RN36

120

120

LEDR0

LEDR0

LEDR

LEDR

LEDR1

LEDR1

LEDR

LEDR

LEDR2

LEDR2

LEDR

LEDR

LEDR3

LEDR3

LEDR

LEDR

LEDR4

LEDR4

LEDR

LEDR

LEDR5

LEDR5

LEDR

LEDR

LEDR6

LEDR6

LEDR

LEDR

LEDR7

LEDR7

LEDR

LEDR

LEDR8

LEDR8

LEDR

LEDR

LEDR9

LEDR9

LEDR

LEDR

LEDG8

LEDG8

LEDG

LEDG

LEDR10

LEDR10

LEDR

LEDR

LEDR11

LEDR11

LEDR

LEDR

LEDR12

LEDR12

LEDR

LEDR

LEDR13

LEDR13

LEDR

LEDR

LEDR14

LEDR14

LEDR

LEDR

LEDR15

LEDR15

LEDR

LEDR

LEDR16

LEDR16

LEDR

LEDR

LEDR17

LEDR17

LEDR

LEDR

LEDG0

LEDG1

LEDG2

LEDG3

4

3

2

1

5

6

7

8

RN25

RN25

120

120

LEDG4

LEDG5

LEDG6

LEDG7

4

3

2

1

5

6

7

8

RN27

RN27

120

120

LEDG0

LEDG0

LEDG

LEDG

LEDG1

LEDG1

LEDG

LEDG

LEDG2

LEDG2

LEDG

LEDG

LEDG3

LEDG3

LEDG

LEDG

LEDG4

LEDG4

LEDG

LEDG

LEDG5

LEDG5

LEDG

LEDG

LEDG6

LEDG6

LEDG

LEDG

LEDG7

LEDG7

LEDG

LEDG

D

C

B

A

5

4

3

2

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

Title

Title

Size

Size

Size

B

B

B

DE2-115 Main Board

DE2-115 Main Board

DE2-115 Main Board

Document Number

Document Number

Document Number

LCD & LED

LCD & LED

LCD & LED

Rev

Rev

Rev

A

A

A

Date:

Date:

Date:

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Sheet

Sheet

Sheet

1

7

7

7

of

of

of

27

27

27

�

D

C

B

A

5

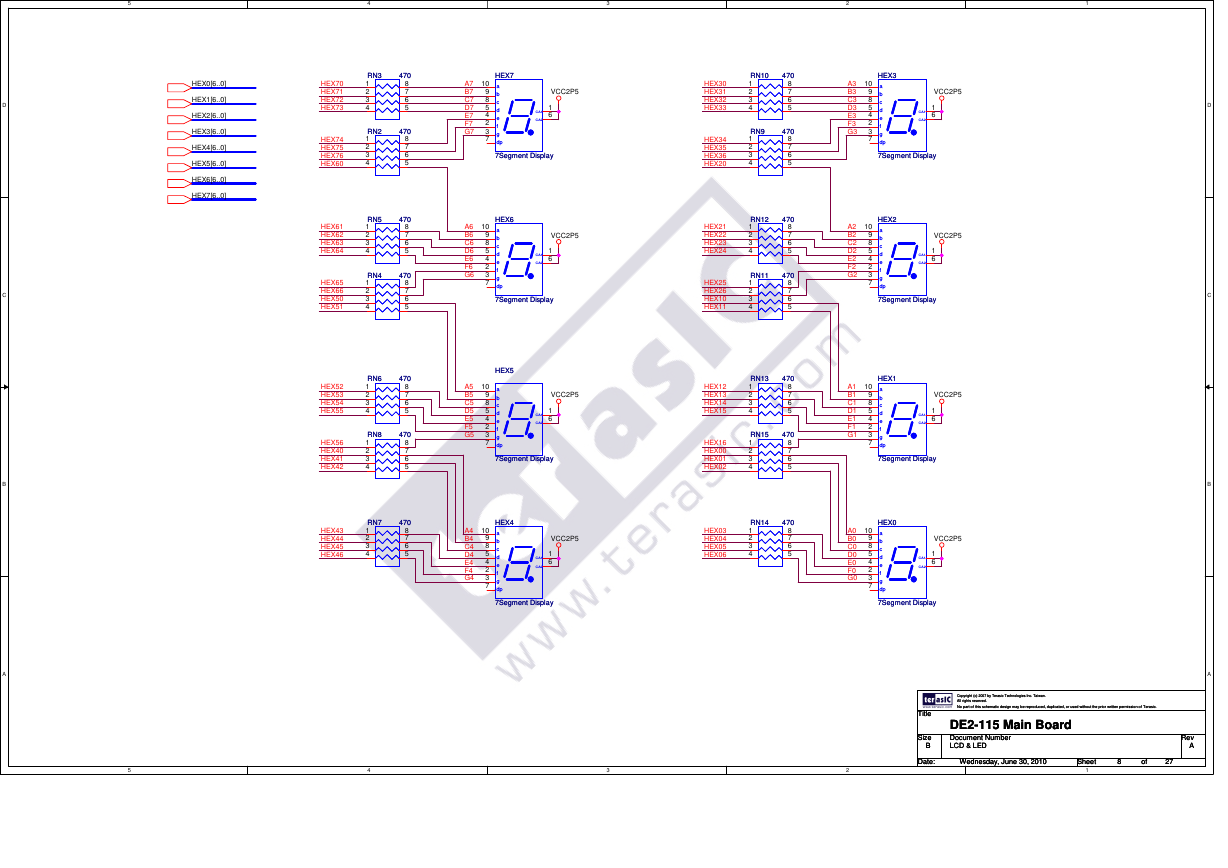

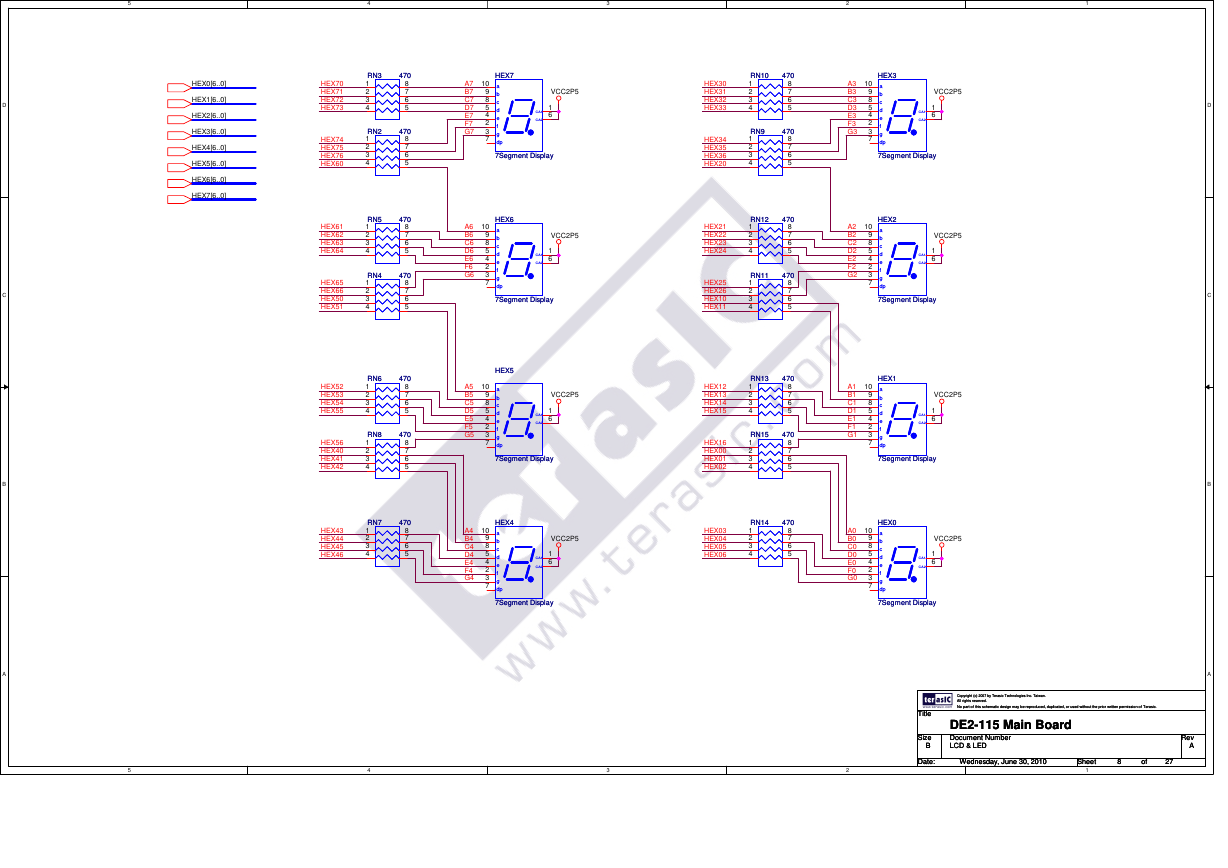

HEX0[6..0]

HEX1[6..0]

HEX2[6..0]

HEX3[6..0]

HEX4[6..0]

HEX5[6..0]

HEX6[6..0]

HEX7[6..0]

4

RN3

RN3

1

2

3

4

RN2

RN2

1

2

3

4

RN5

RN5

1

2

3

4

RN4

RN4

1

2

3

4

RN6

RN6

1

2

3

4

RN8

RN8

1

2

3

4

RN7

RN7

1

2

3

4

470

470

8

7

6

5

470

470

8

7

6

5

470

470

8

7

6

5

470

470

8

7

6

5

470

470

8

7

6

5

470

470

8

7

6

5

470

470

8

7

6

5

HEX70

HEX71

HEX72

HEX73

HEX74

HEX75

HEX76

HEX60

HEX61

HEX62

HEX63

HEX64

HEX65

HEX66

HEX50

HEX51

HEX52

HEX53

HEX54

HEX55

HEX56

HEX40

HEX41

HEX42

HEX43

HEX44

HEX45

HEX46

HEX7

HEX7

A7

B7

C7

D7

E7

F7

G7

10

9

8

5

4

2

3

7

a

a

b

b

c

c

d

d

e

e

f

f

g

g

dp

dp

VCC2P5

1

6

CA1

CA1

CA2

CA2

7Segment Display

7Segment Display

HEX6

HEX6

A6

B6

C6

D6

E6

F6

G6

10

9

8

5

4

2

3

7

a

a

b

b

c

c

d

d

e

e

f

f

g

g

dp

dp

VCC2P5

1

6

CA1

CA1

CA2

CA2

7Segment Display

7Segment Display

HEX5

HEX5

A5

B5

C5

D5

E5

F5

G5

10

9

8

5

4

2

3

7

a

a

b

b

c

c

d

d

e

e

f

f

g

g

dp

dp

VCC2P5

1

6

CA1

CA1

CA2

CA2

7Segment Display

7Segment Display

HEX4

HEX4

A4

B4

C4

D4

E4

F4

G4

10

9

8

5

4

2

3

7

a

a

b

b

c

c

d

d

e

e

f

f

g

g

dp

dp

VCC2P5

1

6

CA1

CA1

CA2

CA2

3

2

1

HEX30

HEX31

HEX32

HEX33

HEX34

HEX35

HEX36

HEX20

HEX21

HEX22

HEX23

HEX24

HEX25

HEX26

HEX10

HEX11

HEX12

HEX13

HEX14

HEX15

HEX16

HEX00

HEX01

HEX02

RN10

RN10

1

2

3

4

RN9

RN9

1

2

3

4

RN12

RN12

1

2

3

4

RN11

RN11

1

2

3

4

RN13

RN13

1

2

3

4

RN15

RN15

1

2

3

4

470

470

8

7

6

5

470

470

8

7

6

5

470

470

8

7

6

5

470

470

8

7

6

5

470

470

8

7

6

5

470

470

8

7

6

5

HEX03

HEX04

HEX05

HEX06

RN14

RN14

1

2

3

4

470

470

8

7

6

5

HEX3

HEX3

A3

B3

C3

D3

E3

F3

G3

10

9

8

5

4

2

3

7

a

a

b

b

c

c

d

d

e

e

f

f

g

g

dp

dp

VCC2P5

1

6

CA1

CA1

CA2

CA2

7Segment Display

7Segment Display

HEX2

HEX2

A2

B2

C2

D2

E2

F2

G2

10

9

8

5

4

2

3

7

a

a

b

b

c

c

d

d

e

e

f

f

g

g

dp

dp

VCC2P5

1

6

CA1

CA1

CA2

CA2

7Segment Display

7Segment Display

HEX1

HEX1

A1

B1

C1

D1

E1

F1

G1

10

9

8

5

4

2

3

7

a

a

b

b

c

c

d

d

e

e

f

f

g

g

dp

dp

VCC2P5

1

6

CA1

CA1

CA2

CA2

7Segment Display

7Segment Display

HEX0

HEX0

A0

B0

C0

D0

E0

F0

G0

10

9

8

5

4

2

3

7

a

a

b

b

c

c

d

d

e

e

f

f

g

g

dp

dp

VCC2P5

1

6

CA1

CA1

CA2

CA2

7Segment Display

7Segment Display

7Segment Display

7Segment Display

5

4

3

2

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

Title

Title

Size

Size

Size

B

B

B

DE2-115 Main Board

DE2-115 Main Board

DE2-115 Main Board

Document Number

Document Number

Document Number

LCD & LED

LCD & LED

LCD & LED

Rev

Rev

Rev

A

A

A

Date:

Date:

Date:

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Wednesday, June 30, 2010

Sheet

Sheet

Sheet

1

8

8

8

of

of

of

27

27

27

D

C

B

A

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc