特征特征

• 高高 Performance, 低低 Power

• Advanced RISC Architecture

AVR

® 8位微控制器

位微控制器

– 135 Powerful Instructions – Most Single Clock Cycle

Execution

- 32个个8位通用工作寄存器

位通用工作寄存器

- 全静态工作

全静态工作

– Up to 16 MIPS Throughput at 16

MHz

- 片上片上2周期乘法器

周期乘法器

•

•

•

•

•

•

•

Non-volatile Program and Data Memories

– 64K/128K/256K Bytes of In-System Self-Programmable

FlashEndurance: 10,000 Write/Erase Cycles

- 可选启动代码段与独立锁定位

可选启动代码段与独立锁定位

- 4K字节字节EEPROM

在系统编程通过片上引导程序

在系统编程通过片上引导程序

真正同时读 - 写操写操

真正同时读

作作

耐力:耐力:100,000写写/擦除周期

擦除周期

字节片内SRAM

- 8K字节片内

- 达到达到64K字节可选外部存储器空间

字节可选外部存储器空间

- 可以对锁定软件安全

可以对锁定软件安全

JTAG((IEEE 1149.1标准兼容)接口

标准兼容)接口

- 边界扫描功能根据

边界扫描功能根据JTAG标准标准

- 广泛片上调试支持

广泛片上调试支持

- 闪存闪存,EEPROM,熔丝位和锁定位通过

熔丝位和锁定位通过JTAG接口编程

接口编程

外设特性

外设特性

位定时器/计数器具有独立预分频器和比较模式

计数器具有独立预分频器和比较模式

计数器具有独立预分频器,Compare-和捕捉模式

位定时器/计数器具有独立预分频器

和捕捉模式

- 两个两个8位定时器

- 4个个16位定时器

- 实时计数器具有独立振荡器

实时计数器具有独立振荡器

- 4个个8位位PWM通道通道

- 六六/ 12个个PWM通道通道,具有可编程解决方案从

具有可编程解决方案从2至至16位位

四可编程串行USART((ATmega1281/2561,ATmega640/1280/2560))

(ATmega1281/2561, ATmega640/1280/2560)

- 输出比较调制

输出比较调制

- 8/16通道通道,10位位ADC

- 双双/四可编程串行

- 主主/从从SPI串行接口

串行接口

面向字节2线串行接口

- 面向字节

线串行接口

- 可编程看门狗定时器具有独立片内振荡器

可编程看门狗定时器具有独立片内振荡器

- 片上模拟比较器

片上模拟比较器

- 中断和唤醒引脚电平变化

中断和唤醒引脚电平变化

单片机特性

单片机特性

- 上电复位和可编程欠压检测

上电复位和可编程欠压检测

- 片内标定振荡器

片内标定振荡器

- 外部和内部中断源

外部和内部中断源

- 六睡眠模式:空闲

六睡眠模式:空闲,ADC降噪降噪,省电省电,掉电掉电,待机待机,

和扩展和扩展Standby

I / O和封装和封装

- 51/86可编程可编程I / O线(线(ATmega1281/2561,ATmega640/1280/2560))

– 64-lead

(ATmega1281/2561)

– 100-lead (ATmega640/1280/2560)

- 100引脚引脚TQFP封装(封装(64引脚引脚TQFP选项)选项)

温度范围:

温度范围:

速度等级:

速度等级:

°C至至85

°C工业级工业级

– -

40

–

ATmega640/1280/1281/2560/2561V:

– ATmega640/1280/1281/2560/2561:

0 - 4兆赫兆赫@ 1.8 - 5.5V,0 - 8兆赫兆赫@ 2.7 -

5.5V

0 - 8兆赫兆赫@ 2.7 - 5.5V,0 - 16兆赫兆赫@ 4.5 -

5.5V

8-bit

微控制器

微控制器

with

64K/128K/256K

字节系统

字节系统

可编程可编程

Flash

ATmega640/V

ATmega1280/V

ATmega1281/V

ATmega2560/V

ATmega2561/V

前进前进

信息信息

摘要摘要

2549BS–AVR–05/05

注:这是一个总结性文件.一个完整文档可以在我们

网站www.atmel.com.

�

引脚配置

引脚配置

图图1.

引脚ATmega640/1280/2560

2

ATmega640/1280/1281/2560/2561

2549BS–AVR–05/05

�

ATmega640/1280/1281/2560/2561

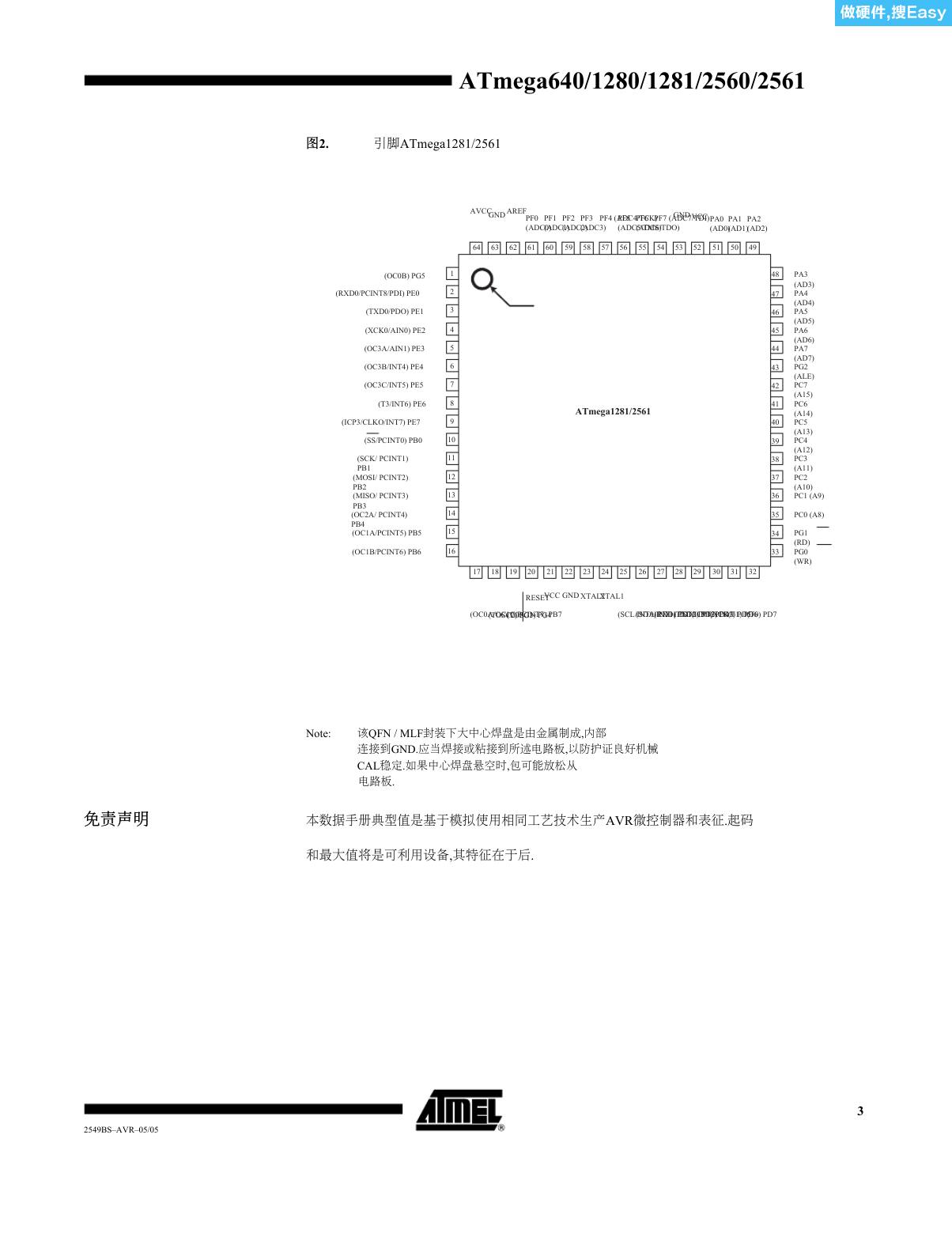

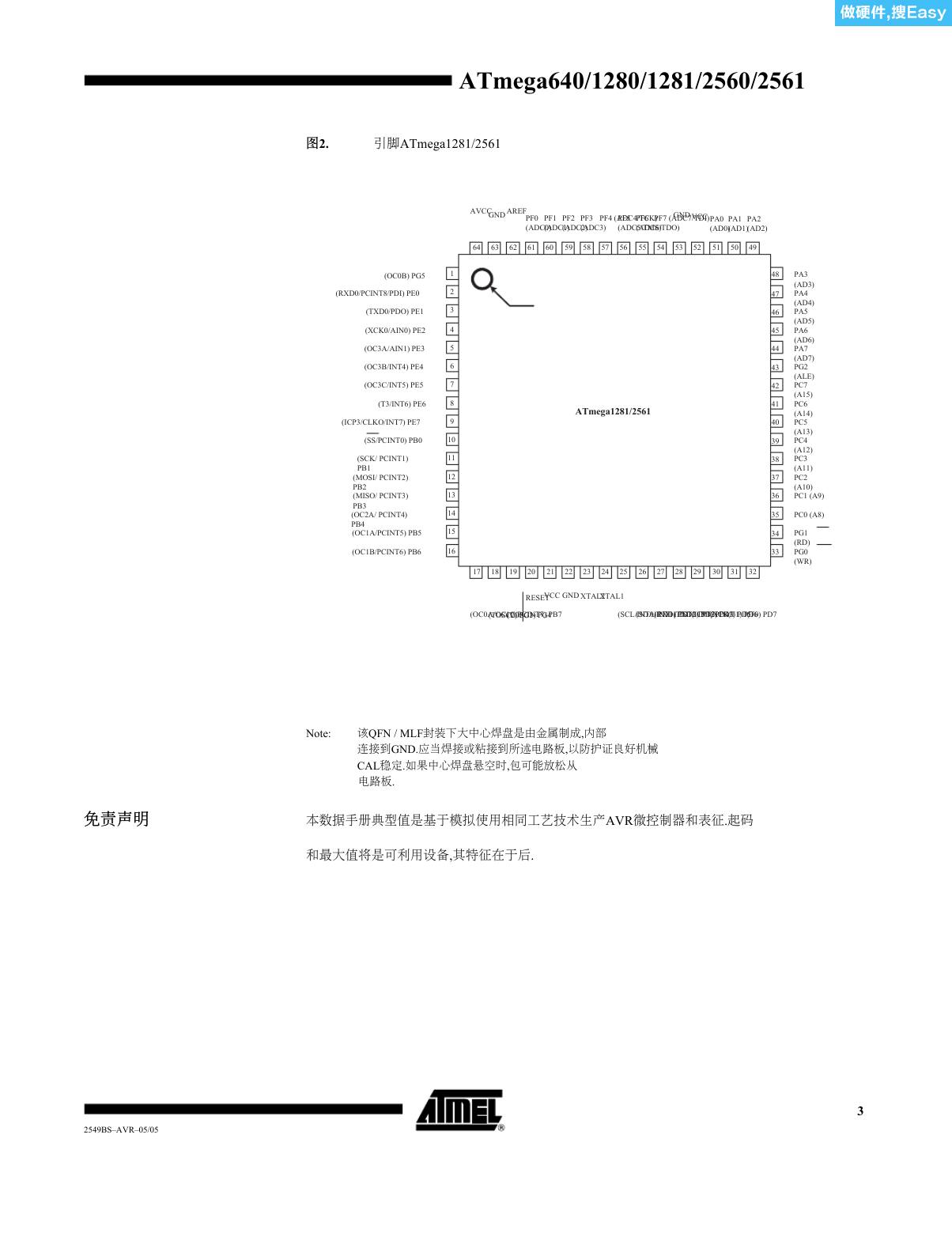

图图2.

引脚ATmega1281/2561

AVCCGND AREF

PF3

PF2

PF1

PF0

(ADC2)

(ADC1)

(ADC0)

(ADC3)

PF4 (ADC4/TCK)

PF5

(ADC5/TMS)

PF6

(ADC6/TDO)

GND VCC

PF7 (ADC7/TDI)

PA0

(AD0)

PA1

(AD1)

PA2

(AD2)

(OC0B) PG5

(RXD0/PCINT8/PDI) PE0

(TXD0/PDO) PE1

(XCK0/AIN0) PE2

(OC3A/AIN1) PE3

(OC3B/INT4) PE4

(OC3C/INT5) PE5

(T3/INT6) PE6

(ICP3/CLKO/INT7) PE7

(SS/PCINT0) PB0

(SCK/ PCINT1)

PB1

(MOSI/ PCINT2)

PB2

(MISO/ PCINT3)

PB3

(OC2A/ PCINT4)

PB4

(OC1A/PCINT5) PB5

(OC1B/PCINT6) PB6

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

ATmega1281/2561

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

RESET

VCC

GND XTAL2

XTAL1

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

PA3

(AD3)

PA4

(AD4)

PA5

(AD5)

PA6

(AD6)

PA7

(AD7)

PG2

(ALE)

PC7

(A15)

PC6

(A14)

PC5

(A13)

PC4

(A12)

PC3

(A11)

PC2

(A10)

PC1 (A9)

PC0 (A8)

PG1

(RD)

PG0

(WR)

(OC0A/OC1C/PCINT7) PB7

(TOSC2) PG3

(TOSC1) PG4

(SCL/INT0) PD0 (TXD1/INT3) PD3

(ICP1) PD4

(RXD1/INT2) PD2

(SDA/INT1) PD1

(XCK1) PD5

(T1) PD6

(T0) PD7

Note:

该QFN / MLF封装下大中心焊盘是由金属制成,内部

连接到GND.应当焊接或粘接到所述电路板,以防护证良好机械

CAL稳定.如果中心焊盘悬空时,包可能放松从

电路板.

免责声明

免责声明

本数据手册典型值是基于模拟使用相同工艺技术生产AVR微控制器和表征.起码

和最大值将是可利用设备,其特征在于后.

2549BS–AVR–05/05

3

�

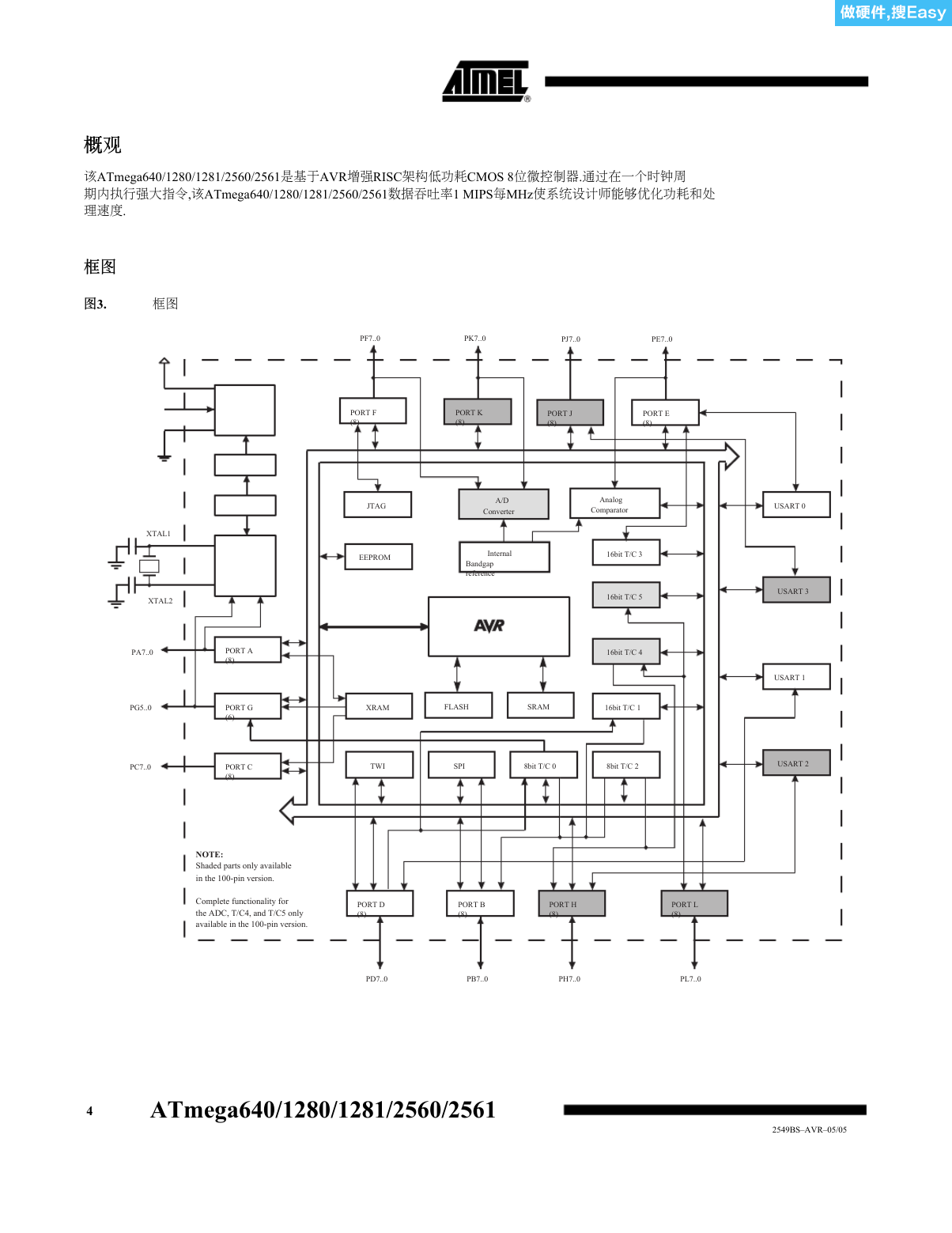

概观概观

该ATmega640/1280/1281/2560/2561是基于AVR增强RISC架构低功耗CMOS 8位微控制器.通过在一个时钟周

期内执行强大指令,该ATmega640/1280/1281/2560/2561数据吞吐率1 MIPS每MHz使系统设计师能够优化功耗和处

理速度.

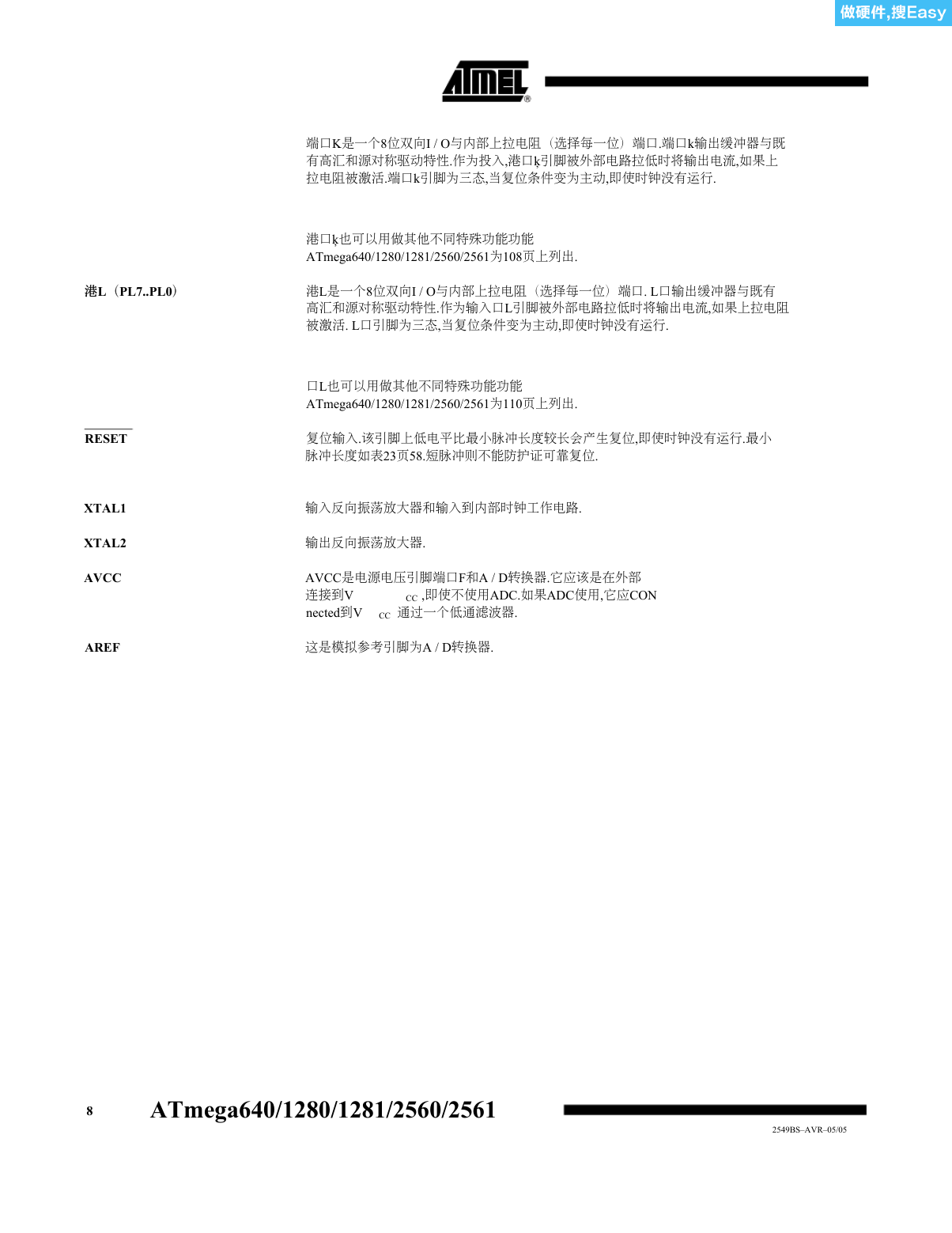

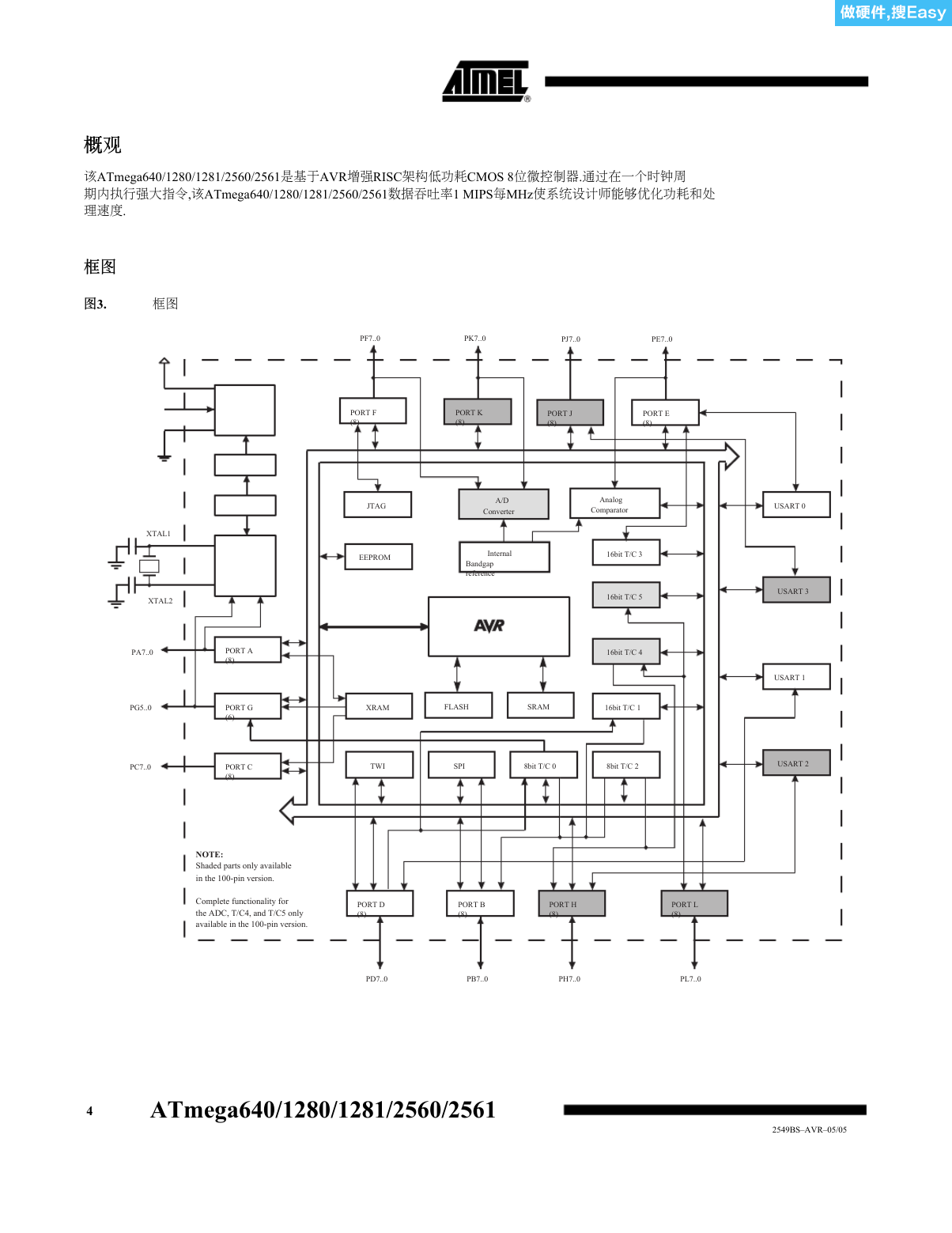

框图框图

图图3.

框图

XTAL1

XTAL2

PA7..0

PG5..0

PC7..0

PORT A

(8)

PORT G

(6)

PORT C

(8)

PF7..0

PK7..0

PJ7..0

PE7..0

PORT F

(8)

PORT K

(8)

PORT J

(8)

PORT E

(8)

JTAG

EEPROM

A/D

Converter

Analog

Comparator

Internal

Bandgap

reference

16bit T/C 3

16bit T/C 5

16bit T/C 4

XRAM

FLASH

SRAM

16bit T/C 1

USART 0

USART 3

USART 1

TWI

SPI

8bit T/C 0

8bit T/C 2

USART 2

NOTE:

Shaded parts only available

in the 100-pin version.

Complete functionality for

the ADC, T/C4, and T/C5 only

available in the 100-pin version.

PORT D

(8)

PORT B

(8)

PORT H

(8)

PORT L

(8)

PD7..0

PB7..0

PH7..0

PL7..0

4

ATmega640/1280/1281/2560/2561

2549BS–AVR–05/05

�

ATmega640/1280/1281/2560/2561

AVR内核具有丰富指令集和32个通用工作寄存器.

所有寄存器都直接连接到算术逻辑单元(ALU),允许两个独立寄存器中在一个时钟周

期一条指令来访问.这种结构大大提高代码效率,同时实现最高至10倍,比传统CISC微

控制器更快.

断或硬件复位.于

该ATmega640/1280/1281/2560/2561提供以下功能:64K / 128K / 256K

对系统内可编程闪存,具有同时读 - 写能力,4K字节字节

EEPROM,8K字节SRAM,54/86通用I / O口线,32个通用与工作

ing寄存器,实时计数器(RTC),六灵活定时器/计数器具有比较

模式和PWM,4个USART,一个面向字节2线串行接口,16通道,10

位ADC与可编程增益可编程可选差分输入级

看门狗定时器具有片内振荡器,一个SPI串行端口,IEEE标准. 1149.1兼容

JTAG测试接口,也可用于访问片上调试系统及编程

明和六个软件选择省电模式.空闲模式时CPU停止工作

而SRAM,定时器/计数器,SPI端口以及中断系统继续

运行.掉电模式,防护存登记内容,但冻结振荡器

器,禁用所有其他芯片功能,直到下一个中

省电模式下,异步定时器继续运行,允许用户main-

覃一个时间基准,而该设备其他部分正在睡觉. ADC噪声抑制

模式下CPU停止工作,并且除异步定时器和ADC所有I / O模块,到最小值,以

imize ADC转换时开关噪声.在待机模式下,水晶/谐振器

振荡器运行时,器件其他部分正在睡觉.这允许非常快速启动

加上低功耗.在扩展待机模式下,主

振荡器和异步定时器继续运行.

该设备是采用Atmel高密度非易失性存储器技术生产.

片内ISP Flash允许程序存储器在系统重新编程

通过一个SPI串行接口,一个传统非易失性存储器编程,或

通过在AVR内核上运行片内引导程序.引导程序可以使用任何

接口下载应用程序在应用程序闪存.柔软-

洁具引导Flash将继续运行,而应用Flash部分

更新,提供真正同时读 - 写操作.通过将8位RISC CPU

与系统自编程闪存梅布尔在单片CH IP,爱特梅尔

ATmega640/1280/1281/2560/2561是一个功能强大单片机,

具有成本效益解决方案许多嵌入式控制应用.

该ATmega640/1280/1281/2560/2561 AVR具有一整套编程与系统开发工具,包

括:C语言编译器,宏汇编,程序调试器/仿真器,仿真器及评估板.

它提供高度灵活和

2549BS–AVR–05/05

5

�

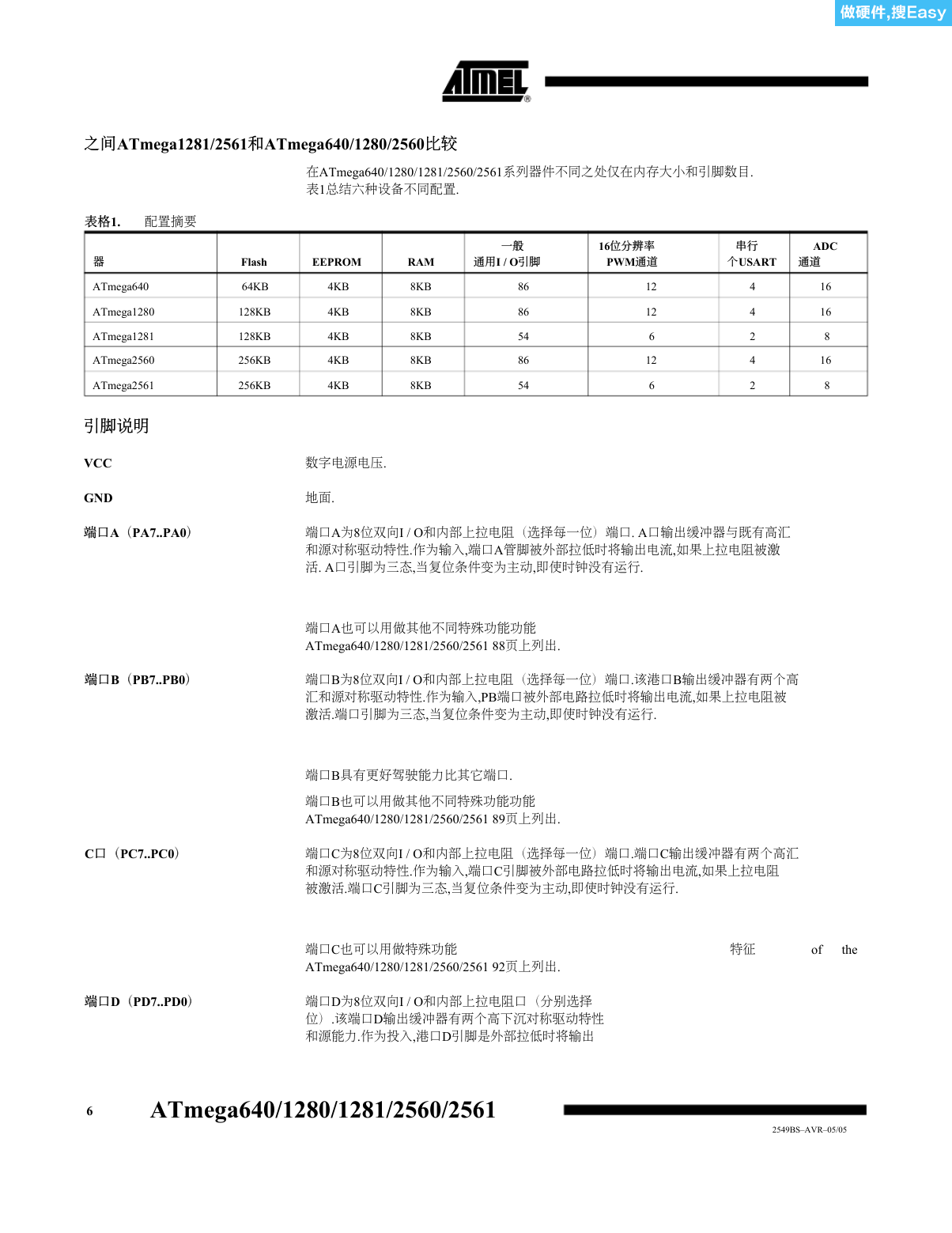

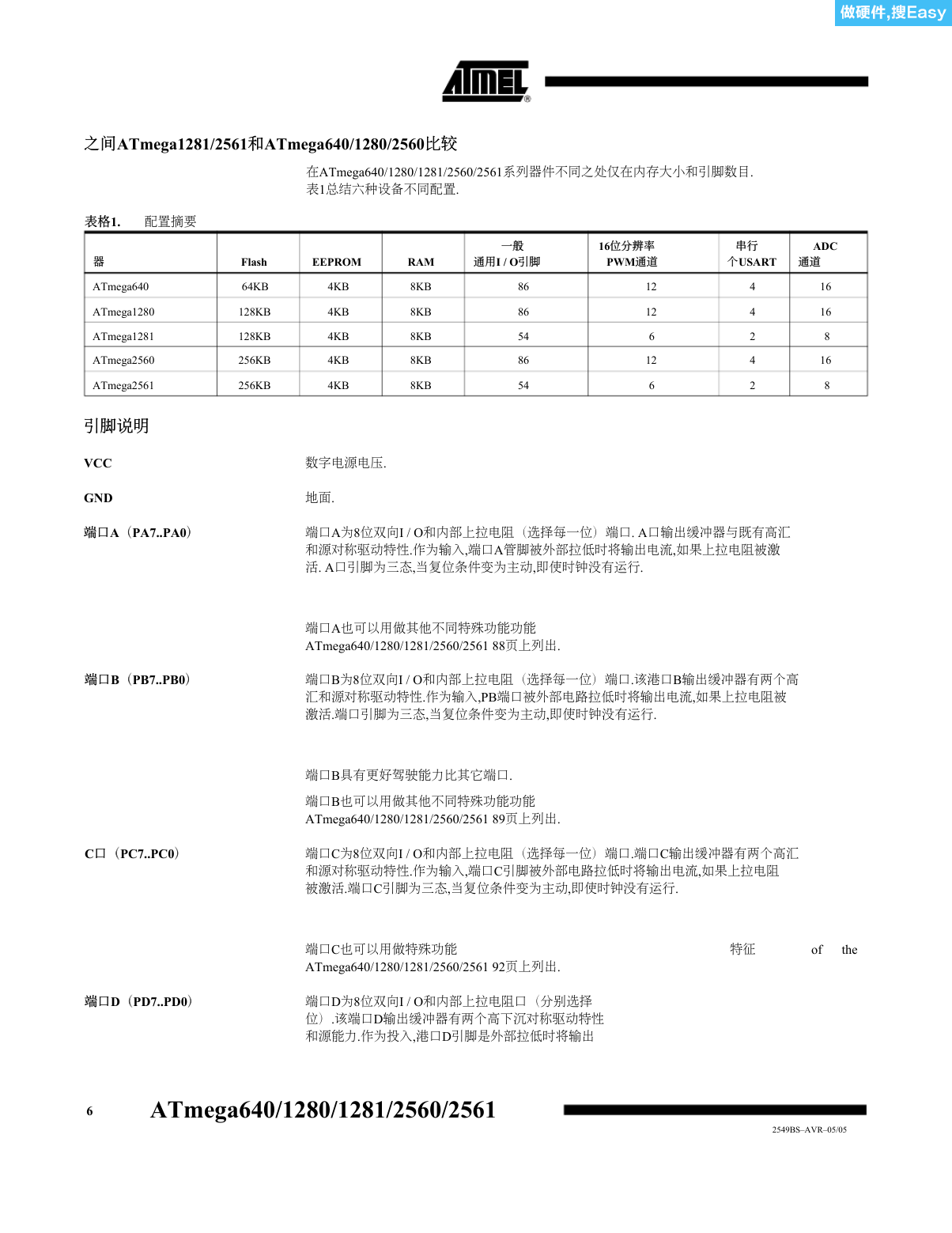

之间之间ATmega1281/2561和和ATmega640/1280/2560比较比较

在ATmega640/1280/1281/2560/2561系列器件不同之处仅在内存大小和引脚数目.

表1总结六种设备不同配置.

表格表格1. 配置摘要

器器

ATmega640

ATmega1280

ATmega1281

ATmega2560

ATmega2561

引脚说明

引脚说明

VCC

GND

Flash

64KB

128KB

128KB

256KB

256KB

EEPROM

RAM

一般一般

通用通用I / O引脚引脚

16位分辨率

位分辨率

PWM通道通道

串行串行

个个USART

ADC

通道通道

4KB

4KB

4KB

4KB

4KB

8KB

8KB

8KB

8KB

8KB

86

86

54

86

54

12

12

6

12

6

4

4

2

4

2

16

16

8

16

8

数字电源电压.

地面.

端口端口A((PA7..PA0))

端口A为8位双向I / O和内部上拉电阻(选择每一位)端口. A口输出缓冲器与既有高汇

和源对称驱动特性.作为输入,端口A管脚被外部拉低时将输出电流,如果上拉电阻被激

活. A口引脚为三态,当复位条件变为主动,即使时钟没有运行.

端口A也可以用做其他不同特殊功能功能

ATmega640/1280/1281/2560/2561 88页上列出.

端口端口B((PB7..PB0))

端口B为8位双向I / O和内部上拉电阻(选择每一位)端口.该港口B输出缓冲器有两个高

汇和源对称驱动特性.作为输入,PB端口被外部电路拉低时将输出电流,如果上拉电阻被

激活.端口引脚为三态,当复位条件变为主动,即使时钟没有运行.

端口B具有更好驾驶能力比其它端口.

端口B也可以用做其他不同特殊功能功能

ATmega640/1280/1281/2560/2561 89页上列出.

C口(口(PC7..PC0))

端口C为8位双向I / O和内部上拉电阻(选择每一位)端口.端口C输出缓冲器有两个高汇

和源对称驱动特性.作为输入,端口C引脚被外部电路拉低时将输出电流,如果上拉电阻

被激活.端口C引脚为三态,当复位条件变为主动,即使时钟没有运行.

端口端口D((PD7..PD0))

端口C也可以用做特殊功能

ATmega640/1280/1281/2560/2561 92页上列出.

端口D为8位双向I / O和内部上拉电阻口(分别选择

位).该端口D输出缓冲器有两个高下沉对称驱动特性

和源能力.作为投入,港口D引脚是外部拉低时将输出

特征

of

the

6

ATmega640/1280/1281/2560/2561

2549BS–AVR–05/05

�

ATmega640/1280/1281/2560/2561

当前,如果上拉电阻被激活.该端口D引脚为三态,当复位条件变为主动,即使时钟没有

运行.

端口D也可以用做其他不同特殊功能功能

ATmega640/1280/1281/2560/2561 94页上列出.

端口端口E((PE7..PE0))

端口E为8位双向I / O和内部上拉电阻(选择每一位)端口.该端口E输出缓冲器与既有高

汇和源对称驱动特性.作为输入,则端口被外部电路拉低时将输出电流,如果上拉电阻

被激活.该端口E引脚为三态,当复位条件变为主动,即使时钟没有运行.

端口端口F((PF7..PF0))

端口E也可以用做其他不同特殊功能功能

ATmega640/1280/1281/2560/2561 96页上列出.

端口F作为模拟输入A / D转换器.

端口F也可以作为8位双向I / O口,如果不使用A / D转换器.

端口引脚内部上拉电阻(选择每一位).该端口F输出缓冲器与既有高汇和源对称驱动特

性.

作为输入,则端口被外部电路拉低时将输出电流,如果上拉电阻被激活.口引脚为三态

,当复位条件变为主动,即使时钟没有运行.如果JTAG接口使能,引脚PF7(TDI),

PF5(TMS)和PF4(TCK)上拉电阻会即使复位时被激活.

端口F也可以作为JTAG接口功能.

端口端口G((PG5..PG0))

端口G是一个具有内部上拉电阻(选择每一位)6位I / O端口.该端口G输出缓冲器与既有

高汇和源对称驱动特性.作为输入,则端口被外部电路拉低时将输出电流,如果上

拉电阻被激活.该端口G引脚为三态,当复位条件变为主动,即使时钟没有运行.

端口G也可以用做其他不同特殊功能功能

ATmega640/1280/1281/2560/2561为102页上列出.

端口端口H((PH7..PH0))

端口H是一个8位双向I / O与内部上拉电阻(选择每一位)端口.该端口H输出缓冲器与

既有高汇和源对称驱动特性.作为输入,端口H引脚被外部电路拉低时将输出电流,如果

上拉电阻被激活.该端口H引脚为三态,当复位条件变为主动,即使时钟没有运行.

端口H也可以用做其他不同特殊功能功能

ATmega640/1280/1281/2560/2561如第104页上列出.

端口端口J((PJ7..PJ0))

端口J是一个8位双向I / O与内部上拉电阻(选择每一位)端口.该端口J输出缓冲器与

既有高汇和源对称驱动特性.作为输入,端口J引脚被外部电路拉低时将输出电流,如果

上拉电阻被激活.该端口J引脚为三态,当复位条件变为主动,即使时钟没有运行.

端口J也可以用做其他不同特殊功能功能

ATmega640/1280/1281/2560/2561为106页上列出.

端口端口K((PK7..PK0))

港口ķ作为模拟输入A / D转换器.

2549BS–AVR–05/05

7

�

端口K是一个8位双向I / O与内部上拉电阻(选择每一位)端口.端口k输出缓冲器与既

有高汇和源对称驱动特性.作为投入,港口ķ引脚被外部电路拉低时将输出电流,如果上

拉电阻被激活.端口k引脚为三态,当复位条件变为主动,即使时钟没有运行.

港口ķ也可以用做其他不同特殊功能功能

ATmega640/1280/1281/2560/2561为108页上列出.

港港L((PL7..PL0))

港L是一个8位双向I / O与内部上拉电阻(选择每一位)端口. L口输出缓冲器与既有

高汇和源对称驱动特性.作为输入口L引脚被外部电路拉低时将输出电流,如果上拉电阻

被激活. L口引脚为三态,当复位条件变为主动,即使时钟没有运行.

RESET

XTAL1

XTAL2

AVCC

AREF

口L也可以用做其他不同特殊功能功能

ATmega640/1280/1281/2560/2561为110页上列出.

复位输入.该引脚上低电平比最小脉冲长度较长会产生复位,即使时钟没有运行.最小

脉冲长度如表23页58.短脉冲则不能防护证可靠复位.

输入反向振荡放大器和输入到内部时钟工作电路.

输出反向振荡放大器.

AVCC是电源电压引脚端口F和A / D转换器.它应该是在外部

连接到V

nected到V CC 通过一个低通滤波器.

CC ,即使不使用ADC.如果ADC使用,它应CON

这是模拟参考引脚为A / D转换器.

8

ATmega640/1280/1281/2560/2561

2549BS–AVR–05/05

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc