大疆 FPGA 开发工程师笔试 2018-7-6

一共是 75 分钟的时间,从 19:30 到 20:45,题型如下:(可能分值会有错误,实在记不清了)

20 个单选: 40 分 10 个多选: 20 分 5个填空题:15 分 5 个简单题:25 分

• FPGA 的时序分析与时序约束

• FPGA 内部资源

• FPGA 语法

• 同步异步电路分析

• 可综合的 Verilog 语句

• 状态机的设计

• Verilog 代码的编写

• FIFO 深度计算

• 各类存储器之间的区别

• 定点数量化

• 数电门电路、多路选择器等的灵活使用

• 还涉及到 CPU 的部分题目,例如 RISC 指令集 5 级流水线、CPU 启动过程等。

• 还记得两个:代码覆盖率和正则表达式里的字符匹配。

�

华为海思

• DRAM 相关的问题,DRAM 如何实现存储读写操作之类的FPGA 内部资源

• 如何 refresh;

• FIFO 的一些基本问题;

• Verilog 的基本问题;

• 什么是同步电路什么是异步电路,讲一下 fifo 的原理、作用、结构,

• 跨时钟域的传输场写异步 fifo 的代码。

• random()函数,不知道他的函数功能,如何去测试它

�

• 1、集成电路设计前端流程及工具

• 2、FPGA 和 ASIC 的概念,他们的区别

• 3、LATCH 和 DFF 的概念和区别

• 4、用 DFF 实现二分频、

• 5、用 VERILOG 或 VHDL 写一段代码,实现消除一个 glitch

• 6、给一个表达式 f=xxxx+xxxx+xxxxx+xxxx 用最少数量的与非门实现(实际

• 上就是化简)

• 7、用 VERILOG 或 VHDL 写一段代码,实现 10 进制计数器、

• 8、给出一个门级的图,又给了各个门的传输延时,问关键路径是什么,还问给出输入,使得输出依

赖于关键路径、

• 9、A,B,C,D,E 进行投票,多数服从少数,输出是 F(也就是如果 A,B,C,D,E中 1 的个数比 0 多,那么 F 输

出为 1,否则 F 为 0),用与非门实现,输入数目没有限制。

�

2012 联发科数字 IC 设计笔试题

• 请解释 Latch 与 flip‐flop 的区别;

• 请解释 setup time 和 hold time 之间的区别

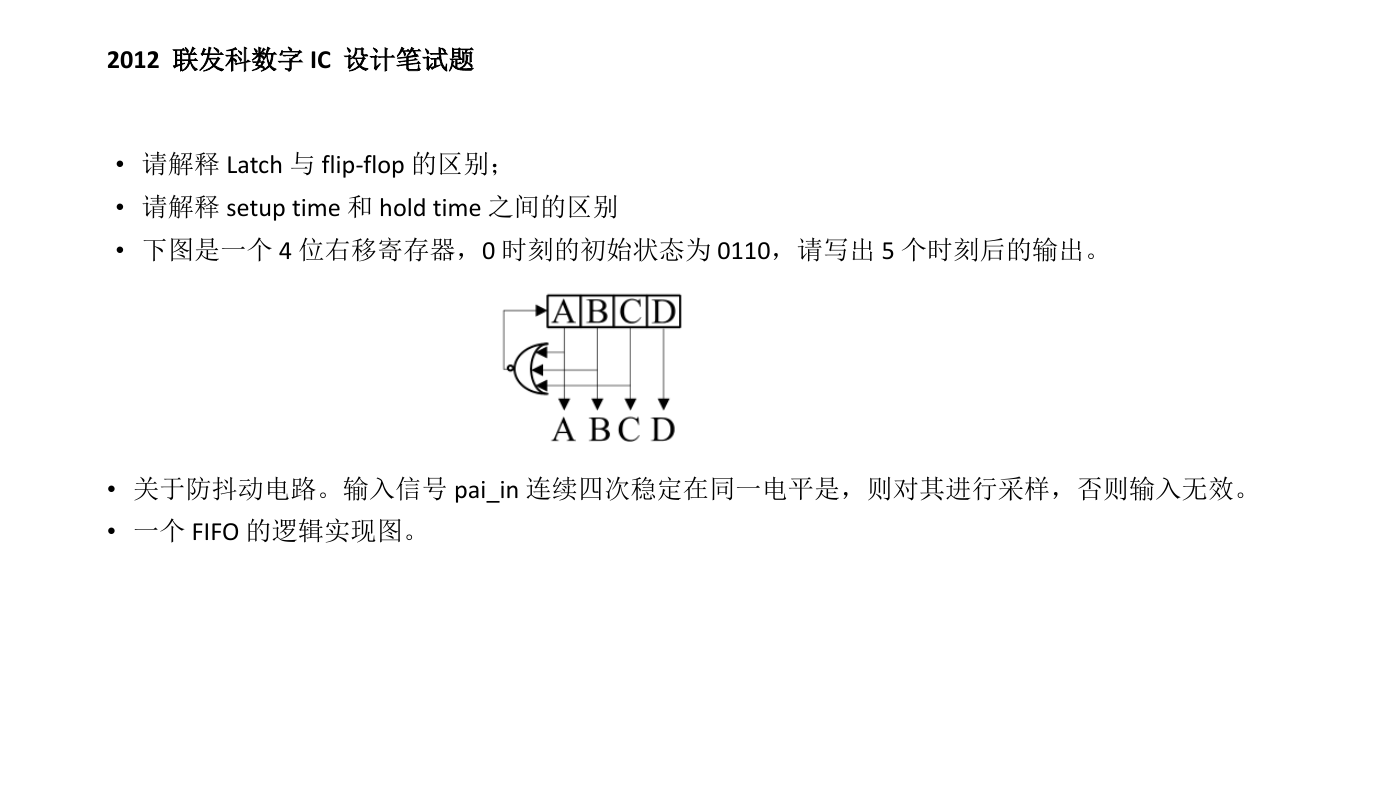

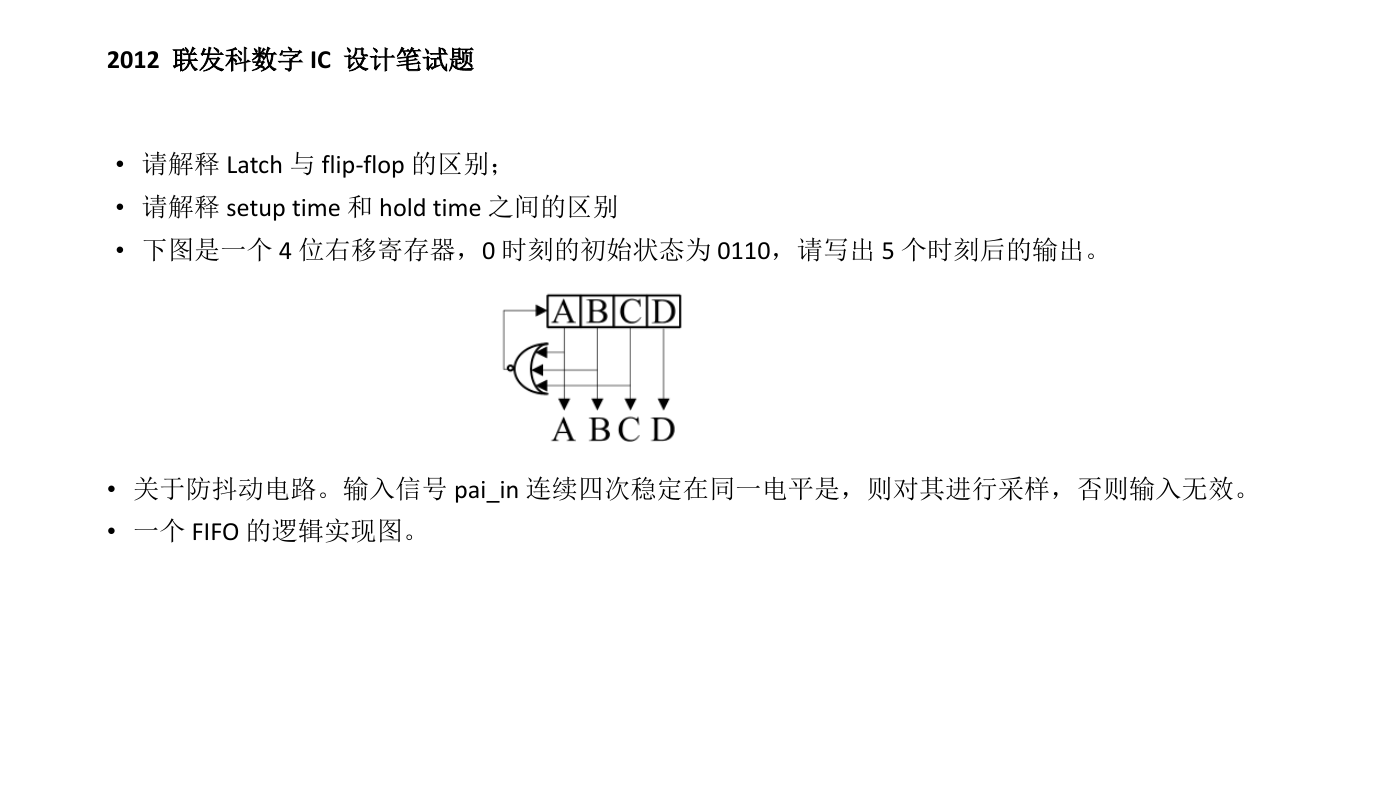

• 下图是一个 4 位右移寄存器,0 时刻的初始状态为 0110,请写出 5 个时刻后的输出。

• 关于防抖动电路。输入信号 pai_in 连续四次稳定在同一电平是,则对其进行采样,否则输入无效。

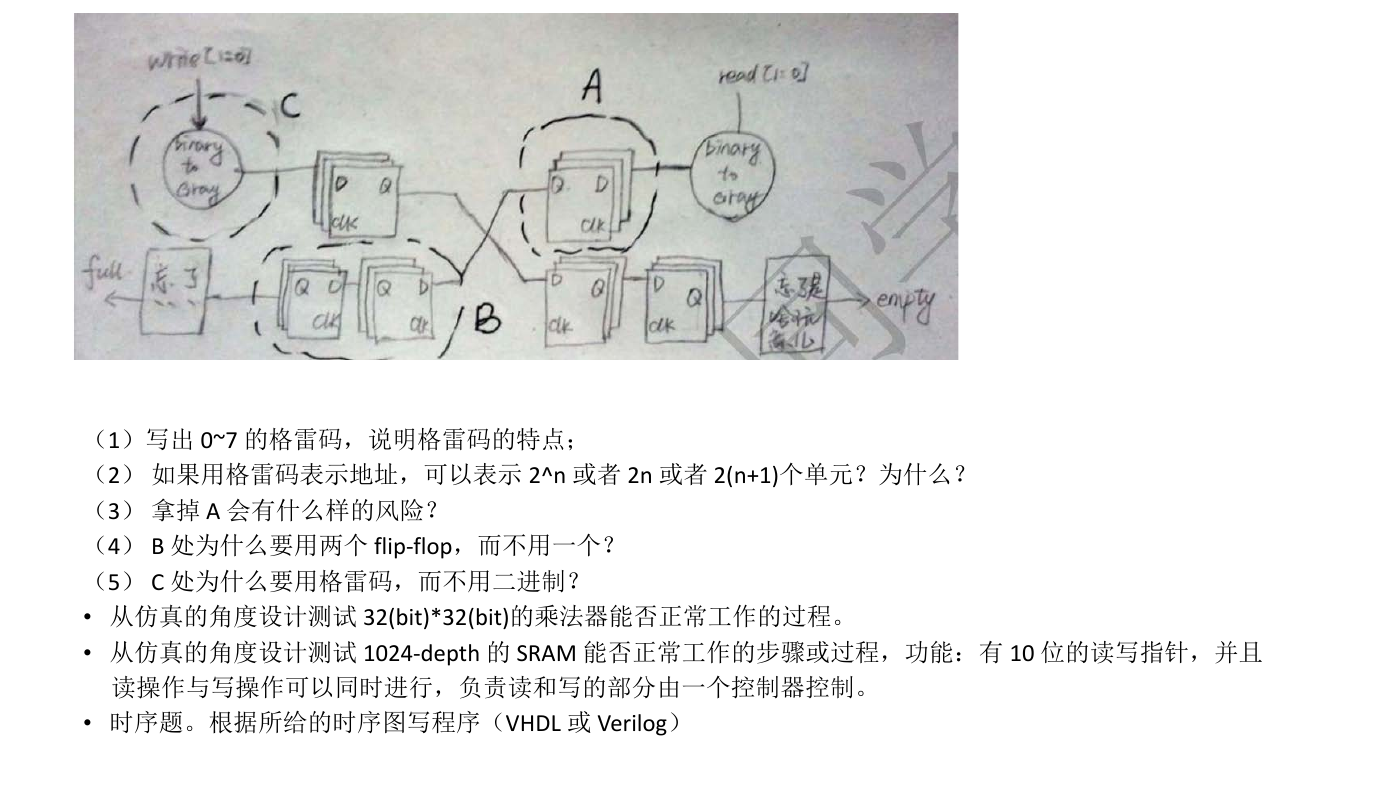

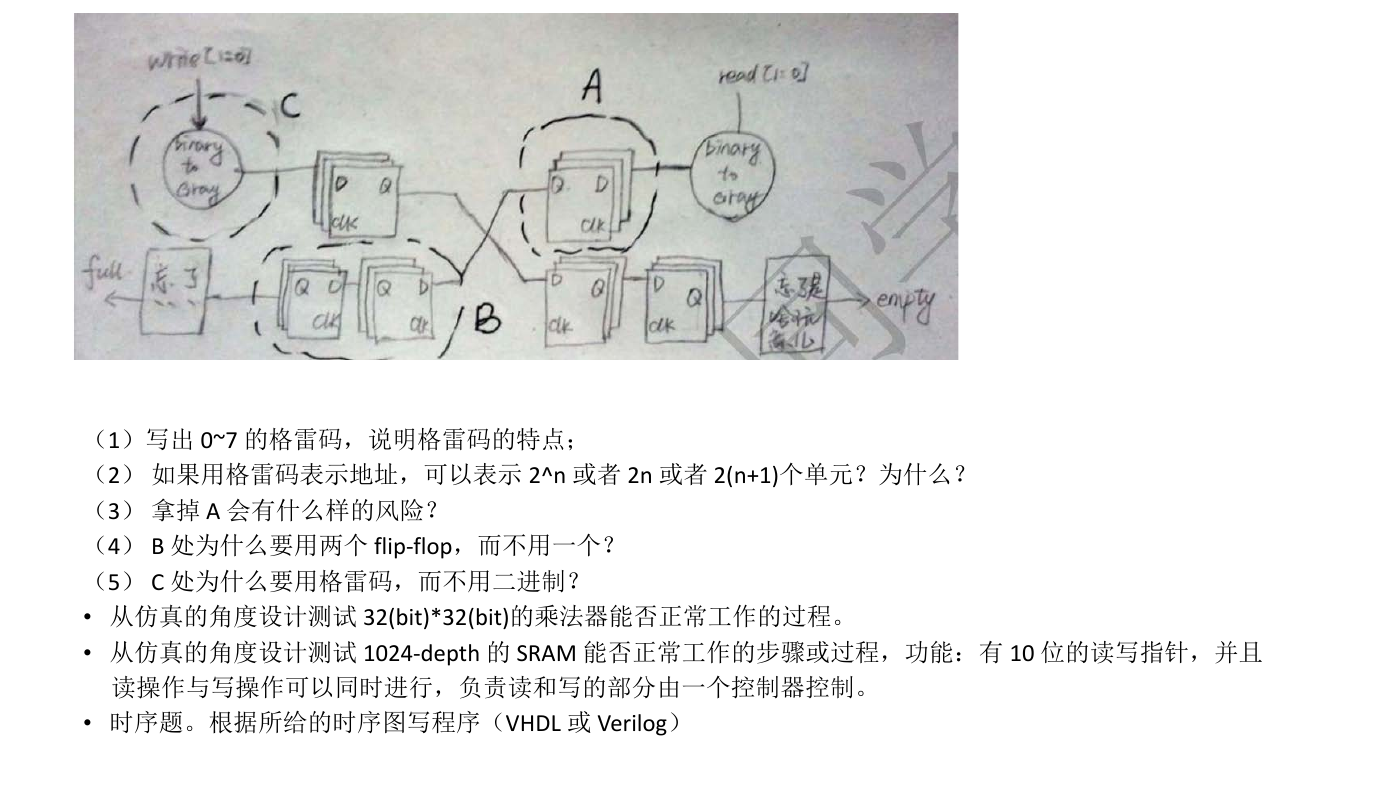

• 一个 FIFO 的逻辑实现图。

�

(1)写出 0~7 的格雷码,说明格雷码的特点;

(2) 如果用格雷码表示地址,可以表示 2^n 或者 2n 或者 2(n+1)个单元?为什么?

(3) 拿掉 A 会有什么样的风险?

(4) B 处为什么要用两个 flip‐flop,而不用一个?

(5) C 处为什么要用格雷码,而不用二进制?

• 从仿真的角度设计测试 32(bit)*32(bit)的乘法器能否正常工作的过程。

• 从仿真的角度设计测试 1024‐depth 的 SRAM 能否正常工作的步骤或过程,功能:有 10 位的读写指针,并且

读操作与写操作可以同时进行,负责读和写的部分由一个控制器控制。

• 时序题。根据所给的时序图写程序(VHDL 或 Verilog)

�

芯原的笔试题

• 用 IV 曲线说明 PMOS 的各种工作方式

•

• 什么是 DFT?如何在模拟设计中运用

latch‐up 概念及如何避免

DFT 是 desigh for test,就是在设计的时候就添加了一些用来测试的电路,这样通过测试就可以推算出失

效的原因和地址

模拟电路中:

• 各个 stage 间关键点留 pad 准备扎针?

• PAD 是要用面积的...其实只要 analog 只要你想好了要测什么东西,事先设计好方案和数字 DFT 是一样

的

• 阶越响应的运算 ,画波特图

• ESD 的问题

• 天线效应

�

联发科的集成电路 IC 设计

• 基本的 IC 设计、数字逻辑(FPGA)的基础知识

• 高斯滤波器设计原理,积分模块设计具体细节,位宽溢出考虑,然后问验证的情况,验证平台怎么搭

的,model 怎么写的

• 通信的知识,QPSK,星座图,冲击响应求群延迟,用乘法器画出设计框图

• FIR 滤波器的电路实现(时域乘积对应频域卷积,画出触发器延迟和加法器)

�

• IC 设计的流程与用到的软件

• OCV 的作用与在 STA 中怎样考虑

• 形式验证的作用与方法

• 画出一个门禁系统的流程图

要求:a. 输入两位数(楼层号和房间号),#号键确认,发送响门铃信号。

b. 输入*号键后输入两位数的密码,#键确认,打开门。

c. 在数字输入时,输入*键取消之前的所有输入

• 画了一个异步信号防抖动电路的网表,就是一些寄存器,多路选择器,之内的东西,功能是同步异步

输入,并判断输入信号是否维持 4 个时钟周期以上,大于四个周期才输入。要求写出 RTL 级代码;给

出了一些时序参数,要求计算电路工作的最大频率。

• 一个 FIFO 的题,

• 一个 DMA 的题

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc