Chrontel

CH7025/CH7026

Datasheet

CH7025/CH7026 TV/VGA Encoder

the

and

video

signals

standards

GENERAL DESCRIPTION

The CH7025/CH7026 is a device targeting handheld

and similar consumer systems which accept digital

input signal. CH7025/CH7026 encodes and transmits

data through 10-bit DACs. The device is able to

encode

generate

synchronization signals SDTV format for NTSC and

PAL

for

480p,576p,720p and 1080i. Analog RGB output and

composite SYNC signal are also supported. The

device accepts different data formats including RGB

and YCbCr (e.g. RGB565, RGB666, RGB888,

ITU656 like YCbCr, etc.).Both interlaced and non-

interlaced input data formats are supported. 16Mbit

SDRAM

in package. Frame rate

conversion, Image rotation, zooming and scaling, are

supported.

and HDTV

is embedded

format

in

or

FEATURES

• Support multiple output formats. Such as SDTV format

(NTSC and PAL), HDTV format for 480p,576p,720p and

1080i, analog RGB output for VGA. Sync signals can be

provided

composite manner

(Programmable composite sync generation).

separated

• Three on-chip 10-bit high speed DACs providing flexible

output capabilities. Such as single, double or triple CVBS

outputs, YPbPr output, RGB output and simultaneous

CVBS and S-video outputs.

Internal embedded 16Mbits SDRAM is used as frame

buffer. Supporting for frame rate conversion. 90/180/270

degree image rotation and vertical or horizontal flip

functions are supported.

•

• Programmable

24-bit/18-bit/16-bit/15-bit/12-bit/8-bit

digital input interface supports various RGB (RGB888,

RGB666, RGB565 and etc), YCbCr (4:4:4 YCbCr,

ITU656) and 2x or 3x multiplexed input. CPU/Memory

interface are supported.

• Support for flexible input resolution is up to 800x800 and

1024x680. 320x240, 640x480, 960x720 are support.

• Bypass mode is supported.

• Flexible up and down scaling engine is embedded

including de-flickering capability. Text enhancement is

supported.

• Pixel by pixel brightness, contrast, hue and saturation

adjustment for each kind of output are supported. For

RGB output, only brightness and contrast adjustment are

supported.

• Pixel by pixel horizontal position adjustment and line by

line vertical position adjustment are supported.

• Fully programmable through serial port. IO and SPC/SPD

voltage supported is from 1.2V to 3.3V.

• TV/Monitor connection detect capability.

• Programmable power management. DAC can be switched

off based on detection result (Driver support is required).

• Flexible pixel clock frequency from graphics controller is

supported (2.3MHz –120MHz). Flexible input clock from

crystal or oscillator is supported (2.3MHz – 64MHz).

• MacrovisionTM 7.1.L1 for SDTV is supported in CH7025

(CH7026 is Non-Macrovision part.). MacrovisionTM copy

protection support for progressive scan TV (480p, 576p

CH7025 only).

• CGMS-A support for SDTV and HDTV (CH7025 only).

• Offered in BGA or QFP package.

Note: the above feature list is subject to change without notice. Please contact Chrontel for more information

and current updates.

201-1000-001 Rev. 1.23,

03/31/2010

1

�

CHRONTEL

Input

data

format

decoder

CPU

interface

Serial

port

PLL

RGB/YCbCr

CSB

WEB

VSYNC

DIN

SPC

SPD

XI

XO

H,V,DE

2

CH7025/CH7026

SDRAM

MUX

CSC

(YCbCr

to RGB)

Scaler

MUX

CSC

(RGB to

YUV)

HUE

SAT

BRI

CON

VP

HP

TV

formater

MUX

BRI

CON

VP

HP

SYNC

position

adjust

Composite

sync

generation

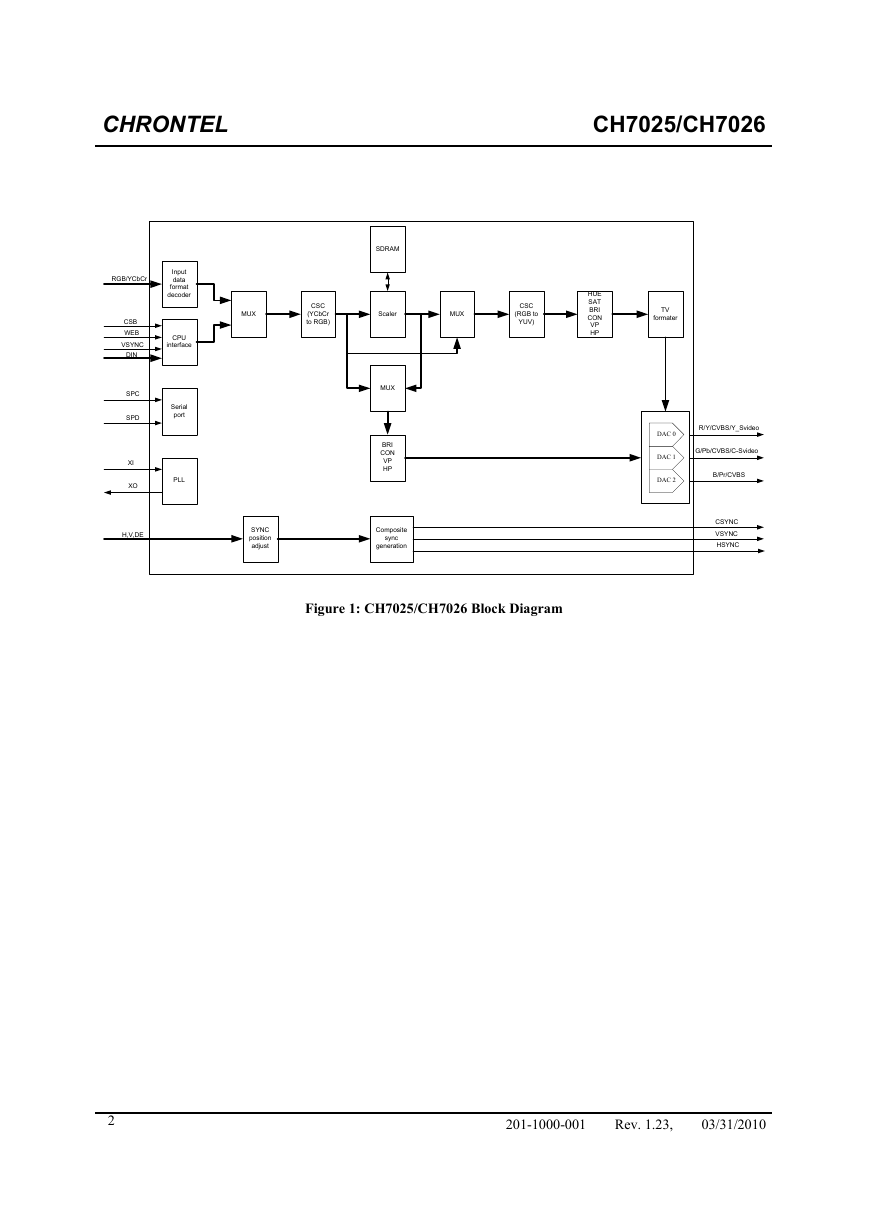

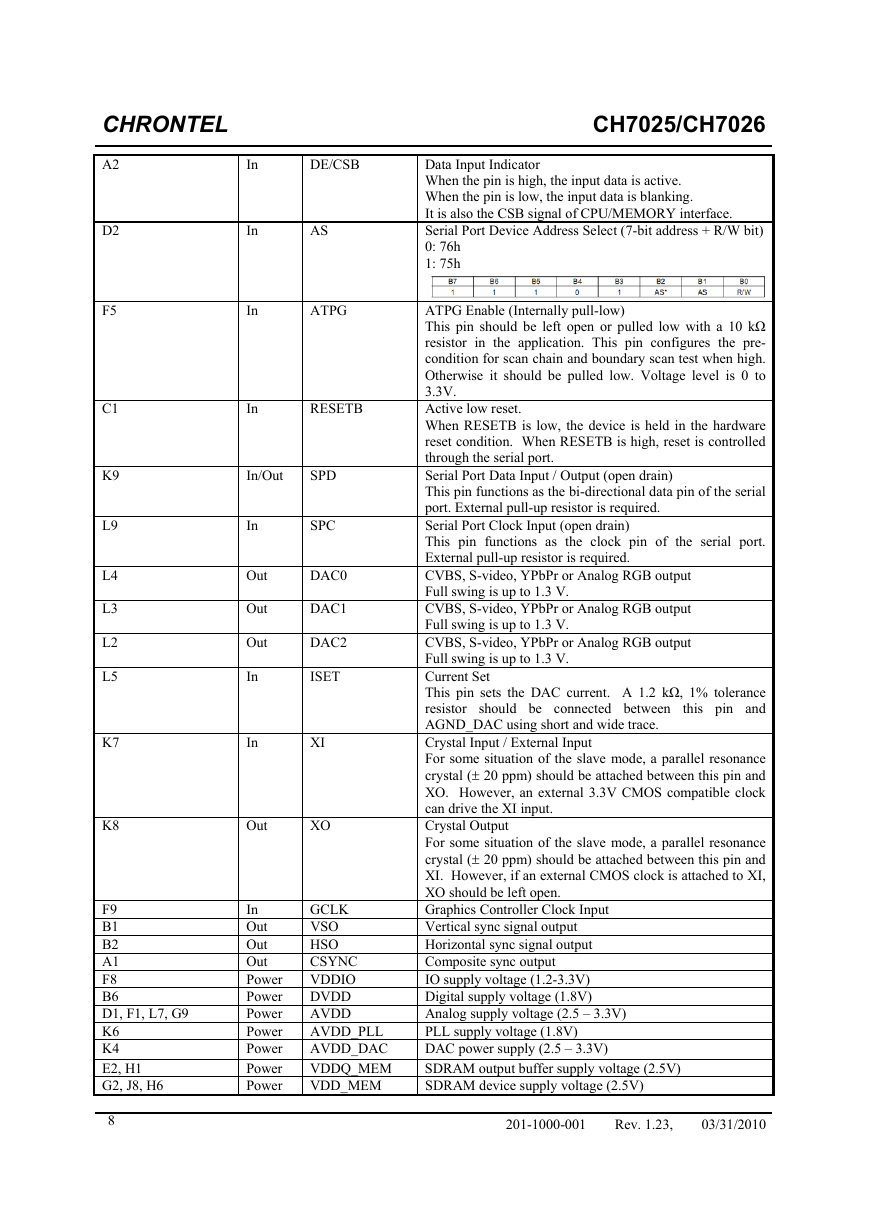

Figure 1: CH7025/CH7026 Block Diagram

DAC 0

DAC 1

DAC 2

R/Y/CVBS/Y_Svideo

G/Pb/CVBS/C-Svideo

B/Pr/CVBS

CSYNC

VSYNC

HSYNC

201-1000-001 Rev. 1.23, 03/31/2010

�

CHRONTEL

CH7025/CH7026

Table of Contents

FEATURES.................................................................................................................................................1

GENERAL DESCRIPTION ..........................................................................................................................1

1.0

1.1

1.2

PIN-OUT......................................................................................................................................6

Package Diagram.......................................................................................................................................6

Pin Description ..........................................................................................................................................7

2.0

2.1

2.2

FUNCTIONAL DESCRIPTION....................................................................................................11

Input Interface .......................................................................................................................................11

Overview..........................................................................................................................................11

Input Clock and Data Timing Diagram............................................................................................11

Input Data Voltage...........................................................................................................................12

Input Data Format............................................................................................................................12

Chip Output ...........................................................................................................................................14

TV Output........................................................................................................................................14

VGA Output.....................................................................................................................................15

Video DAC Output ..........................................................................................................................15

DAC Single/Double Termination ....................................................................................................15

Video DAC Connection Detect .......................................................................................................15

Picture Enhancement .......................................................................................................................15

Color Sub-carrier Generation...........................................................................................................15

ITU-R BT.470 Compliance .............................................................................................................16

Testing Functions and Power Down Mode..........................................................................................16

Test Pattern Select ...........................................................................................................................16

SDRAM Power Down .....................................................................................................................16

Serial Port...............................................................................................................................................16

Introduction......................................................................................................................................16

Electrical Characteristics of the Serial Port........................................................................................17

Transfer Protocol ..............................................................................................................................17

Chrontel Encoder Write Cycle Protocol (R/W* = 0)..........................................................................18

Chrontel Encoder Read Cycle Protocol (R/W* = 1)...........................................................................19

2.1.1

2.1.2

2.1.3

2.1.4

2.2.1

2.2.2

2.2.3

2.2.4

2.2.5

2.2.6

2.2.7

2.2.8

2.3.1

2.3.2

2.4.1

2.4.2

2.4.3

2.4.4

2.4.5

2.3

2.4

3.0

3.1

3.2

3.3

4.0

4.1

4.2

4.3

4.4

4.5

5.0

6.0

REGISTER CONTROL ...............................................................................................................21

Control Registers Index ...........................................................................................................................21

Control Registers Map.............................................................................................................................24

Register Descriptions...............................................................................................................................27

ELECTRICAL SPECIFICATIONS ...............................................................................................55

Absolute Maximum Ratings ....................................................................................................................55

Recommended Operating Conditions ......................................................................................................55

Electrical Characteristics .........................................................................................................................56

Digital Inputs / Outputs............................................................................................................................56

AC Specifications ....................................................................................................................................57

PACKAGE DIMENSIONS ...........................................................................................................58

REVISION HISTORY .................................................................................................................60

201-1000-001 Rev. 1.23,

03/31/2010

3

�

CHRONTEL

CH7025/CH7026

4

201-1000-001 Rev. 1.23, 03/31/2010

�

CHRONTEL

CH7025/CH7026

FIGURES AND TABLES

List of Figures

Figure 1: CH7025/CH7026 Block Diagram ......................................................................................................2

Figure 2: BGA Package (Top View) .................................................................................................................6

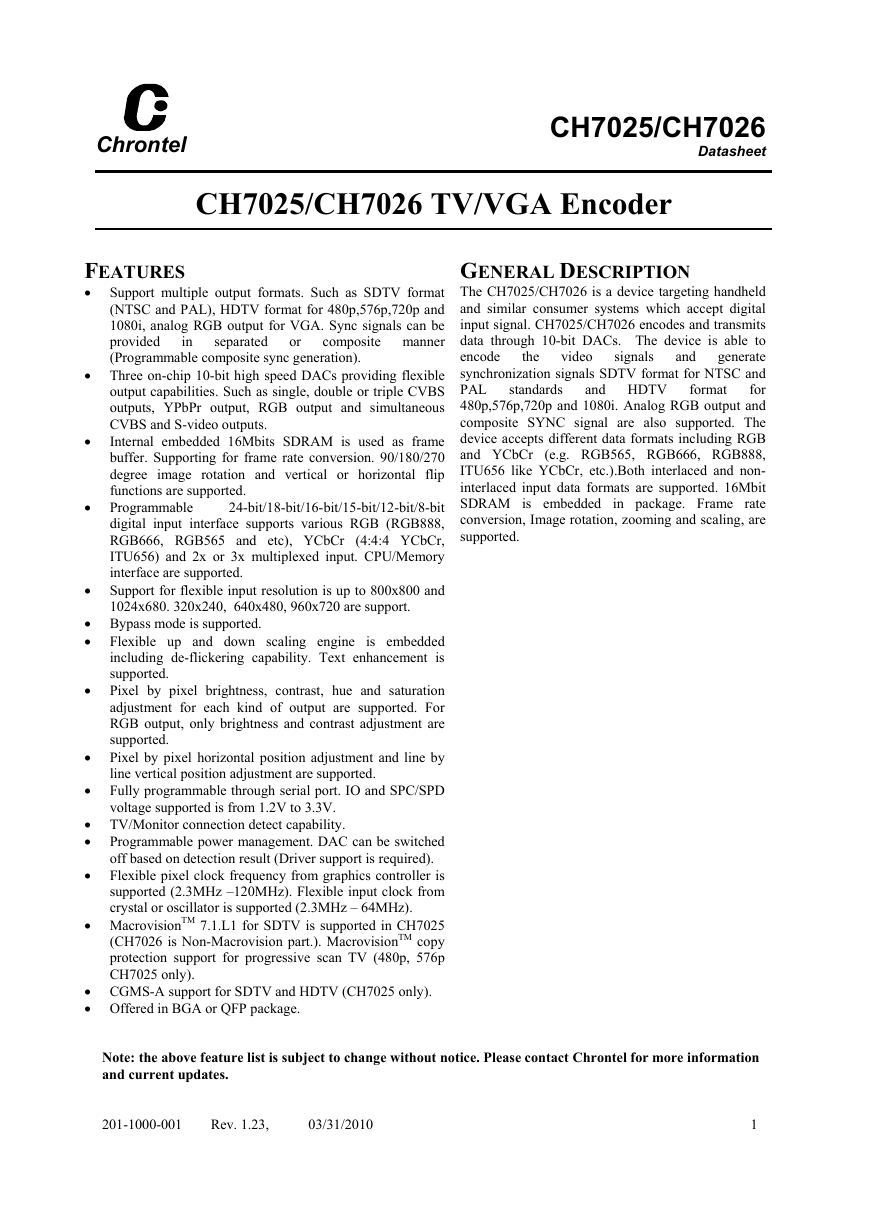

Figure 3: 80 Pin LQFP Package ........................................................................................................................7

Figure 4: Clock and Data Input Timing in 3x Multiplexed Mode ..................................................................11

Figure 5: SDR and DDR Input Data Formats..................................................................................................11

Figure 6: Horizontal Input Timing...................................................................................................................12

Figure 7: Vertical Input Timing.......................................................................................................................12

Figure 8: CPU/MEMORY Interface Timing ...................................................................................................12

Figure 9: The Connection of the Serial Port Interface .....................................................................................17

Figure 10: Acknowledge Protocol ...................................................................................................................19

Figure 11:Single-step Write Cycles (2 cycles) ................................................................................................19

Figure 12: Auto-Increment Write Cycle..........................................................................................................19

Figure 13: Single-step Read Cycles (2 cycles) ................................................................................................20

Figure 14:Auto-increment Read Cycles...........................................................................................................20

Figure 15: 80 Pin TFBGA Package .................................................................................................................58

Figure 16: 80 Pin LQFP Package ....................................................................................................................59

Table 1: Pin Name Description (BGA Package) ...............................................................................................7

Table 2: Pin Name Descriptions (LQFP80 Package).........................................................................................9

Table 3: Input Data Format.............................................................................................................................13

Table 4: Supported SDTV Standards...............................................................................................................14

Table 5: Supported EDTV/HDTV Standards ..................................................................................................14

Table 6: Composite Sync Type........................................................................................................................15

Table 7: Video DAC Configurations for CH7025/CH7026 ............................................................................15

Table 8: Test Pattern Selection ........................................................................................................................16

Table 9: Control Registers Index.....................................................................................................................21

Table 10: Serial Port Register Map..................................................................................................................24

Table 11 : DAC Power Down Control Bits .....................................................................................................28

Table 12: Multiple TV Output Configuration..................................................................................................30

Table 13: DAC Output Swapping Sequence....................................................................................................30

Table 14 : HIGH,SWAP Format......................................................................................................................31

Table 15: SDTV/VGA Output Format ............................................................................................................31

Table 16: Macrovision Level Mode MVMODE[1:0]......................................................................................46

Table 17 : EDTV/HDTV Output Format.........................................................................................................48

Table 18: Attached Display Mapping..............................................................................................................54

List of Tables

201-1000-001 Rev. 1.23,

03/31/2010

5

�

CHRONTEL

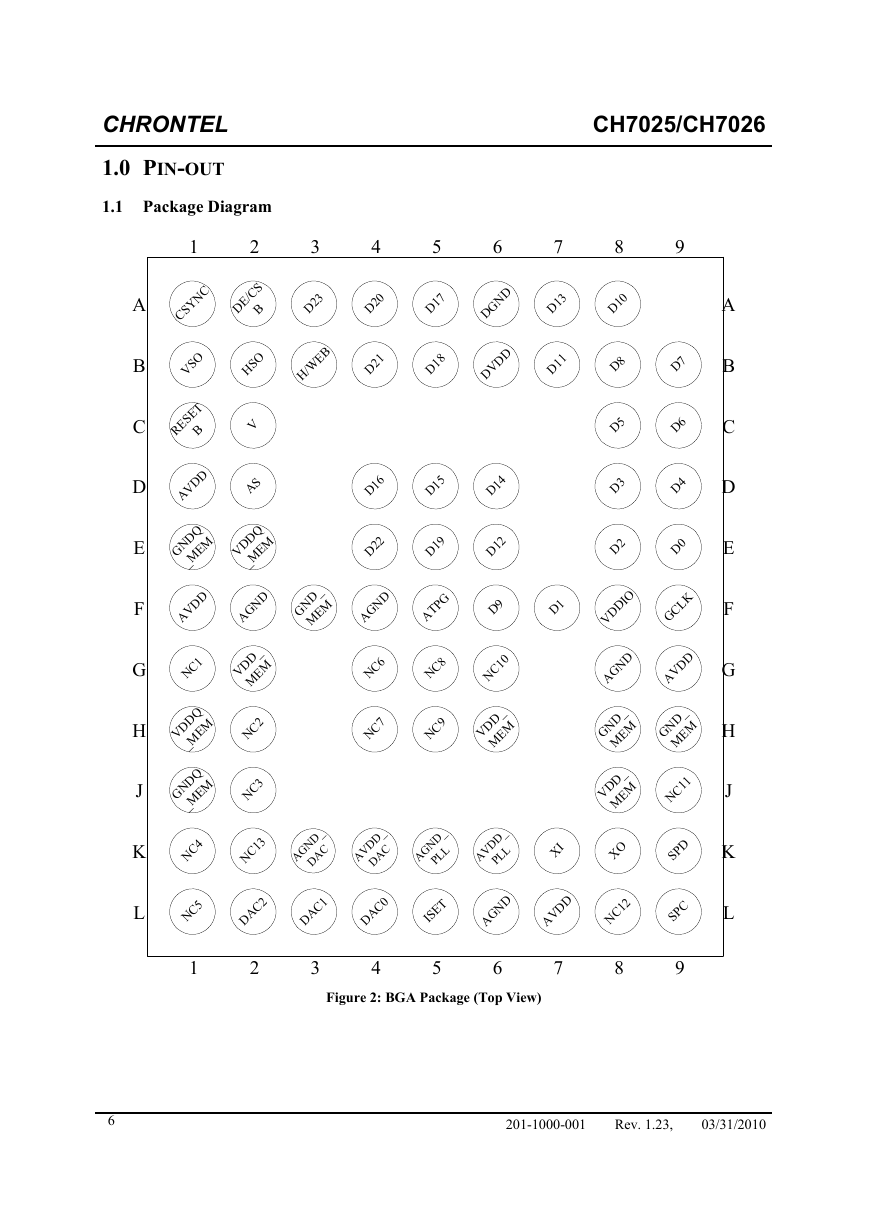

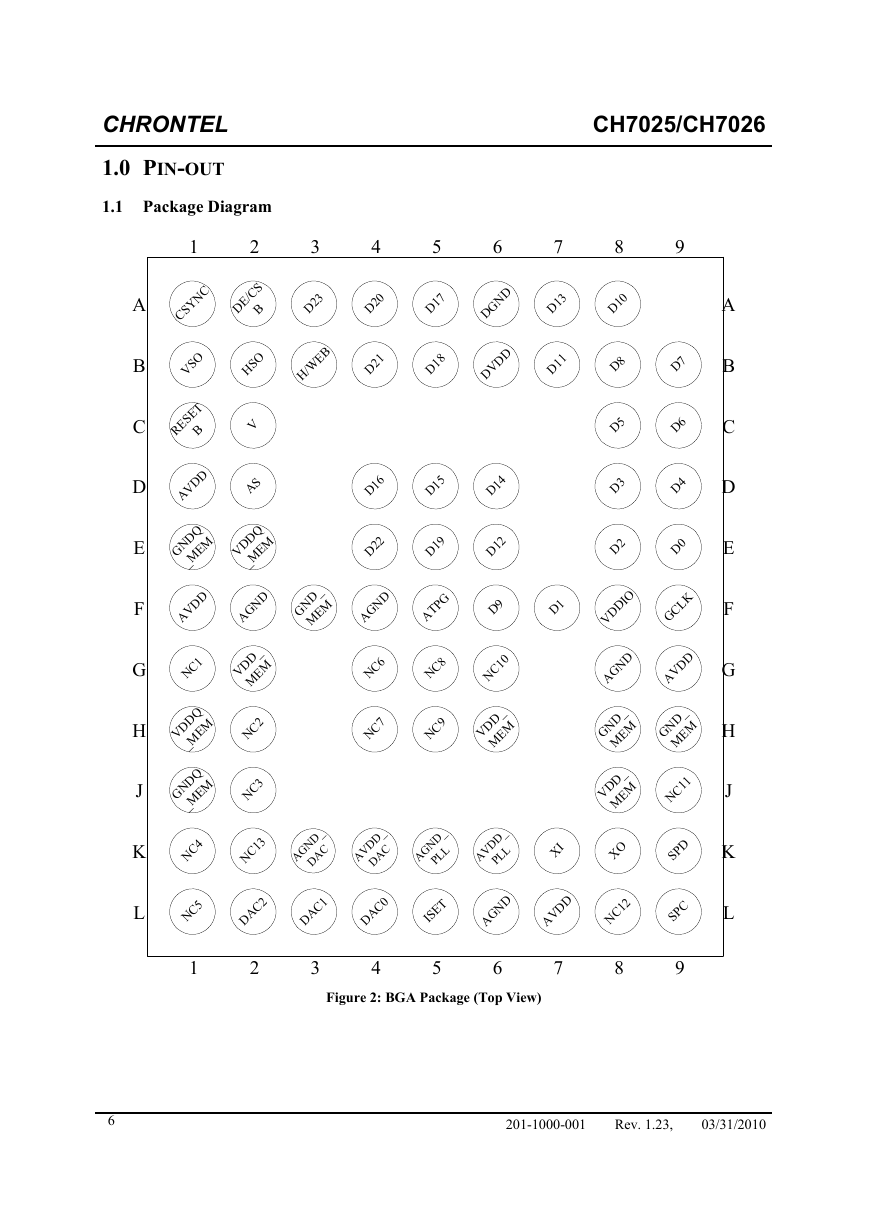

1.0 PIN-OUT

1.1 Package Diagram

CH7025/CH7026

A

B

C

D

E

F

G

H

J

K

L

1

CSYNC

VSO

RESET

B

AVDD

GNDQ

_MEM

AVDD

NC1

VDDQ

_MEM

GNDQ

_MEM

NC4

NC5

1

2

DE/CS

B

HSO

V

AS

VDDQ

_MEM

AGND

VDD_

MEM

NC2

NC3

NC13

DAC2

2

7

D13

D11

D1

3

D23

H/W EB

GND_

MEM

4

D20

D21

D16

D22

AGND

NC6

NC7

5

D17

D18

D15

D19

ATPG

NC8

NC9

6

DGND

DVDD

D14

D12

D9

NC10

VDD_

MEM

AGND_

DAC

AVDD_

DAC

AGND_

PLL

AVDD_

PLL

DAC1

3

DAC0

4

ISET

5

AGND

6

XI

AVDD

7

Figure 2: BGA Package (Top View)

8

D10

D8

D5

D3

D2

VDDIO

AGND

GND_

MEM

VDD_

MEM

XO

NC12

8

9

D7

D6

D4

D0

GCLK

AVDD

GND_

MEM

NC11

SPD

SPC

9

A

B

C

D

E

F

G

H

J

K

L

6

201-1000-001 Rev. 1.23, 03/31/2010

�

CHRONTEL

CH7025/CH7026

B

S

C

E

D

/

B

E

W

VH

/

]

3

2

[

D

]

2

2

[

D

]

1

2

[

D

]

0

2

[

D

]

9

1

[

D

]

8

1

[

D

]

7

1

[

D

]

6

1

[

D

D

D

V

D

D

N

G

D

]

5

1

[

D

]

4

1

[

D

]

3

1

[

D

]

2

1

[

D

]

1

1

[

D

]

0

1

[

D

]

9

[

D

0

8

9

7

8

7

7

7

6

7

5

7

4

7

3

7

2

7

1

7

0

7

9

6

8

6

7

6

6

6

5

6

4

6

3

6

2

6

1

6

HSO

VSO

CSYNC

ATPG

AS

RESETB

AGND

AVDD

GNDQ_MEM

VDDQ_MEM

AGND

AVDD

GND_MEM

VDD_MEM

NC

NC

NC

VDDQ_MEM

GNDQ_MEM

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

Chrontel

CH7025/CH7026

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

2

0

3

1

3

2

3

3

3

4

3

5

3

6

3

7

3

8

3

9

3

0

4

C

A

D

_

D

D

V

A

C

A

D

_

D

N

G

A

2

C

A

D

1

C

A

D

C

A

D

_

D

D

V

A

0

C

A

D

C

A

D

_

D

N

G

A

C

N

C

N

C

N

L

L

P

_

D

N

G

A

L

L

P

_

D

D

V

A

D

N

G

A

T

E

S

I

D

D

V

A

D

P

S

C

P

S

C

N

O

X

I

X

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

D[8]

D[7]

D[6]

D[5]

D[4]

D[3]

D[2]

D[1]

D[0]

VDDIO

GCLK

AVDD

AGND

GND_MEM

GND_MEM

VDD_MEM

VDD_MEM

NC

NC

NC

Figure 3: 80 Pin LQFP Package

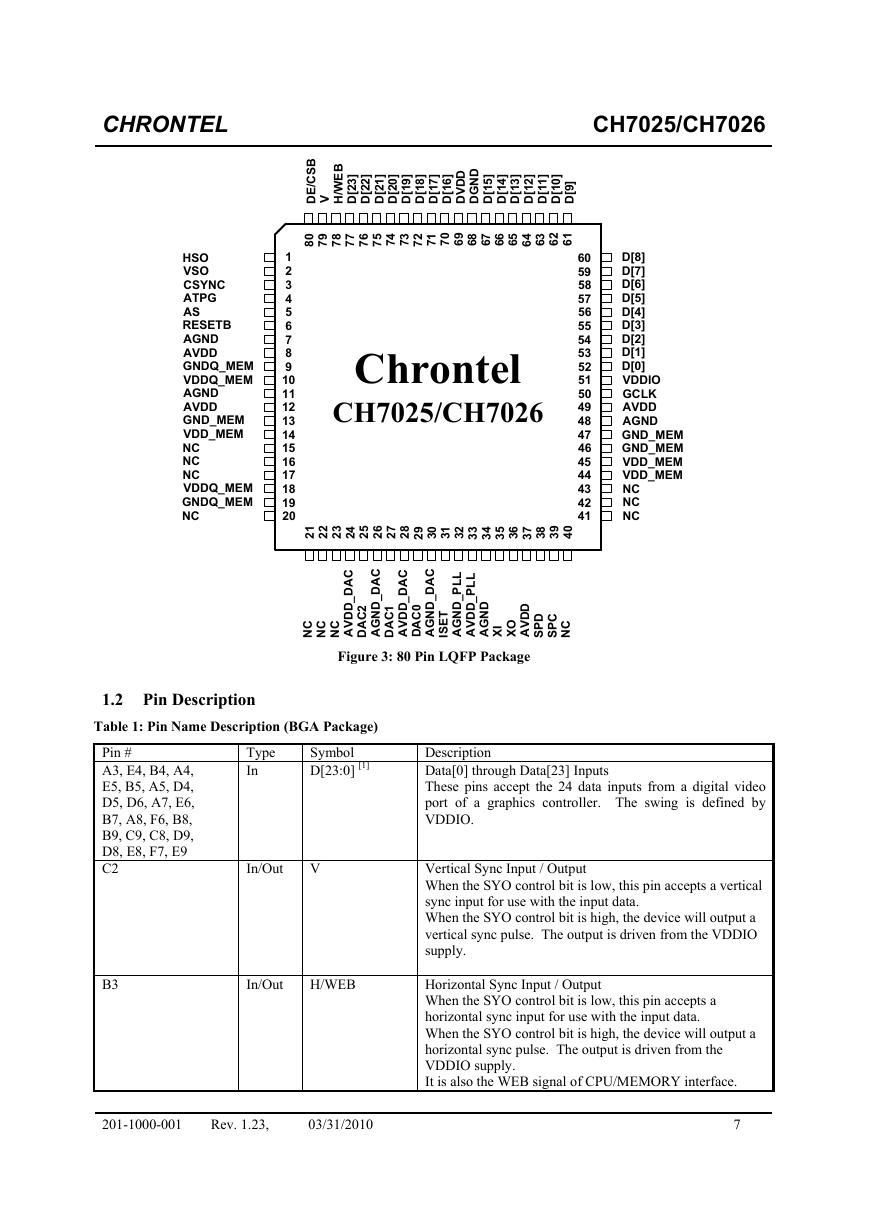

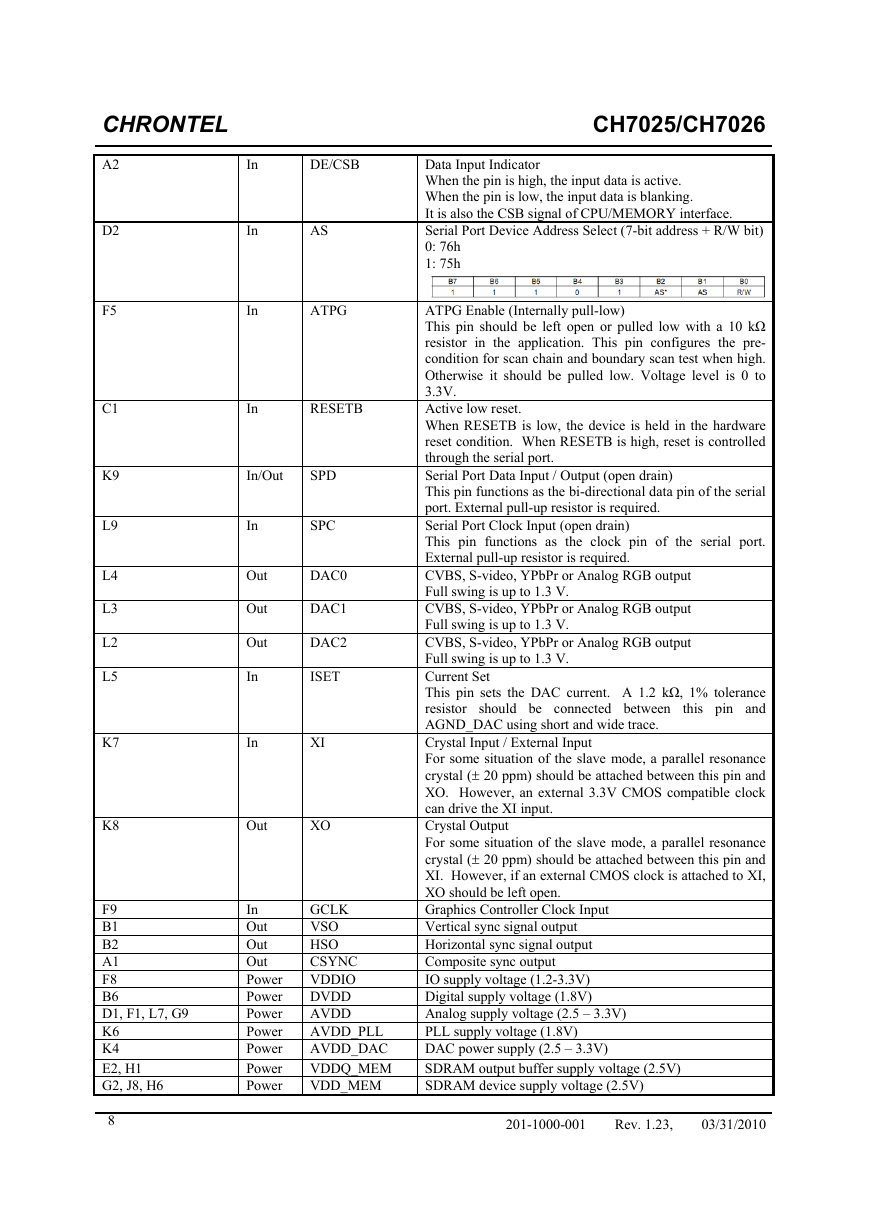

1.2 Pin Description

Table 1: Pin Name Description (BGA Package)

Pin #

A3, E4, B4, A4,

E5, B5, A5, D4,

D5, D6, A7, E6,

B7, A8, F6, B8,

B9, C9, C8, D9,

D8, E8, F7, E9

C2

Symbol

D[23:0] [1]

Type

In

In/Out

V

B3

In/Out

H/WEB

Description

Data[0] through Data[23] Inputs

These pins accept the 24 data inputs from a digital video

port of a graphics controller. The swing is defined by

VDDIO.

Vertical Sync Input / Output

When the SYO control bit is low, this pin accepts a vertical

sync input for use with the input data.

When the SYO control bit is high, the device will output a

vertical sync pulse. The output is driven from the VDDIO

supply.

Horizontal Sync Input / Output

When the SYO control bit is low, this pin accepts a

horizontal sync input for use with the input data.

When the SYO control bit is high, the device will output a

horizontal sync pulse. The output is driven from the

VDDIO supply.

It is also the WEB signal of CPU/MEMORY interface.

201-1000-001 Rev. 1.23,

03/31/2010

7

�

CHRONTEL

A2

D2

F5

C1

K9

L9

L4

L3

L2

L5

K7

K8

In

In

DE/CSB

AS

In

ATPG

In

RESETB

In/Out

SPD

In

SPC

Out

Out

Out

In

DAC0

DAC1

DAC2

ISET

In

XI

Out

XO

F9

B1

B2

A1

F8

B6

D1, F1, L7, G9

K6

K4

E2, H1

G2, J8, H6

8

In

Out

Out

Out

Power

Power

Power

Power

Power

Power

Power

GCLK

VSO

HSO

CSYNC

VDDIO

DVDD

AVDD

AVDD_PLL

AVDD_DAC

VDDQ_MEM

VDD_MEM

CH7025/CH7026

Data Input Indicator

When the pin is high, the input data is active.

When the pin is low, the input data is blanking.

It is also the CSB signal of CPU/MEMORY interface.

Serial Port Device Address Select (7-bit address + R/W bit)

0: 76h

1: 75h

ATPG Enable (Internally pull-low)

This pin should be left open or pulled low with a 10 kΩ

resistor in the application. This pin configures the pre-

condition for scan chain and boundary scan test when high.

Otherwise it should be pulled low. Voltage level is 0 to

3.3V.

Active low reset.

When RESETB is low, the device is held in the hardware

reset condition. When RESETB is high, reset is controlled

through the serial port.

Serial Port Data Input / Output (open drain)

This pin functions as the bi-directional data pin of the serial

port. External pull-up resistor is required.

Serial Port Clock Input (open drain)

This pin functions as the clock pin of the serial port.

External pull-up resistor is required.

CVBS, S-video, YPbPr or Analog RGB output

Full swing is up to 1.3 V.

CVBS, S-video, YPbPr or Analog RGB output

Full swing is up to 1.3 V.

CVBS, S-video, YPbPr or Analog RGB output

Full swing is up to 1.3 V.

Current Set

This pin sets the DAC current. A 1.2 kΩ, 1% tolerance

resistor should be connected between

this pin and

AGND_DAC using short and wide trace.

Crystal Input / External Input

For some situation of the slave mode, a parallel resonance

crystal (± 20 ppm) should be attached between this pin and

XO. However, an external 3.3V CMOS compatible clock

can drive the XI input.

Crystal Output

For some situation of the slave mode, a parallel resonance

crystal (± 20 ppm) should be attached between this pin and

XI. However, if an external CMOS clock is attached to XI,

XO should be left open.

Graphics Controller Clock Input

Vertical sync signal output

Horizontal sync signal output

Composite sync output

IO supply voltage (1.2-3.3V)

Digital supply voltage (1.8V)

Analog supply voltage (2.5 – 3.3V)

PLL supply voltage (1.8V)

DAC power supply (2.5 – 3.3V)

SDRAM output buffer supply voltage (2.5V)

SDRAM device supply voltage (2.5V)

201-1000-001 Rev. 1.23, 03/31/2010

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc