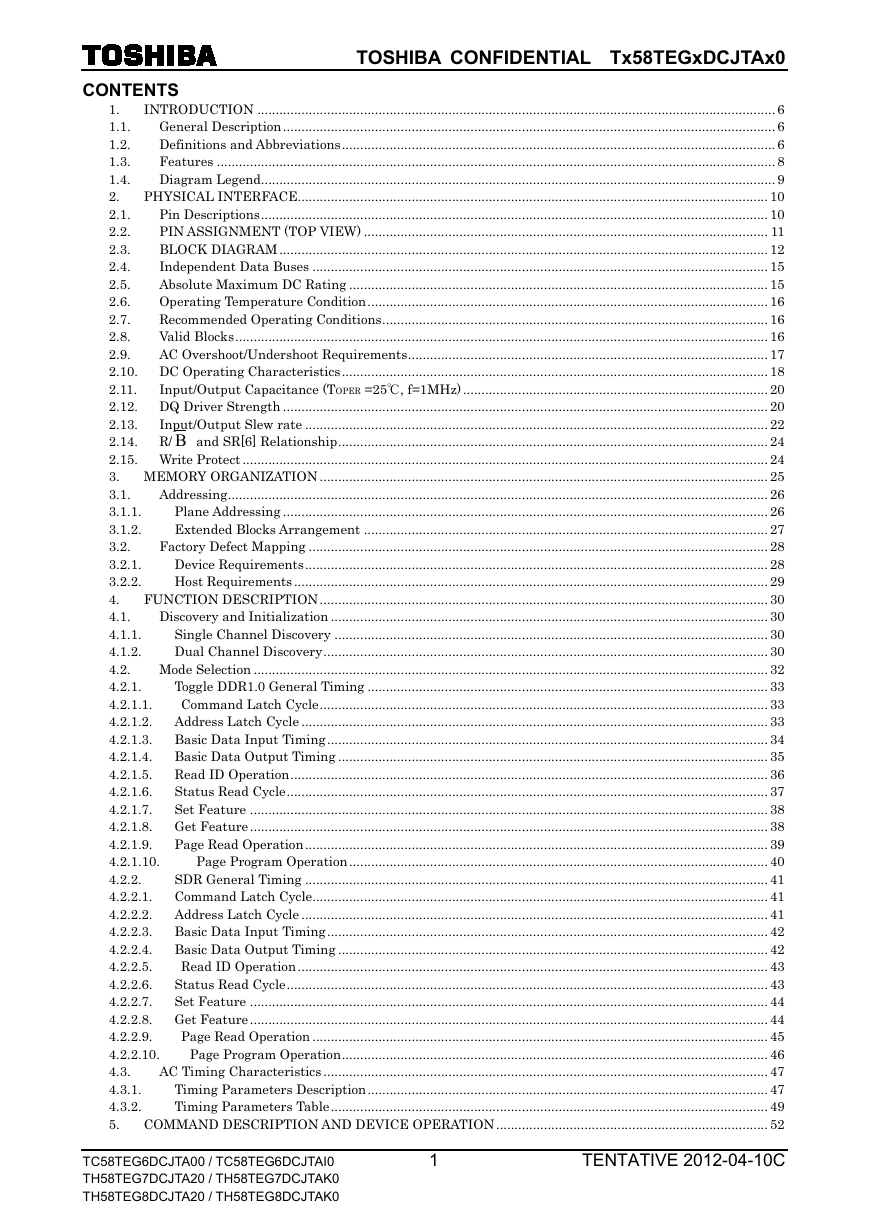

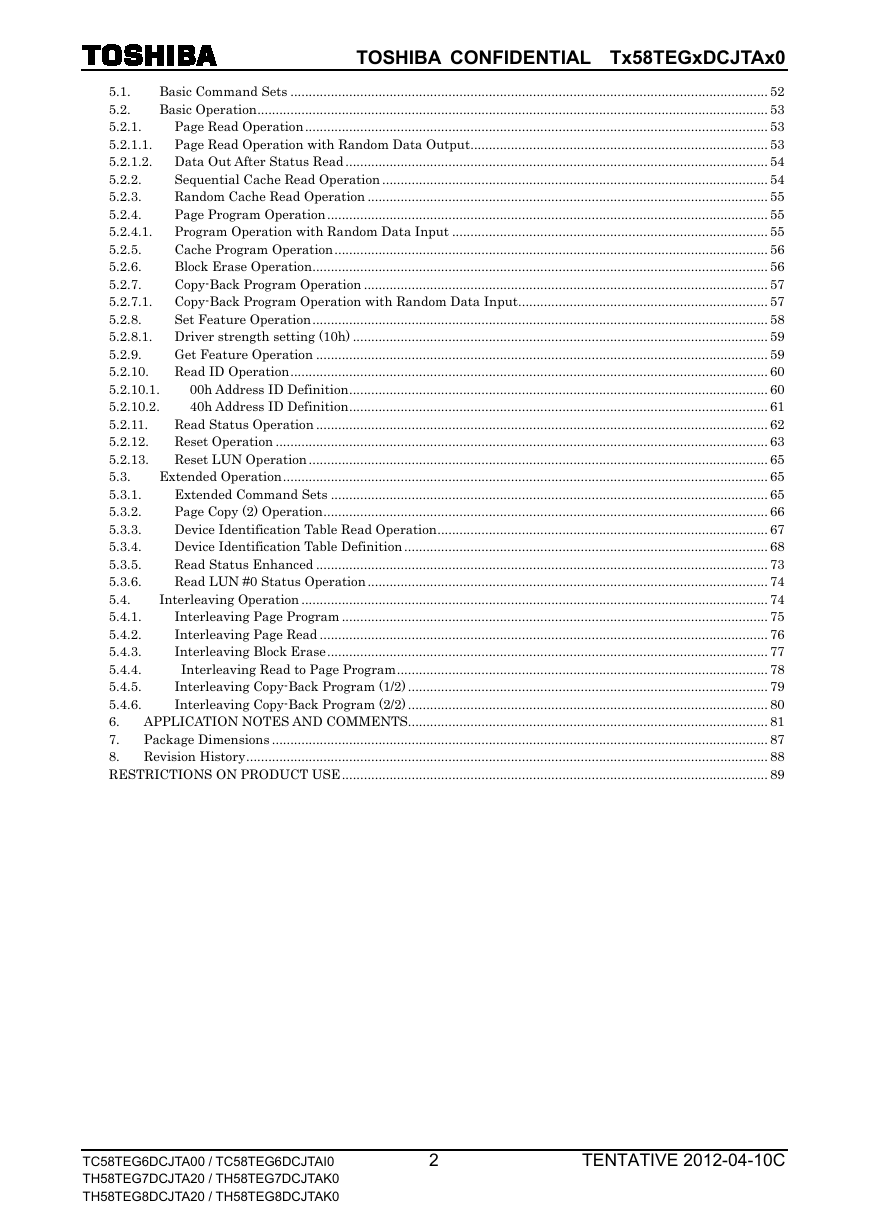

1. INTRODUCTION

1.1. General Description

1.2. Definitions and Abbreviations

1.3. Features

1.4. Diagram Legend

2. PHYSICAL INTERFACE

2.1. Pin Descriptions

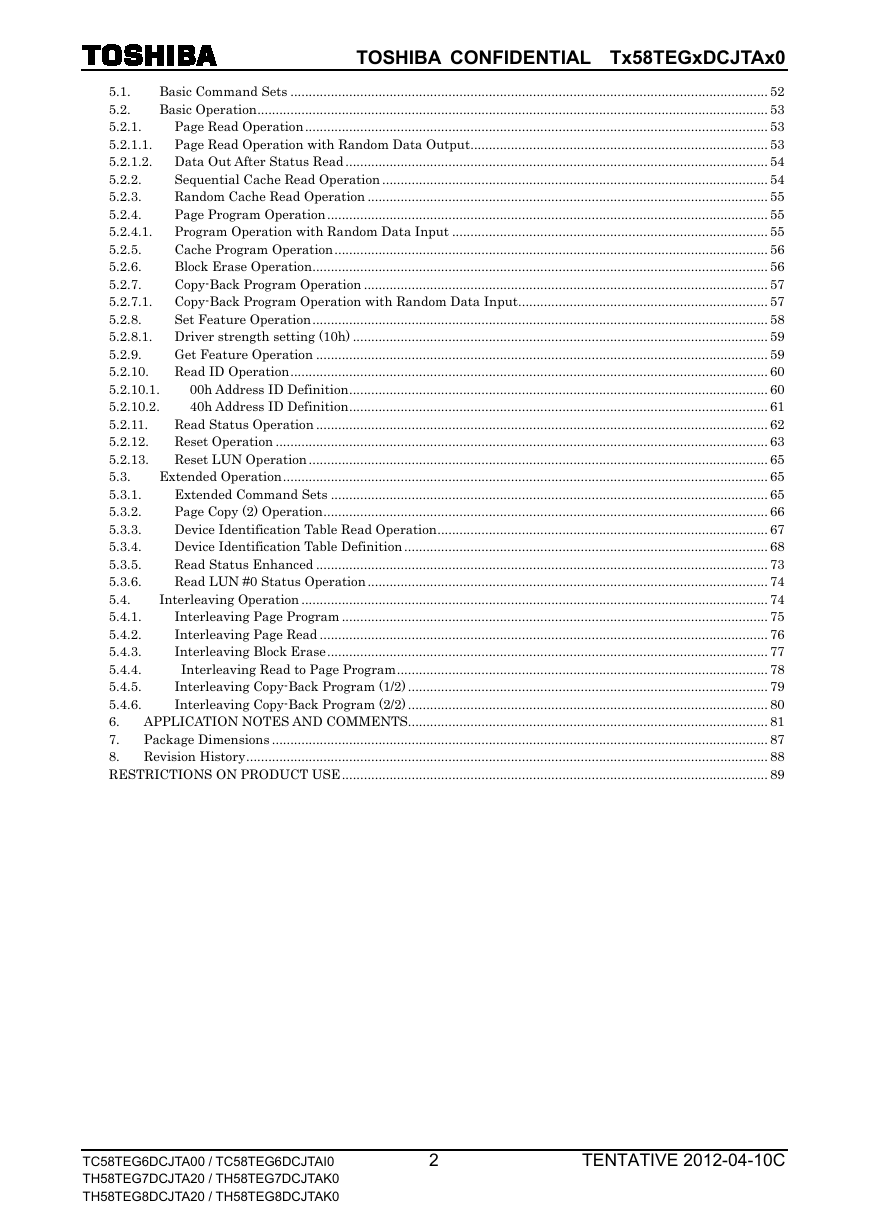

2.2. PIN ASSIGNMENT (TOP VIEW)

SDR

only

SDR

only

Vss NC NU or VssQ NU or VccQ DQ7 DQ6 DQ5 DQ4 NU or VssQ NU or VccQ VccQ VCC VSS NU VccQ NU or VssQ DQ3 DQ2 DQ1 DQ0 NU or VccQ NU or VssQ NC Vss

Vcc Vss NC NC NC 1

0

0

1 NC VCC VSS NC NC CLE ALE

NC NC NC Vss Vcc

Tx58TEGxDCJ

SDR/Toggle

DDR1.0

SDR/Toggle

DDR1.0

Vcc Vss NC NC NC 1

0

0

1 NC VCC VSS NC NC CLE ALE

NC NC NC Vss Vcc

1 48 2 47 3 46 4 45 5 44 6 43 7 42 8 41 9 40 10 39 11 38 12 37 13 36 14 35 15 34 16 33 17 32 18 31 19 30 20 29 21 28 22 27 23 26 24 25

Vss NC VssQ VccQ DQ7 DQ6 DQ5 DQ4 VssQ VccQ VccQ VCC VSS DQS VccQ VssQ DQ3 DQ2 DQ1 DQ0 VccQ VssQ NC Vss

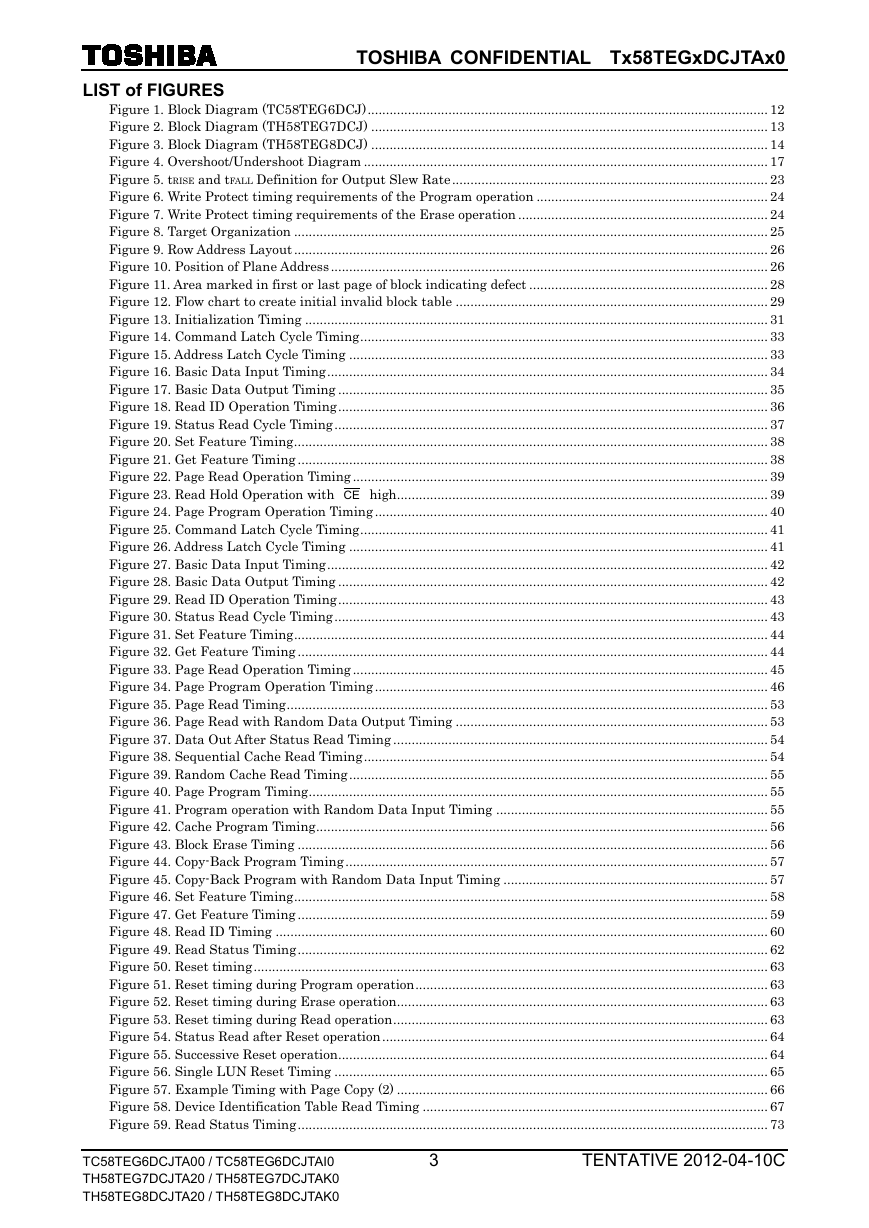

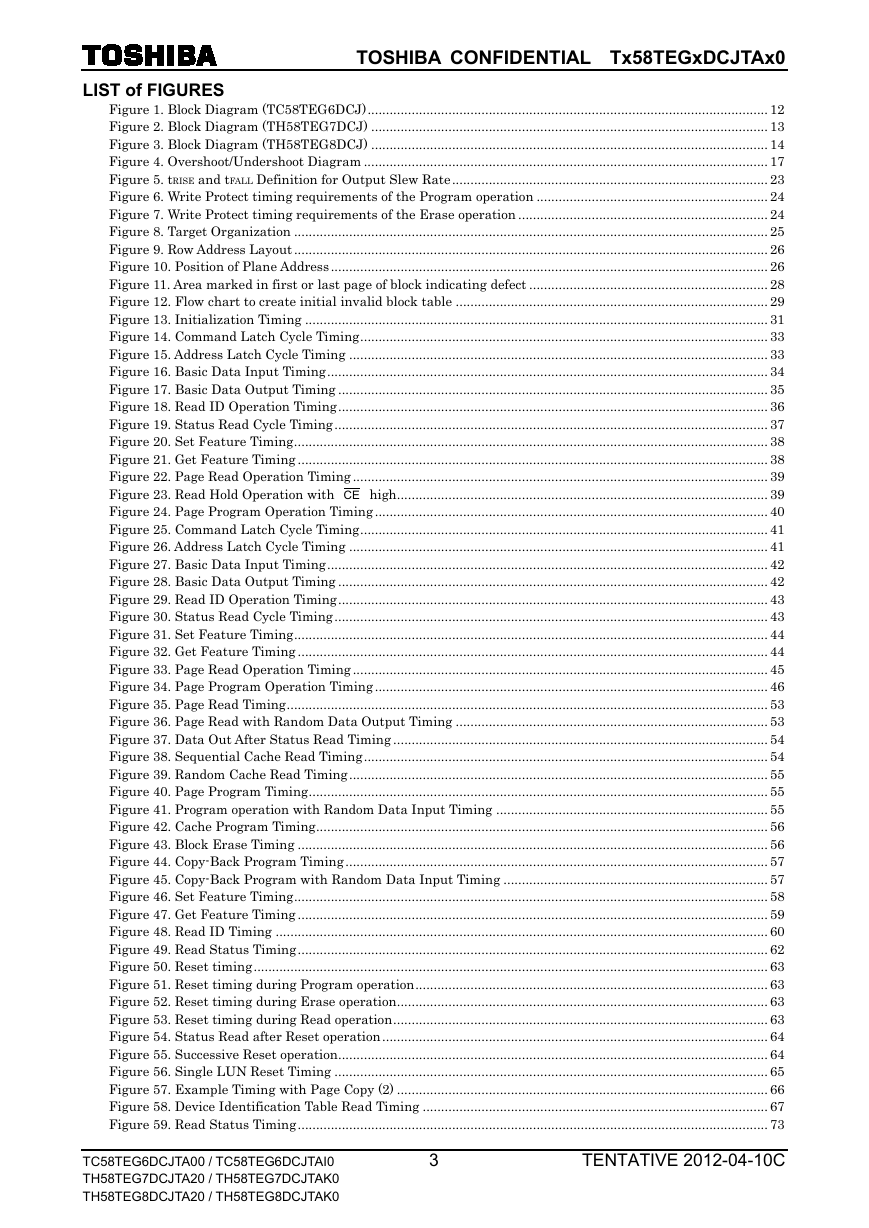

2.3. BLOCK DIAGRAM

Address register

to

Row address buffer decoder

ALE

CLE

DQ7

VSS

DQ0

VCC

Logic control

HV generator

Control circuit

Memory cell array

Sense amp

Data register

Column decoder

Column buffer

Command register

DQS

Status register

I/O Control circuit

VCC

Row address buffer decoder

VSS

Logic control

HV generator

Control circuit

Memory cell array

Sense amp

Data register

Column decoder

Column buffer

Command register

Status register

I/O Control circuit

1

1

Address register

Row address buffer decoder

VSS

VCC

Logic control

HV generator

Control circuit

Memory cell array

Sense amp

Data register

Column decoder

Column buffer

Command register

Status register

I/O Control circuit

to

0

ALE

CLE

0

DQ7

DQ0

VSS

VCC

VCC

VSS

Row address buffer decoder

Logic control

HV generator

Control circuit

Memory cell array

Sense amp

Data register

Column decoder

Column buffer

Command register

Status register

I/O Control circuit

1

1

Address register

Row address buffer decoder

Logic control

HV generator

Control circuit

Memory cell array

Sense amp

Data register

Column decoder

Column buffer

Command register

Status register

I/O Control circuit

to

0

ALE

CLE

0

DQ7

DQ0

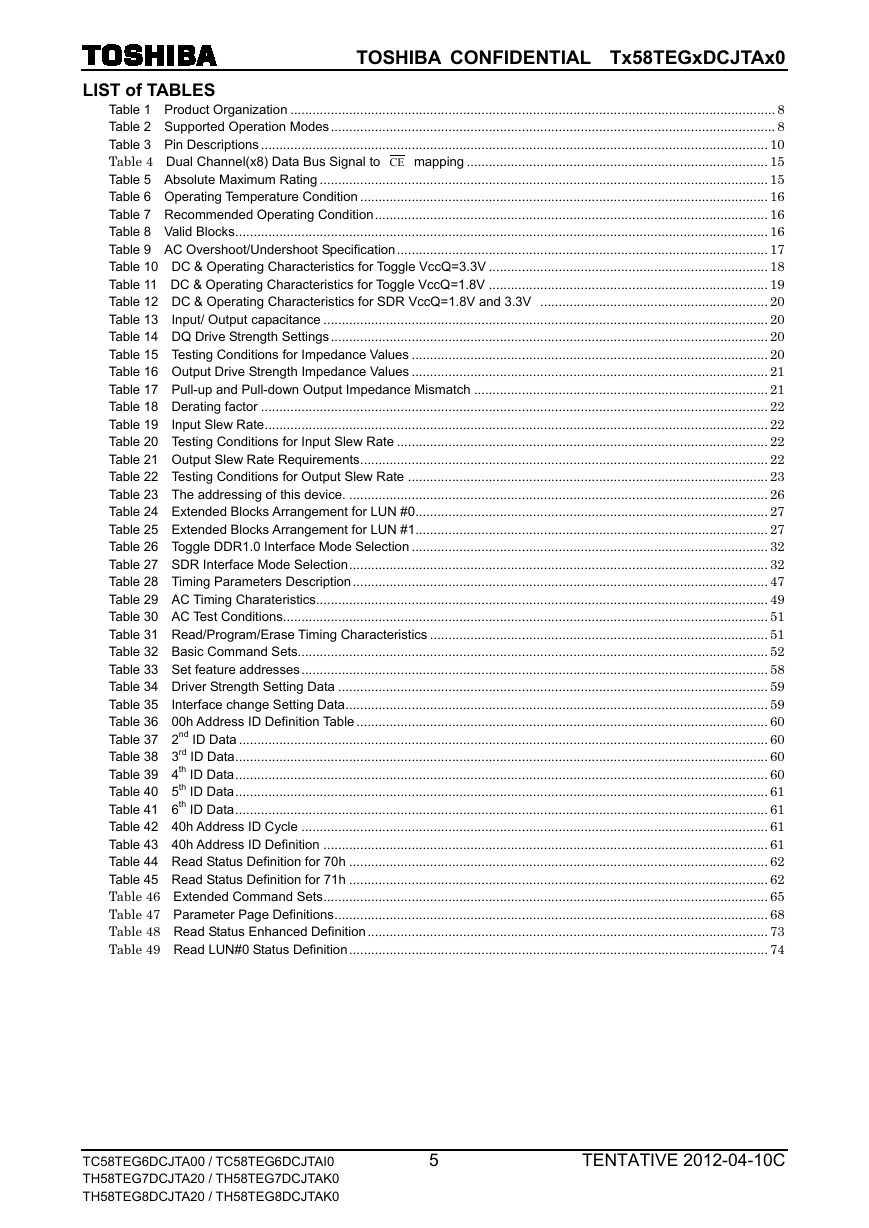

2.4. Independent Data Buses

2.5. Absolute Maximum DC Rating

2.6. Operating Temperature Condition

2.7. Recommended Operating Conditions

2.8. Valid Blocks

NOTE:

1) The device occasionally contains unusable blocks.

2) The first block (Block 0) is guaranteed to be a valid block at the time of shipment.

3) The specification for the minimum number of valid blocks is applicable over the device lifetime.

4) The number of valid blocks includes extended blocks.

2.9. AC Overshoot/Undershoot Requirements

2.10. DC Operating Characteristics

1)*1: Icco0 is the average current during R/B signal=”Busy” state.

2)*2: All operation current are without data cache.

2.11. Input/Output Capacitance (TOPER =25℃, f=1MHz)

2.12. DQ Driver Strength

2.13. Input/Output Slew rate

2.14. R/ and SR[6] Relationship

2.15. Write Protect

3. MEMORY ORGANIZATION

3.1. Addressing

3.1.1. Plane Addressing

3.1.2. Extended Blocks Arrangement

3.2. Factory Defect Mapping

3.2.1. Device Requirements

3.2.2. Host Requirements

4. FUNCTION DESCRIPTION

4.1. Discovery and Initialization

4.1.1. Single Channel Discovery

4.1.2. Dual Channel Discovery

4.2. Mode Selection

H: VIH, L: VIL, *: VIH or VIL

4.2.1. Toggle DDR1.0 General Timing

4.2.1.1. Command Latch Cycle

4.2.1.2. Address Latch Cycle

4.2.1.3. Basic Data Input Timing

4.2.1.4. Basic Data Output Timing

4.2.1.5. Read ID Operation

4.2.1.6. Status Read Cycle

4.2.1.7. Set Feature

4.2.1.8. Get Feature

4.2.1.9. Page Read Operation

4.2.1.10. Page Program Operation

4.2.2. SDR General Timing

4.2.2.1. Command Latch Cycle

4.2.2.2. Address Latch Cycle

4.2.2.3. Basic Data Input Timing

4.2.2.4. Basic Data Output Timing

4.2.2.5. Read ID Operation

4.2.2.6. Status Read Cycle

4.2.2.7. Set Feature

4.2.2.8. Get Feature

4.2.2.9. Page Read Operation

4.2.2.10. Page Program Operation

4.3. AC Timing Characteristics

4.3.1. Timing Parameters Description

4.3.2. Timing Parameters Table

5. COMMAND DESCRIPTION AND DEVICE OPERATION

5.1. Basic Command Sets

5.2. Basic Operation

5.2.1. Page Read Operation

5.2.1.1. Page Read Operation with Random Data Output

5.2.1.2. Data Out After Status Read

5.2.2. Sequential Cache Read Operation

5.2.3. Random Cache Read Operation

5.2.4. Page Program Operation

5.2.4.1. Program Operation with Random Data Input

5.2.5. Cache Program Operation

5.2.6. Block Erase Operation

5.2.7. Copy-Back Program Operation

5.2.7.1. Copy-Back Program Operation with Random Data Input

5.2.8. Set Feature Operation

5.2.8.1. Driver strength setting (10h)

5.2.9. Get Feature Operation

5.2.10. Read ID Operation

5.2.10.1. 00h Address ID Definition

5.2.10.2. 40h Address ID Definition

5.2.11. Read Status Operation

5.2.12. Reset Operation

When Reset (FFh) command is input during Program operation

When Reset (FFh) command is input during Erase operation

When Reset (FFh) command is input during Read operation

When Read Status command (70h) is input after Reset operation

When two or more Reset commands are input in succession

5.2.13. Reset LUN Operation

5.3. Extended Operation

5.3.1. Extended Command Sets

5.3.2. Page Copy (2) Operation

5.3.3. Device Identification Table Read Operation

5.3.4. Device Identification Table Definition

5.3.5. Read Status Enhanced

5.3.6. Read LUN #0 Status Operation

5.4. Interleaving Operation

5.4.1. Interleaving Page Program

5.4.2. Interleaving Page Read

5.4.3. Interleaving Block Erase

5.4.4. Interleaving Read to Page Program

5.4.5. Interleaving Copy-Back Program (1/2)

5.4.6. Interleaving Copy-Back Program (2/2)

6. APPLICATION NOTES AND COMMENTS

DQS

DQS

DQS

DQS

R/

R/

DQS

DQS

R/

DQS

R/

DQS

R/

DQS

tWH

tCH

CLE

tCLS

tCLS

tWP

tALH

tDS

tDH

tALS

tDS

tDH

: VIH or VIL

ADD

ADD

tCS

tWP

ALE

CLE

: VIH or VIL

tCLH

tCH

tCH

tCLH

ADD

tWC

tWH

tWP

tDS

tDH

tWC

C

tWH

tWP

tDS

tDH

tDS

tDH

ALE

tCS

tCS

tDS

tDH

ADD

tWP

tWH

tWP

tALH

tALS

ADD

tRHOH

tRHOH

tRR

Command

tREA

tRLOH

tRLOH

tDS

tDH

tREA

tREA

tCLHZ

tRP

tREH

tRP

tRHZ

tRP

tRC

tCHZ

ALE

tALH

tCR

tCS2

tCH

tCLH

tCLS2

CLE

Dout

Dout

tALH

tCS

tCH

tCLS

tCS

tDS

tDH

tDS

tDH

DIN N

CLE

ALE

tCH

tCLH

DIN 1

DIN 0

tDS

tDH

tWC

tALS

tWP

tWH

tWP

tWP

If Fail

tDH

tALH

tCH

tCS

tCLS

tALS

tALH

tCH

tDS

tCS

tCLS

ALE

CLE

: VIH or VIL

*: 70h represents the hexadecimal number

: VIH or VIL

Status output

70h*

tREA

tRHZ

tDH

tDS

tIR

tRHOH

tWHR

tWHC

tCHZ

tCH

tWP

tCEA

tCR

tCS

tCLS

tCLH

CLE

tCLR

If Fail

: Do not input data while data is being output.

: VIH or VIL

tCEA

DOUT N ( 1

DOUT N

00h

tDS

tDH

Data out from Col. Add. N

tREA

tRR

tRC

tALS

tCH

tCLH

tCLS

tCS

tWB

tDS

tDH

tR

tCLR

tALH

tDS

tDH

tDS

tDH

tDS

tDH

tDS

tDH

ALE

CLE

tALH

tALS

tWC

tDS

tDH

tCH

tCLH

tCLS

tCS

ADD

ADD

ADD

ADD

ADD

30h

*) M: up to 17664 (byte input data for (8 device).

tADL

DIN N+1

80h

ADD

ADD

ADD

Status output

70h

10h

DINM

DINN

ADD

tALS

tALH

tDS

tWB

tPROG

tDH

tDS

tDH

tCS

: Do not input data while data is being output.

tALH

tDH

tDS

tCS

tCH

tCLH

: VIH or VIL

ALE

CLE

tDH

tDS

tALS

tCLS

tCLS

ADD

30

tRST for read

00

FF

00

tRST for erase

00

FF

D0

Internal erase voltagtRST (max 30 (s)

e

00

tRST for program

00

FF

10

80

Internal VPP

FF

FF

FF

The second command is invalid, but the third command is valid.

(1)

(2)

(3)

FF

FF

10

70

FF

Status : Pass/Fail ( Pass

: Ready/Busy ( Ready

80

FF

Address input

Command other than “81h”, “85h”, “11h” , “15h” or “FFh”

80

Programming cannot be executed.

10

XX

Mode specified by the command.

VCCQ ( 3.3 V / 1.8V Ta ( 25 C CL ( 50 pF

tf

tr

R

tr

tf

5 ns

10 ns

15 ns

2 K(

3 K(

4 K(

1 K(

0

0.5 (s

1.0 (s

1.5 (s

CL

R

VSS

Device

VCCQ

VCCQ

VOH

Busy

VOL

VOH

tr

VOL

VCCQ

Ready

tf

Fail

80

10

80

10

Address M

Data input

70

I/O

Address N

Data input

If the programming result for page address M is Fail, do not try to program the page to address N in another block without the data input sequence.

Because the previous input data has been lost, the same input sequence of 80h command, address and data is necessary.

10

80

M

N

Read operation

Program operation

CLE

Address input

00h

ALE

DQx

Ignored

30h

CLE

ALE

DQx

Address input

Ignored

80h

Data input

Program

Erase

7. Package Dimensions

8. Revision History

RESTRICTIONS ON PRODUCT USE

Bad Block

Bad Block

Block A

Block B

Error occurs

Buffer memory

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc