外部存储器接口(EMIF),External Memory Interface,是 TMS DSP 器件上的

一种接口,具体可以分为 EMIFA 和 EMIFB。一般来说,EMIF 可实现 DSP 与不同类型存储

器(SRAM、Flash RAM、DDR-RAM 等)的连接。一般 EMIF 与 FPGA 相连,从而使 FPGA

平台充当一个协同处理器、高速数据处理器或高速数据传输接口。

EMIF 接口就相当于一个可配置的总线接口,其接口上面的信号线基本囊括了各种存储器

(SRAM、Flash RAM、DDR-RAM 等)的读写接口信号。通过软件配置相应的寄存器,可以使 EMIF

接口工作于和设计中使用的外部存储器相匹配的固定的接口形式。但是与其他固定接口不同

的是,EMIF 接口读写时序中的高低电平的保持时间是可以通过寄存器设置的。

图 2 中,ECLKIN 信号是系统提供的一个外部时钟源。ECLKOUT 信号是由内部产生(基于

ECLKIN),所有与本控制器 EMIF 接口对接的存储器必须工作在 ECLKOUT 下。SBSRAM 接口、

SDRAM 接口和异步接口的信号合并复用。这里的 CE1 片选空间支持所有的 3 种存储器接口。

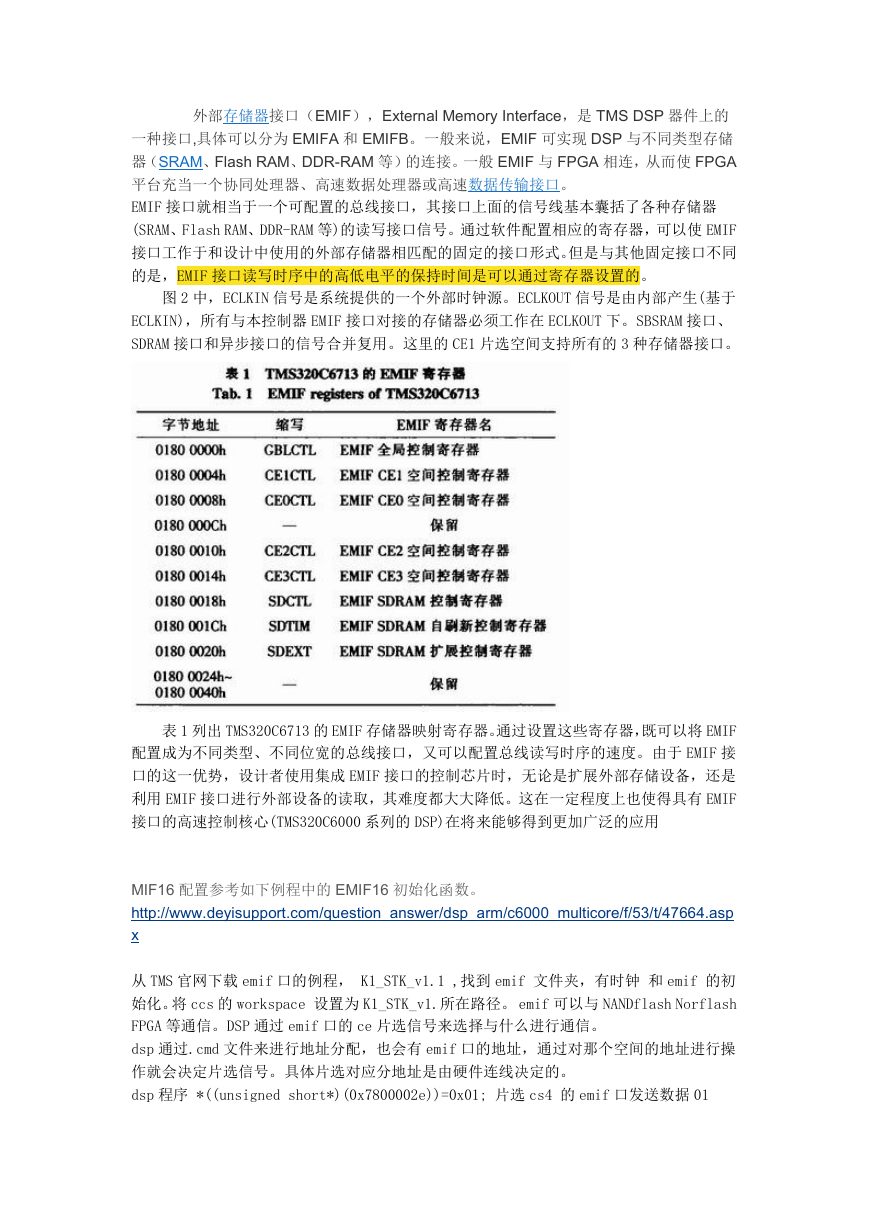

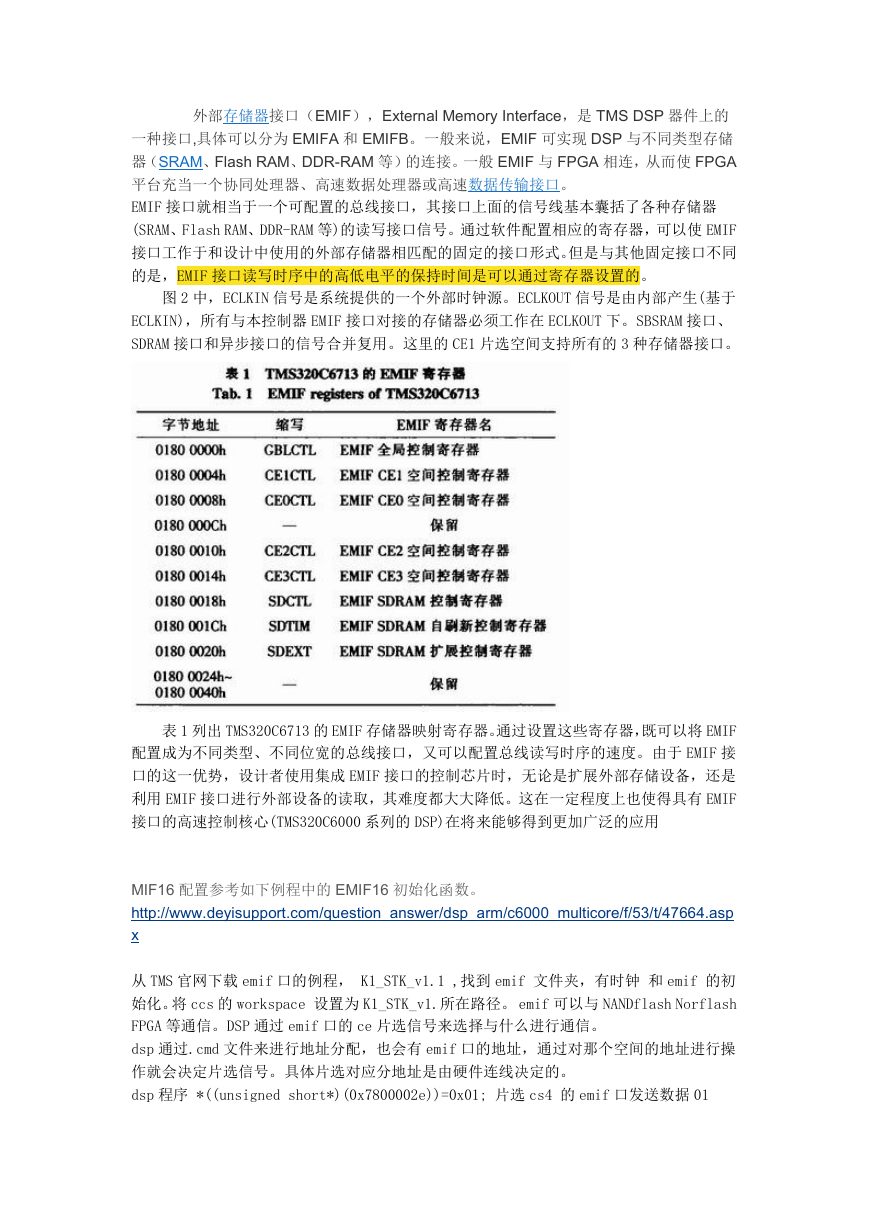

表 1 列出 TMS320C6713 的 EMIF 存储器映射寄存器。通过设置这些寄存器,既可以将 EMIF

配置成为不同类型、不同位宽的总线接口,又可以配置总线读写时序的速度。由于 EMIF 接

口的这一优势,设计者使用集成 EMIF 接口的控制芯片时,无论是扩展外部存储设备,还是

利用 EMIF 接口进行外部设备的读取,其难度都大大降低。这在一定程度上也使得具有 EMIF

接口的高速控制核心(TMS320C6000 系列的 DSP)在将来能够得到更加广泛的应用

MIF16 配置参考如下例程中的 EMIF16 初始化函数。

http://www.deyisupport.com/question_answer/dsp_arm/c6000_multicore/f/53/t/47664.asp

x

从 TMS 官网下载 emif 口的例程, K1_STK_v1.1 ,找到 emif 文件夹,有时钟 和 emif 的初

始化。将 ccs 的 workspace 设置为 K1_STK_v1.所在路径。 emif 可以与 NANDflash Norflash

FPGA 等通信。DSP 通过 emif 口的 ce 片选信号来选择与什么进行通信。

dsp 通过.cmd 文件来进行地址分配,也会有 emif 口的地址,通过对那个空间的地址进行操

作就会决定片选信号。具体片选对应分地址是由硬件连线决定的。

dsp 程序 *((unsigned short*)(0x7800002e))=0x01; 片选 cs4 的 emif 口发送数据 01

�

MEMORY

{

LOCAL_L2_SRAM: o = 0x00800000 l = 0x00080000 /* 512kB LOCAL L2/SRAM */

LOCAL_L1P_SRAM: o = 0x00E00000 l = 0x00008000 /* 32kB LOCAL L1P/SRAM */

LOCAL_L1D_SRAM: o = 0x00F00000 l = 0x00008000 /* 32kB LOCAL L1D/SRAM */

SHRAM: o = 0x0C000000 l = 0x00400000 /* 4MB Multicore shared Memmory */

EMIF16_CS2: o = 0x70000000 l = 0x04000000 /* 64MB EMIF16 CS2 Data Memory */

EMIF16_CS3: o = 0x74000000 l = 0x04000000 /* 64MB EMIF16 CS3 Data Memory */

EMIF16_CS4: o = 0x78000000 l = 0x04000000 /* 64MB EMIF16 CS4 Data Memory */

EMIF16_CS5: o = 0x7C000000 l = 0x04000000 /* 64MB EMIF16 CS5 Data Memory */

DDR3: o = 0x80000000 l = 0x80000000 /* 2GB CE0 and CE1 external DDR3 SDRAM */

}

emif 手册可以看 sprugz3a.pdf

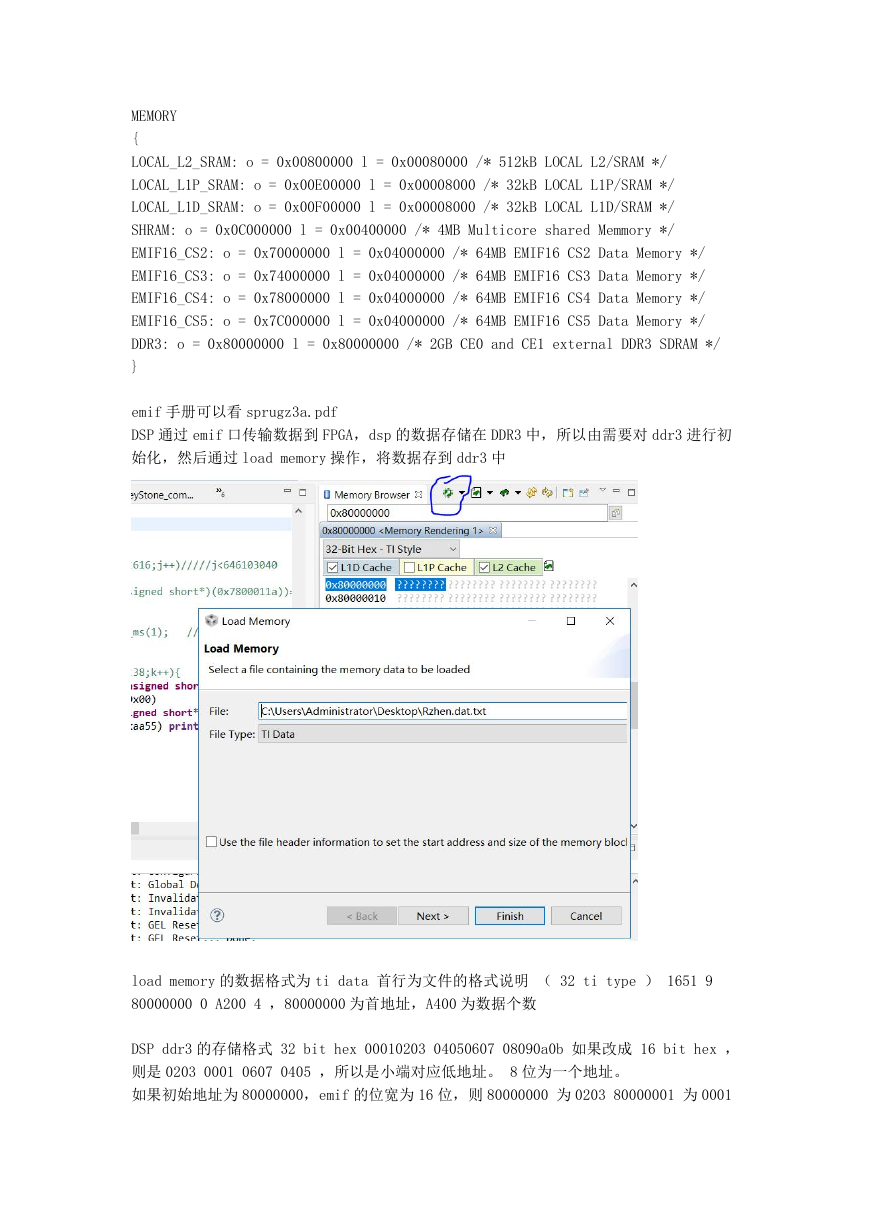

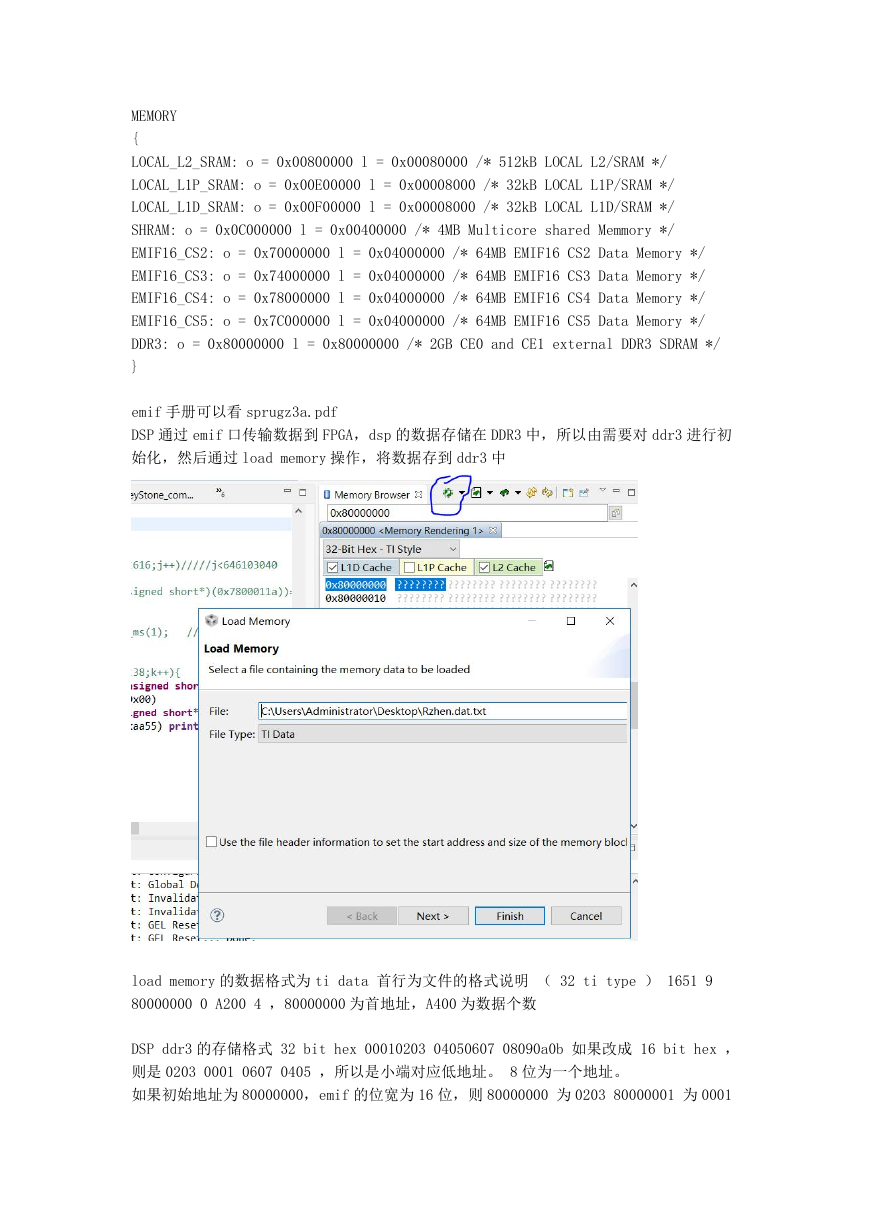

DSP 通过 emif 口传输数据到 FPGA,dsp 的数据存储在 DDR3 中,所以由需要对 ddr3 进行初

始化,然后通过 load memory 操作,将数据存到 ddr3 中

load memory 的数据格式为 ti data 首行为文件的格式说明 ( 32 ti type ) 1651 9

80000000 0 A200 4 ,80000000 为首地址,A400 为数据个数

DSP ddr3 的存储格式 32 bit hex 00010203 04050607 08090a0b 如果改成 16 bit hex ,

则是 0203 0001 0607 0405 ,所以是小端对应低地址。 8 位为一个地址。

如果初始地址为 80000000,emif 的位宽为 16 位,则 80000000 为 0203 80000001 为 0001

�

80000003 为 0607 80000004 为 0405 ,与实际的地址感觉不符,因为 07 才是 80000004 的

数据。但是也只能这样了,未解

emif 初始化设置

emif16_cfg.maxWait = 0x80;

emif16_cfg.wait0Polarity = EMIF_LOW_WAIT;

emif16_cfg.wait1Polarity = EMIF_LOW_WAIT;

emif16_cfg.ceCfg[0]->busWidth = EMIF_BUS_16BIT;

emif16_cfg.ceCfg[0]->opMode = NOR_ASRAM_MODE;

emif16_cfg.ceCfg[0]->strobeMode = SS_STROBE;

emif16_cfg.ceCfg[0]->waitMode = EMIF_WAIT_NONE;

emif16_cfg.ceCfg[0]->wrSetup = 15;

emif16_cfg.ceCfg[0]->wrStrobe = 63;

emif16_cfg.ceCfg[0]->wrHold = 7;

emif16_cfg.ceCfg[0]->rdSetup = 15;

emif16_cfg.ceCfg[0]->rdStrobe = 63;

emif16_cfg.ceCfg[0]->rdHold = 7;

emif16_cfg.ceCfg[0]->turnAroundCycles = 3;

emif16_cfg.ceCfg[0]->nor_pg_Cfg = NULL;

位宽可以是 8 位的,或者是 16 位的,模式可以是 nand flash 或者是 nor_asram(fpga 选择

这种模式)

关于时间的设置详细看用户手册。

emif 口的几个数据,只要给地址和数据进行赋值,emif 口就可以自动将其他的信号 ce(片

选)oe be 等处理好。

�

�

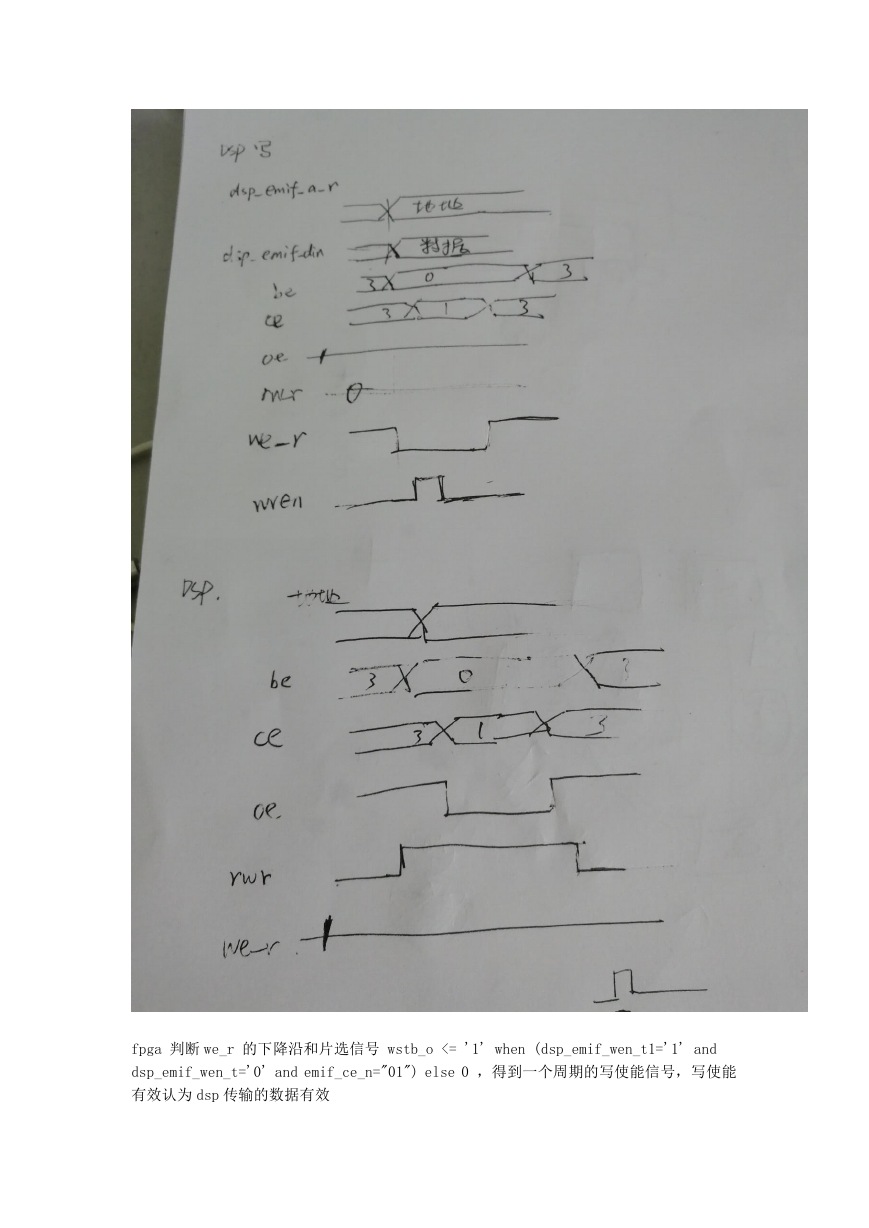

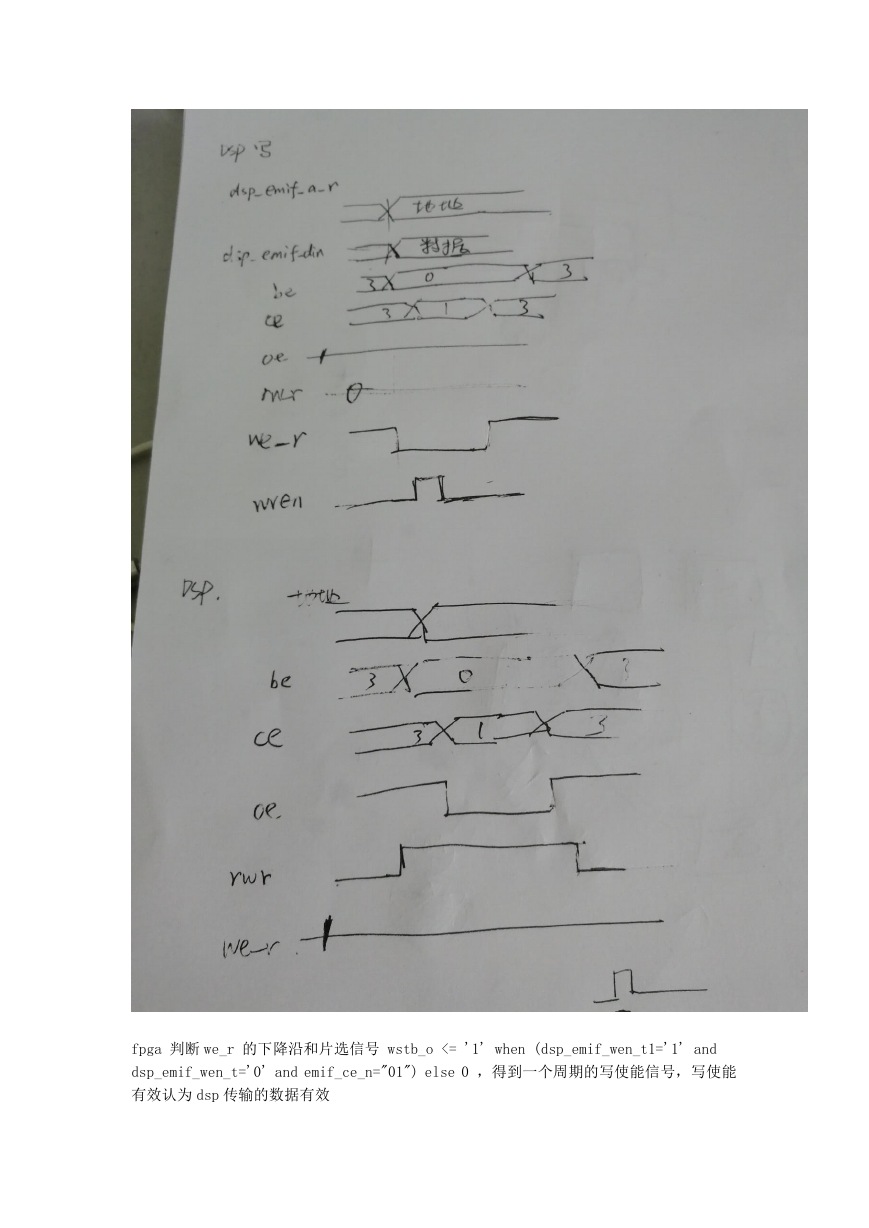

fpga 判断 we_r 的下降沿和片选信号 wstb_o <= '1' when (dsp_emif_wen_t1='1' and

dsp_emif_wen_t='0' and emif_ce_n="01") else 0 ,得到一个周期的写使能信号,写使能

有效认为 dsp 传输的数据有效

�

判断 oe 的下降沿和片选信号得到读使能信号 rstb_o <= '1' when (dsp_emif_oen = '1' and

dsp_emif_oen_i = '0' and emif_ce_n="01") else

'0'

地址需要进行调整,将 23 位和 22 位调整到 0 位和 1 位。(用户手册这是 8 位宽才需要调

整的方式,但是实际情况是 16 的位宽也是这样调整的)

因为数据线是双向的,所以需要进行调整

读使能有效,fpga 传输给 dsp 的数据要准备好。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc