PowerPC 嵌入式系统实验教程

PowerPC 嵌入式系统实验教程

第一章 Power PC 硬件设计及特点介绍

1.1 PowerPC e300 core介绍........................................................................................ 1

1.1.1 概述............................................................................................................. 1

1.1.2 PowerPC架构执行 ...................................................................................... 9

1.1.3 特殊执行信息............................................................................................. 9

1.1.4 内核之间的区别....................................................................................... 10

1.1.5 e300 内核间区别....................................................................................... 12

1.2 MPC8349 芯片介绍 ............................................................................................ 12

1.2 PowerPC MPC8349E开发板硬件设计........................................................ 17

1.2.1 板极功能................................................................................................... 17

1.2.2 MPC8349E-mITX开发板上器件装配...................................................... 36

1.2.3 连接器....................................................................................................... 37

1.2.4 跳线帽,拨码开关和LED灯................................................................... 42

1.2.5 MPC8349E-mITXE开发板配置 ............................................................... 47

1.2.6 规格........................................................................................................... 56

1.2.7 机械数据................................................................................................... 57

1.2.8 启动........................................................................................................... 57

1.2.9 MPC8349E-mITX软件.............................................................................. 63

1.3 系统设计信息..................................................................................................... 64

1.3.1 电源设计................................................................................................... 64

1.3.2 系统时钟................................................................................................... 68

1.3.3 上电复位与复位配置............................................................................... 70

1.3.4 复位配置信号........................................................................................... 70

1.3.5 JTAG与DEBUG ........................................................................................ 71

1.3.6 功能模块................................................................................................... 73

第 1 页 共 2 页

�

PowerPC 嵌入式系统实验教程

第二章 基础实验............................................................................................................. 80

2.1 UART 与 PC通信实验 ...................................................................................... 80

2.2 GTIMERS 计时实验.......................................................................................... 99

2.3 I2C接口实验...................................................................................................... 109

2.4 RTC实验一 alarm功能实验............................................................................. 136

2.5 RTC实验二 周期执行任务实验.................................................................... 1488

2.6 SPI接口Loop模式读写实验 ............................................................................. 154

2.7 Random Number Generator实验..................................................................... 1799

2.8 PCI Agent与Host连接实验 ............................................................................... 201

2.9 TESC Loopback 实验..................................................................................... 2177

第三章 综合应用实验................................................................................................. 2733

3.1 U-boot在PowerPC中的使用 ........................................................................... 2733

3.2 Embeded Linux编译与移植.............................................................................. 340

3.3 MPC8349 ITX 开发板 LED字符设备驱动.................................................... 342

3.4 网络设备驱动程序........................................................................................... 351

3.5 RTL8139 驱动程序解析 .................................................................................. 365

3.6 Linux 透明代理与防火墙实现........................................................................ 373

附录............................................................................................................................... 3788

附录I Freescale PowerPC处理器概述................................. 错误!未定义书签。8

附录II Micetek开发板介绍..................................................................................... 387

附录III Jediview 安装与注册 .............................................................................. 4188

附录IV LTIB的使用................................................................................................ 445

第 2 页 共 2 页

�

PowerPC 嵌入式系统实验教程

第一章 PowerPC 硬件设计及特点介绍

1.1 PowerPC e300 core 介绍

1.1.1 概述

本部分描述了e300内核的详细情况,提供了说明主要功能单元的结构框图,并简要描述

了这些单元如何相互作用。也特别提到了e300和以前来源于MPC603e处理器的PowerPC之间

执行的所有不同之处。请见章节“e300内核之间的差异,用于e300内核配置间区别的描述”。

e300内核是RISC(reduced instruction set computer)微处理器系列的低功率器件。内核

执行PowerPC架构的32位部分,该架构定义了32位有效地址,8、16和32位整数数据类型,

以及32和64位浮点数据类型。

内核是能发出和停止每时钟周期三个指令之多的超级数量处理器。为了更高的性能,指

令不以程序命令来执行;然而,内核使完成出现序列化。

e300内核独立执行单元包括:整数单元(IU),浮点单元(FPU),分支处理单元(BPU),

负载/存储单元(LSU)和系统整数单元(SRU)。e300c2和e300c3集成了用于两个IU的附加

整数单元。特别指出,e300c2不包括FPU。并行执行指令的能力和对带迅速执行时间的简单

指令的使用产生了高效率和基于e300内核系统的高流量。大部分整数指令在一个时钟周期里

执行。e300c2和e300c3里附加的IU和增强型乘法器改进乘法指令到最多两个周期延迟,这是

一个自以前处理器以来的重大改进。在e300c1和e300c2内核里,执行FPU。FPU是管线机制。

所以每个时钟周期能产生和完成一个单精度乘法加法指令。e300c1和e300c3内核给大多数值

代表和所有整数模式的所有单-双精度浮点操作提供硬件支持。

e300c1提供独立片内32KB字节,8通道,联合设置,程序和数据的物理地址缓存和片内

程序和数据内存管理单元 (MMUs)。e300c2 和e300c3包括16KB四通道联合设置程序和数据

缓存。MMUs包含64-入口,两通道,联合设置,提供页要求、实际存储器、地址译码和多

种大小块译码支持的数据和程序译码查看缓冲器(DTLB和ITLB)。TLBs使用最小最近使

用(LRU)替换算法,缓存使用伪随机最小最近使用算法(PLRU)。TLBs用LRU替代算法,

并且缓冲区用PLRU算法。

内核还通过使用两个独立程序和数据块地址译码BAT和DBAT)阵列来支持块地址译

第 1 页 共 490 页

�

PowerPC 嵌入式系统实验教程

码,G2内核从包含每种BAT四对增加到8对BAT。在存储器访问和I/O访问的段、块或页的

基础上,这种增加为保护访问和提供译码提供了更好的灵活性。在进行块译码期间,有效地

址同时和在BAT阵列里所有8个入口做比较。按照PowerPC架构,假如一个有效地址同时位

于在TLB和BAT阵列里,BAT译码具有优先权。

作为共同系统总线(CSB)的一部分,e300内核有64位数据总线和32位地址总线。正常工

作期间,e300内核提供三态(可修改的,专有的和无效的)一致协议,该协议是一套兼容四

态(可修改的/专有的/共享的/无效的)MESI协议。然而,e300数据缓存包含支持共享缓存

一致状态(和其他PowerPC处理器相似)的可编程MESI延伸。两个协议共同工作于包括四

态缓存的系统。内核还支持单击和存储器访问的突发数据译码,并支持存储器映射I/O操作。

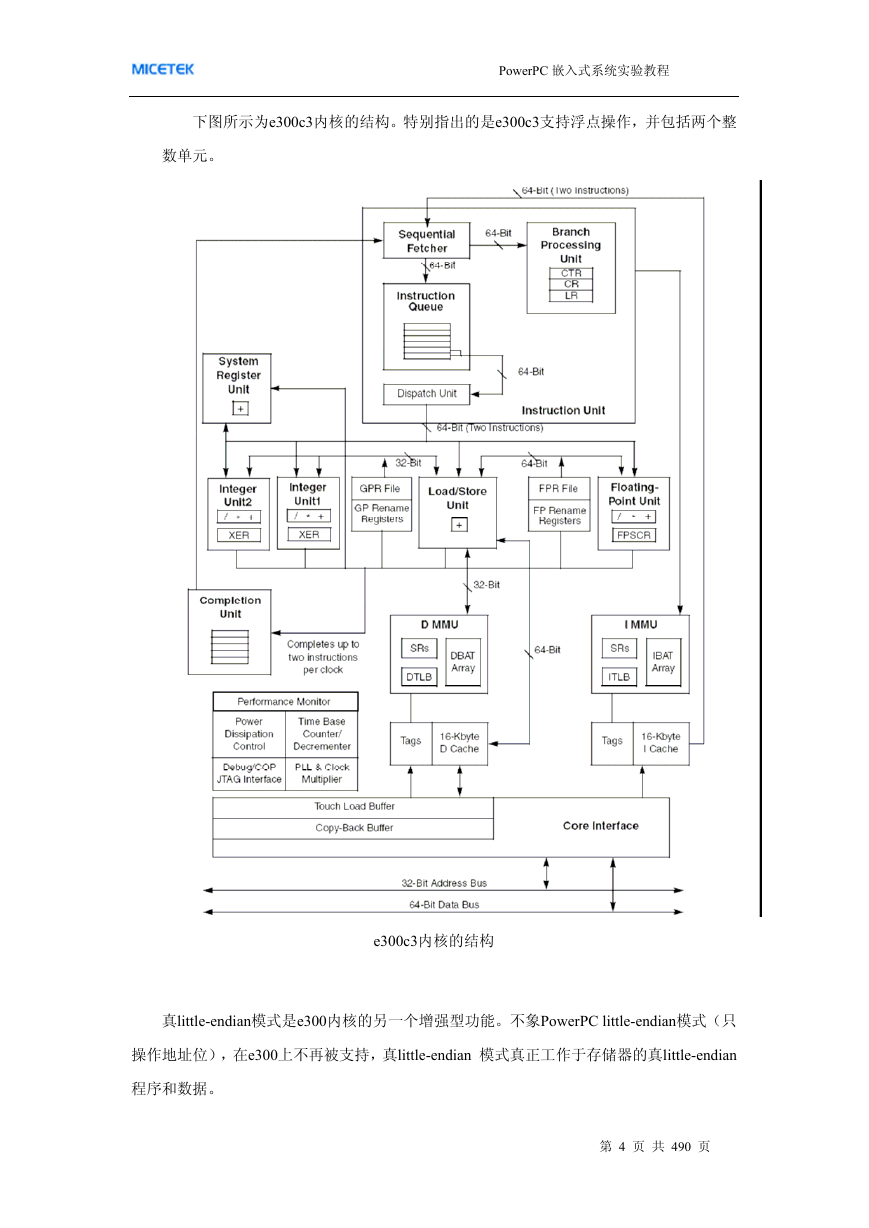

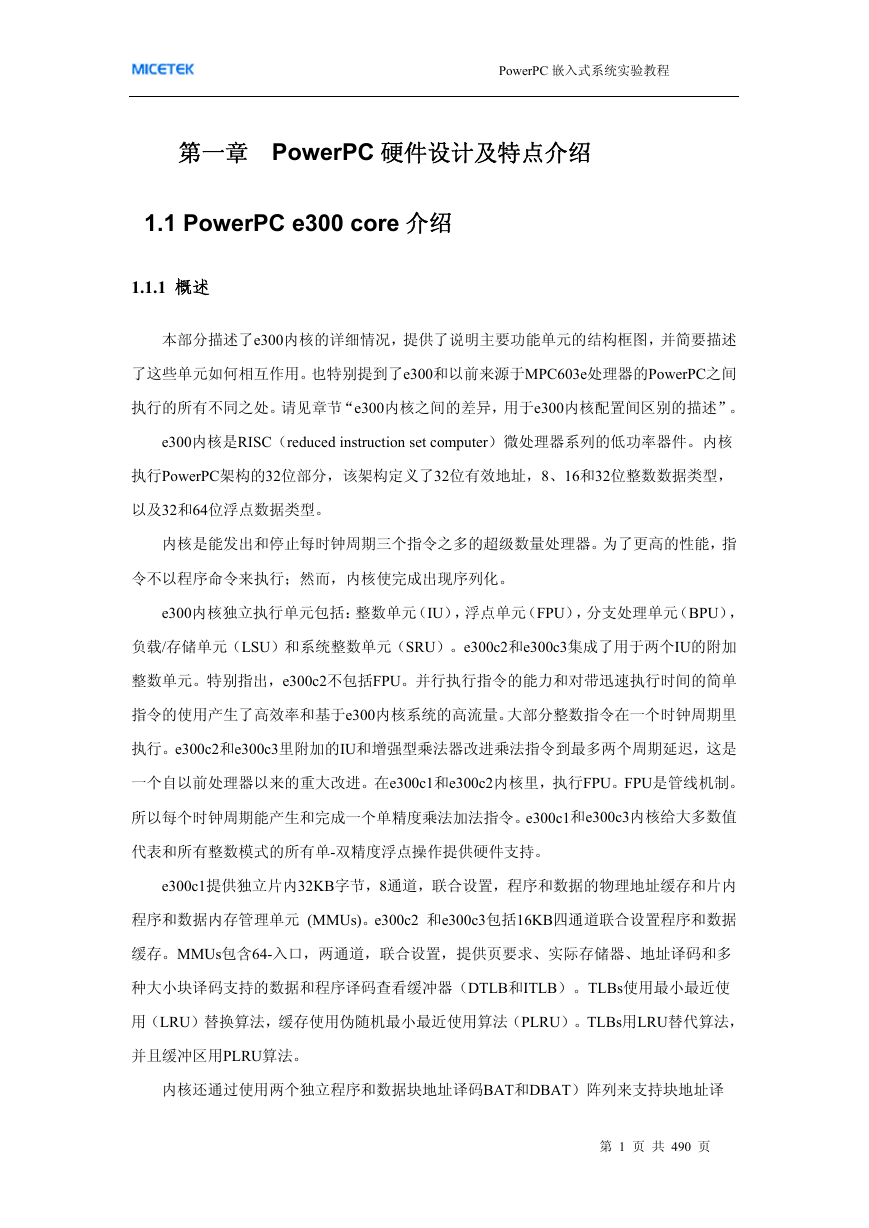

下图所示为e300c1内核的结构框图。

e300c1内核的结构框图

第 2 页 共 490 页

�

PowerPC 嵌入式系统实验教程

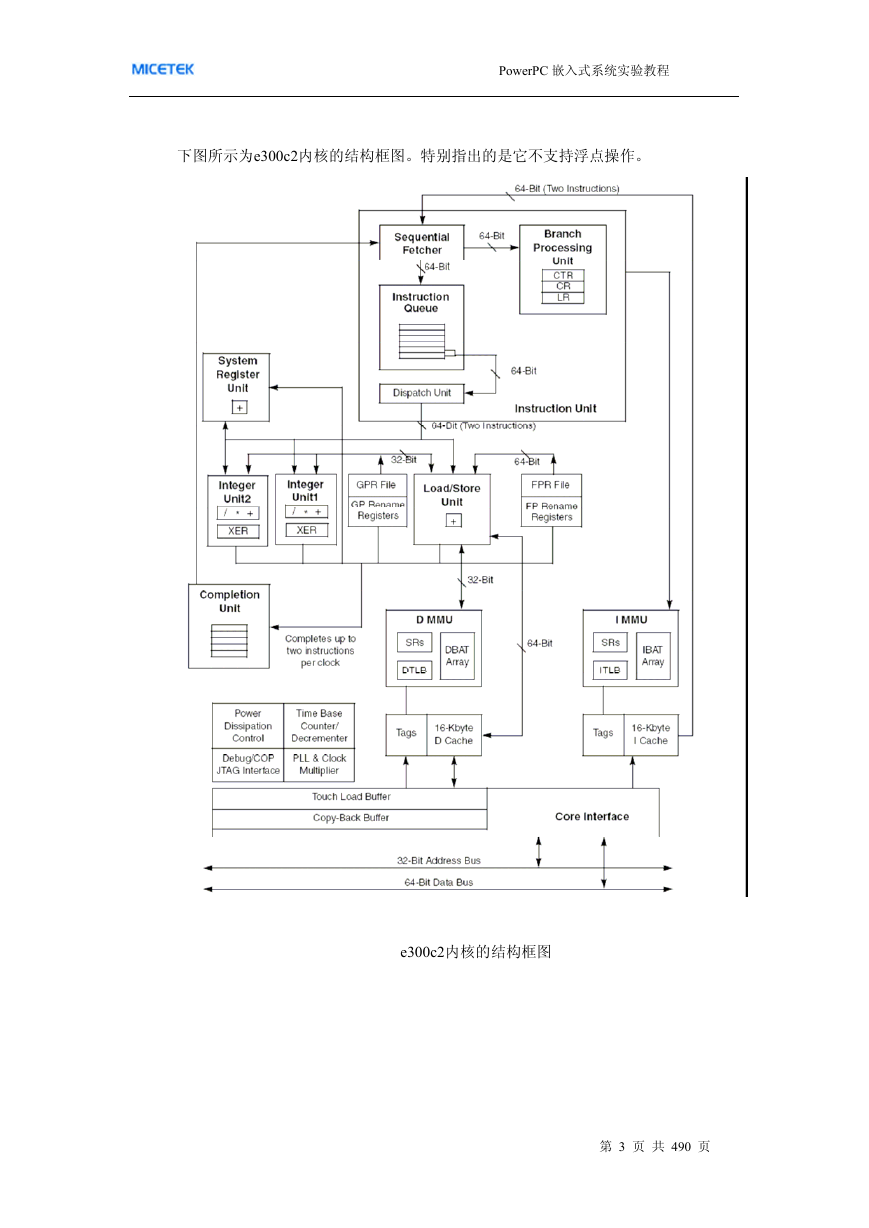

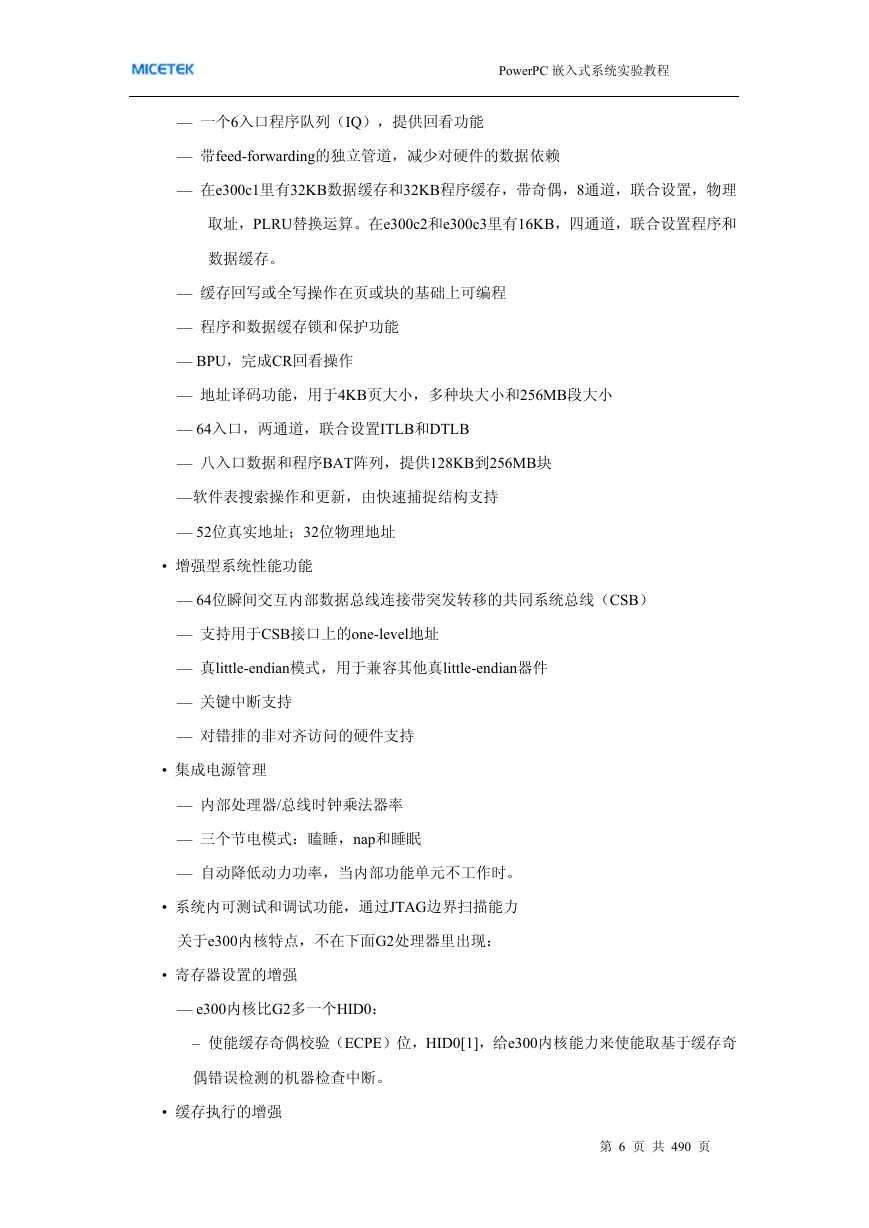

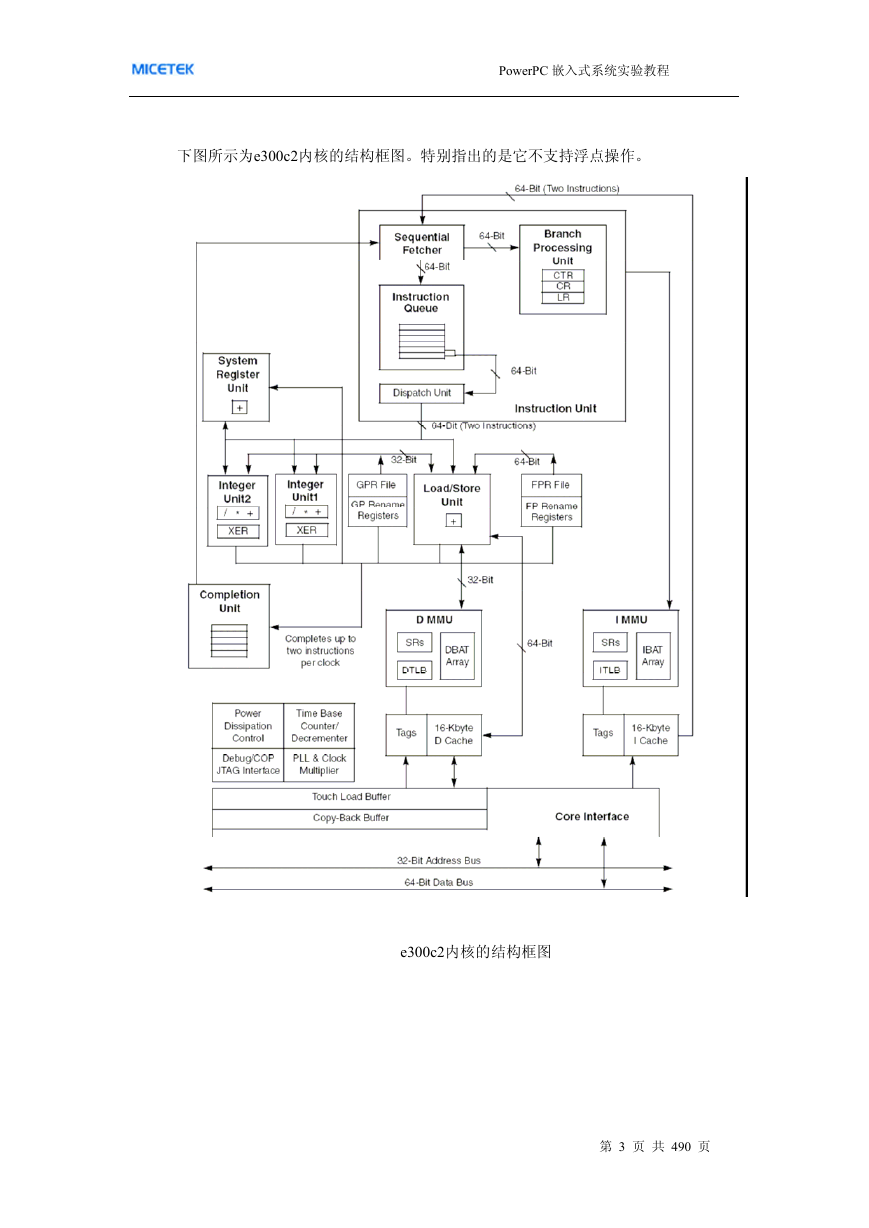

下图所示为e300c2内核的结构框图。特别指出的是它不支持浮点操作。

e300c2内核的结构框图

第 3 页 共 490 页

�

PowerPC 嵌入式系统实验教程

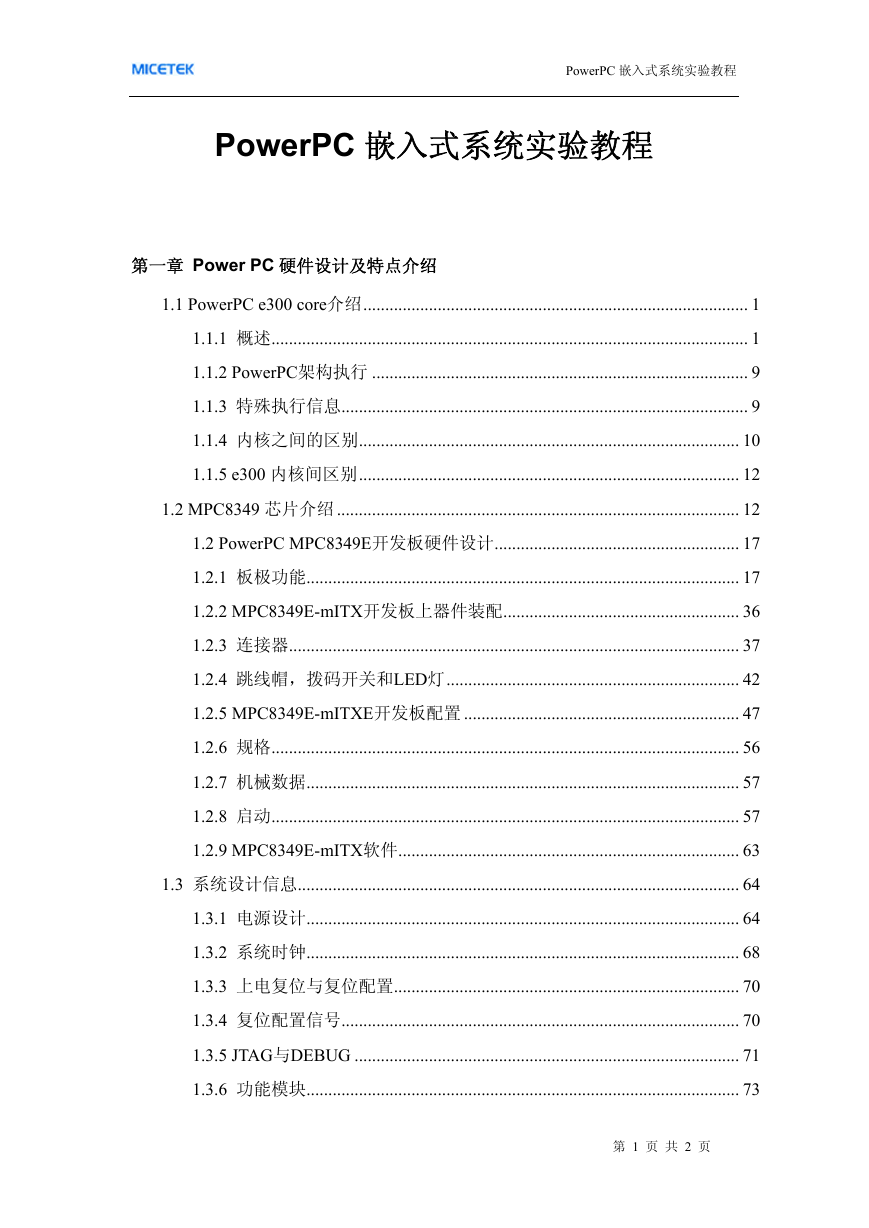

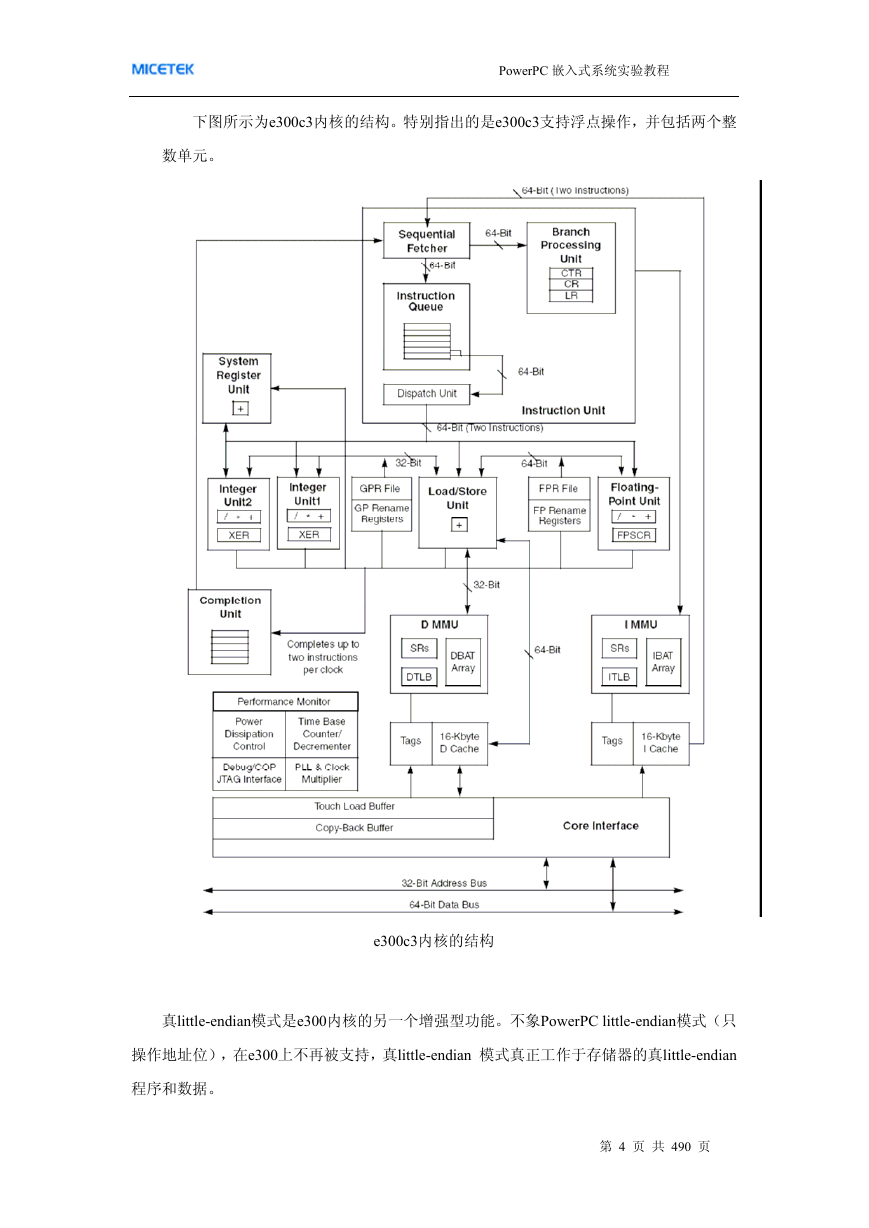

下图所示为e300c3内核的结构。特别指出的是e300c3支持浮点操作,并包括两个整

数单元。

e300c3内核的结构

真little-endian模式是e300内核的另一个增强型功能。不象PowerPC little-endian模式(只

操作地址位),在e300上不再被支持,真little-endian 模式真正工作于存储器的真little-endian

程序和数据。

第 4 页 共 490 页

�

PowerPC 嵌入式系统实验教程

关键中断是e300内核里的一个附加中断,有比系统管理中断更高的优先权。而且,e300

里的调试功能被改进了。控制寄存器的附加的SPRG中断用来增加操作系统的灵活性。

e300c3包括提供监视和计数预定义事件能力的性能监视器件,例如内核时钟,在程序缓

存,数据缓存或L2缓存里的misses,程序派遣类型,非预期分支和其他发生的事。这些事件

(可能是近似值)的数目能用来触发性能监视中断。

e300 core特点

e300内核的主要特征

• 高性能,超级数量微处理器内核

— 相当于三个指令每个时钟发生和停止(两个指令加一个分支指令)

— 相当于五个指令 在执行每个时钟里

— 单周期执行,对所有指令

— 管道浮点单元(FPU),用于所有单精度和双精度操作(在e300c2里不包括)

• 独立执行单元和两个寄存器文件

— 分支处理单元(BPU),展示静态分支预测

— 两个32位整数单元(IU)位于e300c2 和e300c3里。一个32位整数单元(IU)位于

e300c1。

— FPU基于IEEE® 754™ 标准,同时用于单和双精度操作

— 负载/存储单元(LSU),用于数据缓存和通用寄存器GPR和之间的数据转移和浮

点寄存器

— 系统寄存器单元(SRU)执行条件寄存器(CR),特殊用途寄存器(SPR)和整

数加/比较指令。加/比较指令也在IU中被执行。

— 32个32位GPRs ,用于整数操作数

— 32个64位FPRs ,用于单或双精度操作数

• 高程序和数据流量

— 零周期分支能力

— 在不可解决条件分支上的可编程静态分支预测

— e300c2和e300c3里的两个整数单元和增强的乘法器,用于增强型整数程序流量和最

大两个周期乘法指令延迟

— 程序取单元在每个时钟里能从程序缓存中取两个指令。

第 5 页 共 490 页

�

PowerPC 嵌入式系统实验教程

— 一个6入口程序队列(IQ),提供回看功能

— 带feed-forwarding的独立管道,减少对硬件的数据依赖

— 在e300c1里有32KB数据缓存和32KB程序缓存,带奇偶,8通道,联合设置,物理

取址,PLRU替换运算。在e300c2和e300c3里有16KB,四通道,联合设置程序和

数据缓存。

— 缓存回写或全写操作在页或块的基础上可编程

— 程序和数据缓存锁和保护功能

— BPU,完成CR回看操作

— 地址译码功能,用于4KB页大小,多种块大小和256MB段大小

— 64入口,两通道,联合设置ITLB和DTLB

— 八入口数据和程序BAT阵列,提供128KB到256MB块

—软件表搜索操作和更新,由快速捕捉结构支持

— 52位真实地址;32位物理地址

• 增强型系统性能功能

— 64位瞬间交互内部数据总线连接带突发转移的共同系统总线(CSB)

— 支持用于CSB接口上的one-level地址

— 真little-endian模式,用于兼容其他真little-endian器件

— 关键中断支持

— 对错排的非对齐访问的硬件支持

• 集成电源管理

— 内部处理器/总线时钟乘法器率

— 三个节电模式:瞌睡,nap和睡眠

— 自动降低动力功率,当内部功能单元不工作时。

• 系统内可测试和调试功能,通过JTAG边界扫描能力

关于e300内核特点,不在下面G2处理器里出现:

• 寄存器设置的增强

— e300内核比G2多一个HID0:

– 使能缓存奇偶校验(ECPE)位,HID0[1],给e300内核能力来使能取基于缓存奇

偶错误检测的机器检查中断。

• 缓存执行的增强

第 6 页 共 490 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc