Vol.23 No.1

January 2006

安 徽 工 业 大 学 学 报

J.of Anhui University of Technology

第 23 卷 第 1 期

2006 年 1 月

文章编号: 1671-7872(2006)01-0076-04

基于 FPG A 的 U SB 接口读写设计

( 南京航空航天大学 信息科学与技术学院, 江苏 南京 210016)

周 芳

摘要: 介绍了一种用 FPG A 实现 U SB 接口读写的设计方法。着重分析主循环, 中断服务处理器和 D 12 命令接口等几个结构模块

的设计。在 X ilinx ISE 软件平台上, 验证了读写模块的 V erilog H D L 语言代码。

关键词: U SB ; FPG A ; PD IU SB D 12; V erilog H D L

中图分类号: TN 402

文献标识码: B

D esign ofU SB Interface R ead-W rite B ased on FPG A

( C ollege of Inform ation Science & Technology,N anjing U niversity of A eronautics & A stronautics, N anjing 210016,

C hina)

ZHOU Fang

Abstr act: A w ay to design U SB interface R ead-W rite based on FPG A is introduced. M ain Loop, Interrupt Service

Processorand D 12 C om m and Interface,etc are analyzed and designed,and realized by V erilog H D L in X ilinx ISE .

Key wor ds: U niversalSerialB us; FPG A ; PD IU SB D 12; V erilog H D L

引

言

U SB (U niversalSerialB us)就是通用串行总线, 是近年来应用在 PC 领域的新型接口技术。由于 U SB 可以用

简便有效的方法与多种类型的外设通信, 导致了 U SB 接口的设计和编程比较复杂。为了降低设计者的开发

难度, 使用专用的 U SB 控制器已成为首选方案。

目 前 市 场 上 供 应 的 U SB 控 制 器 主 要 有 两 种: 一 种 是 微 控 制 器( M C U) 集 成 在 芯 片 里 面, 如 C Y PR E SS 的

E Z-U SB 和 SIE M E N S 的 C 541 等; 另一种就 是纯粹的 U SB 接 口芯片, 仅用 来处理 U SB 通 信, 由另一个 外部

M C U 管理 U SB 控制器的寄存器、设备描述符的获取和数据包的交换等, U SB 控制器使用串行口或并行口与

M C U 连接。这类芯片主要有 PH ILIPS 的 PD IU SB D 11( I2C 接口) 和 PD IU SB D 12( 并行接口) 等。文中所采用的

是 PH ILIPS 公司的 PD IU SB D 12 器件。

如今, 计算机外围设备市场上使用 U SB 接口的数码相机、扫描仪、U 盘和鼠标等设备比较常见, 这些设备

均可采用外部 M C U 加 U SB 接口芯片的设计。如果设备的应用比较简单, 那么 M C U 所要处理的事务量不大,

它的某些功 能不一定能 派上用场, 这 时完全可以 考虑用现场 可 编 程 门 阵 列( FPG A) 来 取 代 微 控 制 器, 管 理

U SB 控制器的寄存器、设备描述符的获取和数据包的交换等。此外, 由于 FPG A 能够满足低功率和可重配置

逻辑解决方案的要求, 在复用和可移植性方面, FPG A 器件比 M C U 具有更高的胜算把握[1]。

用 FPG A 实现 U SB 接口的读写正是居于此思想来设计的, 由 U SB 设备控制器 PD IU SB D 12 ( 以下简称

D 12) 和 FPG A 组合在一起, 以实现与主机之间的数据通信。该方案实现的 U SB 通信便于修改且易于实现, 如

果 U SB 设备控制器部分是用 IP 核实现的, 还可以与 FPG A 相结合, 作为一个功能模块嵌入到 SO C 中, 可使

不同情况最大限度地灵活设计片上系统。

收稿日期: 2005- 05- 10

作者简介: 周芳( 1979- ) , 女, 江苏南京人, 硕士研究生, 助教, 研究方向为数字系统设计与计算机应用。

�

第 1 期

1 系统结构原理

周 芳:基于 F P G A 的 U S B 接口读写设计

77

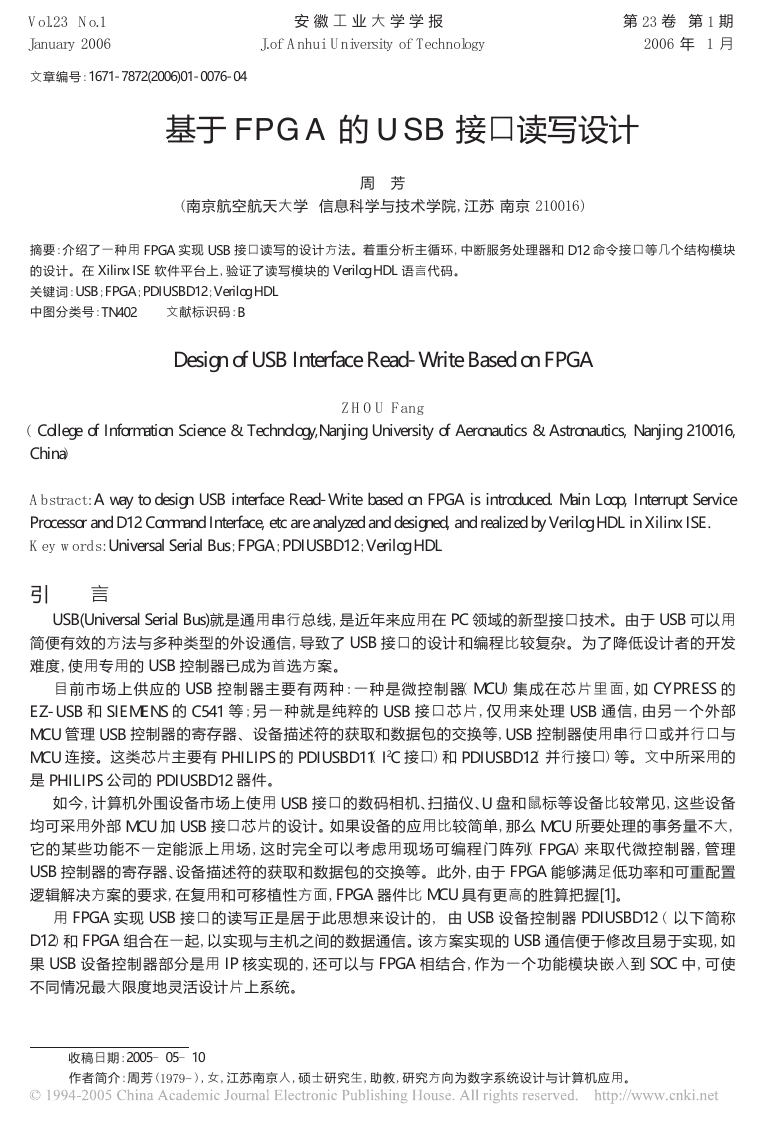

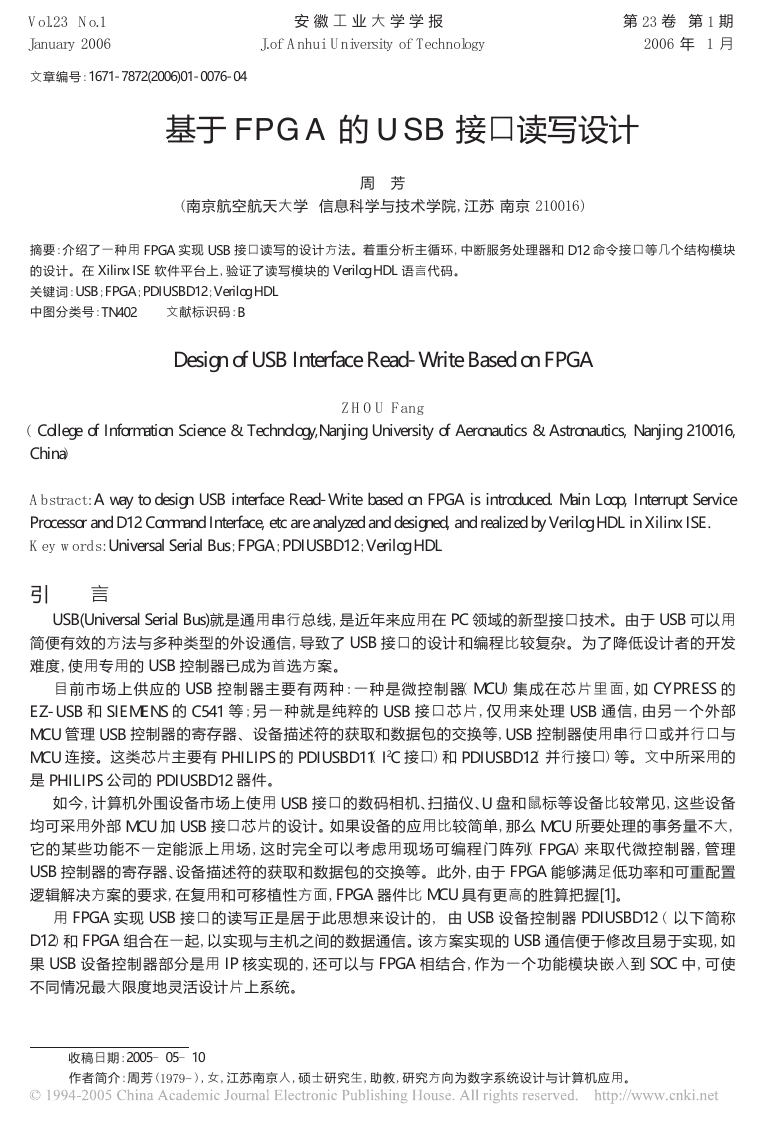

接 口 读 写 设 计 的 重 点 是 U S B 接 口 读 写 部

分, 其设计思 想主要是基 于 P D IU S B D 12 芯片

的应用[2]。

它通过与 D 12 芯片的通信, 对主机传来的

数据进行处理, 或者按照协议规定向主机发送

数据, 实现与主机之间的 U S B 通信。根据读写

模块所要实现的功能, 可以将其划分为几个部

分 : 主 循 环 ; 中 断 服 务 处 理 器 IS P (interrupt

service processor);D 12 命令接口;标准请求处

(standard request com m and

理 器 S R C P

processor)和 R A M 数据缓冲区, 其结构框图如

图 1 所示。

图 1 系统层次结构框图

2 USB 接口读写模块与 PDIUSBD12 的接口

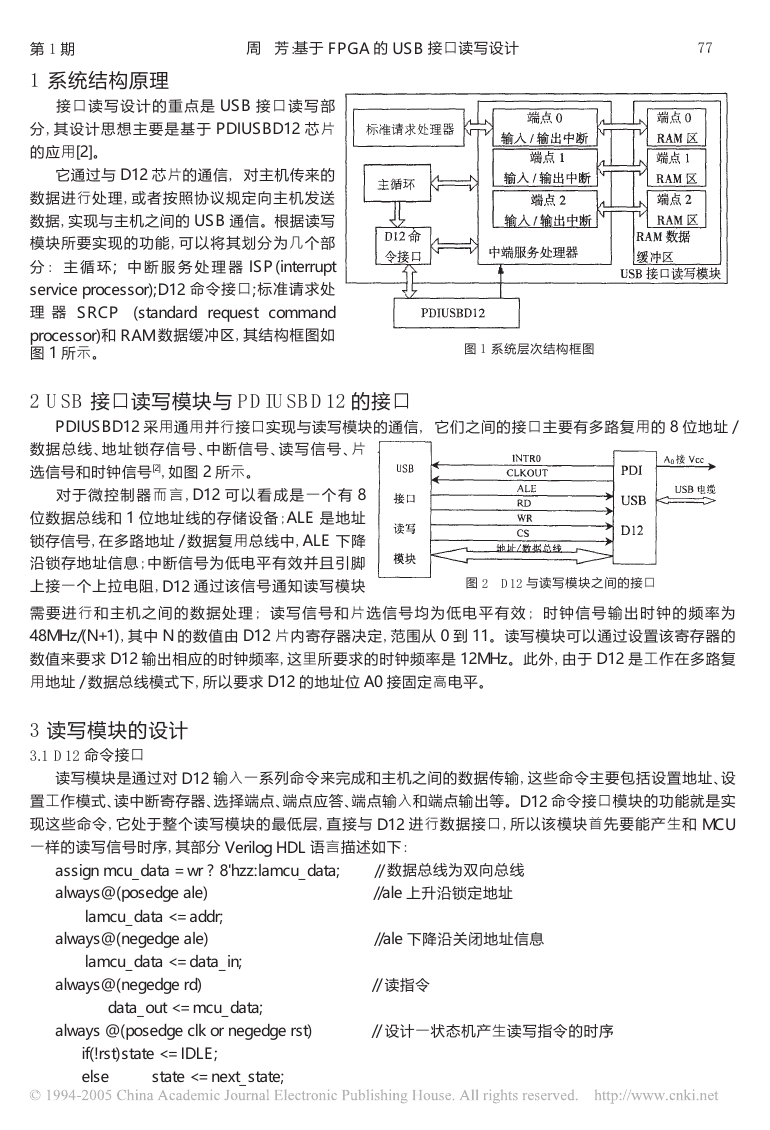

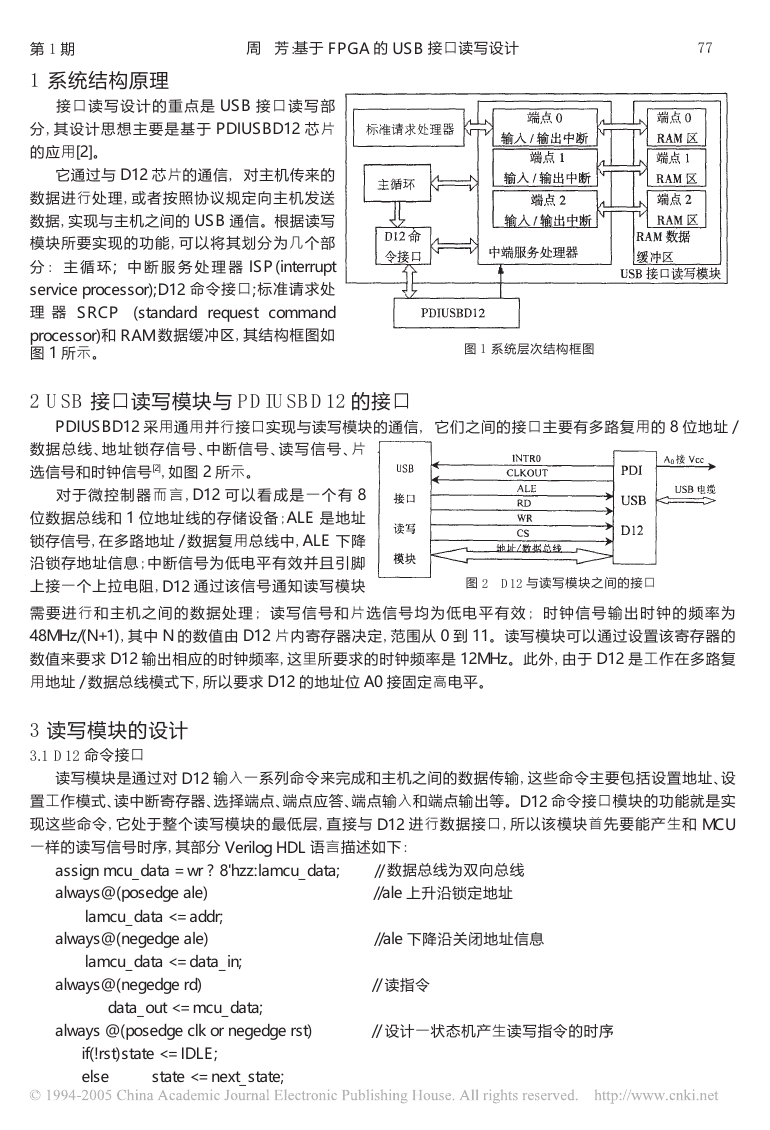

P D IU S B D 12 采用通用并行接口实现与读写模块的通信, 它们之间的接口主要有多路复用的 8 位地址 /

数据总线、地 址 锁 存 信 号 、中 断 信 号 、读 写 信 号 、片

选信号和时钟信号[2], 如图 2 所示。

对 于 微 控 制 器 而 言 , D 12 可 以 看 成 是 一 个 有 8

位数据总线和 1 位地址线的存储设备; A LE 是地址

锁存信号, 在多路地址 /数据复用总线中, A LE 下降

沿锁存地址信息; 中断信号为低电平有效并且引脚

上接一个上拉电阻, D 12 通过该信号通知读写模块

图 2 D12 与读写模块之间的接口

需 要 进 行 和 主 机 之 间 的 数 据 处 理; 读 写 信 号 和 片 选 信 号 均 为 低 电 平 有 效 ; 时 钟 信 号 输 出 时 钟 的 频 率 为

48M H z/(N +1), 其中 N 的数值由 D 12 片内寄存器决定, 范围从 0 到 11。读写模块可以通过设置该寄存器的

数值来要求 D 12 输出相应的时钟频率, 这里所要求的时钟频率是 12M H z。此外, 由于 D 12 是工作在多路复

用地址 /数据总线模式下, 所以要求 D 12 的地址位 A 0 接固定高电平。

3 读写模块的设计

3.1 D12 命令接口

读写模块是通过对 D 12 输入一系列命令来完成和主机之间的数据传输, 这些命令主要包括设置地址、设

置工作模式、读中断寄存器、选择端点、端点应答、端点输入和端点输出等。D 12 命令接口模块的功能就是实

现这些命令, 它处于整个读写模块的最低层, 直接与 D 12 进行数据接口, 所以该模块首先要能产生和 M C U

一样的读写信号时序, 其部分 V erilog H D L 语言描述如下:

assign m cu_data = w r ? 8'hzz:lam cu_data;

alw ays@ (posedge ale)

//数据总线为双向总线

//ale 上升沿锁定地址

lam cu_data <= addr;

alw ays@ (negedge ale)

lam cu_data <= data_in;

alw ays@ (negedge rd)

data_out<= m cu_data;

//ale 下降沿关闭地址信息

//读指令

alw ays @ (posedge clk or negedge rst)

//设计一状态机产生读写指令的时序

if(!rst)state <= ID LE ;

else

state <= next_state;

�

78

安 徽 工 业 大 学 学 报

2006 年

alw ays @ (posedge clk)

begin

next_state = state;

//默认时不改变当前状态, 状态机设计部分省略

针对不同的 D 12 命令, 数据总线上的数据和地址都不一样。在对 D 12 进行命令输入时, 首先向奇地址

( 如 0F 3H ) 输出相应的命令代码, 然后再向偶地址( 如 0F 0H ) 输出数据, 或从偶地址读回数据。比如要实现读

中断寄存器命令, D 12 命令接口模块先向 0F 3H 地址输入数据 0F 4H ( D 12 读中断寄存器命令代码) , 然后再

从 0F 0H 的地址单元读回一字节数据, 该数据内容就是中断寄存器的内容。

3.2 中断服务处理器

D 12 是由中断信号通知接口读写模块和主机之间进行数据处理。中断服务处理器在接收到该信号后, 通

过 D 12 命令接口向 D 12 发送读中断寄存器命令, 根据得到的中断寄存器中的内容来转入相应的中断服务。

根据 D 12 的应用特性和 U S B 协议[3], 可以把中断服务类型分为 6 类: 端点 0 输入中断 /输出中断, 端点 1 输

入中断 /输出中断和端点 2 输入中断 /输出中断。其部分 V erilog H D L 语言描述如下:

case(IN IS R )

//总线挂起状态

//IN IS R : 中断寄存器

8'b10000000:S U S P E N D = 1'b1;

8'b01000000:B U S R S T = 1'b1;//总线复位状态

8'b00100000: E P 0T X = 1'b1; //端点 0 输入中断

8'b00010000: E P 0R X = 1'b1; //端点 0 输出中断

8'b00001000: E P 1T X = 1'b1; //端点 1 输入中断

8'b00000100: E P 1R X = 1'b1; //端点 1 输出中断

8'b00000010: E P 2T X = 1'b1; //端点 2 输入中断

8'b00000001: E P 2R X = 1'b1; //端点 2 输出中断

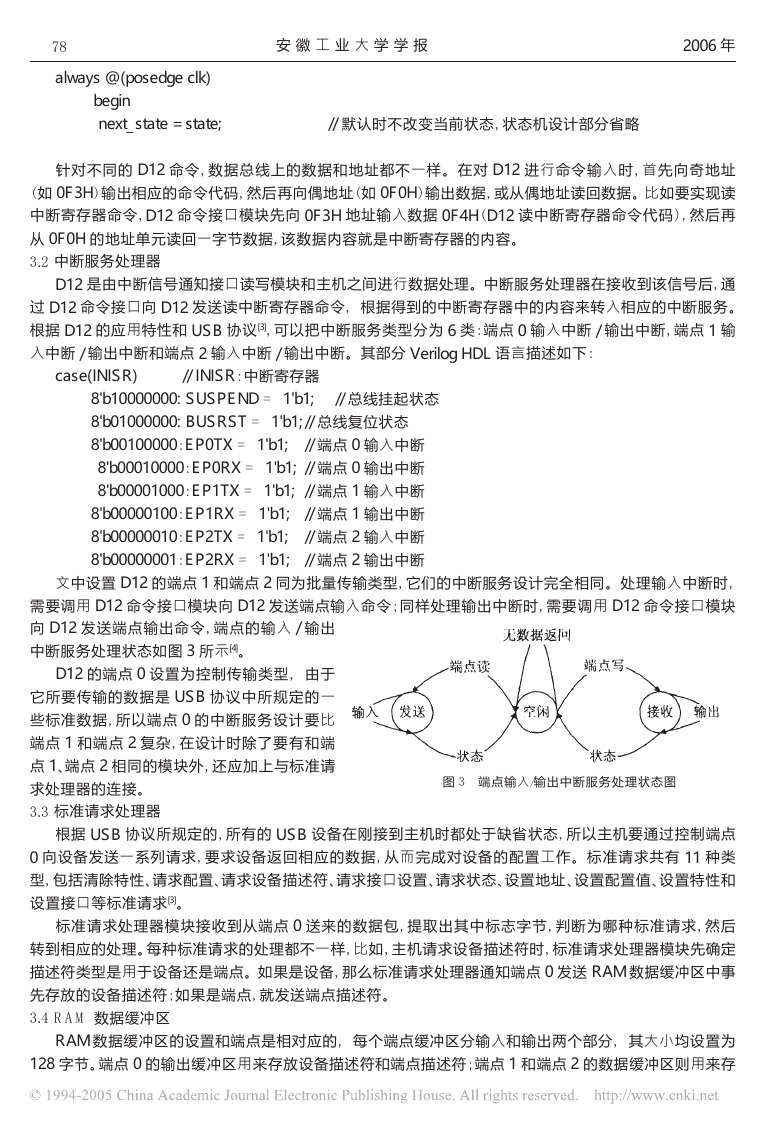

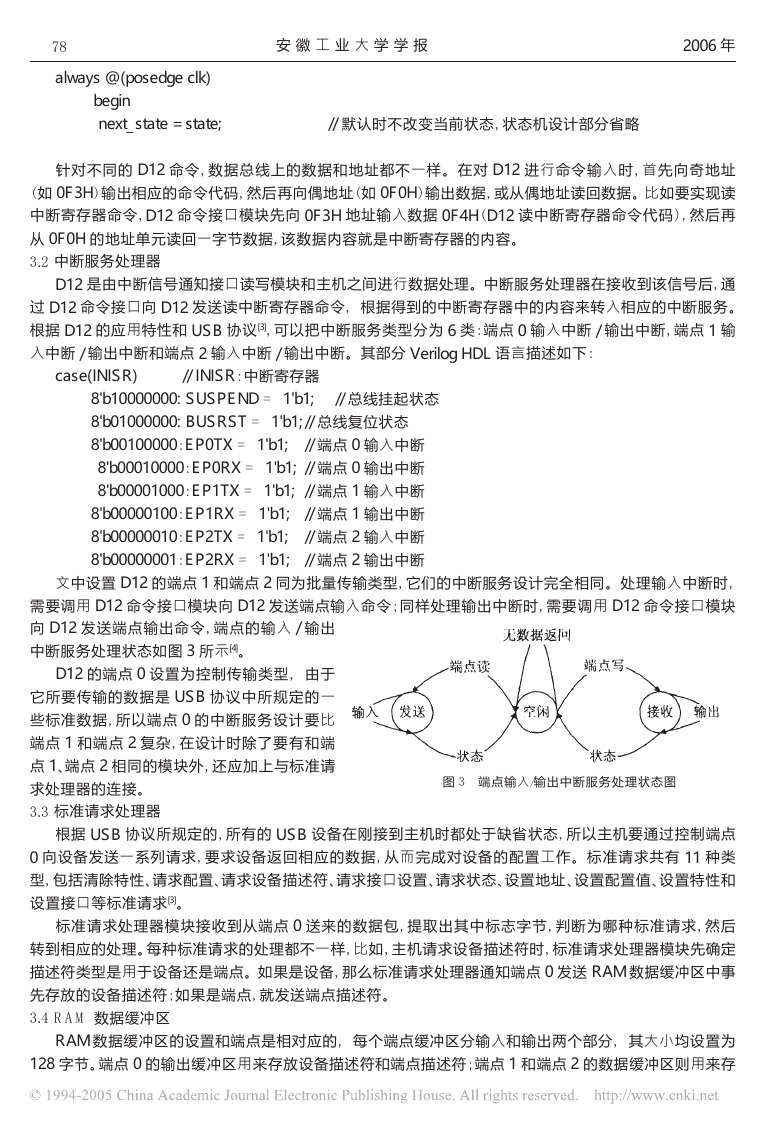

文中设置 D 12 的端点 1 和端点 2 同为批量传输类型, 它们的中断服务设计完全相同。处理输入中断时,

需要调用 D 12 命令接口模块向 D 12 发送端点输入命令; 同样处理输出中断时, 需要调用 D 12 命令接口模块

向 D 12 发送端点输出命令, 端点的输入 /输出

中断服务处理状态如图 3 所示[4]。

D 12 的端点 0 设置为控制传输类型, 由于

它所要传输的数据是 U S B 协议中所规定的一

些标准数据, 所以端点 0 的中断服务设计要比

端点 1 和端点 2 复杂, 在设计时除了要有和端

点 1、端点 2 相同的模块外, 还应加上与标准请

求处理器的连接。

3.3 标准请求处理器

图 3 端点输入/输出中断服务处理状态图

根据 U S B 协议所规定的, 所有的 U S B 设备在刚接到主机时都处于缺省状态, 所以主机要通过控制端点

0 向设备发送一系列请求, 要求设备返回相应的数据, 从而完成对设备的配置工作。标准请求共有 11 种类

型, 包括清除特性、请求配置、请求设备描述符、请求接口设置、请求状态、设置地址、设置配置值、设置特性和

设置接口等标准请求[3]。

标准请求处理器模块接收到从端点 0 送来的数据包, 提取出其中标志字节, 判断为哪种标准请求, 然后

转到相应的处理。每种标准请求的处理都不一样, 比如, 主机请求设备描述符时, 标准请求处理器模块先确定

描述符类型是用于设备还是端点。如果是设备, 那么标准请求处理器通知端点 0 发送 R A M 数据缓冲区中事

先存放的设备描述符; 如果是端点, 就发送端点描述符。

3.4 RAM 数据缓冲区

R A M 数据缓冲区的设置和端点是相对应的, 每个端点缓冲区分输入和输出两个部分, 其大小均设置为

128 字节。端点 0 的输出缓冲区用来存放设备描述符和端点描述符; 端点 1 和端点 2 的数据缓冲区则用来存

�

第 1 期

周 芳:基于 F P G A 的 U S B 接口读写设计

79

放实际应用中传输的数据。

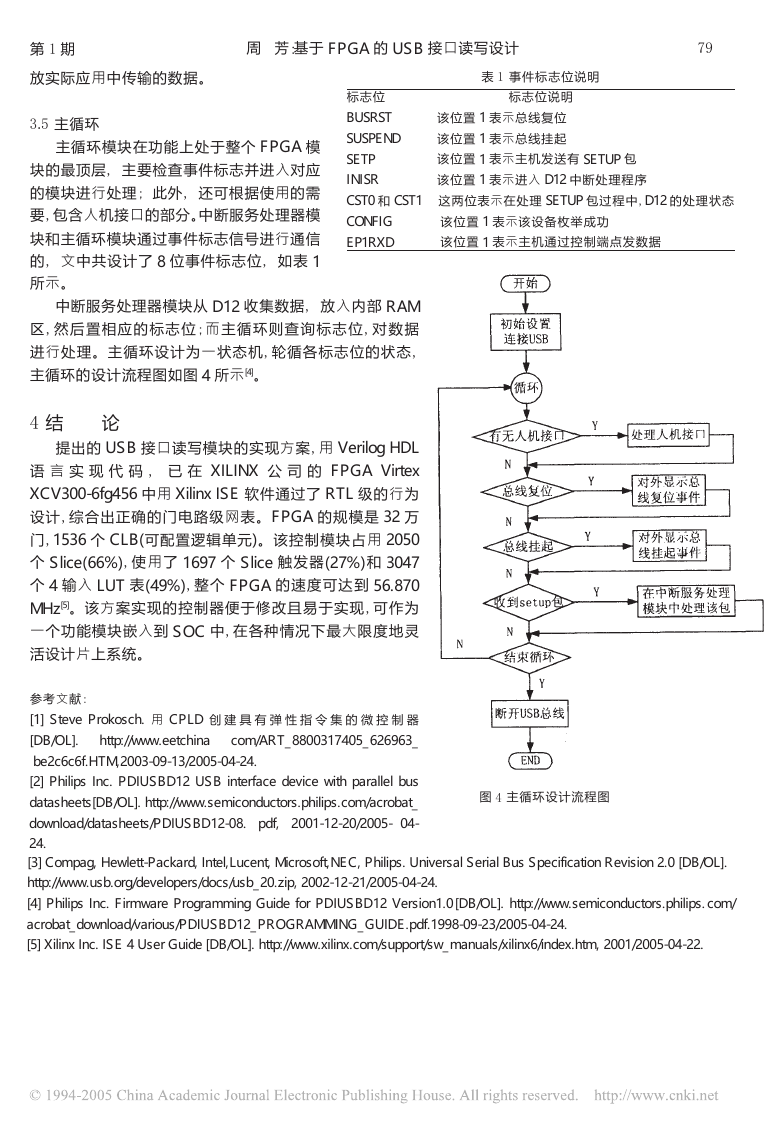

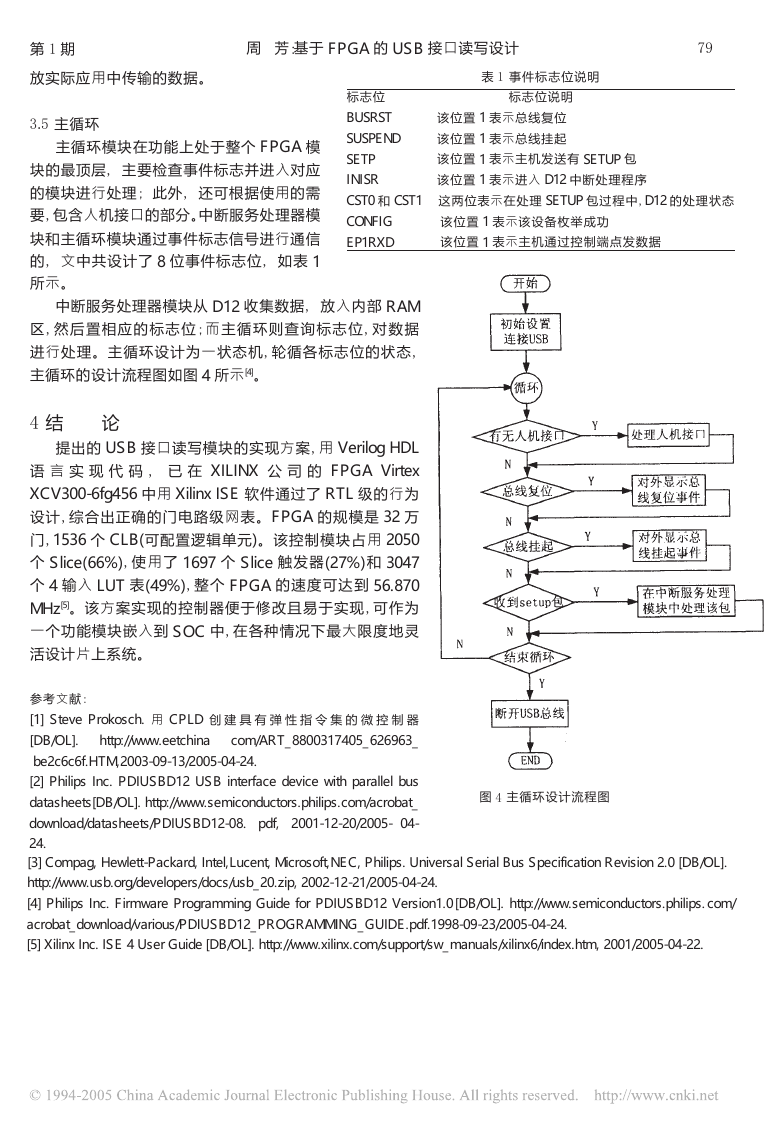

3.5 主循环

主循环模块在功能上处于整个 F P G A 模

块的最顶层, 主要检查事件标志并进入对应

的模块进行处理; 此外, 还可根据使用的需

要, 包含人机接口的部分。中断服务处理器模

块和主循环模块通过事件标志信号进行通信

的, 文中共设计了 8 位事件标志位, 如表 1

所示。

标志位

B U SR ST

表 1 事件标志位说明

标志位说明

该位置 1 表示总线复位

SU SPE N D

该位置 1 表示总线挂起

SE TP

该位置 1 表示主机发送有 SE TU P 包

IN ISR

C ST0 和 C ST1 这两位表示在处理 SE TU P 包过程中, D 12 的处理状态

该位置 1 表示进入 D 12 中断处理程序

C O N FIG

E P1R X D

该位置 1 表示该设备枚举成功

该位置 1 表示主机通过控制端点发数据

中断服务处理器模块从 D 12 收集数据, 放入内部 R A M

区, 然 后置相应的 标志位; 而 主循环则查 询标志位, 对 数 据

进行处理。主循环设计为一状态机, 轮循各标志位的状态,

主循环的设计流程图如图 4 所示[4]。

4 结

论

提出的 U S B 接口读写模块的实现方案, 用 V erilog H D L

语 言 实 现 代 码 , 已 在 X ILIN X 公 司 的 F P G A V irtex

X C V 300-6fg456 中用 X ilinx IS E 软件通过了 R T L 级的行为

设计, 综合出正确的门电路级网表。F P G A 的规模是 32 万

门, 1536 个 C LB (可配置逻辑单元)。该控制模块占用 2050

个 S lice(66% ), 使用了 1697 个 S lice 触发器(27% )和 3047

个 4 输入 LU T 表(49% ), 整个 F P G A 的速度可达到 56.870

M H z[5]。该方案实现的控制器便于修改且易于实现, 可作为

一个功能模块嵌入到 S O C 中, 在各种情况下最大限度地灵

活设计片上系统。

参考文献:

[1] S teve P rokosch. 用 C P LD 创 建 具 有 弹 性 指 令 集 的 微 控 制 器

[D B /O L].

http://w w w .eetchina

com /A R T _8800317405_626963_

be2c6c6f.H T M ,2003-09-13/2005-04-24.

[2] P hilips Inc. P D IU S B D 12 U S B interface device w ith parallel bus

datasheets[D B /O L].http://w w w .sem iconductors.philips.com /acrobat_

dow nload/datasheets/P D IU S B D 12-08. pdf, 2001-12-20/2005- 04-

图 4 主循环设计流程图

24.

[3]C om pag,H ew lett-P ackard,Intel,Lucent,M icrosoft,N E C ,P hilips.U niversalS erialB us S pecification R evision 2.0 [D B /O L].

http://w w w .usb.org/developers/docs/usb_20.zip,2002-12-21/2005-04-24.

[4] P hilips Inc. F irm w are P rogram m ing G uide for P D IU S B D 12 V ersion1.0 [D B /O L]. http://w w w .sem iconductors.philips.com /

acrobat_dow nload/various/P D IU S B D 12_P R O G R A M M IN G _G U ID E .pdf.1998-09-23/2005-04-24.

[5]X ilinx Inc.IS E 4 U serG uide [D B /O L].http://w w w .xilinx.com /support/sw _m anuals/xilinx6/index.htm ,2001/2005-04-22.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc