广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 http://www.zlgmcu.com

PDIUSBD12 带并行总线的 USB 接口器件

特性

符合通用串行总线 USB

1.1 版规范

高性能 USB 接口器件 集成了 SIE

FIFO 存储器 收发器以及电压调整器

符合大多数器件的分类规格

可与任何外部微控制器/微处理实现高速并行接口 2M 字节/秒

完全自治的直接内存存取 DMA 操作

集成 320 字节多结构 FIFO 存储器

主端点的双缓冲配置增加了数据吞吐量并轻松实现实时数据传输

在批量模式和同步模式下均可实现 1M 字节/秒的数据传输速率

具有良好 EMI 特性的总线供电能力

在挂起时可控制 LazyClock 输出

可通过软件控制与 USB 的连接

采用 GoodLink 技术的连接指示器,在通讯时使 LED 闪烁

可编程的时钟频率输出

符合 ACPI

OnNOW 和 USB 电源管理的要求

内部上电复位和低电压复位电路

有 SO28 和 TSSOP28 封装

工业级操作温度

40

+85

高于 8kV 的在片静电防护电路 减少了额外元件的费用

具有高错误恢复率(>99%)的全扫描设计确保了高品质

双电源操作 3.3±0.3V 或扩展的 5V 电源,范围为 3.6~5.5V

多中断模式实现批量和同步传输

描述

PDIUSBD12 是一款性价比很高的 USB 器件 它通常用作微控制器系统中实现与微控制器进行通信的

高速通用并行接口 它还支持本地的 DMA 传输

这种实现 USB 接口的标准组件使得设计者可以在各种不同类型微控制器中选择出最合适的微控制器

这种灵活性减小了开发的时间 风险以及费用 通过使用已有的结构和减少固件上的投资 从而用最快捷

的方法实现最经济的 USB 外设的解决方案

PDIUSBD12 完全符合 USB1.1 版的规范 它还符合大多数器件的分类规格 成像类 海量存储器件

通信器件 打印设备以及人机接口设备 同样地 PDIUSBD12 理想地适用于许多外设 例如 打印机 扫

描仪 外部的存储设备 Zip 驱动器 和数码相机等等 它使得当前使用 SCSI 的系统可以立即降低成本

PDIUSBD12 所具有的低挂起功耗连同 LazyClock 输出可以满足使用 ACPI OnNOW 和 USB 电源管理

的要求 低的操作功耗可以应用于使用总线供电的外设

此外它还集成了许多特性 包括 SoftConnetTM GoodLinkTM 可编程时钟输出 低频晶振和终止寄存

器集合 所有这些特性都为系统显著节约了成本 同时使 USB 功能在外设上的应用变得容易

订购信息

封装

28 脚塑料 SO

28 脚塑料 TSSOP

温度范围

-40 ~85

-40 ~85

编号

PDIUSBD12 D

PDIUSBD12 PW

1

�

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 http://www.zlgmcu.com

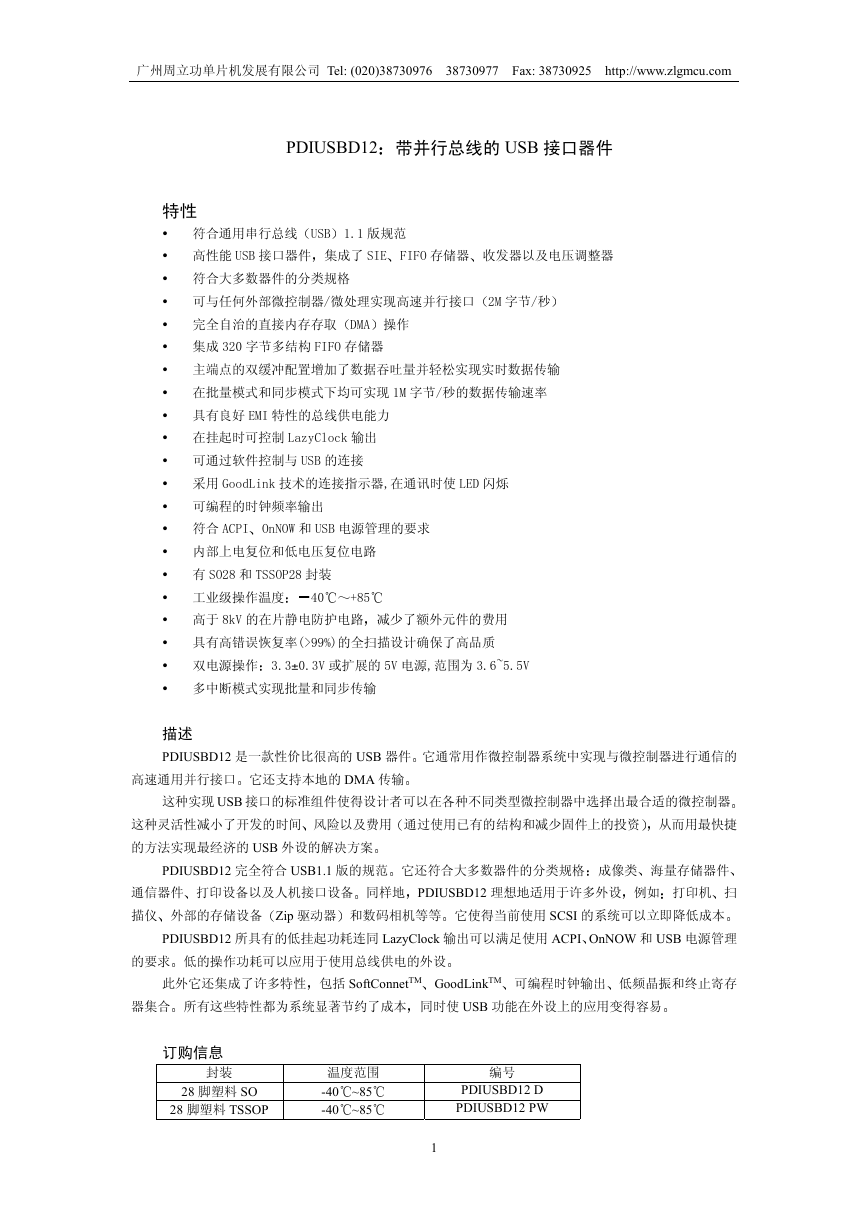

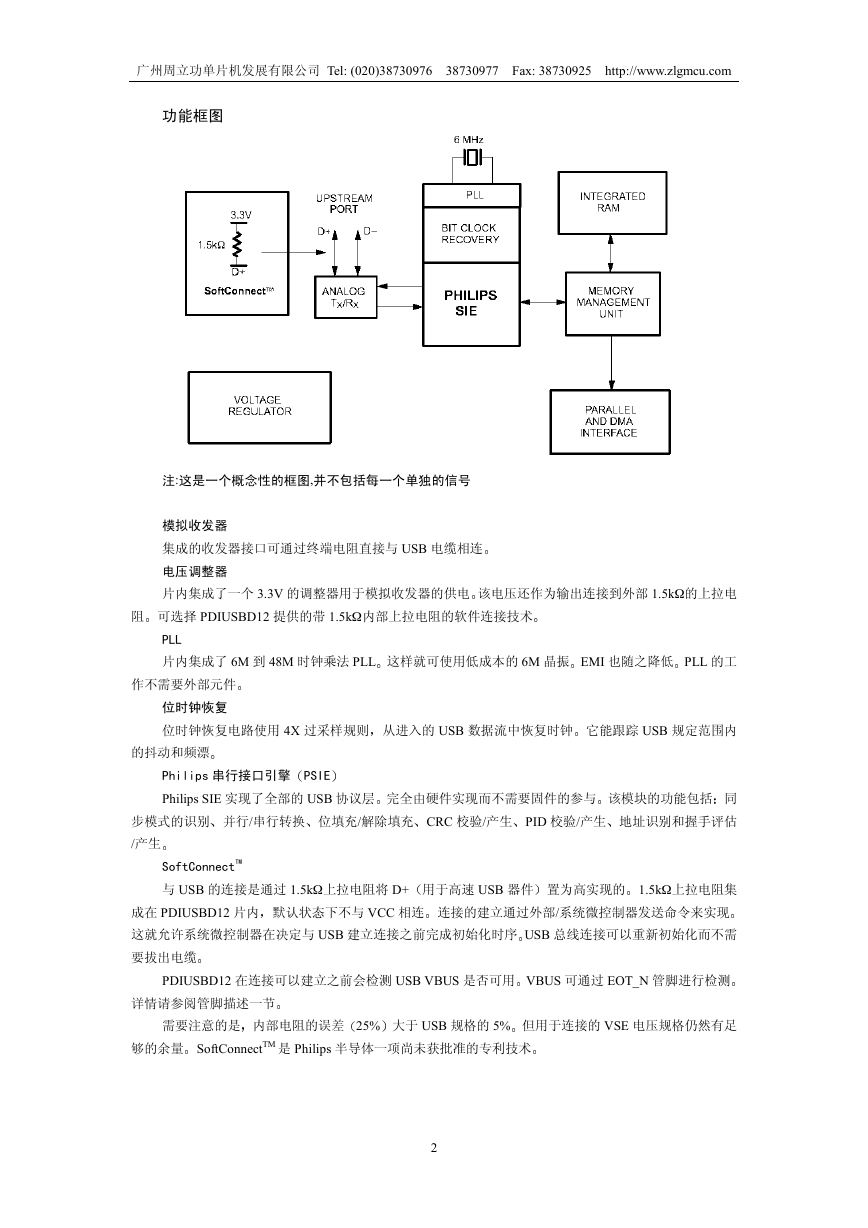

功能框图

注:这是一个概念性的框图,并不包括每一个单独的信号

模拟收发器

集成的收发器接口可通过终端电阻直接与 USB 电缆相连

电压调整器

片内集成了一个 3.3V 的调整器用于模拟收发器的供电 该电压还作为输出连接到外部 1.5kΩ的上拉电

阻 可选择 PDIUSBD12 提供的带 1.5kΩ内部上拉电阻的软件连接技术

PLL

片内集成了 6M 到 48M 时钟乘法 PLL 这样就可使用低成本的 6M 晶振 EMI 也随之降低 PLL 的工

作不需要外部元件

位时钟恢复

位时钟恢复电路使用 4X 过采样规则 从进入的 USB 数据流中恢复时钟 它能跟踪 USB 规定范围内

的抖动和频漂

Philips 串行接口引擎 PSIE

Philips SIE 实现了全部的 USB 协议层 完全由硬件实现而不需要固件的参与 该模块的功能包括 同

步模式的识别 并行/串行转换 位填充/解除填充 CRC 校验/产生 PID 校验/产生 地址识别和握手评估

/产生

SoftConnectTM

与 USB 的连接是通过 1.5kΩ上拉电阻将 D+ 用于高速 USB 器件 置为高实现的 1.5kΩ上拉电阻集

成在 PDIUSBD12 片内 默认状态下不与 VCC 相连 连接的建立通过外部/系统微控制器发送命令来实现

这就允许系统微控制器在决定与 USB 建立连接之前完成初始化时序 USB 总线连接可以重新初始化而不需

要拔出电缆

PDIUSBD12 在连接可以建立之前会检测 USB VBUS 是否可用 VBUS 可通过 EOT_N 管脚进行检测

详情请参阅管脚描述一节

需要注意的是 内部电阻的误差 25% 大于 USB 规格的 5% 但用于连接的 VSE 电压规格仍然有足

够的余量 SoftConnectTM 是 Philips 半导体一项尚未获批准的专利技术

2

�

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 http://www.zlgmcu.com

GoodLinkTM

GoodLinkTM 技术可提供良好的 USB 连接指示 在枚举中 LED 指示根据通信的状况间歇闪烁 当

PDIUSBD12 成功地枚举和配置后 LED 指示将一直点亮 随后与 PDIUSBD12 之间成功的传输 带应答

将关闭 LED 处于挂起状态时 LED 将会关闭

该特性为 USB 器件 集线器和 USB 通信状态提供了用户友好的指示 作为一个诊断工具 它对隔离

故障的设备是很有用的 该特性降低了现场支持和热线的成本

存储器管理单元 MMU 和集成 RAM

在以 12M/s 的速率传输并与微控制器并口相连时 MMU 和集成 RAM 作为 USB 之间速度差异的缓冲

区 这就允许微控制器以它自己的速率对 USB 信息包进行读写

并行和 DMA 接口

一个普通的并行接口定义成易于使用 快速而且可以与主流的微控制器直接接口 对一个微控制器而

言 PDIUSBD12 看起来就象一个带 8 位数据总线和一个地址位 占用 2 个位置 的存储器件 PDIUSBD12

支持多路复用和非复用的地址和数据总线 还支持主端点与本地共享 RAM 之间直接读取的 DMA 传输 支

持单周期和突发模式的 DMA 传输

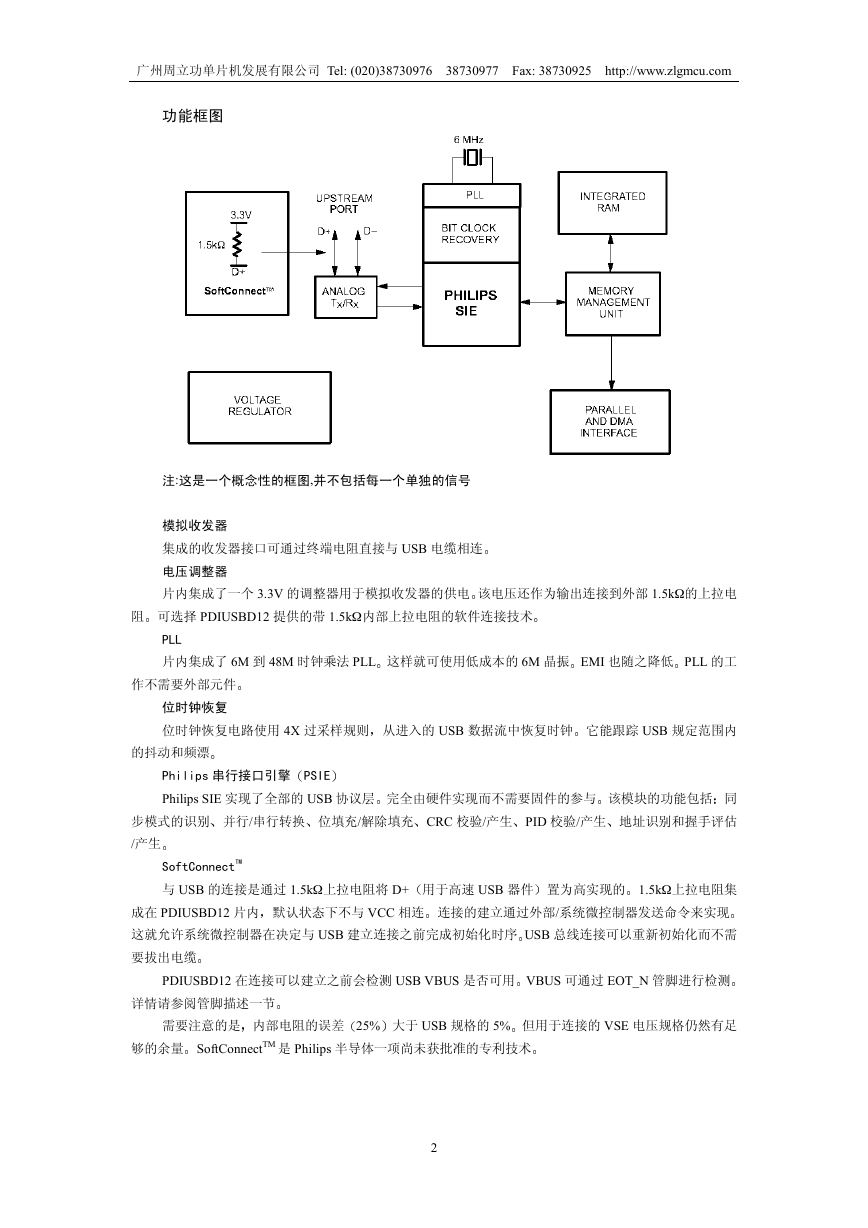

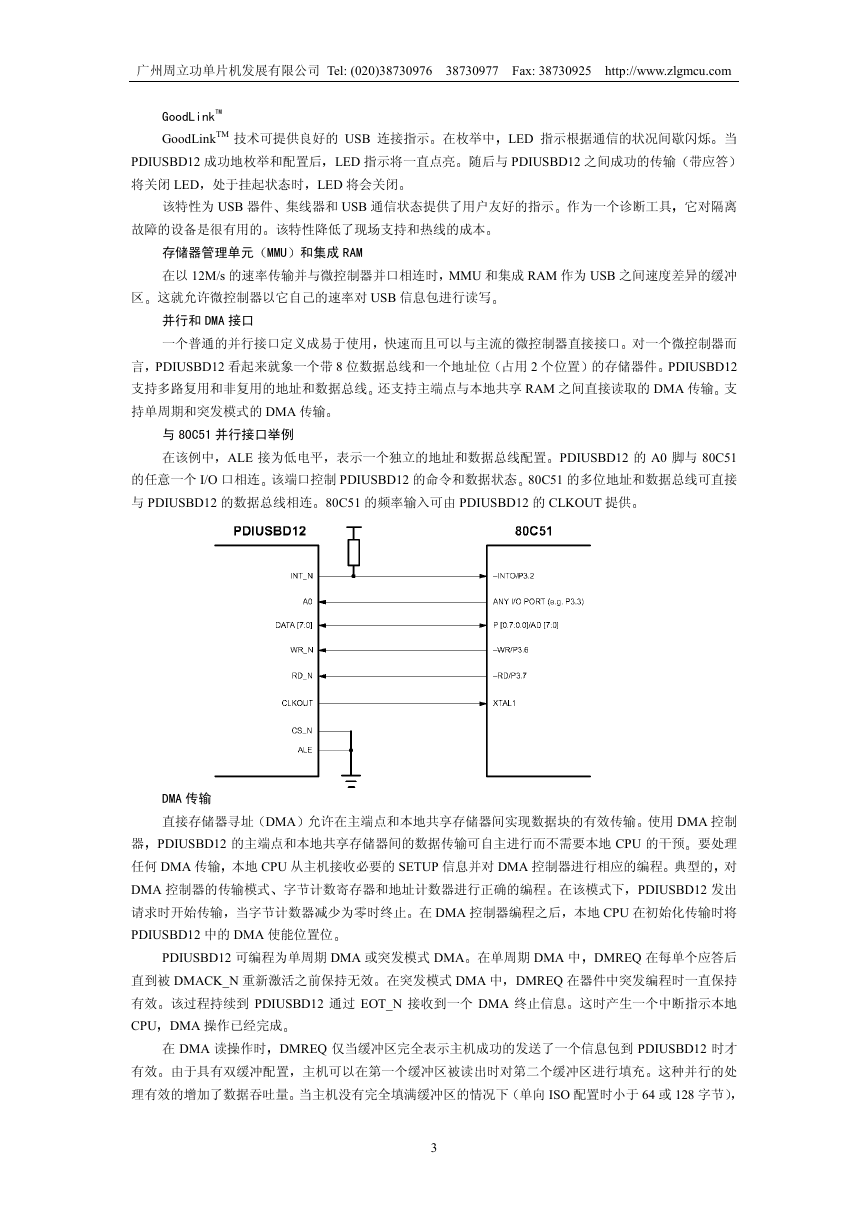

与 80C51 并行接口举例

在该例中 ALE 接为低电平 表示一个独立的地址和数据总线配置 PDIUSBD12 的 A0 脚与 80C51

的任意一个 I/O 口相连 该端口控制 PDIUSBD12 的命令和数据状态 80C51 的多位地址和数据总线可直接

与 PDIUSBD12 的数据总线相连 80C51 的频率输入可由 PDIUSBD12 的 CLKOUT 提供

DMA 传输

直接存储器寻址 DMA 允许在主端点和本地共享存储器间实现数据块的有效传输 使用 DMA 控制

器 PDIUSBD12 的主端点和本地共享存储器间的数据传输可自主进行而不需要本地 CPU 的干预 要处理

任何 DMA 传输 本地 CPU 从主机接收必要的 SETUP 信息并对 DMA 控制器进行相应的编程 典型的 对

DMA 控制器的传输模式 字节计数寄存器和地址计数器进行正确的编程 在该模式下 PDIUSBD12 发出

请求时开始传输 当字节计数器减少为零时终止 在 DMA 控制器编程之后 本地 CPU 在初始化传输时将

PDIUSBD12 中的 DMA 使能位置位

PDIUSBD12 可编程为单周期 DMA 或突发模式 DMA 在单周期 DMA 中 DMREQ 在每单个应答后

直到被 DMACK_N 重新激活之前保持无效 在突发模式 DMA 中 DMREQ 在器件中突发编程时一直保持

有效 该过程持续到 PDIUSBD12 通过 EOT_N 接收到一个 DMA 终止信息 这时产生一个中断指示本地

CPU DMA 操作已经完成

在 DMA 读操作时 DMREQ 仅当缓冲区完全表示主机成功的发送了一个信息包到 PDIUSBD12 时才

有效 由于具有双缓冲配置 主机可以在第一个缓冲区被读出时对第二个缓冲区进行填充 这种并行的处

理有效的增加了数据吞吐量 当主机没有完全填满缓冲区的情况下 单向 ISO 配置时小于 64 或 128 字节

3

�

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 http://www.zlgmcu.com

DMREQ 会在缓冲区的最后一个字节时无效 而不管当前的 DMA 突发计数 在更新了 DMA 突发计数的下

一个包发送时 DMREQ 再次被激活

DMA 的写操作与之相似 当缓冲区未装满时 DMREQ 一直有效 当缓冲区填满时 在下一个 IN 标

志将信息包送入主机 当传输完成之后 DMREQ 变为无效 同样的 双缓冲配置在这也改善了数据的吞吐

量 在非同步传输中 批量模式和中断 在数据被发送到主机之前 缓冲区需要通过 DMA 写操作完全装

满 唯一的例外是 在 DMA 传输结束时 EOT_N 接收的信号将会停止 DMA 写操作并且在下一个 IN 标志

置位时将缓冲区的内容传送到主机

在同步模式中 本地 CPU 和 DMA 控制器必须保证它们在一个 USB 帧 1ms 中能够吞吐的最大信

息包的规模 DMACK_N 的激活将自动选择主端点 端点 2 而不管当前选择的端点 PDIUSBD12 的 DMA

操作可通过普通的 I/O 对其它端点的存取实现交叉存取 DMA 操作可通过以下方式终止 复位 DMA 使能

寄存器位或 EOT_N 加上 DMACK_N 以及 RD_N/WR_N 的激活

PDIUSBD12 支持单地址模式中的 DMA 传输 也可以在 DMA 控制器的双地址模式中工作 在单地址

模式中 DMA 通过 DREQ DMACK_N,EOT_N,WR_N 和 RD_N 控制线实现传输 在双地址模式中

DMREQ,DMACK_N 和 EOT_N 未用 取而代之的是 CS_N,WR_N 和 RD_N 控制信号 需要遵循 PDIUSBD12

的 I/O 模式传输协议 在读周期中对 DMAC 信号源进行访问 在写周期对目标进行访问 传输需要两个单

独的总线周期来储存暂存在 DMAC 中的数据

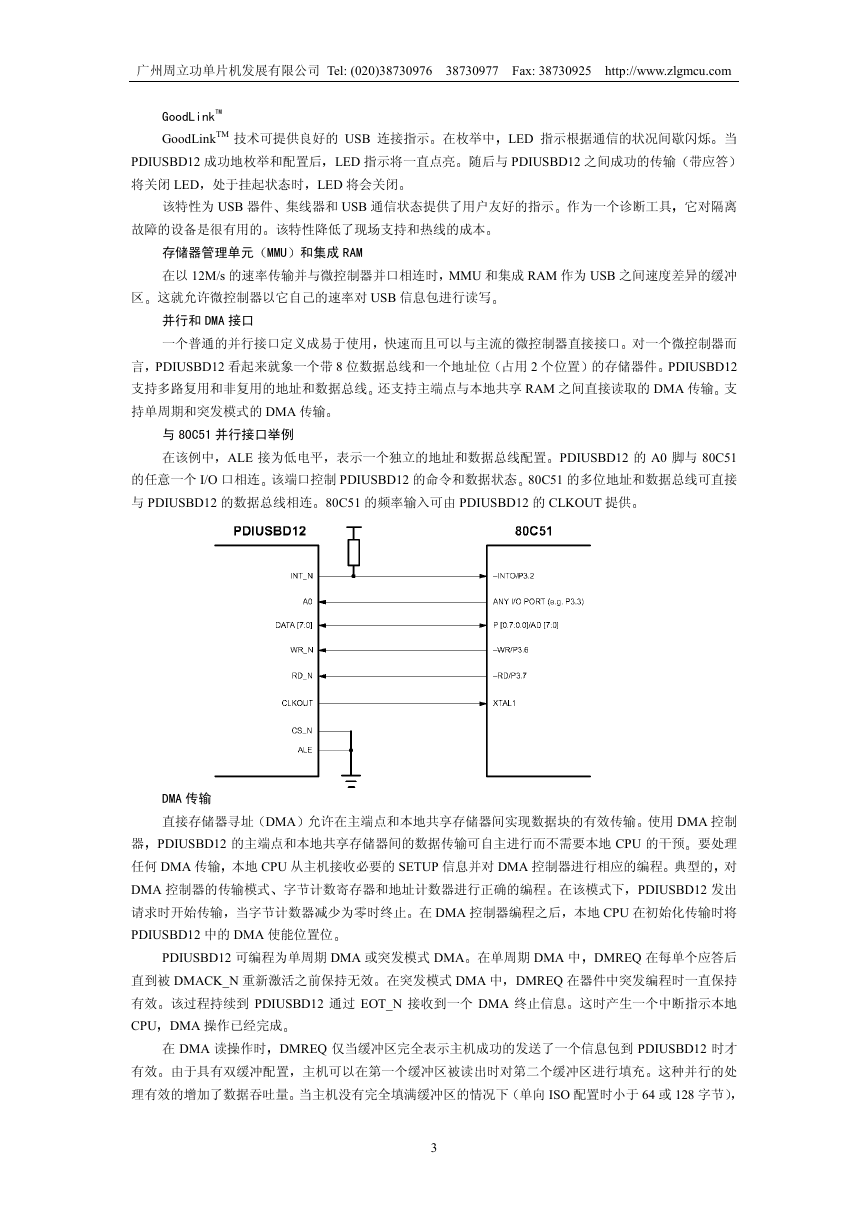

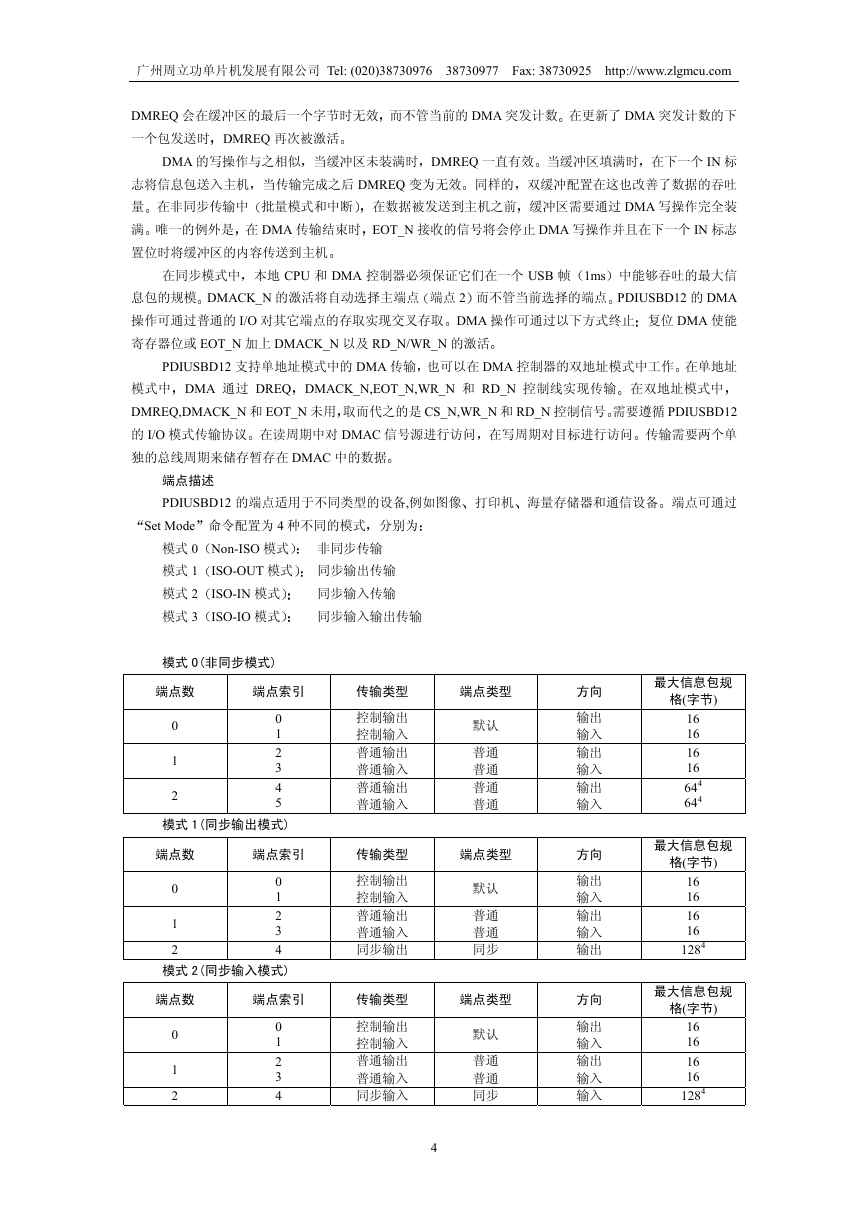

端点描述

PDIUSBD12 的端点适用于不同类型的设备,例如图像 打印机 海量存储器和通信设备 端点可通过

Set Mode 命令配置为 4 种不同的模式 分别为

模式 0 Non-ISO 模式 非同步传输

模式 1

模式 2

模式 3

ISO-OUT 模式 同步输出传输

ISO-IN 模式 同步输入传输

ISO-IO 模式 同步输入输出传输

模式 0(非同步模式)

端点数

端点索引

0

1

2

0

1

2

3

4

5

模式 1(同步输出模式)

端点数

端点索引

0

1

2

0

1

2

3

4

模式 2(同步输入模式)

端点数

端点索引

0

1

2

0

1

2

3

4

传输类型

控制输出

控制输入

普通输出

普通输入

普通输出

普通输入

传输类型

控制输出

控制输入

普通输出

普通输入

同步输出

传输类型

控制输出

控制输入

普通输出

普通输入

同步输入

端点类型

默认

普通

普通

普通

普通

端点类型

默认

普通

普通

同步

端点类型

默认

普通

普通

同步

4

方向

输出

输入

输出

输入

输出

输入

方向

输出

输入

输出

输入

输出

方向

输出

输入

输出

输入

输入

最大信息包规

格(字节)

16

16

16

16

644

644

最大信息包规

格(字节)

16

16

16

16

1284

最大信息包规

格(字节)

16

16

16

16

1284

�

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 http://www.zlgmcu.com

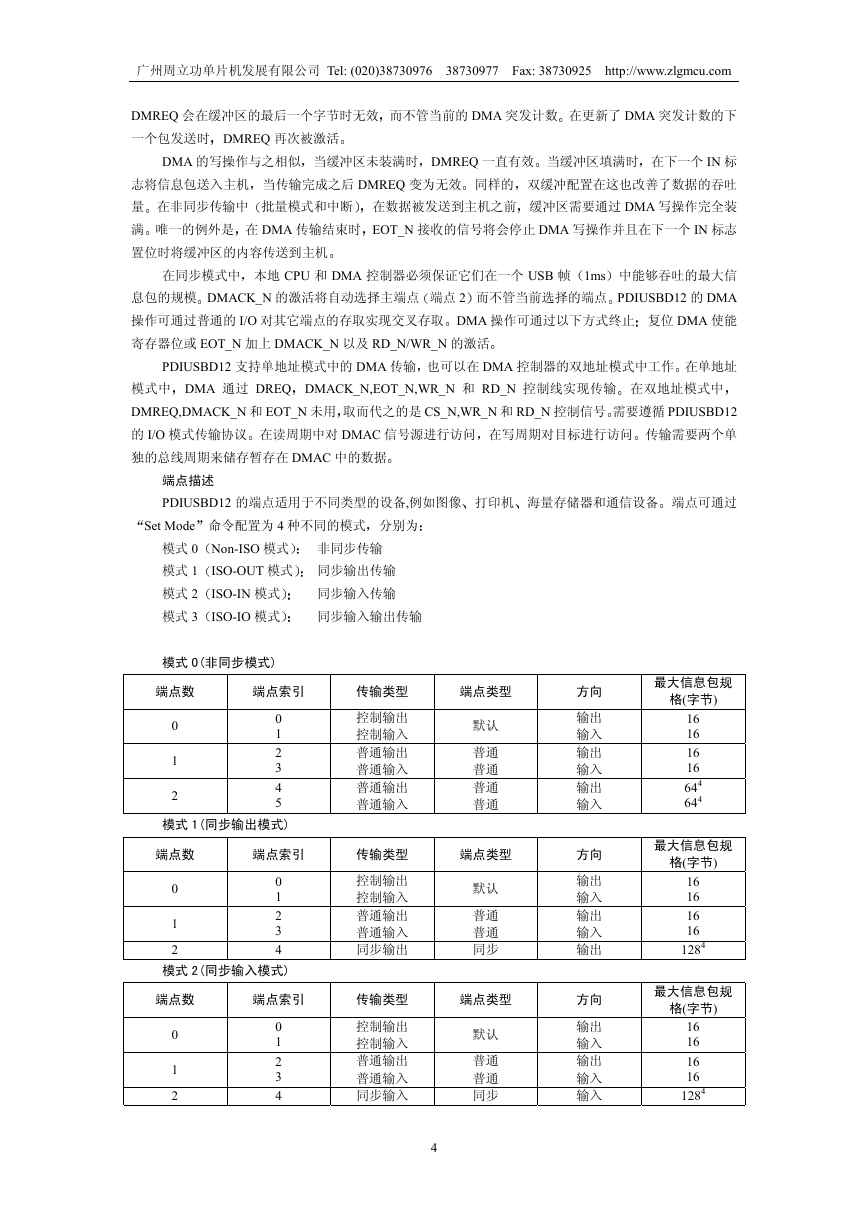

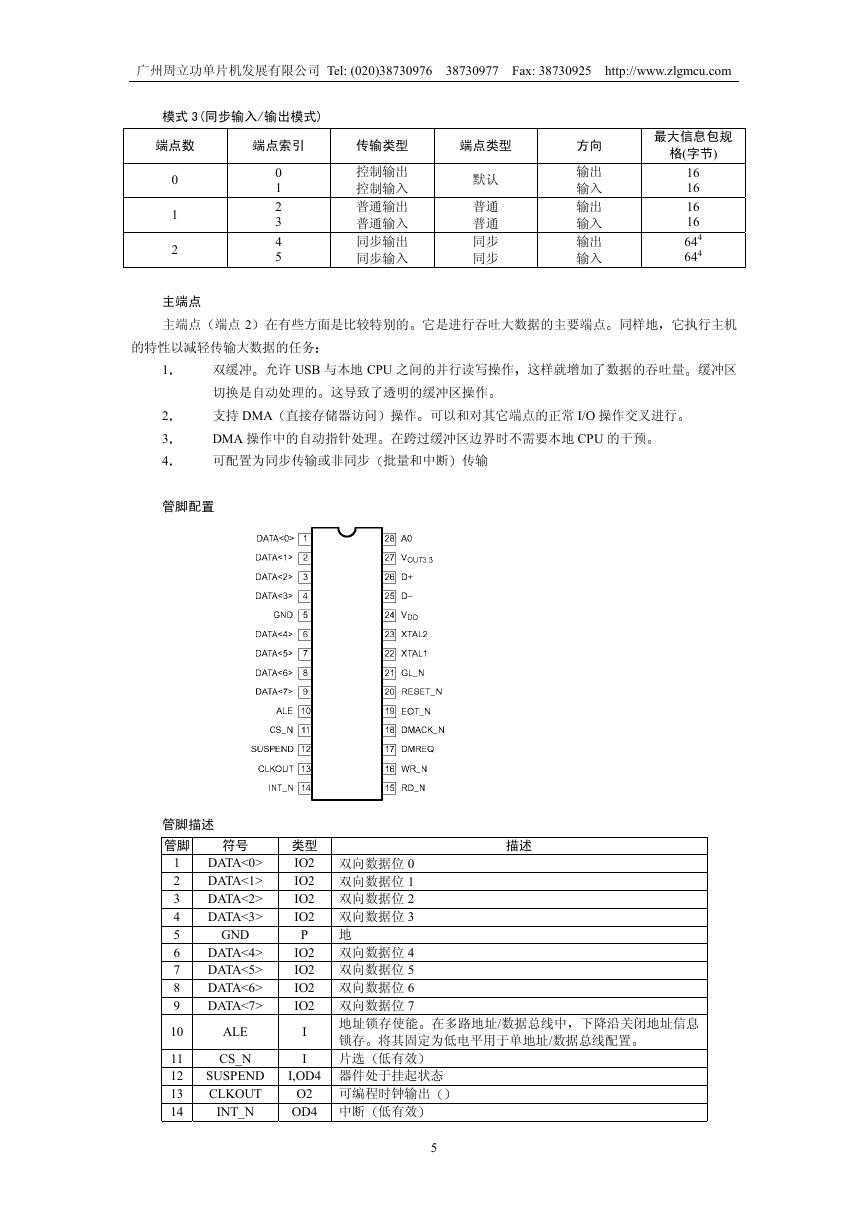

模式 3(同步输入/输出模式)

端点数

端点索引

0

1

2

0

1

2

3

4

5

传输类型

控制输出

控制输入

普通输出

普通输入

同步输出

同步输入

端点类型

默认

普通

普通

同步

同步

方向

输出

输入

输出

输入

输出

输入

最大信息包规

格(字节)

16

16

16

16

644

644

主端点

主端点 端点 2 在有些方面是比较特别的 它是进行吞吐大数据的主要端点 同样地 它执行主机

的特性以减轻传输大数据的任务

双缓冲 允许 USB 与本地 CPU 之间的并行读写操作 这样就增加了数据的吞吐量 缓冲区

切换是自动处理的 这导致了透明的缓冲区操作

支持 DMA 直接存储器访问 操作 可以和对其它端点的正常 I/O 操作交叉进行

DMA 操作中的自动指针处理 在跨过缓冲区边界时不需要本地 CPU 的干预

可配置为同步传输或非同步 批量和中断 传输

地址锁存使能 在多路地址/数据总线中 下降沿关闭地址信息

锁存 将其固定为低电平用于单地址/数据总线配置

片选 低有效

I

SUSPEND

CLKOUT

INT_N

I,OD4 器件处于挂起状态

O2 可编程时钟输出

OD4 中断 低有效

5

1

2

3

4

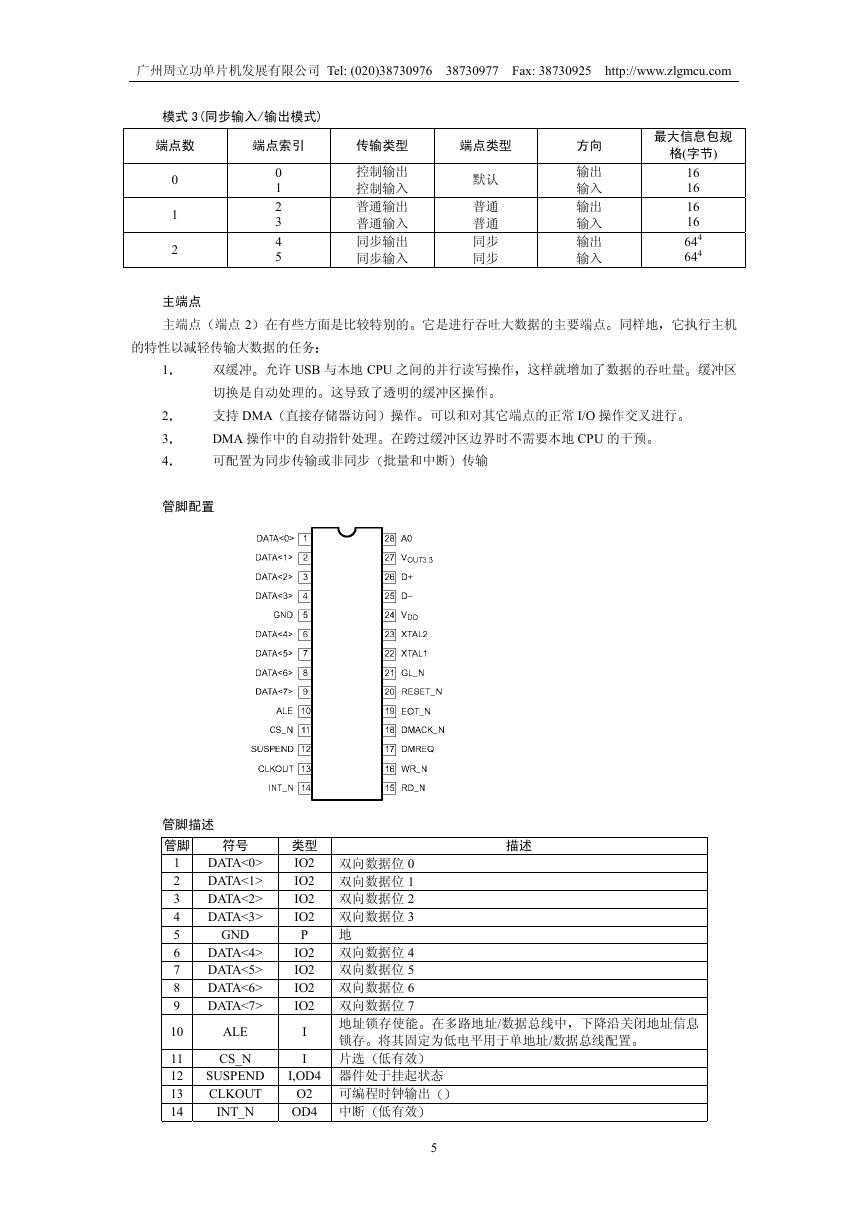

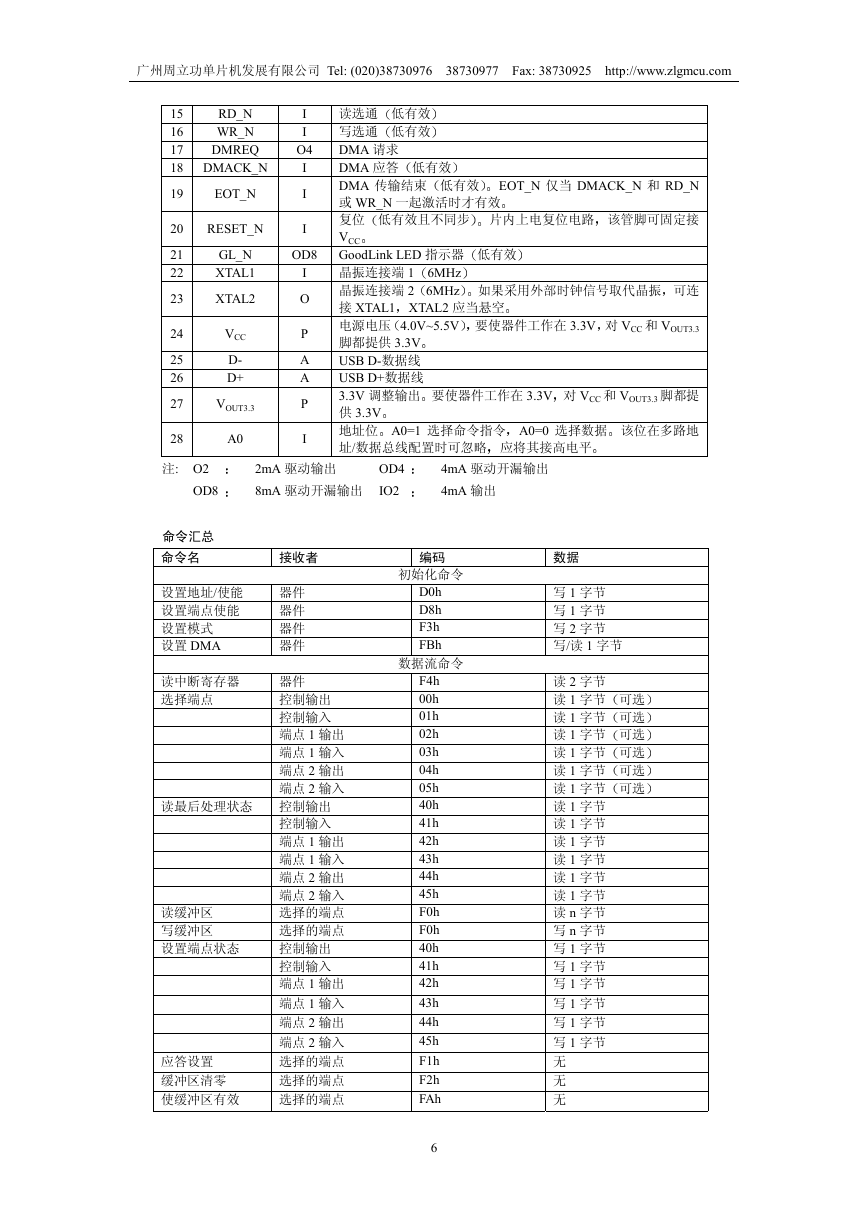

管脚配置

管脚描述

管脚

1

2

3

4

5

6

7

8

9

10

11

12

13

14

描述

符号

DATA<0>

DATA<1>

DATA<2>

DATA<3>

GND

DATA<4>

DATA<5>

DATA<6>

DATA<7>

ALE

CS_N

类型

IO2 双向数据位 0

IO2 双向数据位 1

IO2 双向数据位 2

IO2 双向数据位 3

P

IO2 双向数据位 4

IO2 双向数据位 5

IO2 双向数据位 6

IO2 双向数据位 7

I

地

�

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 http://www.zlgmcu.com

RD_N

WR_N

DMREQ

15

16

17

18 DMACK_N

19

20

21

22

23

24

25

26

27

28

EOT_N

RESET_N

GL_N

XTAL1

XTAL2

VCC

D-

D+

VOUT3.3

A0

I

I

O4

I

I

I

读选通 低有效

写选通 低有效

DMA 请求

DMA 应答 低有效

DMA 传输结束 低有效 EOT_N 仅当 DMACK_N 和 RD_N

或 WR_N 一起激活时才有效

复位 低有效且不同步 片内上电复位电路 该管脚可固定接

VCC

OD8 GoodLink LED 指示器 低有效

P

6MHz

晶振连接端 1

I

O 晶振连接端 2 6MHz 如果采用外部时钟信号取代晶振 可连

接 XTAL1 XTAL2 应当悬空

电源电压 4.0V~5.5V 要使器件工作在 3.3V 对 VCC 和 VOUT3.3

脚都提供 3.3V

USB D-数据线

USB D+数据线

3.3V 调整输出 要使器件工作在 3.3V 对 VCC 和 VOUT3.3 脚都提

供 3.3V

地址位 A0=1 选择命令指令 A0=0 选择数据 该位在多路地

址/数据总线配置时可忽略 应将其接高电平

A

A

P

I

OD8

注: O2

命令汇总

命令名

2mA 驱动输出

8mA 驱动开漏输出

OD4

IO2

4mA 驱动开漏输出

4mA 输出

接收者

编码

数据

设置地址/使能

设置端点使能

设置模式

设置 DMA

器件

器件

器件

器件

器件

控制输出

控制输入

端点 1 输出

端点 1 输入

端点 2 输出

端点 2 输入

读中断寄存器

选择端点

读最后处理状态 控制输出

控制输入

端点 1 输出

端点 1 输入

端点 2 输出

端点 2 输入

读缓冲区

选择的端点

选择的端点

写缓冲区

控制输出

设置端点状态

控制输入

端点 1 输出

端点 1 输入

端点 2 输出

端点 2 输入

应答设置

选择的端点

选择的端点

缓冲区清零

使缓冲区有效

选择的端点

初始化命令

D0h

D8h

F3h

FBh

数据流命令

F4h

00h

01h

02h

03h

04h

05h

40h

41h

42h

43h

44h

45h

F0h

F0h

40h

41h

42h

43h

44h

45h

F1h

F2h

FAh

6

写 1 字节

写 1 字节

写 2 字节

写/读 1 字节

读 2 字节

读 1 字节 可选

读 1 字节 可选

读 1 字节 可选

读 1 字节 可选

读 1 字节 可选

读 1 字节 可选

读 1 字节

读 1 字节

读 1 字节

读 1 字节

读 1 字节

读 1 字节

读 n 字节

写 n 字节

写 1 字节

写 1 字节

写 1 字节

写 1 字节

写 1 字节

写 1 字节

无

无

无

�

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 http://www.zlgmcu.com

普通命令

F6h

F5h

发送恢复

读当前帧数目

命令描述

有 3 种基本的类型的命令 初始化 数据流和通用命令

初始化命令

初始化命令在 USB 网络进行枚举处理时使用 这些命令用于使能端点的功能 还可用来设置 USB 分

无

读 1 或 2 字节

配的地址

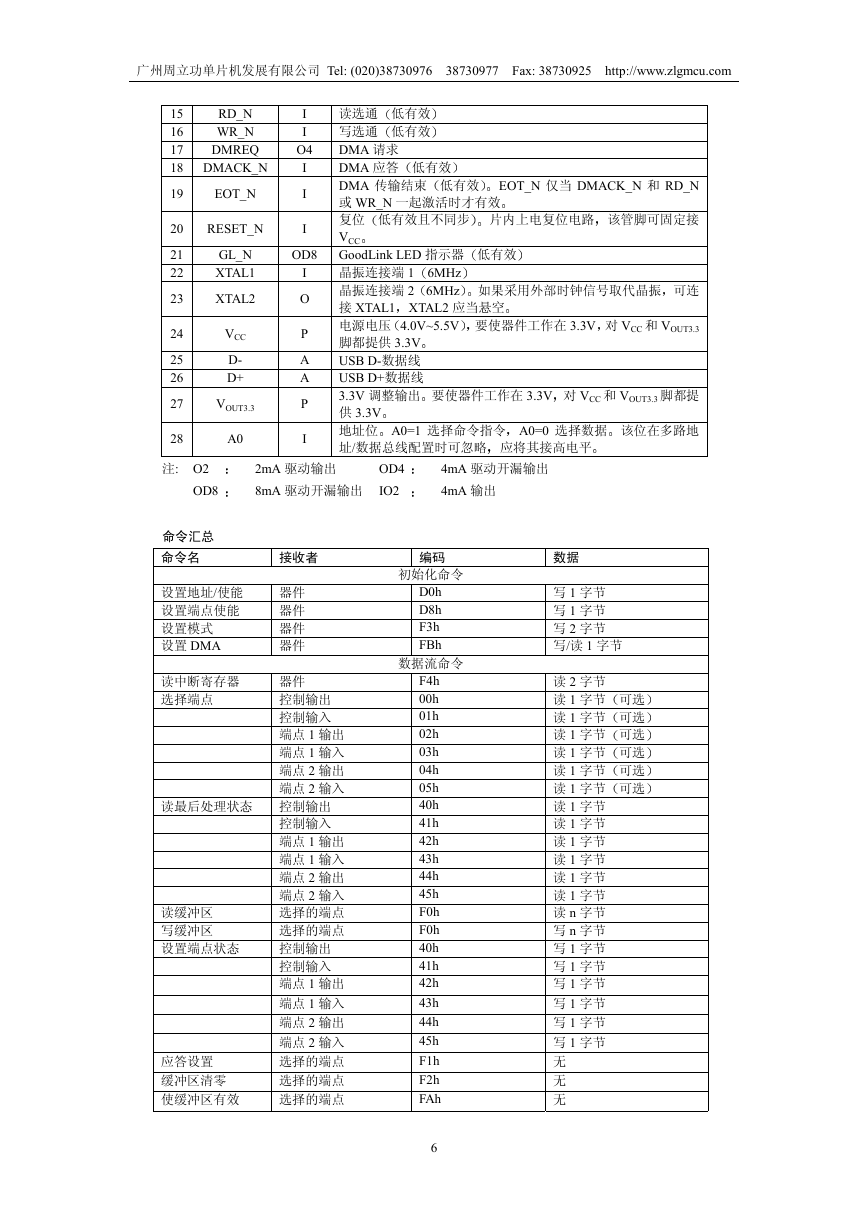

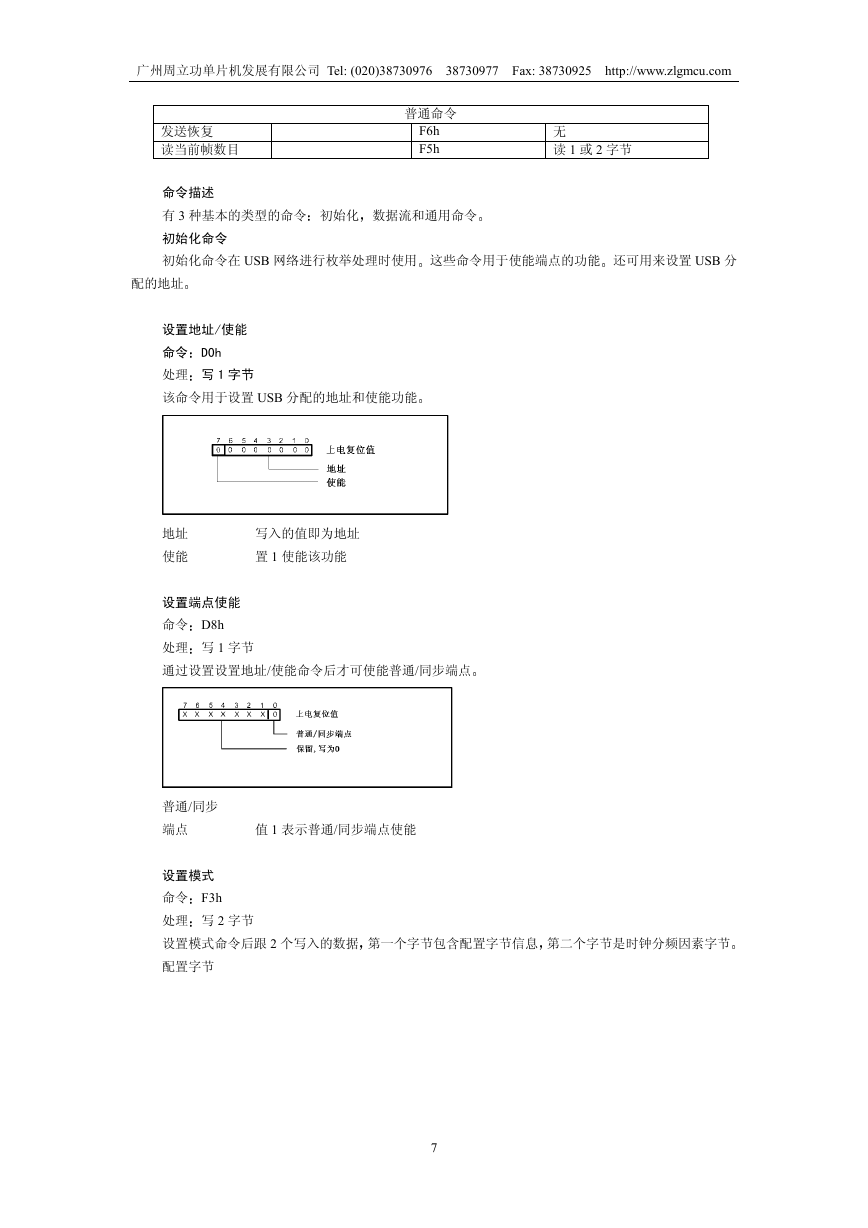

设置地址/使能

命令 D0h

写入的值即为地址

置 1 使能该功能

处理 写 1 字节

该命令用于设置 USB 分配的地址和使能功能

地址

使能

设置端点使能

命令 D8h

处理 写 1 字节

通过设置设置地址/使能命令后才可使能普通/同步端点

普通/同步

端点

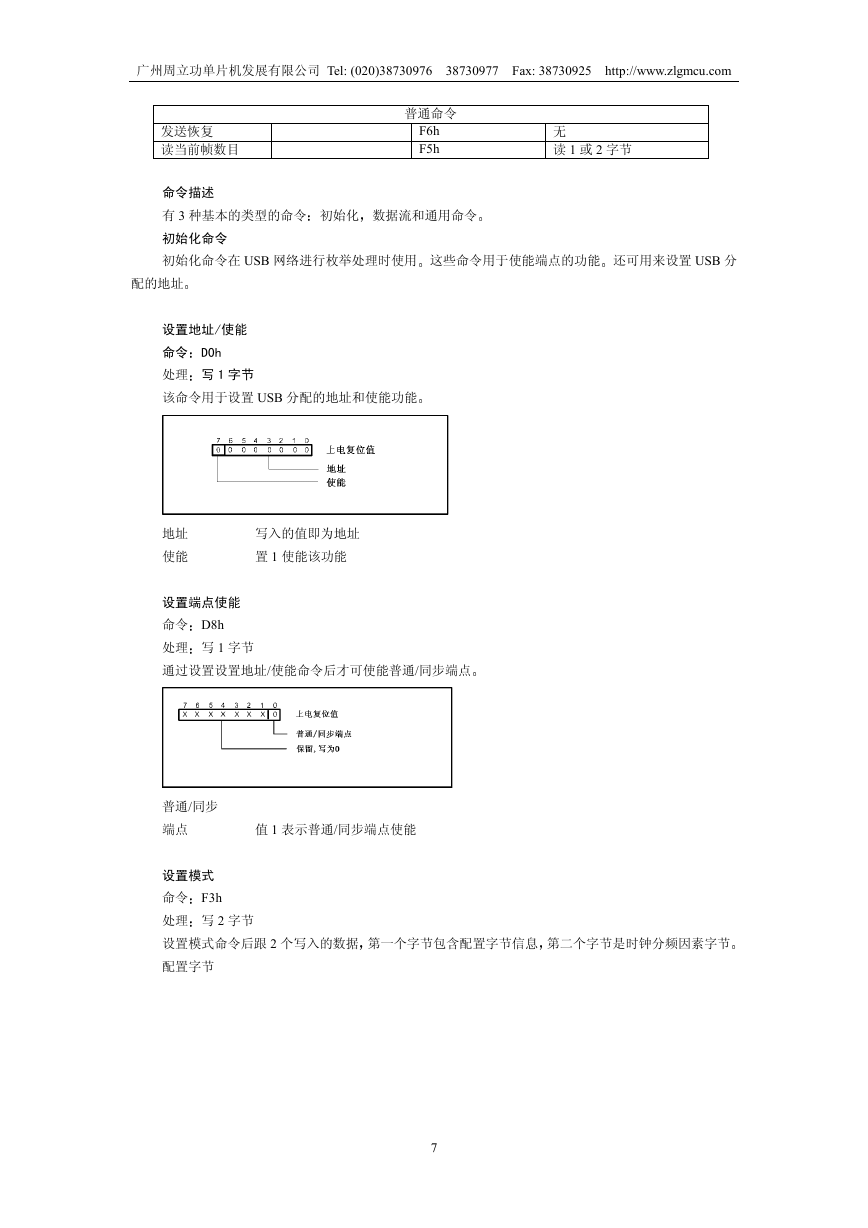

设置模式

命令 F3h

处理 写 2 字节

设置模式命令后跟 2 个写入的数据 第一个字节包含配置字节信息 第二个字节是时钟分频因素字节

配置字节

值 1 表示普通/同步端点使能

7

�

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 http://www.zlgmcu.com

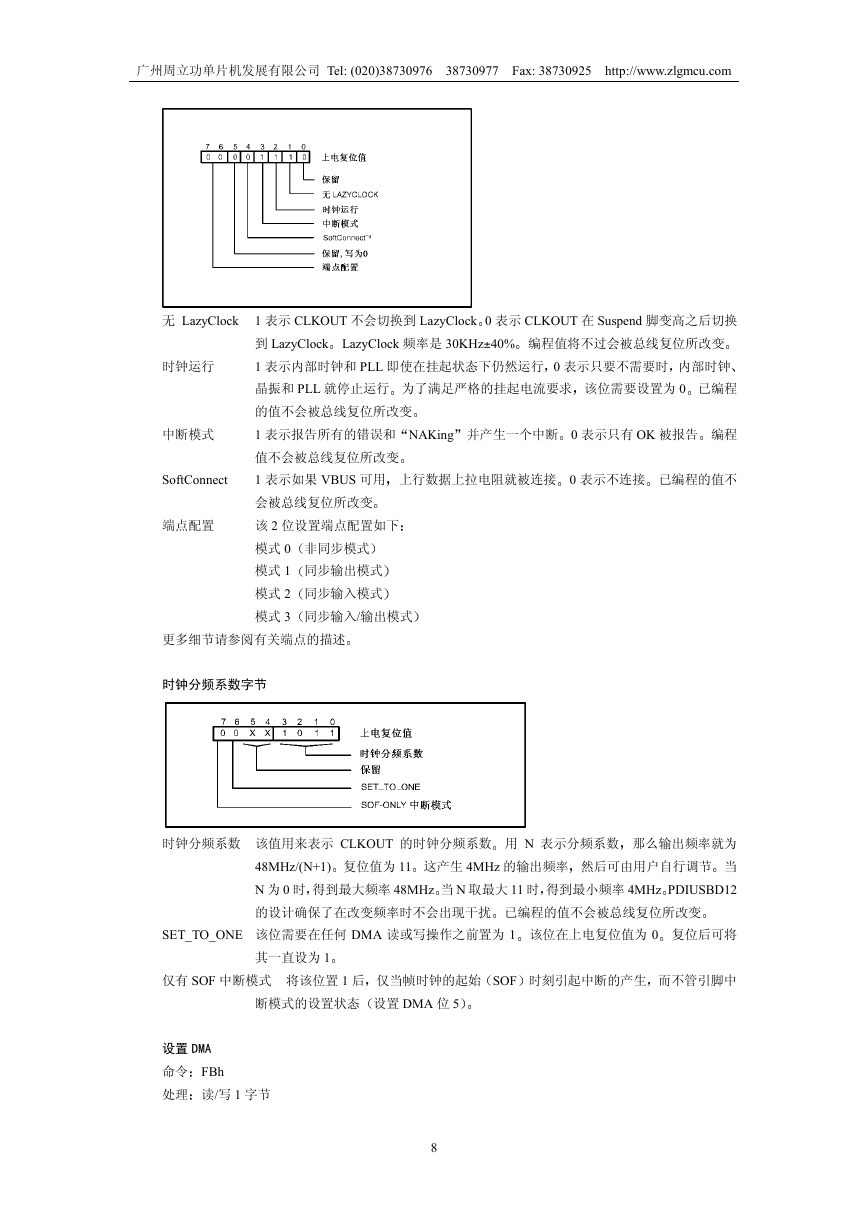

中断模式

SoftConnect

时钟运行

无 LazyClock 1 表示 CLKOUT 不会切换到 LazyClock 0 表示 CLKOUT 在 Suspend 脚变高之后切换

到 LazyClock LazyClock 频率是 30KHz±40% 编程值将不过会被总线复位所改变

1 表示内部时钟和 PLL 即使在挂起状态下仍然运行 0 表示只要不需要时 内部时钟

晶振和 PLL 就停止运行 为了满足严格的挂起电流要求 该位需要设置为 0 已编程

的值不会被总线复位所改变

1 表示报告所有的错误和 NAKing 并产生一个中断 0 表示只有 OK 被报告 编程

值不会被总线复位所改变

1 表示如果 VBUS 可用 上行数据上拉电阻就被连接 0 表示不连接 已编程的值不

会被总线复位所改变

该 2 位设置端点配置如下

模式 0 非同步模式

模式 1 同步输出模式

模式 2 同步输入模式

模式 3 同步输入/输出模式

端点配置

更多细节请参阅有关端点的描述

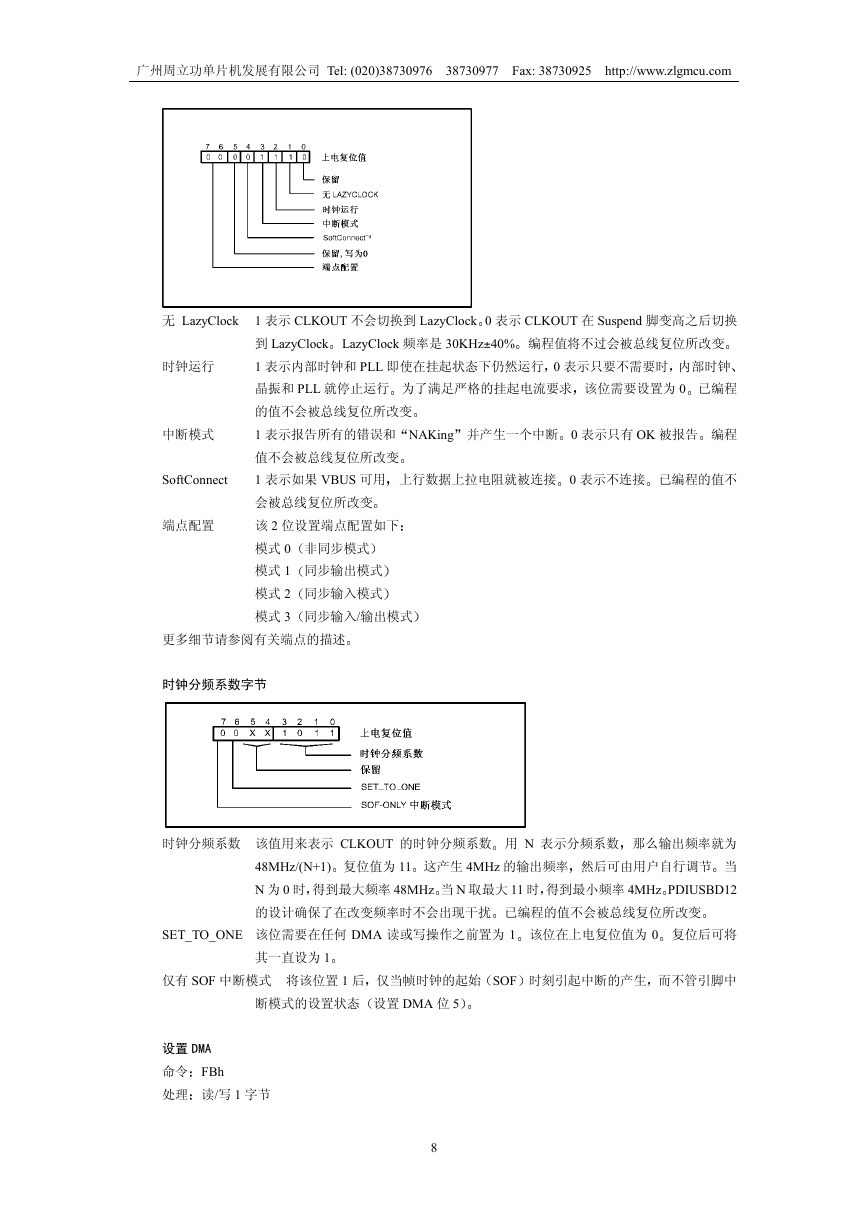

时钟分频系数字节

时钟分频系数 该值用来表示 CLKOUT 的时钟分频系数 用 N 表示分频系数 那么输出频率就为

48MHz/(N+1) 复位值为 11 这产生 4MHz 的输出频率 然后可由用户自行调节 当

N 为 0 时 得到最大频率 48MHz 当 N 取最大 11 时 得到最小频率 4MHz PDIUSBD12

的设计确保了在改变频率时不会出现干扰 已编程的值不会被总线复位所改变

SET_TO_ONE 该位需要在任何 DMA 读或写操作之前置为 1 该位在上电复位值为 0 复位后可将

其一直设为 1

仅有 SOF 中断模式 将该位置 1 后 仅当帧时钟的起始 SOF 时刻引起中断的产生 而不管引脚中

断模式的设置状态 设置 DMA 位 5

设置 DMA

命令 FBh

处理 读/写 1 字节

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc