Calibre 后仿

1. 在用户目录(/home/用户名)下的 Simulation 文件夹中,新建一个存放后仿真文件的文件夹,

如对本例的 inverter 则后仿文件夹名可取为“postinv”。

2. 新建一个 inverter 的 schematic cellview,如取为 inverter_simu,并画好 inverter 的电路图

和进行相应的电路仿真。仿真完成后,则会在 simulation 文件夹中生成一个相应的存放仿真

结果的文件夹,且其文件夹名与 schematic cellview name 完全一样。该文件夹中保存了仿真

生成的电路网表(在文件夹“…/simulation/inverter_simu/spectre/schematic/netlist”中)和仿真

分析结果(在文件夹“…/simulation/inverter_simu/spectre/schematic/psf”中,里面存入了 dc、

ac 和 tran 分析的所有静态工作点、所有节点电压和电流等信息)。

将文件夹“…/simulation/inverter_simu/spectre/schematic/netlist”中的网表文件“input.scs”

( 该 文 件 为 spectre 仿 真时 所 运 行 的网 表 文 件 ,相 当 Hspice 的 “.sp ”文 件) 和 文件 夹

“…/simulation/inverter_simu/spectre/schematic/psf”中“runObjFile”文件(该文件为查看仿真

分析结果文件“dc-dc”、“ac-ac”和“tran-tran”中的节点电压电流等信息时的控制文件,里

面包含了节点控制信息)复制到后仿文件夹“postinv”中。

注意:这里的 schematic cellview(如取名为 inverter_simu_1)最好是先建成 symbol,然后

再新建一个仿真用的 schematic cellview(如取名为 inverter_simu_2)。在 schematic cellview

(inverter_simu_2) 中 调 用 inverter_simu_1 的 symbol 来 构 造 电 路 图 进 行 仿 真 , 用 对

inverter_simu_2 进行电路仿真的过程中所生成的电路网表文件“input.scs”进行后仿真。不

要直接对 inverter_simu_1 进行电路仿真和不要直接用 inverter_simu_1 仿真生成的“input.scs”

进行后仿真,尤其是对于较大的电路( 如有十几个或几十个晶体管的电路) 。因为直接用

inverter_simu_1 仿真生成的“input.scs”进行后仿真时,schematci 网表和 PEX 提取的版图网

表的节点很难保持一致,具体的原因将会在后面的后仿过程中详细介绍。

3. 运行 Caliber->Run PEX,提取包含寄生参数的版图网表

(1) 新建一个 PEX 用的 inverter 的 layout 和 schematic cellview,并按 Calibre LVS 过程中画电

路图和版图的方法,画好相应的 inverter 的版图和电路图。

(2) 运行Calibre->Run PEX,即弹出Calibre Interactive-PEX 对话框,其中的Rules 栏目和Inputs

栏目与 Calibre LVS 的填写完全一样(注意:运行 PEX 的控制文件完全与 LVS 的控制文件完

全一样,也是“chrt035ee_lvs.ctl”文件,不要选择其它的文件,如“.cal”和“.pex”等文件)。

左击 Outputs 按钮,在 Outputs 对话框中的 Extraction Type 栏目中选择上“Transistor level”

和“Lumped C + coupling caps”(因为 EEPROM 是数字工艺,寄生电容对数字电路功能影响

不大,因而主要考虑的是寄生电容的影响,故规则文件中只规定了寄生电容的提取规则,不

能提取寄生电阻)。

填写好各栏目后,左击“Run PEX”运行 PEX。

1

�

(3) PEX 运行成功后,即弹出一个提取出来的网表文件对话框。将这个 PEX 提取出来的版图

网表文件保存到新建的用于后仿的文件夹“postinv”中,并对其命名,如取为“netlistinv”。

打开 PEX 提取出来的网表“netlistinv”,若该网表用 INCLUDE 命令包含了其它的文件,

则应将这些文件也复制到后仿文件夹“postinv”中(注意:这些文件都保存在 PEX 输出文件

夹中,如“ee035_lvsout”)。对 PEX 提取出来的网表“netlistinv”,还可注意到:PEX 提取

出来的电路网表均是以子电路的形式的来描述的。这一点也是先将 schematic cellview

(inverter_simu_1)建成 symbol,然后再新建一个仿真用的 schematic cellview(inverter_simu_2)

调用已建好的 symbol 进行电路仿真的理由。

4. 对 schematic 进行电路仿真所生成的电路网表“input.scs”和 PEX 提取出来的版图网表

“netlistinv”,将“input.scs”的电路描述部分用 PEX 提取出来的版图网表“netlistinv”中相

应的电路描述部分替换。在网表替换过程中,应注意如下事项:

(1) 若 PEX 提取出来的版图网表“netlistinv”中包含其它文件,即该网表用 INCLUDE 命令

包含了其它的文件,则应在 PEX 输出文件夹 (如“ee035_lvsout”) 中将这些相应的文件也

复制到后仿文件夹“postinv”中。

(2) 替换后的电路网表中的节点和端口名及顺序要完全一致,且节点和端口顺序要以对

schematic 进行电路仿真所生成的电路网表“input.scs”为准。

(3) 要特别注意的地方是:

(a) PEX 提取出来的版图网表“netlistinv”是以 spice 语法来描述的。并且,若版图中的端口

名的第一个字母若采用了数字,如“0”等,或在端口名的后面加了“!”号,如“vdd!”及

“gnd!”,则提取出来的网表中的端口名会与所标的端口名不一样,所有的端口名前均被添

加了“nonref_”。故一定要用全英文字符串来标注版图中的端口名。

(b) 用 spice 语法描述的电路在进行电路仿真时是不区分大小写的,即节点名“IN”与“in”

是完全一样的。而用 spectre 语法描述的电路在进行电路仿真时则是区分大小写的,即节点

名分别为“IN”与“in”的两个节点是完全不相同的。这一点在进行电路仿真时要特别注意。

(c) 若对 schematic 中的端口是采用全数字来进行标注或端口名的第一个字母是数字,如“0”

或以“0”开头,则在电路仿真生成的网表“input.scs”中,对该端口名前会自动添加上“_net0”,

从而使 schematic 中的端口名与网表中的节点名不一致。所以尽量要用用全英文字符串来标

注 schematic 中的端口名。

(d) 对 schematic 中未指定端口名的节点,spectre 在电路仿真生成电路网表时是自动给这些

未指定端口名的节点命名的,一般以“_net”开头,后面接编号。为保证 PEX 提取出的版

图网表和 spectre 提取出的电路网表尽量一致,应对 schematic 作如下处理:凡是版图中标有

端口名的地方,在 schematic 中的相应地方也要采用 pin 标注上一样的端口名。(由于电源

电压节点“vdd!”和地节点“0”比较特殊,这里可暂时不考虑 schematic 中电源电压节点和

地节点的端口标注,后面将会介绍这两个端口的处理方法。)

(4) 网表的替换可采取如下两种方法:

一是:不改动 PEX 提取出来的版图网表“netlistinv”中的节点和端口名及顺序,而是

2

�

改动 schematic 电路仿真生成的电路网表“input.scs”中的节点和端口名及顺序,使之与前者

完全一致。

二是:不改动 schematic 电路仿真生成的电路网表“input.scs”中的节点和端口名及顺

序,而是改动 PEX 提取出来的版图网表“netlistinv”中的节点和端口名及顺序,使之与前

者完全一致。这种方法对小电路还可行;但对大的电路则不可行,因为大的电路中的需改动

的地方很多。

因而,一般是采用第一种方法来替换“input.scs”中的电路网表。

(5) 在用 PEX 提取出来的版图网表“netlistinv”替换 schematic 电路仿真生成的电路网表

“input.scs”中的相应电路描述部分时也有两种方法:

一是:打开 PEX 提取出来的版图网表“netlistinv”和 schematic 电路仿真生成的电路网

表“input.scs”,将 PEX 提取出来的版图网表“netlistinv”中的内容复制到“input.scs”中,

并替换掉“input.scs”相应的电路描述部分。然后修改“input.scs”文件中的所有节点和端

口名及顺序,使两者完全一致。

二是:直接删除 schematic 电路仿真生成的电路网表“input.scs”中与 PEX 提取出来的

版图网表“netlistinv”相应的电路描述部分,然后用“INCLUDE netlistinv” 命令代替该

电路描述部分,即直接将 PEX 提取出来的版图网表“netlistinv”包含到“input.scs”中。然

后修改“input.scs”文件中的所有节点和端口名及顺序,使两者完全一致。

(6) 修改 PEX 提取出来的版图网表“netlistinv”中的所有元件的模型名,使之与 model 文件

中定义的元件的模型名完全一致。

(7) 在修改后的电路网表“input”文件中加入如下语句:

在“input”文件中被替换的电路描述部分之前加入命令:

simulator lang=spice (意思是该命令之后的电路网表是以 spice 语法来描述的)

在“input”文件中被替换的电路描述部分之后加入命令:

simulator lang=spectre (意思是该命令之后的电路网表是以 spectre 语法来描述的)

(8) 在用 spectre 进行电路仿真时,应特别注意以下事项:

spectre 在进行电路仿真时,默认的电源电压节点只有“vdd!”,默认的地节点只有“0”;

并且“vdd!”和“0”均被定义成了全局变量(global 0 vdd!)。

故在对 spectre 网表“input.scs”进行电路仿真之前,应先确保 PEX 提取出来的版图网

表“netlistinv”中的电源电压节点 VDD 和地节点 GND(spice 语法描述的)和 spectre 所定义

的电源节点“vdd!”和地节点“0”是连接在一起的。修改的方法有如下两种:

(a) 由 4(3)(a)可知:版图中的电源电压端口和地端口应采用大写或小写的“vdd”和“gnd”

来进行标注,故 PEX 所提取的版图网表中电源电压节点和地节点分别为“VDD”和“GND”。

因而只需将 PEX 所提取的版图网表中的所有电源电压节点“VDD”和地节点“GND” 分

别替换为 spectre 语法所下定义的电源电压节点“vdd!”和地节点“0”即可。

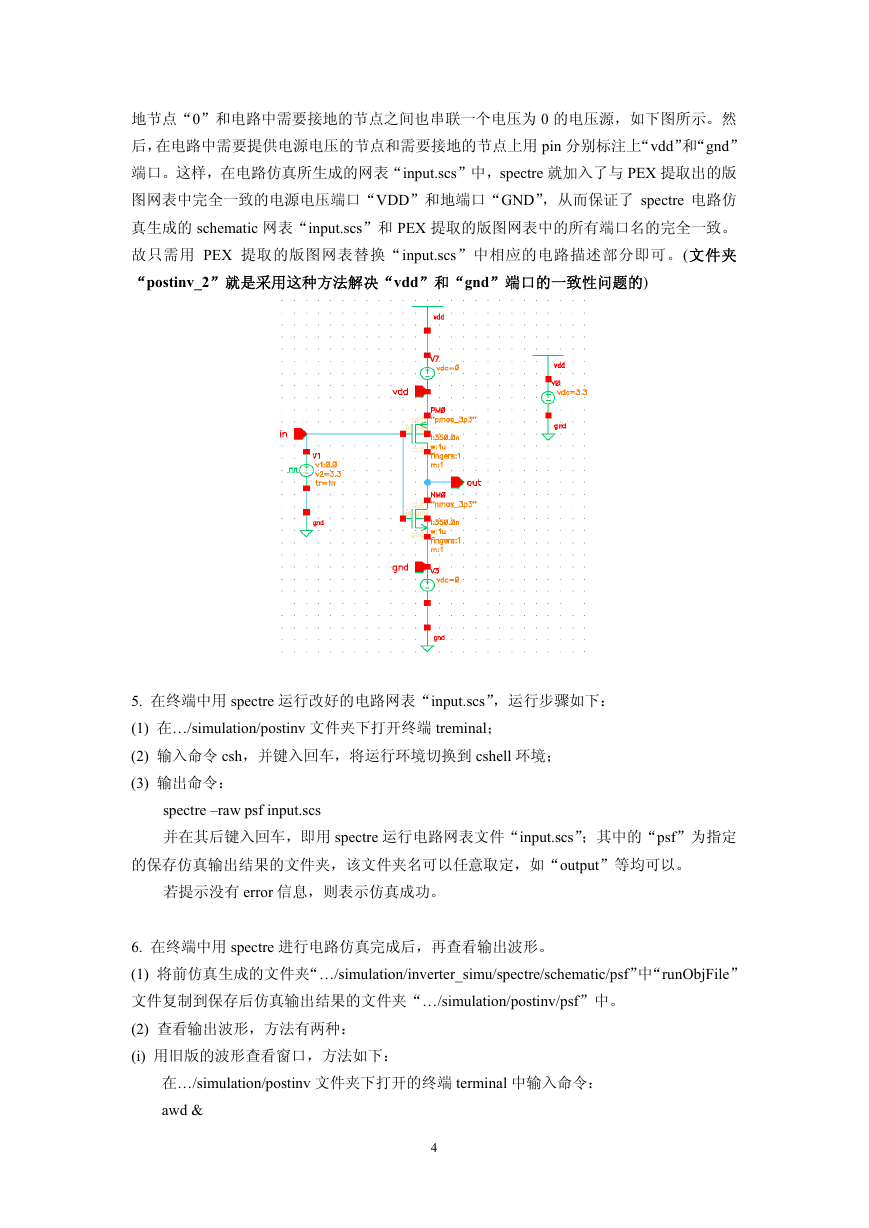

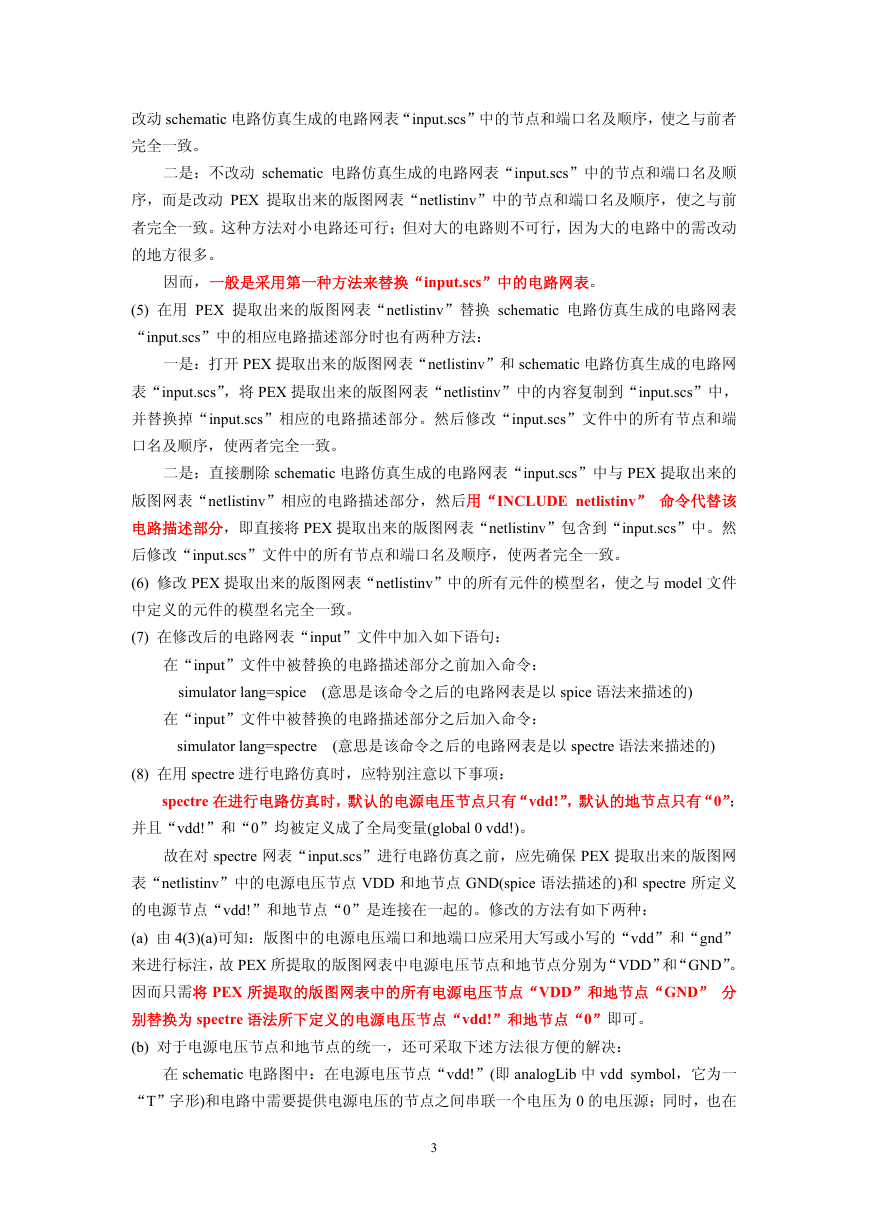

(b) 对于电源电压节点和地节点的统一,还可采取下述方法很方便的解决:

在 schematic 电路图中:在电源电压节点“vdd!”(即 analogLib 中 vdd symbol,它为一

“T”字形)和电路中需要提供电源电压的节点之间串联一个电压为 0 的电压源;同时,也在

3

�

地节点“0”和电路中需要接地的节点之间也串联一个电压为 0 的电压源,如下图所示。然

后,在电路中需要提供电源电压的节点和需要接地的节点上用 pin 分别标注上“vdd”和“gnd”

端口。这样,在电路仿真所生成的网表“input.scs”中,spectre 就加入了与 PEX 提取出的版

图网表中完全一致的电源电压端口“VDD”和地端口“GND”,从而保证了 spectre 电路仿

真生成的 schematic 网表“input.scs”和 PEX 提取的版图网表中的所有端口名的完全一致。

故只需用 PEX 提取的版图网表替换“input.scs ”中相应的电路描述部分即可。(文件夹

“postinv_2”就是采用这种方法解决“vdd”和“gnd”端口的一致性问题的)

5. 在终端中用 spectre 运行改好的电路网表“input.scs”,运行步骤如下:

(1) 在…/simulation/postinv 文件夹下打开终端 treminal;

(2) 输入命令 csh,并键入回车,将运行环境切换到 cshell 环境;

(3) 输出命令:

spectre –raw psf input.scs

并在其后键入回车,即用 spectre 运行电路网表文件“input.scs”;其中的“psf”为指定

的保存仿真输出结果的文件夹,该文件夹名可以任意取定,如“output”等均可以。

若提示没有 error 信息,则表示仿真成功。

6. 在终端中用 spectre 进行电路仿真完成后,再查看输出波形。

(1) 将前仿真生成的文件夹“…/simulation/inverter_simu/spectre/schematic/psf”中“runObjFile”

文件复制到保存后仿真输出结果的文件夹“…/simulation/postinv/psf”中。

(2) 查看输出波形,方法有两种:

(i) 用旧版的波形查看窗口,方法如下:

在…/simulation/postinv 文件夹下打开的终端 terminal 中输入命令:

awd &

4

�

(注意:这里的“&”表示在后台运行该命令,它可所打开的终端还可输入其它命令。

如不加“&”后缀,则该终端就死掉了,不可再输入其它任何命令。)

并在其后键入回车,即弹出“Browser Project Hierarchy”对话框,在其中的“Porject

Directory”栏目中填写保存后仿真输出结果的文件夹“…/simulation/postinv/psf ”的路径

“./psf”,并键入回车,则弹出“Results Browser”窗口。左击“Results Browser”窗口下的

左侧小窗口中的 “dc-dc”或“ac-ac”或“tran-tran”,则在右侧的小窗口中显示出相应的分

析类型所对应的各个节点,然后右键双击节点名即弹出该节点的电压波形图;左键双击则可

调出 calculator。

(ii) 启动 Cadence 中的新版 Results Browser 来查看输出波形。

输入命令“icfb &”,启动 cadence。打开 tools->Analog Artist Environment->Results Browser

即可打开 Results Browser 对话框。点击上侧菜单栏中的:File->Open,找到要保存仿真输出

结果的文件夹“…/simulation/postinv/psf”并打开,则会在 Results Browser 下方的左侧的小

窗口中显示所保存的所有仿真结果文件,如“dc-dc”或“ac-ac”或“tran-tran”等。若左击

左侧小窗口中的 “dc-dc”或“ac-ac”或“tran-tran”,则在右侧的小窗口中显示出相应的分

析类型所对应的各个节点。然后右击节点名,则显示出一个下拉列表,根据需要选择上节点

波形的输出方式(append 表示与前面的所有波形显示在同一窗口中;replace 表示替换掉波形

窗口中已显示的波形;newsubwin 表示以新的子窗口的形式显示该波形;newwin 表示以新

的窗口的形式显示该波形)。在弹出的波形窗口中,点击 tools->calculator 即可调出计算器,

通过 calculator 可对波形进行运算,也可对不不同仿真结果中的波形进行运算处理。

7. 在查看波形时,会发现一个比较严重的问题。

如果第 2 步中电路仿真所生成的网表文件“input.scs”是直接画电路图就进行电路仿真

得到的;而不是先画电路图建立 symbol,再调用 symbol 进行电路仿真得到,则仿真结果中

总不能正常显示出输出波形。

这是因为采用 Analog Artist Environment 得到的仿真结果中的节点及端口名是区分大小

写的(spectre 语法),而 PEX 提取出来的版图网表“netlistinv”中的节点及端口名是不区分大

小写的(spice 语法),且提取出的节点及端口名均以大写表示。若电路仿真所生成的网表文件

“input.scs”的节点和端口名是以小写表示的,则在第 2 步电路仿真所生成的输出仿真结果

文件夹中的“…/simulation/inverter_simu/spectre/schematic/psf”中的“runObjFile”所记录的

节点和端口名也是小写的,即使将“input.scs”中节点和端口名及顺序改为与“netlistinv”

完全一致,但是它们的大小写却无法统一,因而在输出结果中同一个节点和端口同时出现

了大写的(对应于 PEX 提取出来的版图网表“netlistinv”)和小写的(对应于第 2 步电路仿真

生成的网表文件“input.scs”),致使仿真结果不能正常保存和显示。

解决这一问题的方法有三种:

(1) 在电路仿真时,先将要进行电路仿真的 schematic cellview(如取名为 inverter_simu_1)建成

symbol,然后再建一个新的仿真用 schematic cellview(如取名为 inverter_simu_2)。在 schematic

cellview (inverter_simu_2)中调用 inverter_simu_1 的 symbol 来构造电路图并进行电路仿真,

5

�

再用对 inverter_simu_2 进行电路仿真所生成的电路网表文件“input.scs”进行后仿真。

这样,spectre 在电路仿真时所生成的网表文件“input.scs”中的主电路部分是以子电路

的形式描述的,在子电路之外的元件只有电压源和输入激励源。通过这样的子电路形式处理

后,可避免所有的节点或端口名的不一致问题,不需要在 schematic 中外加冗余的零电压源

来加入电源电压端口“vdd”和地端口“gnd”(参见 4(8)(b)),只需保证端口顺序完全一致

即可。故在后仿真时,推荐采用这种方法进行后仿。采用这种方法可实现如下效果:

(a) 由于 PEX 提取出来的电路网表均是以子电路的形式描述的,故很容易实现

“input.scs”中的描述 inverter_simu_1 的电路网表的替换。

(b) 输入激励源的非地节点也在子电路之外。由于 spectre 在提取 schematic 的电路网表

时,对子电路是两套节点处理方法,即子电路两套节点:一是主电路调用子电路时所定义的

一套子电路外部节点;二是子电路定义时所下定义的一套内部节点。

(i) 子电路外部节点。spectre 在提取 schematic 的电路网表,给主电路中的每一个节点

都定义了一个节点名,这些节点处于最上层,主电路的仿真结果都保存在这些最上层的节点

中。在主电路调用子电路时,根据子电路的端口调用顺序赋予了一套这样的处于最上层的节

点,也即外部节点。

(ii) 内部节点。内部节点是 spectre 通过 symbol 提取电路时所生成的一套节点,它是根

据建立 symbol 的 schematic cellview 的端口定义来生成的。(其实,symbol 相当于是子电路)

对于上例中的电路图单元 inverter_simu_1,由于在建立 symbol 时需先采用 pin 对

inverter_simu_1 的端口进行定义,即需定义 vdd、gnd、输入端口 in 和输出端口 out。而在建

立 symbol 时也保存了这些端口信息,故这些端口也就是 symbol(或子电路)的内部节点。或

者 说 ,spectre 在 提 取 inverter_simu_1 的 symbol 的 网 表 时 , 实 质 上 也 就 是 在 提 取

inverter_simu_1 的网表。而在提取电路网表时,若某个节点或端口已经采用 pin 进行了命名,

则所生成的电路网表的相应节点也应采用该 pin 名称,也即 pin 实际上是定义了电路网表的

节点名称。

对于采用 symbol 仿真的 inverter 例子,它的节点定义如下:

内部节点: .subckt inverter_simu_1 GND IN OUT VDD

.ends inverter_simu_1

外部节点: I0 ( 0 net3 OUT vdd!) inverter_simu_1

虽然在提取网表时,对 symbol(或子电路)赋予两套节点,即外部节点和内部节点,但在

进行电路仿真时它们只相当于一套节点,语法规定这不是重复定义,因而不会导致仿真出错。

由于第 2 步中电路仿真过程中所生成的保存输出仿真结果的记录文件“runObjFile” (保

存在第 2 步电路仿真所生成的输出仿真结果文件夹“…/simulation/inverter_simu/spectre

/schematic/psf”中)所记录的节点信息为外部节点信息,故通过 symbol(或子电路)处理后,

“runObjFile”保存的节点信息与 symbol(或子电路)的内部节点无关,从而保证了 symbol(或

子电路) 的内部节点不影响输出仿真结果的保存和输出仿真结果的正常显示。( 文件夹

“postsimu_inv”则是采用调用 symbol 建立 schematic cellview 的方法进行后仿真的结果)

6

�

如果是直接对 inverter_simu_1 进行电路仿真,则 PEX 提取出来的版图网表“netlistinv”

不能以子电路形式嵌入到“input.scs”中。此时,输入激励源的非地节点和输出节点可能会

由于大小写的缘故不能正常保存仿真数据结果。若第 2 步中电路仿真所生成的网表文件

“input.scs”的 inverter 的输入和输出节点分别为小写的 in 和 out,而 PEX 提取出来的版图

网表“netlistinv”的输入和输出节点则分别为大写的 IN 和 OUT。由于第 2 步中电路仿真所

生成的输出仿真结果记录文件“runObjFile”保存的节点名是小写的,而替换后的“input.scs”

网表文件中的输入和输出节点又以大写形式表示,则保存输出结果信息时就会出现混乱,从

而不能正常显示节点波形。

注意:采用这种方法在替换网表时,可用 INCLUDE 命令直接替换,不必复制。但需

修改 PEX 提取的版图网表中所定义的子电路的名称和端口顺序,使之与主电路调用时的名

称和端口顺序完全一致。(文件夹“postinv_0”就是采用这种方法进行后仿真的)

(2) 直接对 inverter_simu_1 进行电路仿真,在修改网表“input.scs”时作如下处理:

(a) 用 PEX 提取出来的版图网表“netlistinv”的内容替换掉到对 inverter_simu_1 进行电路仿

真所生成的网表“input.scs”中相应的电路描述部分(注意:“netlistinv”用 INCLUDE 命令包

含的文件也需要复制到后仿文件夹中)

(b) 将“netlistinv”的所有节点和端口名及顺序改为与对 inverter_simu_1 进行电路仿真所生

成的网表“input.scs ”中的节点和端口名及顺序完全一致,并且节点和端口顺序要以对

inverter_simu_1 进行电路仿真所生成的网表“input.scs”为准。

对于小的电路,这样的操作还勉强可行,但对于较大规模的电路,这样的操作是几乎不

可行的。( 文件夹“postinv_1 ”则是采用直接对 schematic cellview 进行电路仿真生成

“input.scs”的方法进行后仿真的结果)

(3) 也是直接对 inverter_simu_1 进行电路仿真,但在仿真之前先采用 4(8)(b)所述方法对电路

图进行处理,然后再进行后仿真。这种方法也比较简单,推荐也可采用这种方法来做后仿真。

采用这种方法处理网表“input.scs”的过程如下:

(a) 先对 schematic 电路图的端口进行处理,保证 spectre 仿真生成的电路网表“input.scs”和

PEX 提取的版图网表的端口名完全一致:

在电源电压节点“vdd!”(即 analogLib 中 vdd symbol,它为一“T”字形)和电路中需要

提供电源电压的节点之间串联一个电压为 0 的电压源;同时,也在地节点“0”和电路中需

要接地的节点之间也串联一个电压为 0 的电压源,如下图所示。然后,在电路中需要提供电

源电压的节点和需要接地的节点上用 pin 分别标注上“vdd”和“gnd”端口。

在 schematic 电路图中,用 pin 标注上与 PEX 提取的版图网表完全一致的输入输出端口。

(b) 完全(a)步骤后,再调用 Analog Artist 进行电路仿真,得到 spectre 生成的电路网表

“input.scs”和“runObjFile”文件。然后,用 PEX 提取的版图网表替换“input.scs”中相应

的电路描述部分,注意要保证两者的端口顺序也完全一致,之后的后仿过程同前。

(文件夹“postinv_2”就是采用这种方法进行后仿真的)

7

�

注意事项:

1、在对 EEPROM 和 RF 工艺电路进行后仿时,注意里面的三极管的描述需要修改。

后仿真时,将版图提取出来的电路网表替换电路仿真生成的“input.scs”文件中的相应

的电路网表时,注意其中的三极管描述要进行修改。三极管的描述方式要按照电路仿真生成

的“input.scs”文件中的描述方式来进行描述说明,不能按版图提取出来的 spice 语法格式

来描述,否则仿真时不能后仿真时不能正常调用三极管的相应模型来进行仿真。

对 chartered EEPROM 和 RF 工艺,其三极管的电路描述方式好像如下:

Q1 C B E 模型名 m=2 (m 表示并联的三极管的个数,与 MOS 管的 m 意义一样)

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc