DFI

DDR PHY Interface

DFI 3.1 Specification

MARCH 21, 2014

DDR PHY Interface, Version 3.1

March 21, 2014

1 of 141

Copyright 1995-2014

Cadence Design Systems, Inc.

�

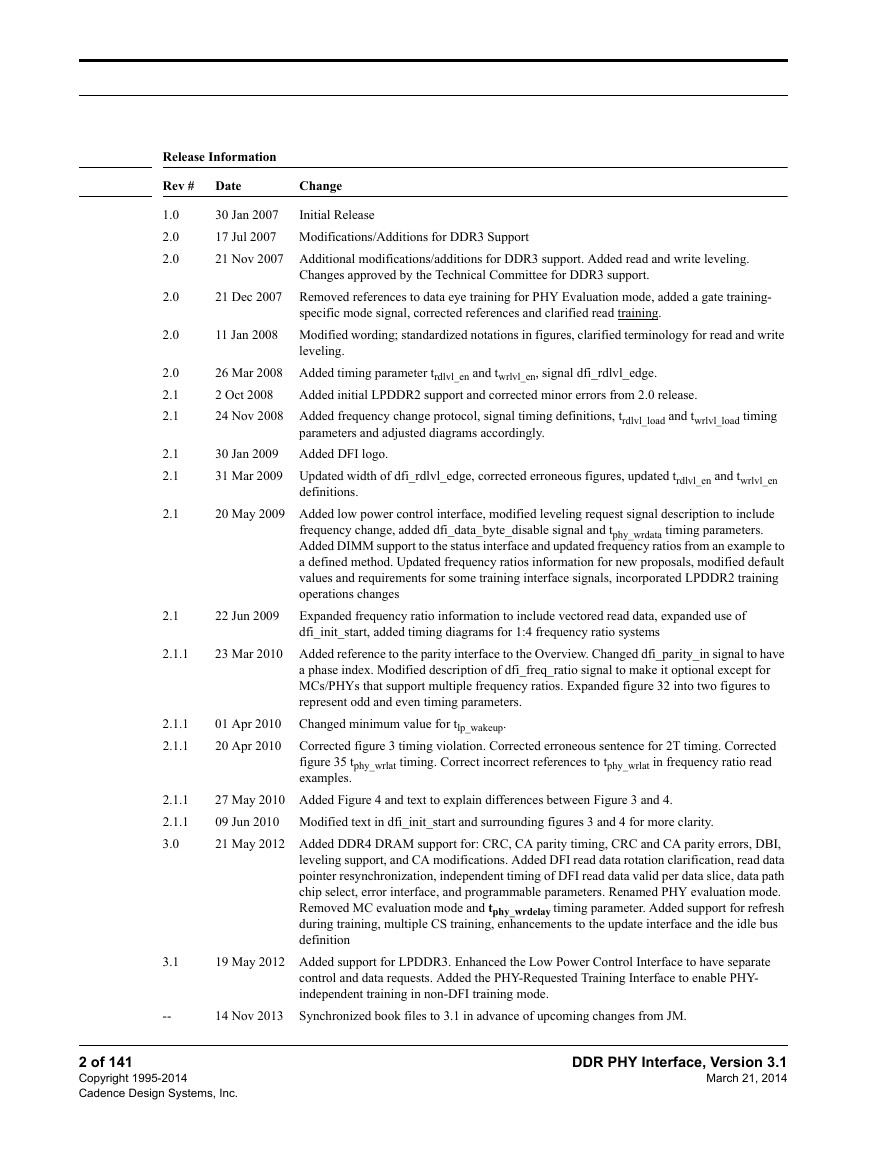

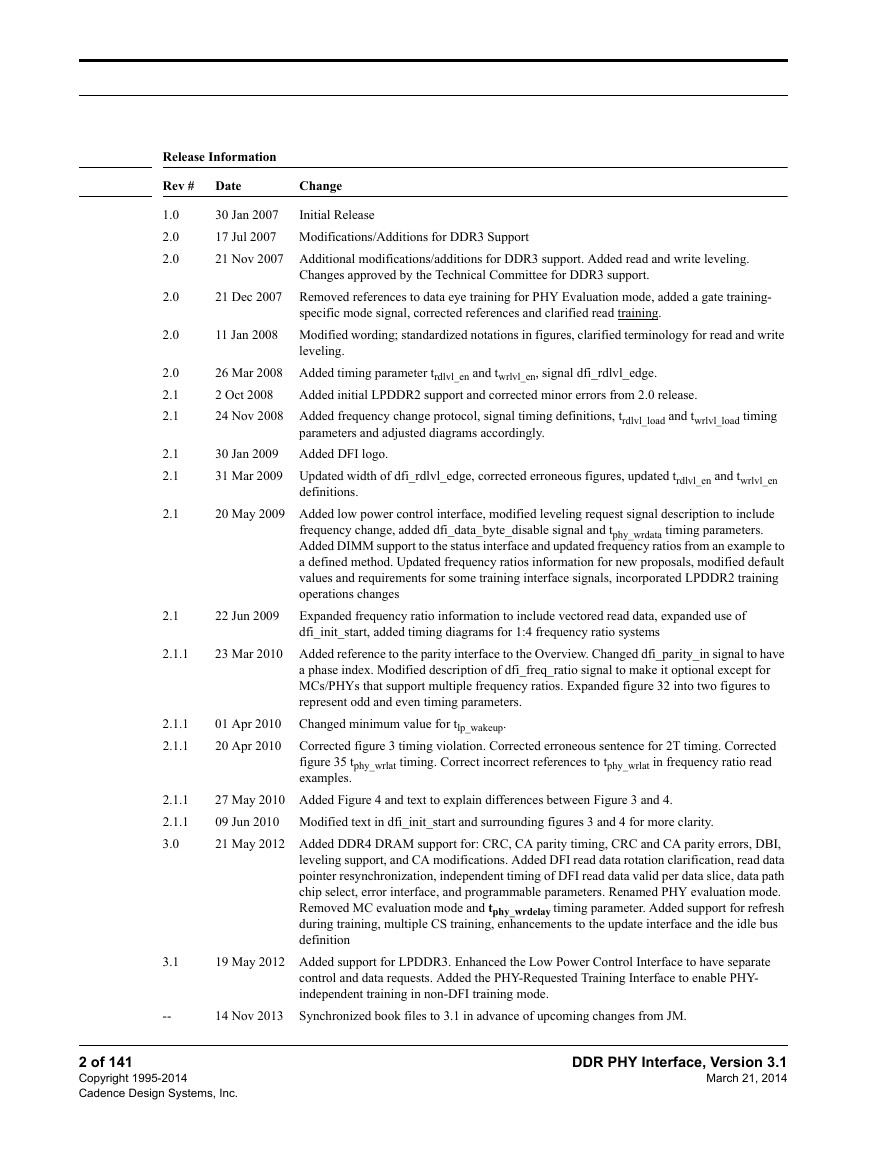

Release Information

Rev #

Date

Change

Initial Release

30 Jan 2007

17 Jul 2007 Modifications/Additions for DDR3 Support

21 Nov 2007 Additional modifications/additions for DDR3 support. Added read and write leveling.

Changes approved by the Technical Committee for DDR3 support.

21 Dec 2007 Removed references to data eye training for PHY Evaluation mode, added a gate training-

specific mode signal, corrected references and clarified read training.

11 Jan 2008 Modified wording; standardized notations in figures, clarified terminology for read and write

leveling.

26 Mar 2008 Added timing parameter trdlvl_en and twrlvl_en, signal dfi_rdlvl_edge.

2 Oct 2008

24 Nov 2008 Added frequency change protocol, signal timing definitions, trdlvl_load and twrlvl_load timing

Added initial LPDDR2 support and corrected minor errors from 2.0 release.

parameters and adjusted diagrams accordingly.

Added DFI logo.

30 Jan 2009

31 Mar 2009 Updated width of dfi_rdlvl_edge, corrected erroneous figures, updated trdlvl_en and twrlvl_en

definitions.

20 May 2009 Added low power control interface, modified leveling request signal description to include

frequency change, added dfi_data_byte_disable signal and tphy_wrdata timing parameters.

Added DIMM support to the status interface and updated frequency ratios from an example to

a defined method. Updated frequency ratios information for new proposals, modified default

values and requirements for some training interface signals, incorporated LPDDR2 training

operations changes

Expanded frequency ratio information to include vectored read data, expanded use of

dfi_init_start, added timing diagrams for 1:4 frequency ratio systems

1.0

2.0

2.0

2.0

2.0

2.0

2.1

2.1

2.1

2.1

2.1

2.1.1

2.1.1

2.1.1

2.1.1

2.1.1

3.0

3.1

--

2.1

22 Jun 2009

23 Mar 2010 Added reference to the parity interface to the Overview. Changed dfi_parity_in signal to have

01 Apr 2010

20 Apr 2010

a phase index. Modified description of dfi_freq_ratio signal to make it optional except for

MCs/PHYs that support multiple frequency ratios. Expanded figure 32 into two figures to

represent odd and even timing parameters.

Changed minimum value for tlp_wakeup.

Corrected figure 3 timing violation. Corrected erroneous sentence for 2T timing. Corrected

figure 35 tphy_wrlat timing. Correct incorrect references to tphy_wrlat in frequency ratio read

examples.

27 May 2010 Added Figure 4 and text to explain differences between Figure 3 and 4.

09 Jun 2010 Modified text in dfi_init_start and surrounding figures 3 and 4 for more clarity.

21 May 2012 Added DDR4 DRAM support for: CRC, CA parity timing, CRC and CA parity errors, DBI,

leveling support, and CA modifications. Added DFI read data rotation clarification, read data

pointer resynchronization, independent timing of DFI read data valid per data slice, data path

chip select, error interface, and programmable parameters. Renamed PHY evaluation mode.

Removed MC evaluation mode and tphy_wrdelay timing parameter. Added support for refresh

during training, multiple CS training, enhancements to the update interface and the idle bus

definition

19 May 2012 Added support for LPDDR3. Enhanced the Low Power Control Interface to have separate

control and data requests. Added the PHY-Requested Training Interface to enable PHY-

independent training in non-DFI training mode.

Synchronized book files to 3.1 in advance of upcoming changes from JM.

14 Nov 2013

2 of 141

Copyright 1995-2014

Cadence Design Systems, Inc.

DDR PHY Interface, Version 3.1

March 21, 2014

�

--

--

21 Nov 2013

21 Mar 2014

Incorporated review corrections.

Incorporated committee comments, corrected erroneous cross references, fine-tuned

formatting, fine-tuned typographical items.

Proprietary Notice

No part of this document may be copied or reproduced in any form or by any means without prior written consent of

Cadence.

Cadence makes no warranties with respect to this documentation and disclaims any implied warranties of

merchantability or fitness for a particular purpose. Information in this document is subject to change without notice.

Cadence assumes no responsibility for any errors that may appear in this document.

Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any

representations or warranties as to the completeness, accuracy, or usefulness of the information contained in this

document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does

Cadence assume any liability for damages or costs of any kind that may result from use of such information.

© Copyright 2014 Cadence Design Systems, Inc. All rights reserved worldwide. Portions of this material are © JEDEC

Solid State Technology Association. All rights reserved. Reprinted with permission.

RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraphs (c)(1)(ii) of the

Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Destination Control Statement

All technical data contained in this product is subject to the export control laws of the United States of America.

Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to

determine the applicable regulations and to comply with them.

Trademarks

Cadence and the Cadence logo are registered trademarks of Cadence Design Systems, Inc.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

End User License Agreement2

1.Subject to the provisions of Clauses 2, 3, 4, 5 and 6, Cadence hereby grants to licensee ("Licensee") a perpetual,

nonexclusive, nontransferable, royalty free, worldwide copyright license to use and copy the DFI (DDR PHY Interface)

specification (the "DFI Specification") for the purpose of developing, having developed, manufacturing, having

manufactured, offering to sell, selling, supplying or otherwise distributing products which comply with the DFI

Specification.

2.THE DFI SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES EXPRESS, IMPLIED OR

STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORY QUALITY,

MERCHANTABILITY, NONINFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE.

3.No license, express, implied or otherwise, is granted to Licensee, under the provisions of Clause 1, to use Cadence's or

any other person or entity participating in the development of the DFI Specification listed herein (individually

"Participant," collectively "Participants") trade name, or trademarks in connection with the DFI Specification or any

products based thereon. Nothing in Clause 1 shall be construed as authority for Licensee to make any representations on

behalf of Cadence or the other Participants in respect of the DFI Specification.

4.NOTWITHSTANDING ANYTHING ELSE WILL CADENCE'S TOTAL AGGREGATE LIABILITY FOR ANY

CLAIM, SUIT, PROCEEDING OR OTHERWISE, RELATING IN ANYWAY TO THE DFI SPECIFICATION

EXCEED $1.00USD.

5.NOTWITHSTANDING ANYTHING ELSE WILL ANY PARTICIPANT'S TOTAL AGGREGATE LIABILITY FOR

DDR PHY Interface, Version 3.1

March 21, 2014

3 of 141

Copyright 1995-2014

Cadence Design Systems, Inc.

�

ANY CLAIM, SUIT, PROCEEDING OR OTHERWISE, RELATING IN ANYWAY TO THE DFI SPECIFICATION

EXCEED $1.00USD.

6.Licensee agrees that Cadence and the Participants may use, copy, modify, reproduce and distribute any written

comments or suggestions ("Communications") provided regarding the DFI Specification by Licensee and that Licensee

will not claim any proprietary rights in the DFI Specification, or implementations thereof by any Participant or third

party, as a result of the use of the Communications in developing or changing the DFI Specification. Cadence and the

participants will have no confidentiality obligations with respect to the Communications and Licensee will not include

any confidential information of Licensee or any third party in any Communications.

Participants

ARM Cadence Intel LSI Samsung ST Synopsys

4 of 141

Copyright 1995-2014

Cadence Design Systems, Inc.

DDR PHY Interface, Version 3.1

March 21, 2014

�

CONTENTS

1.0 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.0 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interface Signal Groups. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.0

3.1 Control Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Write Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 . . Write Data Mask/Write DBI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 . . Write Data Chip Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.3 . . Write Data CRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.4 . . Frequency Ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.5 . . Write Data Signals and Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Read Data Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 . . Read DBI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 . . Read Data Chip Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 . . Read Data Valid . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.4 . . Frequency Ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Update Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5

Status Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 . . Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2 . . Clock Disabling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.3 . . Frequency Ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.4 . . Frequency Change . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.5 . . CRC and CA Parity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6 DFI Training Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.1 . . Read Training Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2 . . Write Leveling Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.3 . . CA Training Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.4 . . dfi_lvl_pattern Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.5 . . Periodic Training Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.6 . . PHY-Initiated Training in DFI Training Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.7 . . PHY-Requested Training in Non-DFI Training Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7 Low Power Control Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 Error Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Control Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Data Bus Inversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1 . . Write Transaction Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2 . . DBI - Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.3 . . Cyclic Redundancy Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.0

13

14

26

26

29

29

29

30

30

31

33

34

34

34

35

37

41

41

42

42

42

42

47

48

48

48

55

56

56

56

56

60

62

62

64

66

67

67

75

75

DDR PHY Interface, Version 3.1

March 21, 2014

5 of 141

Copyright 1995-2014,

Cadence Design Systems, Inc.

�

4.9

4.5 Read Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.1 . .Read Transaction Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.2 . .DBI - Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Update . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.1 . .MC-Initiated Update . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.2 . .PHY-Initiated Update. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.3 . .DFI Idle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 DFI Clock Disabling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Frequency Ratios Across the DFI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8

4.8.1 . .Frequency Ratio Clock Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8.2 . .Interface Signals with Frequency Ratio Systems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8.3 . .Write Data Interface in Frequency Ratio Systems. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8.4 . .Read Data Interface in Frequency Ratio Systems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Frequency Change . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9.1 . .Frequency Change Protocol - Acknowledged . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9.2 . .Frequency Change Protocol - Not Acknowledged . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.10 CA Parity Signaling and CA Parity, CRC Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.10.1 .CA Parity Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.10.2 .CA Parity and CRC Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11 DFI Training Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11.1 .Initiating a Training Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11.2 . Read Training . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11.3 .Write Leveling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11.4 .CA Training . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11.5 .dfi_lvl_pattern Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11.6 .Support for Non-data Commands During Training. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11.7 .PHY-Requested Training Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12 Low Power Control Handshaking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.13 Error Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.13.1 .Error Code Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signal Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.0

6.0 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

81

82

88

89

89

90

91

92

93

94

94

98

100

110

111

112

112

113

113

115

116

117

119

120

123

126

127

129

132

133

134

138

6 of 141

Copyright 1995-2014

Cadence Design Systems, Inc.

DDR PHY Interface, Version 3.1

March 21, 2014

�

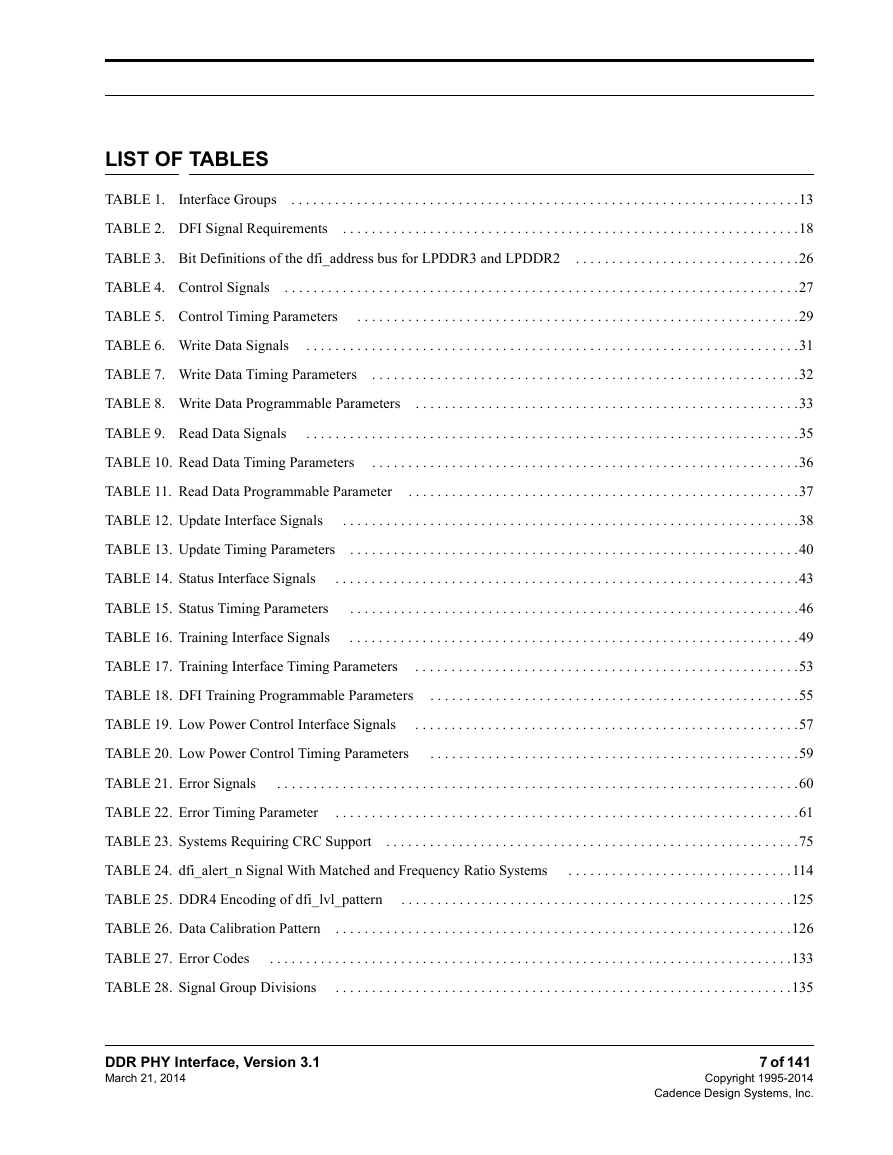

LIST OF TABLES

TABLE 1.

Interface Groups

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

TABLE 2. DFI Signal Requirements

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

TABLE 3. Bit Definitions of the dfi_address bus for LPDDR3 and LPDDR2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

TABLE 4. Control Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

TABLE 5. Control Timing Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

TABLE 6. Write Data Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

TABLE 7. Write Data Timing Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

TABLE 8. Write Data Programmable Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

TABLE 9. Read Data Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

TABLE 10. Read Data Timing Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

TABLE 11. Read Data Programmable Parameter

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

TABLE 12. Update Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

TABLE 13. Update Timing Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

TABLE 14. Status Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

TABLE 15. Status Timing Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

TABLE 16. Training Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

TABLE 17. Training Interface Timing Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

TABLE 18. DFI Training Programmable Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

TABLE 19. Low Power Control Interface Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

TABLE 20. Low Power Control Timing Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

TABLE 21. Error Signals

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

TABLE 22. Error Timing Parameter

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

TABLE 23. Systems Requiring CRC Support

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

TABLE 24. dfi_alert_n Signal With Matched and Frequency Ratio Systems

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

TABLE 25. DDR4 Encoding of dfi_lvl_pattern

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

TABLE 26. Data Calibration Pattern

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

TABLE 27. Error Codes

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

TABLE 28. Signal Group Divisions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

DDR PHY Interface, Version 3.1

March 21, 2014

7 of 141

Copyright 1995-2014

Cadence Design Systems, Inc.

�

TABLE 29. Glossary of Terms

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

8 of 141

Copyright 1995-2014

Cadence Design Systems, Inc.

DDR PHY Interface, Version 3.1

March 21, 2014

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc