2013 年第 09 期,第 46 卷 通 信 技 术 Vol.46,No.09,2013

总第 261 期 Communications Technology No.261,Totally

doi:10.3969/j.issn.1002-0802.2013.09.026

基于FPGA的语音信号采集回放存储系统的设计﹡

路 娜﹡﹡, 赵建平, 胡海凤, 张慧霞

(曲阜师范大学 物理工程学院,山东 曲阜 273165)

【摘 要】系统构建了基于FPGA的语音信号采集存储系统,详细论述了I2C总线控制器,AUD_RAM,驱动器,

WM8731 各个模块的设计方法及功能,并给出了核心代码还有其控制流程。音频编解码芯片WM8731 由于其具有高

性能、低功耗等优点,在音频产品中得到广泛用。在QuartusⅡ9.0 中完成设计,并在modelsim中完成仿真,实

验结果表明,该系统能够可靠完成对人的语音信号的采集、回放与存储,回放时在输出端会听到清晰语音。

【关键词】语音信号;现场可编程门阵列;WM8731; 2I C

【中图分类号】TN332.1 【文献标识码】A 【文章编号】1002-0802(2013)09-0089-03

Design of Speech Signal Acquisition-Playback-Storage System based on FPGA

LU Na, ZHAO Jian-ping, HU Hai-feng, ZHANG Hui-xia

(College of Physics Engineering, Qufu Normal University, Qufu Shandong 273165, China)

【Abstract】The speech signal acquisition-playback-storage system based on FPGA is constructed,

and 2I C bus controller, AUD_RAM, drive, and the designs and functions of various WM8731 modules

are described in detail, including the core code and its control process. Audio Codec WM8731,

for its high quality and low power-consumption, is widely applied in audio products. The design

in Quartus Ⅱ 9.0 is completed and the simulation in modelsim is done, and the experimental results

indicates that the system could reliably implement acquisition, playback and storage of the human

voice signal, and the playback could give clear voice at the output terminal.

【Key words】speech signal; FPGA; WM8731; 2I C

0 引言

语音识别技术始于上世纪 50 年代,现在语音识

别已经从支流技术发展成为主流技术,所以语音信号

的采集以及存储就显得尤为重要。早在 2000 年刘金

华等人提出了用单片机实现语音信号的采集与存

储[1],但是当电路有少量改动时就需要重新修改设

计,这样就有一定的局限性,文中提出了基于FPGA

技术的语音的录制,存储与回放设计方法。FPGA(现

场可编程门阵列),它是在PAL、GAL、PLD等编程器

件的基础上进一步发展的产物,是专用集成电路

(ASIC)中集中度最高的一种。其技术在现代技术领

域具有明显的领先性,使用FPGA来发展数字电路,大

大提高了系统的可靠性[2]。系统采用的是ALTERA公司

﹡收稿日期:2013-04-21;修回日期:2013-08-23。

基金项目:国家自然科学基金项目(批准号:60976015);

山东省自然科学基金项目(No.ZR2010FM023);

信息功能材料国家重点实验室开题资助。

﹡﹡通讯作者:466721533@qq.com。

的CycloneⅡ系列的EP2C35F672C6,给出了I2C总线的

模块设计,以及如何配置音频编解码芯片WM8731,并

给出了设计的核心代码。在应用中可以嵌入该IP核,

能够极大提高该系统的集成度和稳定性,同时降低产

品的开发成本,提高系统设计效率,系统在功能扩张

上具有很高的参考价值和使用价值[3]。

1 系统组成

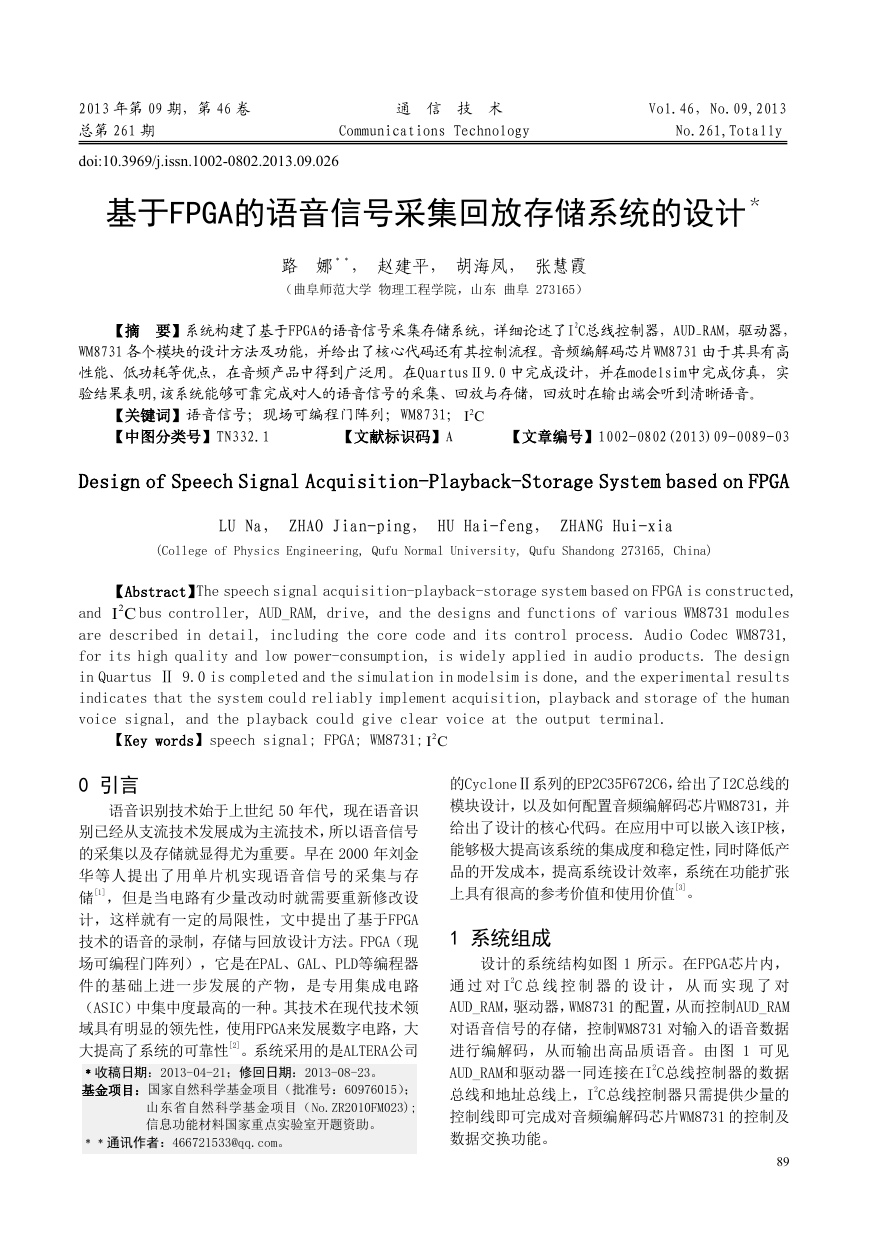

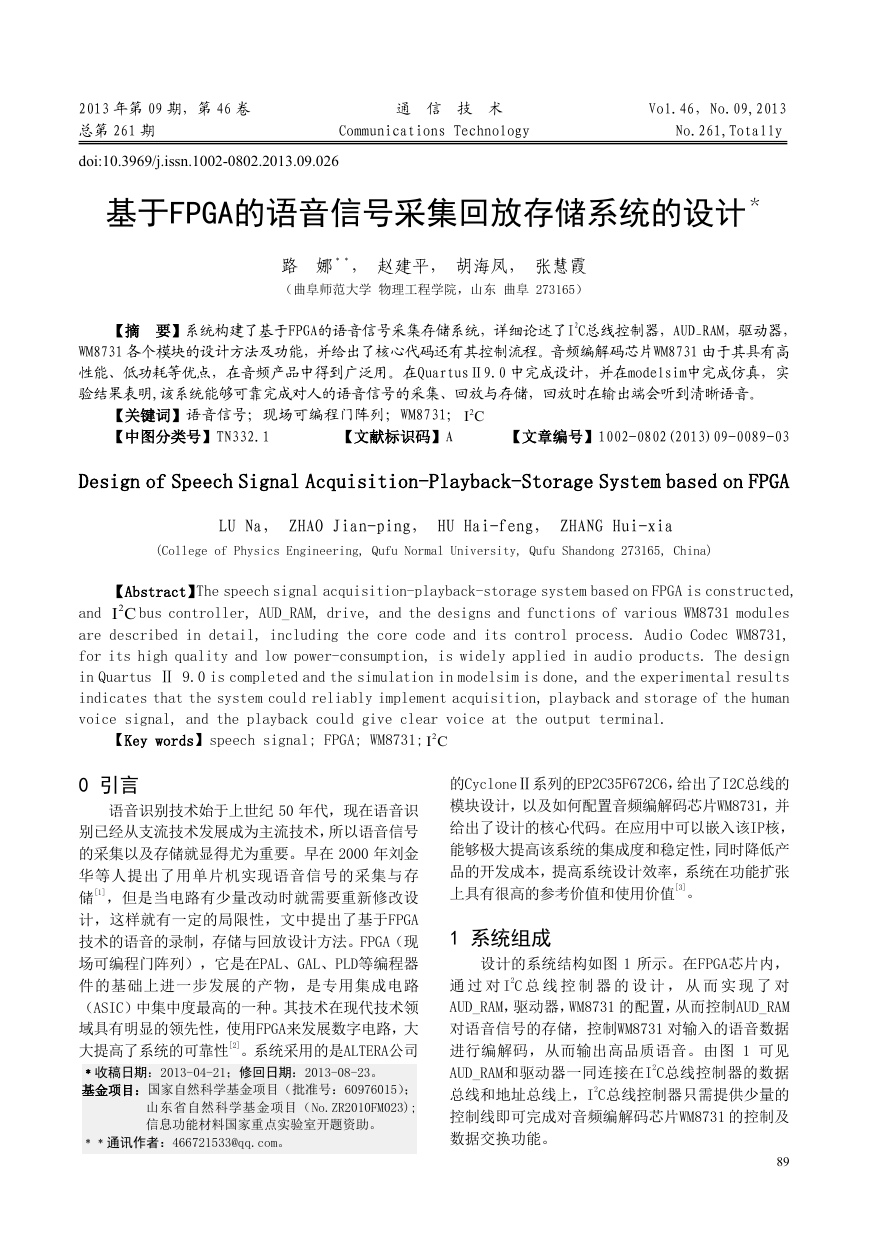

设计的系统结构如图 1 所示。在FPGA芯片内,

通 过 对 I2C 总 线 控 制 器 的 设 计 , 从 而 实 现 了 对

AUD_RAM,驱动器,WM8731 的配置,从而控制AUD_RAM

对语音信号的存储,控制WM8731 对输入的语音数据

进行编解码,从而输出高品质语音。由图 1 可见

AUD_RAM和驱动器一同连接在I2C总线控制器的数据

总线和地址总线上,I2C总线控制器只需提供少量的

控制线即可完成对音频编解码芯片WM8731 的控制及

数据交换功能。

89

�

FPGA 核心芯片Cyxlone EP2C35F672C6N

数据总线

地址总线

AUD_RAM

驱动器

I2C总线

控制器

控

制

线

控

制

线

WM8731音频编解码芯片内部

结构

外部接口

MIC

静

音

开

关

放

大

器 静

音

开

关

多

路

器

多

路

器

数字音频接口

模

数

转

换

数

模

转

换

数

字

滤

波

器

模

数

转

换

外部接口

LINE OUT

静

音

开

关

静

音

开

关

数

模

转

换

控制接口

图 1 系统结构[4]

2 系统模块设计

2.1 I2C总线控制器

i2c_sclk <= 1; sda <= 1;ack1 <= 1;

ack2 <= 1;ack3 <= 1;i2c_end <= 1;

in_sig <= 0; end

else if(i2c_start) begin

case(state)

6'd0:begin

i2c_sclk<=1;sda<=1;ack1<=1;

ack2<=1;ack3<=1;i2c_end<=0;

end //初始化 I2C 总线控制器

//start //slave address //sub address

//data //stop //endmodule

//配置十个寄存器

always@(rdaddr or rst_n)

if(!rst_n) I2C_DATA <= 0;

else begin case(rdaddr)

0:I2C_DATA<={8'h34,16'h001f};

…… //I2C 总线控制器读取数据

endmodule

2.2 音频编解码芯片 WM8731

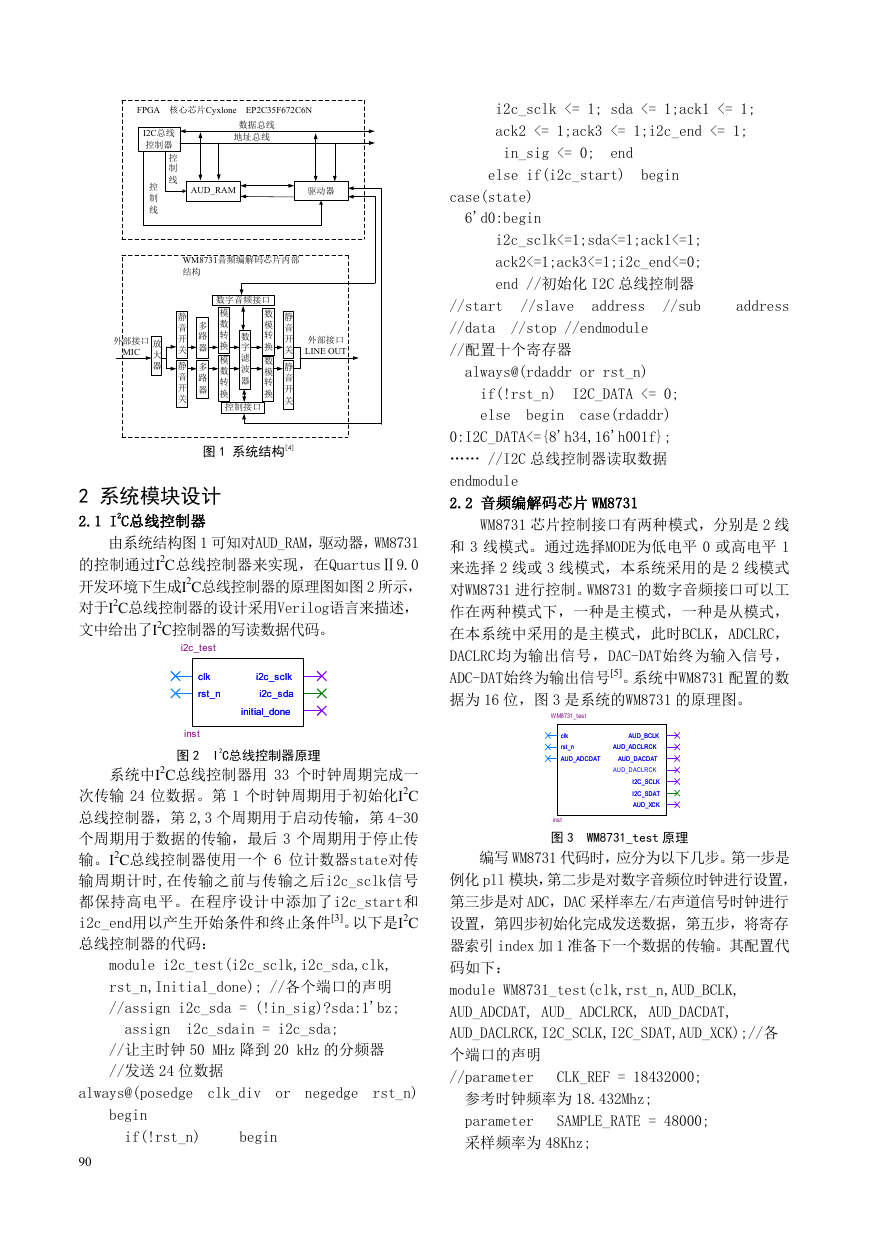

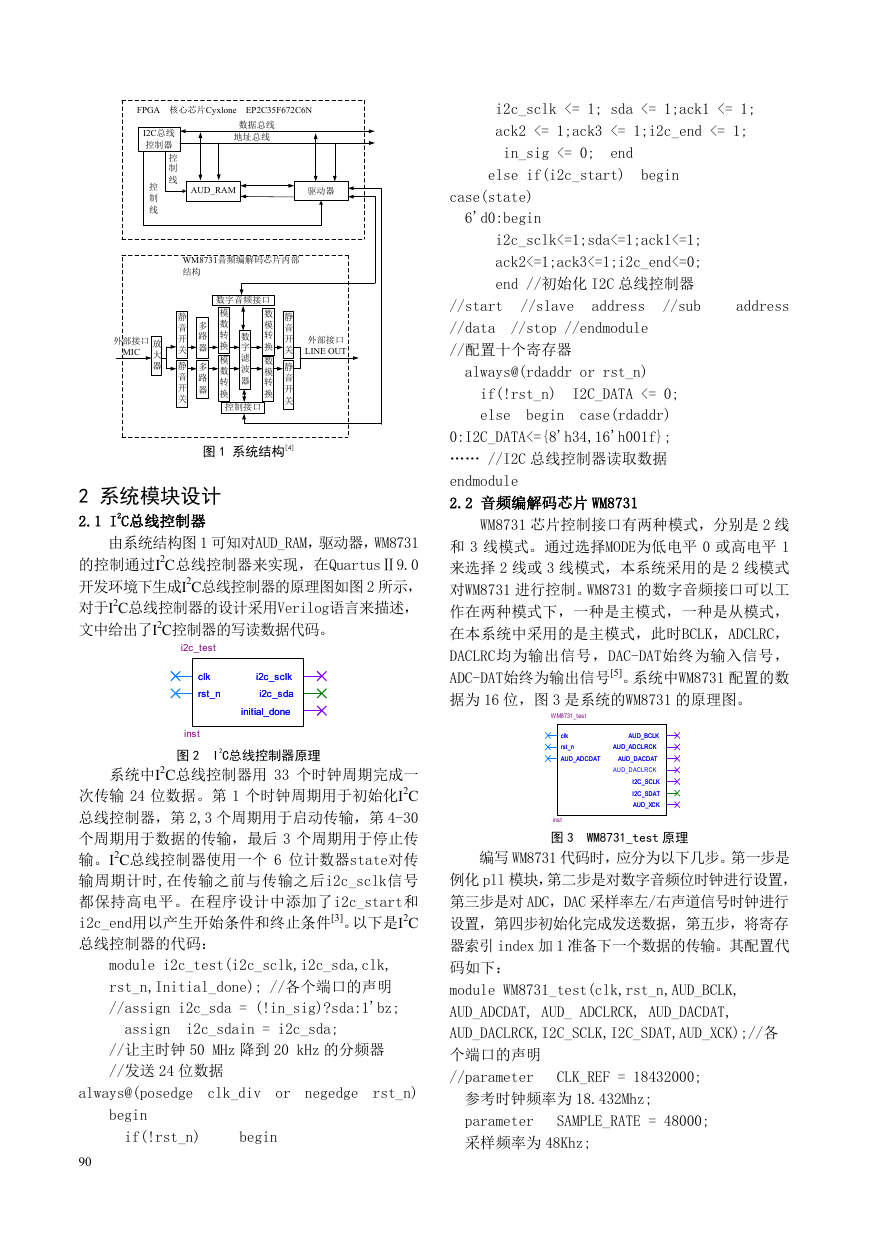

由系统结构图 1 可知对AUD_RAM,驱动器,WM8731

的控制通过I2C总线控制器来实现,在QuartusⅡ9.0

开发环境下生成I2C总线控制器的原理图如图 2 所示,

对于I2C总线控制器的设计采用Verilog语言来描述,

文中给出了I2C控制器的写读数据代码。

i2c_test

clkclk

rst_n

rst_n

i2c_sclk

i2c_sclk

i2c_sda

i2c_sda

initial_done

initial_done

inst

图 2 I2C总线控制器原理

系统中I2C总线控制器用 33 个时钟周期完成一

次传输 24 位数据。第 1 个时钟周期用于初始化I2C

总线控制器,第 2,3 个周期用于启动传输,第 4-30

个周期用于数据的传输,最后 3 个周期用于停止传

输。I2C总线控制器使用一个 6 位计数器state对传

输周期计时,在传输之前与传输之后i2c_sclk信号

都保持高电平。在程序设计中添加了i2c_start和

i2c_end用以产生开始条件和终止条件[3]。以下是I2C

总线控制器的代码:

module i2c_test(i2c_sclk,i2c_sda,clk,

rst_n,Initial_done); //各个端口的声明

//assign i2c_sda = (!in_sig)?sda:1'bz;

assign i2c_sdain = i2c_sda;

//让主时钟 50 MHz 降到 20 kHz 的分频器

//发送 24 位数据

always@(posedge clk_div or negedge rst_n)

begin

if(!rst_n) begin

90

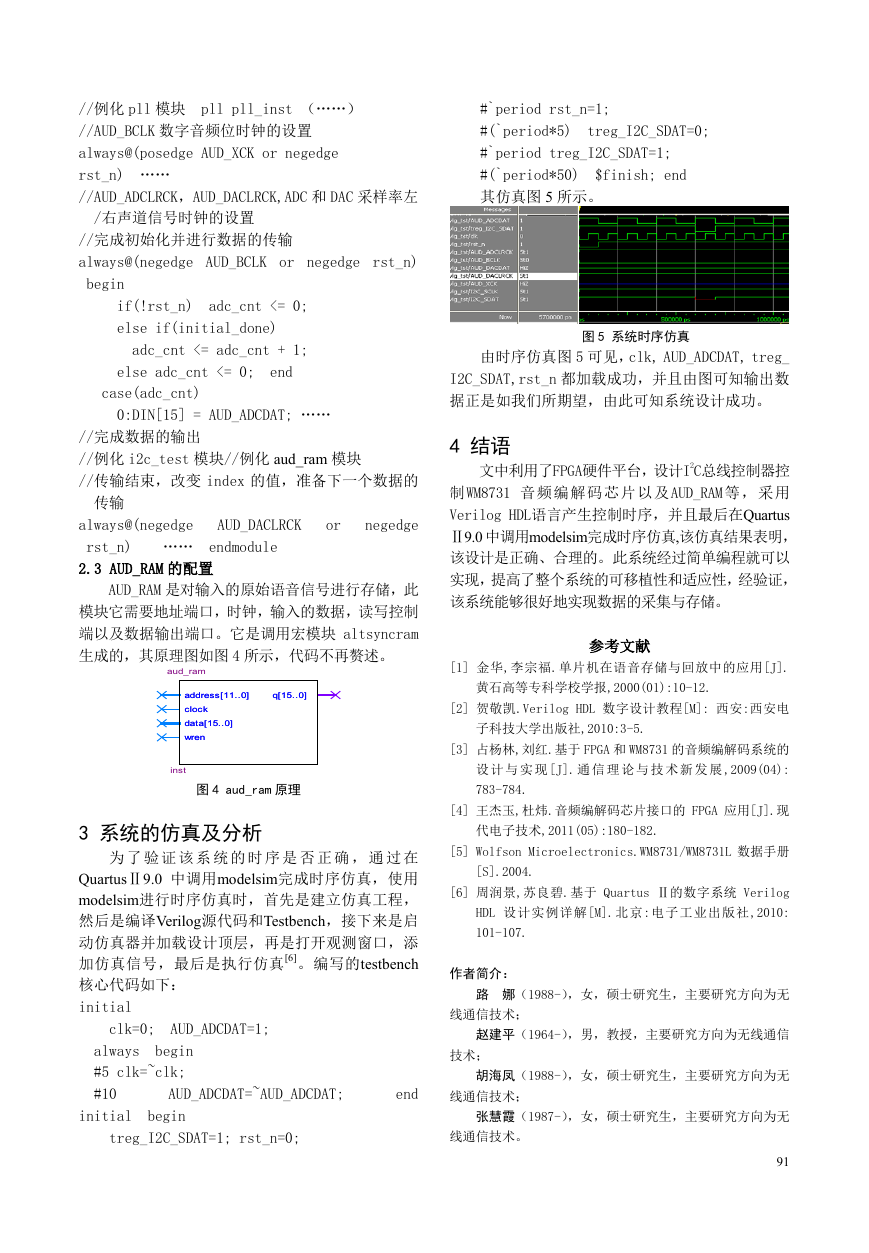

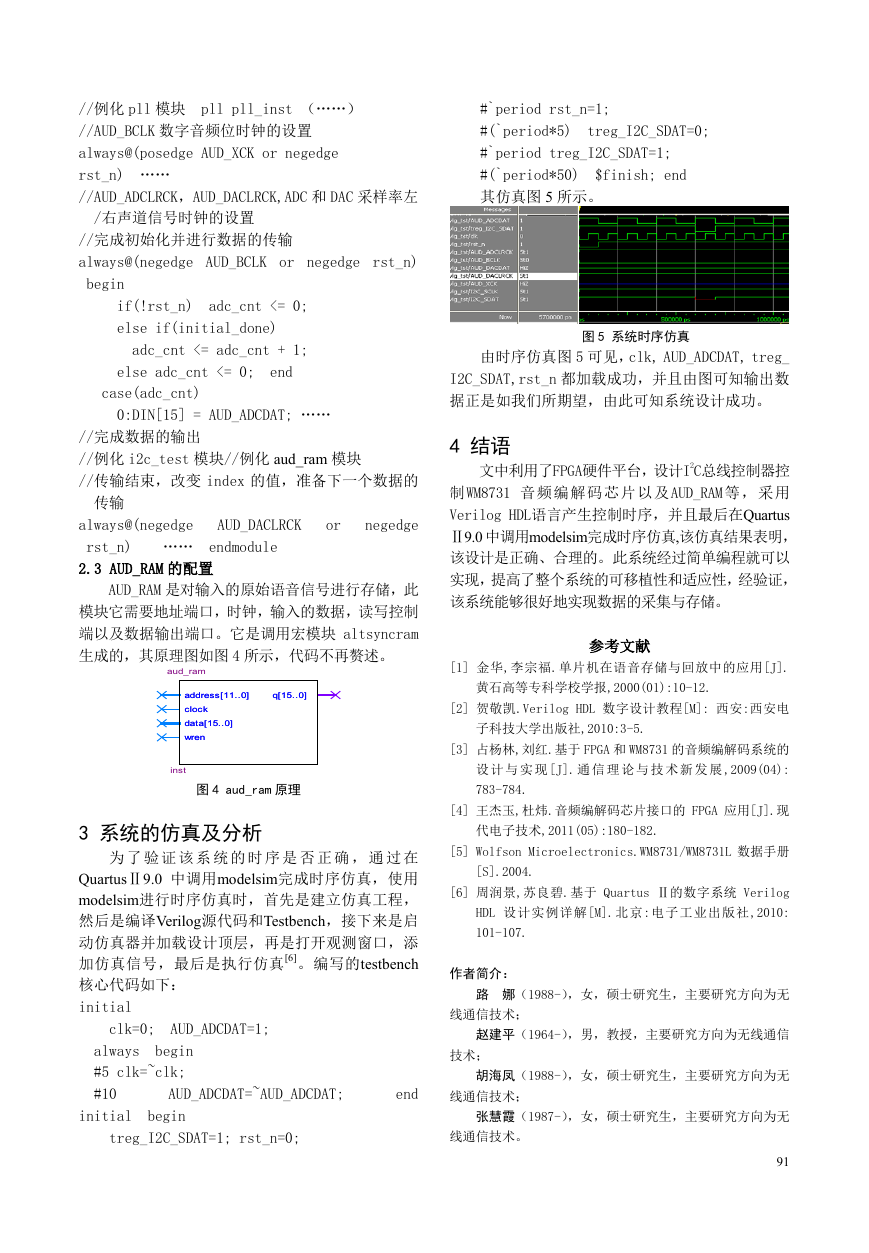

WM8731 芯片控制接口有两种模式,分别是 2 线

和 3 线模式。通过选择MODE为低电平 0 或高电平 1

来选择 2 线或 3 线模式,本系统采用的是 2 线模式

对WM8731 进行控制。WM8731 的数字音频接口可以工

作在两种模式下,一种是主模式,一种是从模式,

在本系统中采用的是主模式,此时BCLK,ADCLRC,

DACLRC均为输出信号,DAC-DAT始终为输入信号,

ADC-DAT始终为输出信号[5]。系统中WM8731 配置的数

据为 16 位,图 3 是系统的WM8731 的原理图。

WM8731_test

clkclk

rst_n

rst_n

AUD_ADCDAT

AUD_ADCDAT

AUD_BCLK

AUD_BCLK

AUD_ADCLRCK

AUD_ADCLRCK

AUD_DACDAT

AUD_DACDAT

AUD_DACLRCK

I2C_SCLK

I2C_SCLK

I2C_SDAT

I2C_SDAT

AUD_XCK

AUD_XCK

inst

图 3 WM8731_test 原理

编写 WM8731 代码时,应分为以下几步。第一步是

例化 pll 模块,第二步是对数字音频位时钟进行设置,

第三步是对 ADC,DAC 采样率左/右声道信号时钟进行

设置,第四步初始化完成发送数据,第五步,将寄存

器索引 index 加 1 准备下一个数据的传输。其配置代

码如下:

module WM8731_test(clk,rst_n,AUD_BCLK,

AUD_ADCDAT, AUD_ ADCLRCK, AUD_DACDAT,

AUD_DACLRCK,I2C_SCLK,I2C_SDAT,AUD_XCK);//各

个端口的声明

//parameter CLK_REF = 18432000;

参考时钟频率为 18.432Mhz;

parameter SAMPLE_RATE = 48000;

采样频率为 48Khz;

�

//例化 pll 模块 pll pll_inst (……)

//AUD_BCLK 数字音频位时钟的设置

always@(posedge AUD_XCK or negedge

rst_n) ……

//AUD_ADCLRCK,AUD_DACLRCK,ADC 和 DAC 采样率左

/右声道信号时钟的设置

//完成初始化并进行数据的传输

always@(negedge AUD_BCLK or negedge rst_n)

begin

if(!rst_n) adc_cnt <= 0;

else if(initial_done)

adc_cnt <= adc_cnt + 1;

else adc_cnt <= 0; end

case(adc_cnt)

0:DIN[15] = AUD_ADCDAT; ……

//完成数据的输出

//例化 i2c_test 模块//例化 aud_ram 模块

//传输结束,改变 index 的值,准备下一个数据的

传输

always@(negedge

AUD_DACLRCK

or

negedge

rst_n) …… endmodule

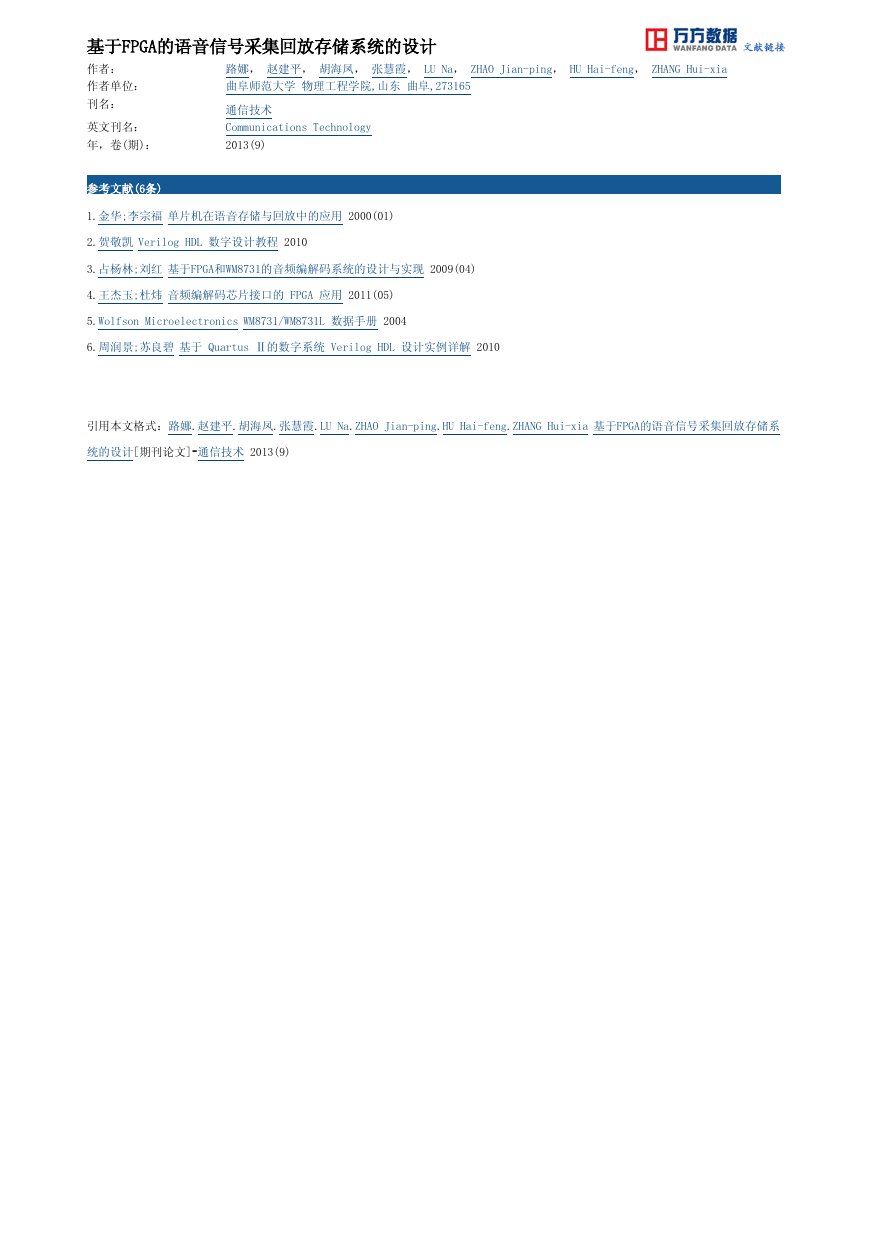

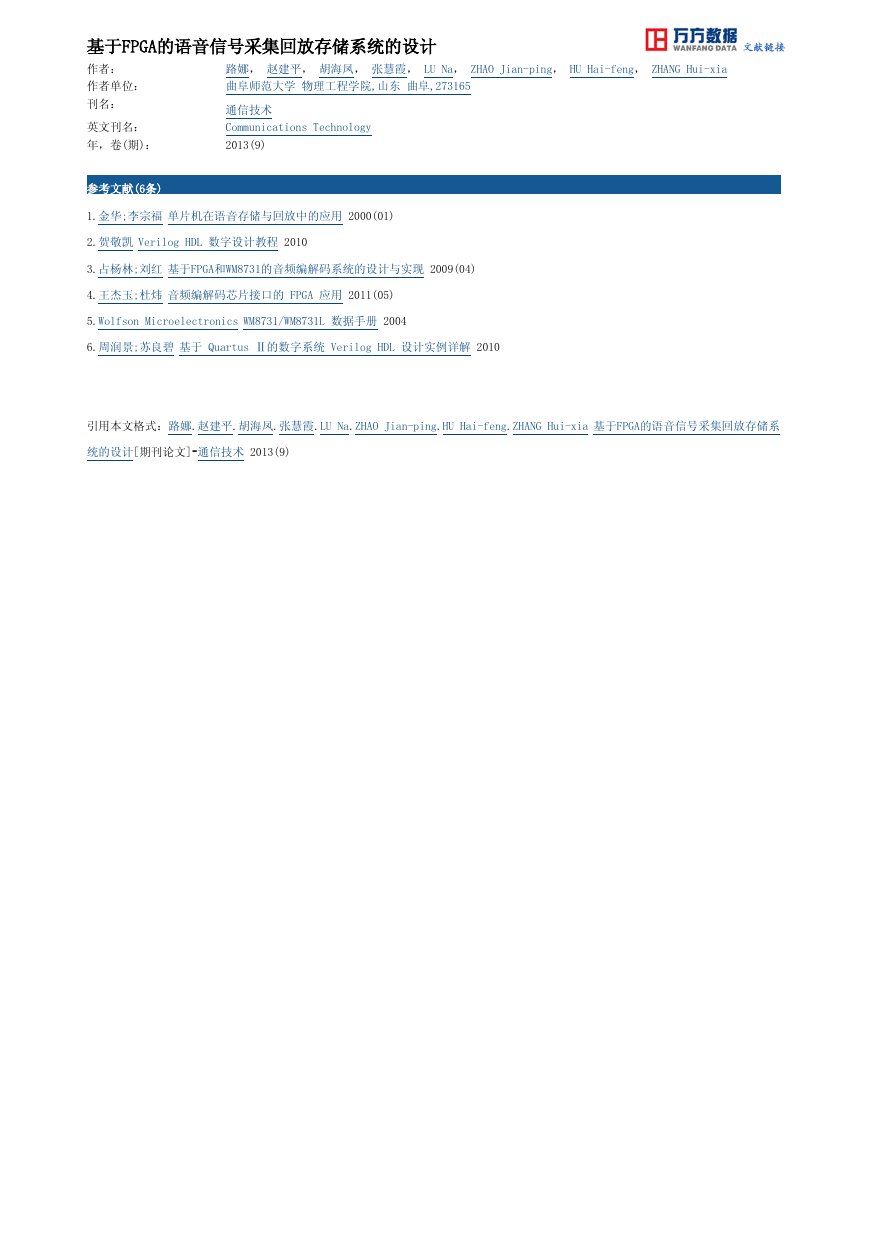

2.3 AUD_RAM 的配置

AUD_RAM 是对输入的原始语音信号进行存储,此

模块它需要地址端口,时钟,输入的数据,读写控制

端以及数据输出端口。它是调用宏模块 altsyncram

生成的,其原理图如图 4 所示,代码不再赘述。

aud_ram

address[11..0]

address[11..0]

clock

clock

data[15..0]

data[15..0]

wrenwren

q[15..0]

q[15..0]

#`period rst_n=1;

#(`period*5) treg_I2C_SDAT=0;

#`period treg_I2C_SDAT=1;

#(`period*50) $finish; end

其仿真图 5 所示。

图 5 系统时序仿真

由时序仿真图 5 可见,clk, AUD_ADCDAT, treg_

I2C_SDAT,rst_n 都加载成功,并且由图可知输出数

据正是如我们所期望,由此可知系统设计成功。

4 结语

文中利用了FPGA硬件平台,设计I2C总线控制器控

制WM8731 音频编解码芯片以及AUD_RAM 等,采用

Verilog HDL语言产生控制时序,并且最后在Quartus

Ⅱ9.0 中调用modelsim完成时序仿真,该仿真结果表明,

该设计是正确、合理的。此系统经过简单编程就可以

实现,提高了整个系统的可移植性和适应性,经验证,

该系统能够很好地实现数据的采集与存储。

参考文献

[1] 金华,李宗福.单片机在语音存储与回放中的应用[J].

黄石高等专科学校学报,2000(01):10-12.

[2] 贺敬凯.Verilog HDL 数字设计教程[M]: 西安:西安电

子科技大学出版社,2010:3-5.

[3] 占杨林,刘红.基于 FPGA 和 WM8731 的音频编解码系统的

图 4 aud_ram 原理

783-784.

设 计 与 实 现[J]. 通 信 理 论 与 技 术 新 发 展,2009(04):

inst

3 系统的仿真及分析

[4] 王杰玉,杜炜.音频编解码芯片接口的 FPGA 应用[J].现

代电子技术,2011(05):180-182.

[5] Wolfson Microelectronics.WM8731/WM8731L 数据手册

为 了 验 证 该 系 统 的 时 序 是 否 正 确 , 通 过 在

QuartusⅡ9.0 中调用modelsim完成时序仿真,使用

modelsim进行时序仿真时,首先是建立仿真工程,

然后是编译Verilog源代码和Testbench,接下来是启

动仿真器并加载设计顶层,再是打开观测窗口,添

加仿真信号,最后是执行仿真[6]。编写的testbench

核心代码如下:

initial

作者简介:

[S].2004.

101-107.

线通信技术;

[6] 周润景,苏良碧.基于 Quartus Ⅱ的数字系统 Verilog

HDL 设计实例详解[M]. 北京:电子工业出版社,2010:

路 娜(1988-),女,硕士研究生,主要研究方向为无

clk=0; AUD_ADCDAT=1;

always begin

#5 clk=~clk;

#10

AUD_ADCDAT=~AUD_ADCDAT;

赵建平(1964-),男,教授,主要研究方向为无线通信

技术;

胡海凤(1988-),女,硕士研究生,主要研究方向为无

end

线通信技术;

initial begin

张慧霞(1987-),女,硕士研究生,主要研究方向为无

treg_I2C_SDAT=1; rst_n=0;

线通信技术。

91

�

基于FPGA的语音信号采集回放存储系统的设计

作者:

路娜, 赵建平, 胡海凤, 张慧霞, LU Na, ZHAO Jian-ping, HU Hai-feng, ZHANG Hui-xia

作者单位:

刊名:

英文刊名:

曲阜师范大学 物理工程学院,山东 曲阜,273165

通信技术

Communications Technology

2013(9)

年,卷(期):

参考文献(6条)

1.金华;李宗福 单片机在语音存储与回放中的应用 2000(01)

2.贺敬凯 Verilog HDL 数字设计教程 2010

3.占杨林;刘红 基于FPGA和WM8731的音频编解码系统的设计与实现 2009(04)

4.王杰玉;杜炜 音频编解码芯片接口的 FPGA 应用 2011(05)

5.Wolfson Microelectronics WM8731/WM8731L 数据手册 2004

6.周润景;苏良碧 基于 Quartus Ⅱ的数字系统 Verilog HDL 设计实例详解 2010

引用本文格式:路娜.赵建平.胡海凤.张慧霞.LU Na.ZHAO Jian-ping.HU Hai-feng.ZHANG Hui-xia 基于FPGA的语音信号采集回放存储系

统的设计[期刊论文]-通信技术 2013(9)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc