中国科技论文在线

MWC 压缩采样系统硬件电路设计与实现#

http://www.paper.edu.cn

盖建新,李洋,杜昊辰*

(哈尔滨理工大学测控技术与仪器黑龙江省高校重点实验室, 哈尔滨, 150080)

5 摘要:针对频域稀疏信号压缩采样物理实现问题,基于调制宽带转换器(MWC)采样方法,

设计了一套完整的压缩采样硬件系统。系统由上下位机两部分组成,下位机负责压缩采样,

上位机实现信号重构。本文重点设计并实现了下位机随机混频、低通滤波、伪随机序列发生、

同步采样等电路功能,并对所设计的电路进行了实际验证。实验结果表明,所设计的系统可

以在采样的同时完成压缩,从远低于奈奎斯特率的采样数据中,以压倒性的概率重构出原始

信号。

关键词:稀疏信号;压缩采样;调制宽带转换器

中图分类号:TN721

10

Design and Implementation of Compressed Sampling

System Based on MWC

GAI Jianxin, LI Yang, DU Haochen

0 引言

随着雷达通信、电子侦察、认知无线电等领域的发展,传输信号的带宽变得越来越宽,

给信号的采样、存储、处理带来了巨大压力。按照传统采样方法,商用 ADC 采样率的发展

速度已经无法满足人们对于信号带宽增长的需求[1]。

近年来,学者 Donoho 和 Candes 等人提出的压缩感知(Compressed Sensing,CS)理论

[2-3]为该问题提出了新的解决方法,即压缩采样方法。压缩感知理论指出,若信号在某个域

下具有稀疏或可压缩的先验知识,可以使用低速的 AD 转换器完成对高频信号的不失真采

样。该理论表明采样速率不再取决于原始信号的带宽,而是取决于原始信号中重要信息的数

量和位置。随后,以色列学者 Mishali 等提出了名为调制宽带转换器(Modulated Wideband

Converter, MWC)的亚奈奎斯特采样(Sub-Nyquist)方法[4-6],所提出的 MWC 系统由随机

基金项目:国家自然科学基金(61501150);黑龙江省青年科学基金项目(QC2014C074);2013 年哈尔滨理工

大学自制教学仪器设备(装置)项目;黑龙江省学位与研究生教育教学改革研究项目(JGXM_HLJ_2015061)

作者简介:盖建新(1980-),男,副教授,主要研究方向:仪器科学与技术. E-mail: gjx800608@126.com

- 1 -

150080)

(The Higher Educational Key Laboratory for Measuring & Control Technology and

Instrumentations of Heilongjiang Province, Harbin University of Science and Technology, Harbin

Abstract: Aiming at the physical implementation issue of compressive sampling for sparse signal

in frequency domain, a complete compressive sampling hardware system is designed based on

modulation wideband converter (MWC) sampling method. This system consists of two parts: a

lower device and an upper computer. The lower device is responsible for compressive sampling,

and the upper computer realizes signal reconstruction. This paper focuses on the circuit design and

implementation of the lower device, including circuit functions of random mixing, low-pass

filtering, pseudo random sequence generating, synchronous sampling, etc. The paper verified these

circuit functions by practical experiments. Experimental results show that the designed system can

perform compression while sampling, and can reconstruct the original signal at an overwhelming

probability from the acquired data at far below Nyquist rate.

Key words: sparse signal; compresive sampling; modulation wideband converter

15

20

25

30

35

40

�

中国科技论文在线

http://www.paper.edu.cn

混频器、低通滤波器、低速采样器等组成。MWC 作为采样前端,通过稀疏最优化重构算法

[7]能够以极高的概率恢复出原始信号。

45

基于压缩感知的 MWC 采样理论一经报道立即引起了广泛关注,但目前完整的 MWC 硬

件系统的报道还很少。本文采用现有元器件,实现了一套从信号的处理、采集到信号的重构

的完整 MWC 硬件系统。实验结果验证了该系统的有效性。

1 MWC 原理简介

50

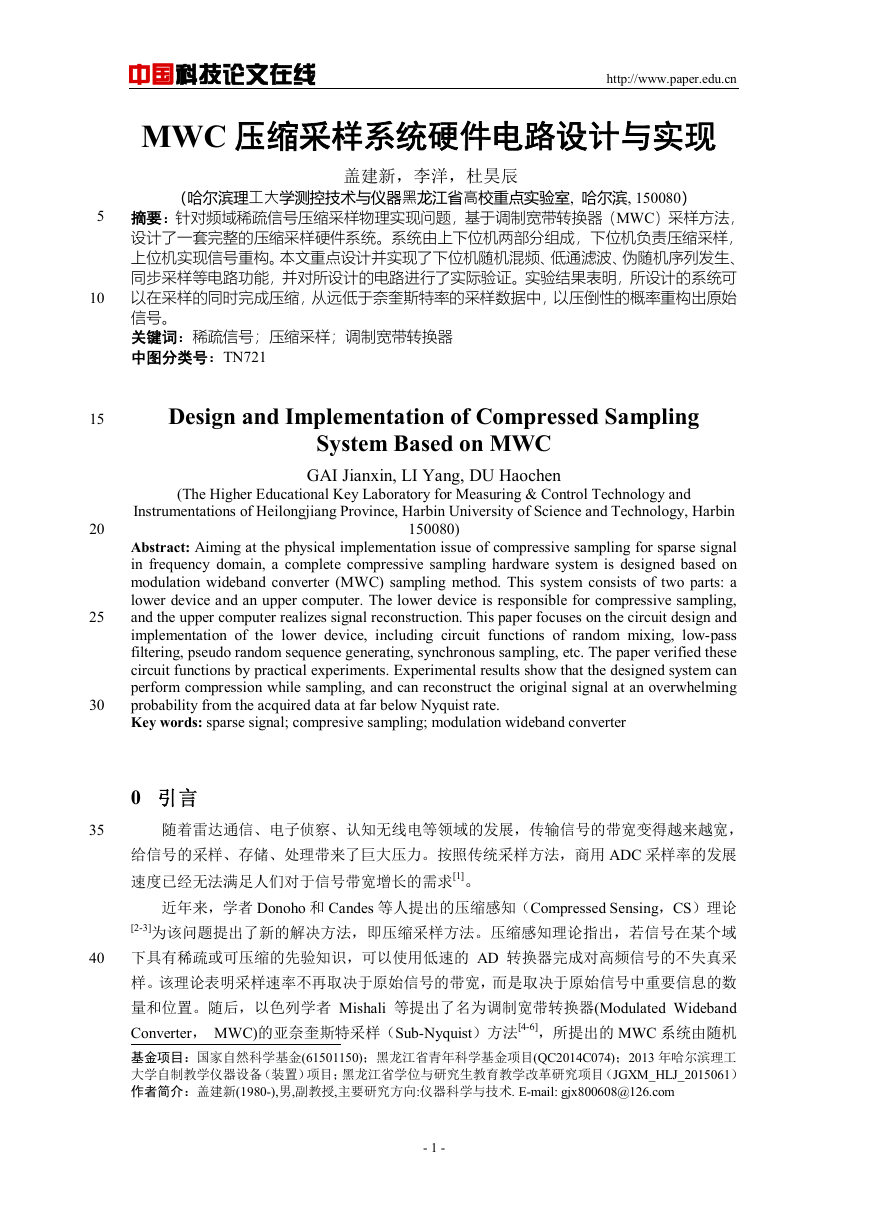

MWC 系统所针对的信号是频域稀疏信号,其模型如图 1 所示。假设 x(t)为实值连续时

间信号,其频谱位于一个较宽的频率范围[-1/2T,1/2T]内,其中 NYQ

为奈奎斯特率,

在该频率范围之内分布着 N 个较窄的子频带,各子频带宽度不超过 B Hz(本例中,N = 4)。

1 /

T

f

=

55

Fig.1 typical spectrum of sparse signal in frequency domain

图 1 典型频域稀疏信号频谱图

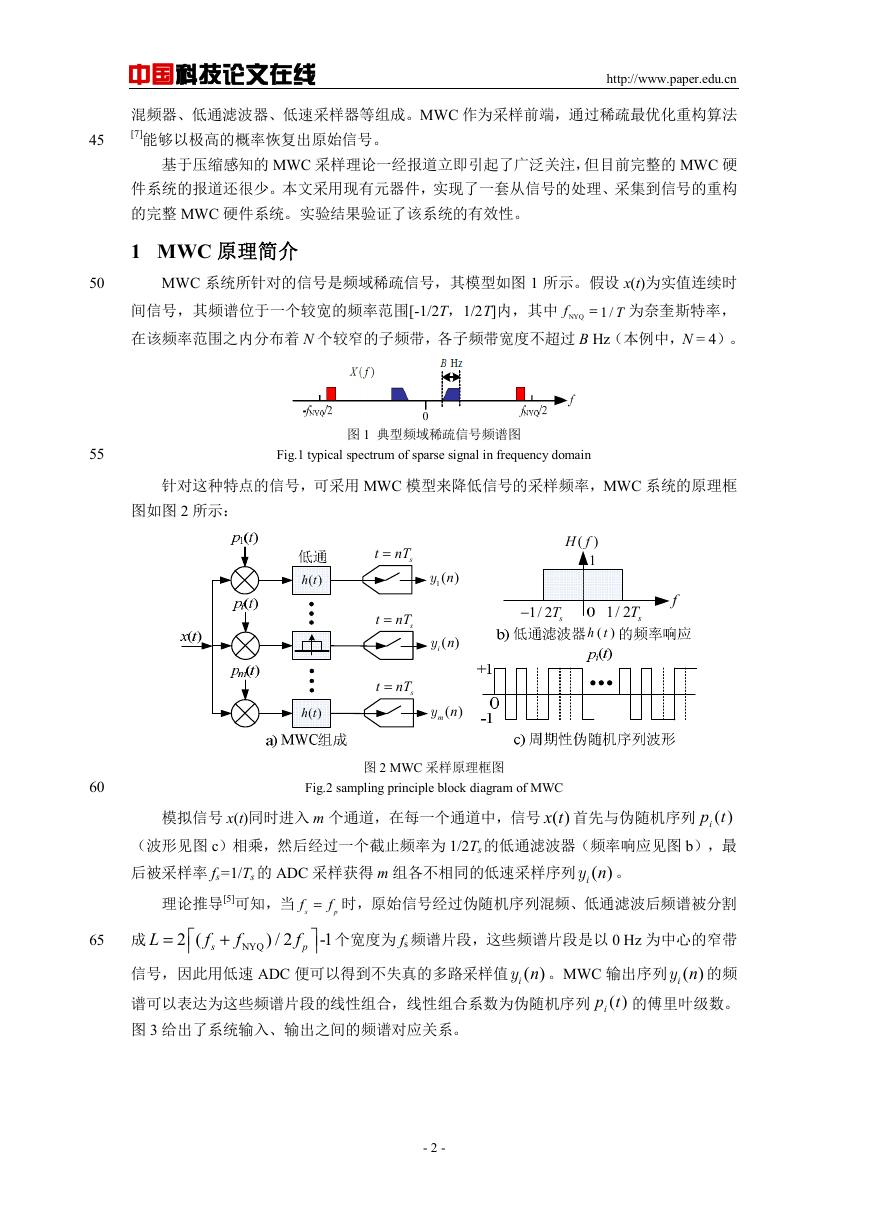

针对这种特点的信号,可采用 MWC 模型来降低信号的采样频率,MWC 系统的原理框

图如图 2 所示:

(

)H f

1

−

1/ 2 sT

1/ 2 sT

h t

( )

f

t

nT=

s

t

nT=

s

t

nT=

s

1( )ny

i ny

( )

m ny

( )

( )h t

( )h t

60

图 2 MWC 采样原理框图

Fig.2 sampling principle block diagram of MWC

ip t

模拟信号 x(t)同时进入 m 个通道,在每一个通道中,信号 ( )x t 首先与伪随机序列 ( )

(波形见图 c)相乘,然后经过一个截止频率为 1/2Ts 的低通滤波器(频率响应见图 b),最

后被采样率 fs=1/Ts 的 ADC 采样获得 m 组各不相同的低速采样序列 ( )

i ny 。

f= 时,原始信号经过伪随机序列混频、低通滤波后频谱被分割

p

理论推导[5]可知,当 s

f

=

f

) / 2

+

f

f

65

成

L

s

p

NYQ

2 (

信号,因此用低速 ADC 便可以得到不失真的多路采样值 ( )

谱可以表达为这些频谱片段的线性组合,线性组合系数为伪随机序列 ( )

图 3 给出了系统输入、输出之间的频谱对应关系。

-1

个宽度为 fs 频谱片段,这些频谱片段是以 0 Hz 为中心的窄带

i ny 的频

ip t 的傅里叶级数。

i ny 。MWC 输出序列 ( )

- 2 -

�

中国科技论文在线

http://www.paper.edu.cn

图 3 低速采样序列与原信号频谱关系示意图

Fig.3 illustration of the spectrum relation between low-rate sampling sequence and the original signal

f

/2,

/2]

(1)

s

s

该关系可简洁地表达为式(1)所示的矩阵方程形式:

f

=[-

∈

zΦ

s

其中Φ 为 m L× 矩阵且 m L< ,

。

)fy 中将 (

MWC系统重构的目标是通过特定的重构算法从 (

−−

0 1

=

y

f

(

)

=Φ

c

i n L

,

i n

,

f

(

f

)

)fz 恢复出来,因为只要得

)fz ,就可以将各个频谱片段搬移至正确的位置,进而恢复出原始信号。由于采样矩阵Φ

到 (

的行数小于列数,导致式(1)是欠定的矩阵方程组,常规解法存在无穷多个解,可以采用优

化求解算法得到唯一的最稀疏解[5]。

2 MWC 硬件设计

70

75

80

2.1 总体目标及方案

本文设计的 MWC 系统是针对通频带宽为 20MHz,输入幅值为 1± V,各个频带所允许

的最大带宽 B 小于 50 kHz 的信号。由 MWC 采样原理可知,采样通道需要多路,本文拟设

计一个四通道 MWC 电路系统,每路采样率为 500kHz;周期性伪随机序列的一个周期的符

号数为 511、低通滤波器截止频率为 150kHz。

85

总体方案框图如图 4 所示,将 MWC 压缩采样系统从结构上划分成上位机和下位机两个

部分,上、下位机之间通过 USB 接口实现采样数据的传输功能。

图 4 MWC 系统方案框图

Fig.4 block diagram of MWC system scheme

90

2.2 下位机硬件设计

下位机负责信号的压缩采样处理,主要包括随机混频、多路同步伪随机序列发生、低通

滤波、同步信号采集和处理等单元电路。

- 3 -

�

中国科技论文在线

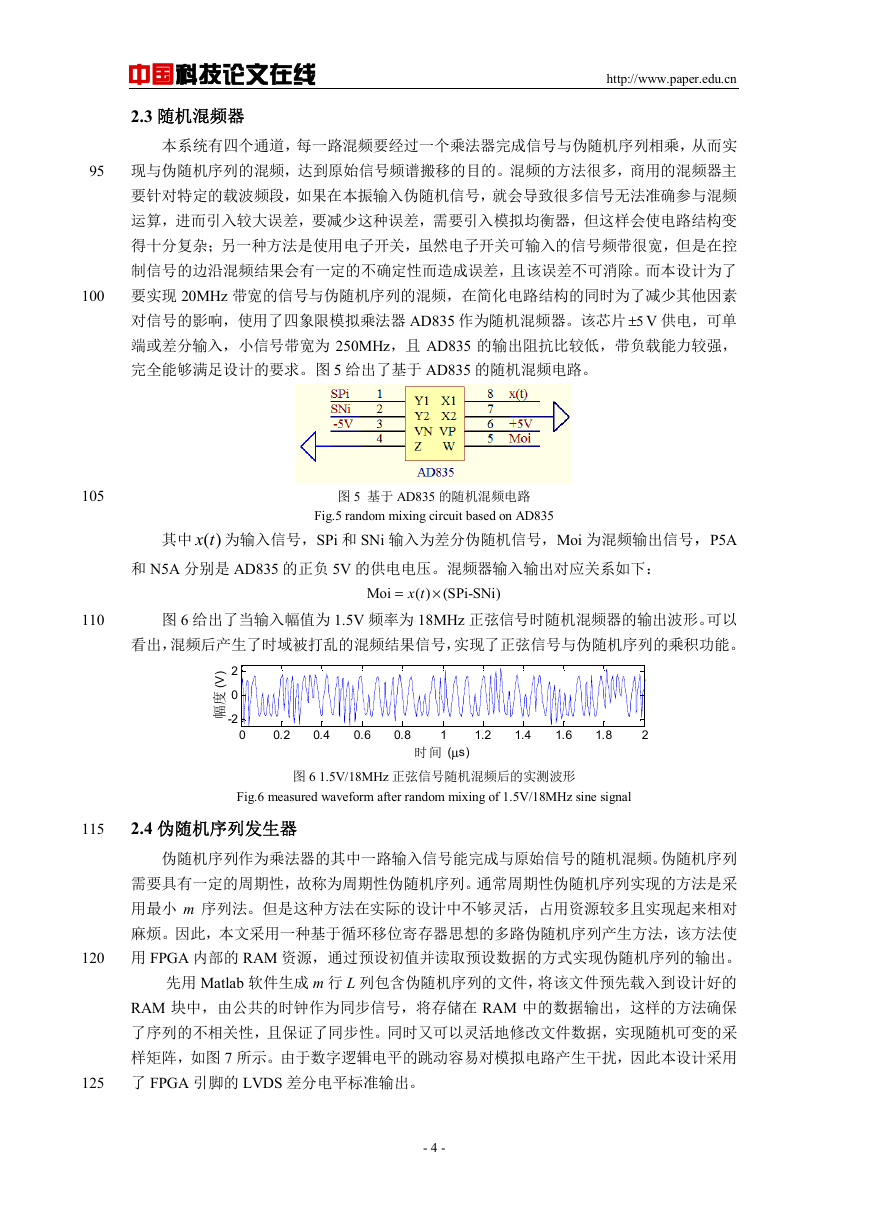

2.3 随机混频器

http://www.paper.edu.cn

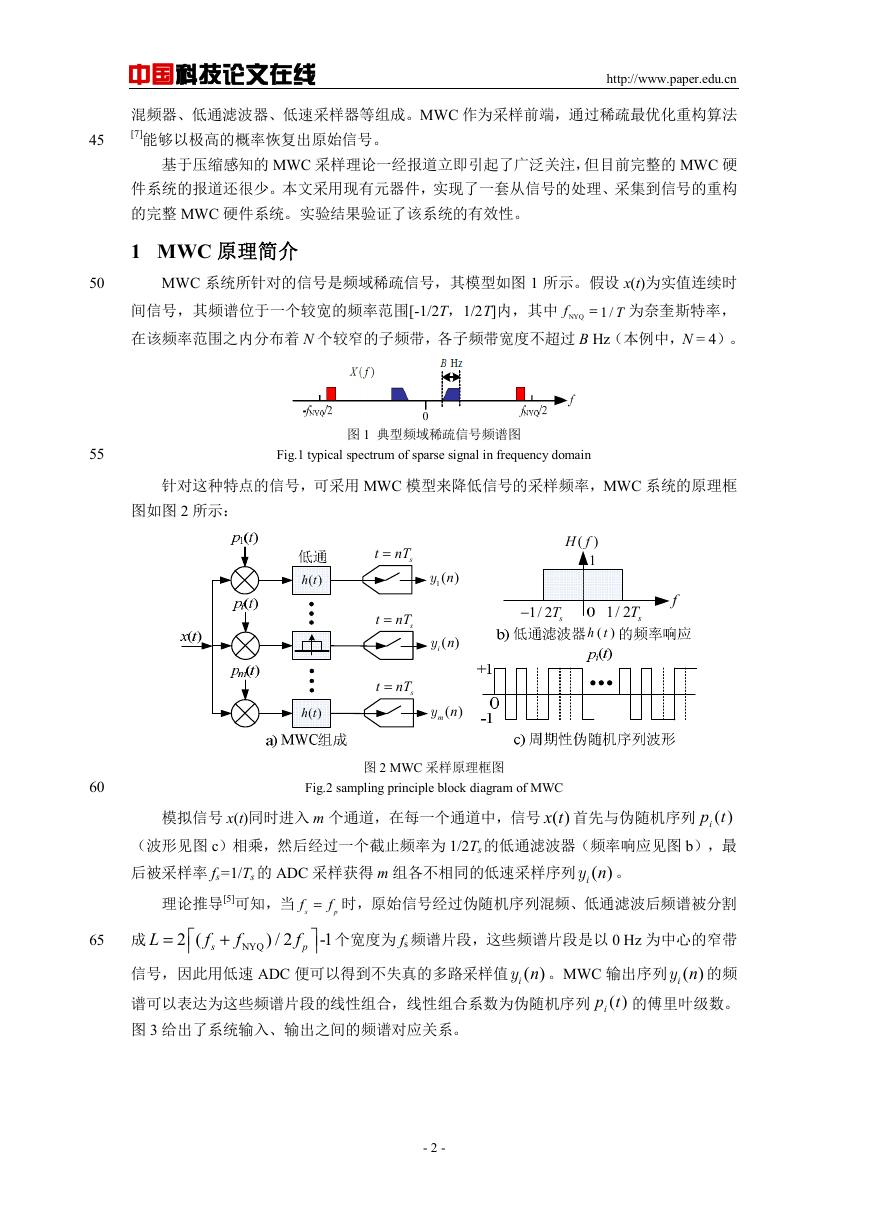

本系统有四个通道,每一路混频要经过一个乘法器完成信号与伪随机序列相乘,从而实

现与伪随机序列的混频,达到原始信号频谱搬移的目的。混频的方法很多,商用的混频器主

要针对特定的载波频段,如果在本振输入伪随机信号,就会导致很多信号无法准确参与混频

运算,进而引入较大误差,要减少这种误差,需要引入模拟均衡器,但这样会使电路结构变

得十分复杂;另一种方法是使用电子开关,虽然电子开关可输入的信号频带很宽,但是在控

制信号的边沿混频结果会有一定的不确定性而造成误差,且该误差不可消除。而本设计为了

要实现 20MHz 带宽的信号与伪随机序列的混频,在简化电路结构的同时为了减少其他因素

对信号的影响,使用了四象限模拟乘法器 AD835 作为随机混频器。该芯片 5± V 供电,可单

端或差分输入,小信号带宽为 250MHz,且 AD835 的输出阻抗比较低,带负载能力较强,

完全能够满足设计的要求。图 5 给出了基于 AD835 的随机混频电路。

图 5 基于 AD835 的随机混频电路

Fig.5 random mixing circuit based on AD835

95

100

105

其中 ( )x t 为输入信号,SPi 和 SNi 输入为差分伪随机信号,Moi 为混频输出信号,P5A

和 N5A 分别是 AD835 的正负 5V 的供电电压。混频器输入输出对应关系如下:

Moi

=

x t

( )

×

(SPi-SNi)

110

图 6 给出了当输入幅值为 1.5V 频率为 18MHz 正弦信号时随机混频器的输出波形。可以

看出,混频后产生了时域被打乱的混频结果信号,实现了正弦信号与伪随机序列的乘积功能。

)

V

(

度

幅

2

0

-2

0

0.2

0.4

0.6

0.8

1

时 间 (μs)

1.2

1.4

1.6

1.8

2

图 6 1.5V/18MHz 正弦信号随机混频后的实测波形

Fig.6 measured waveform after random mixing of 1.5V/18MHz sine signal

115

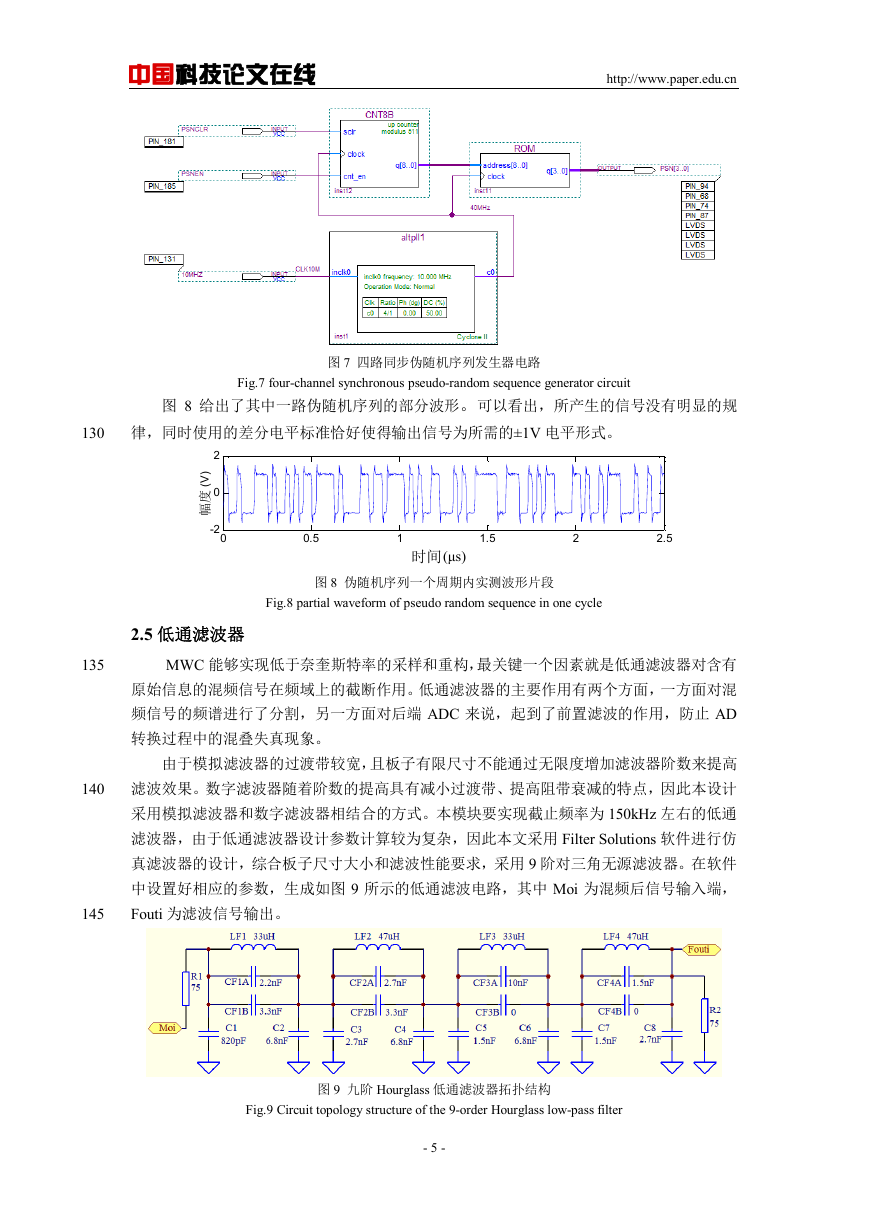

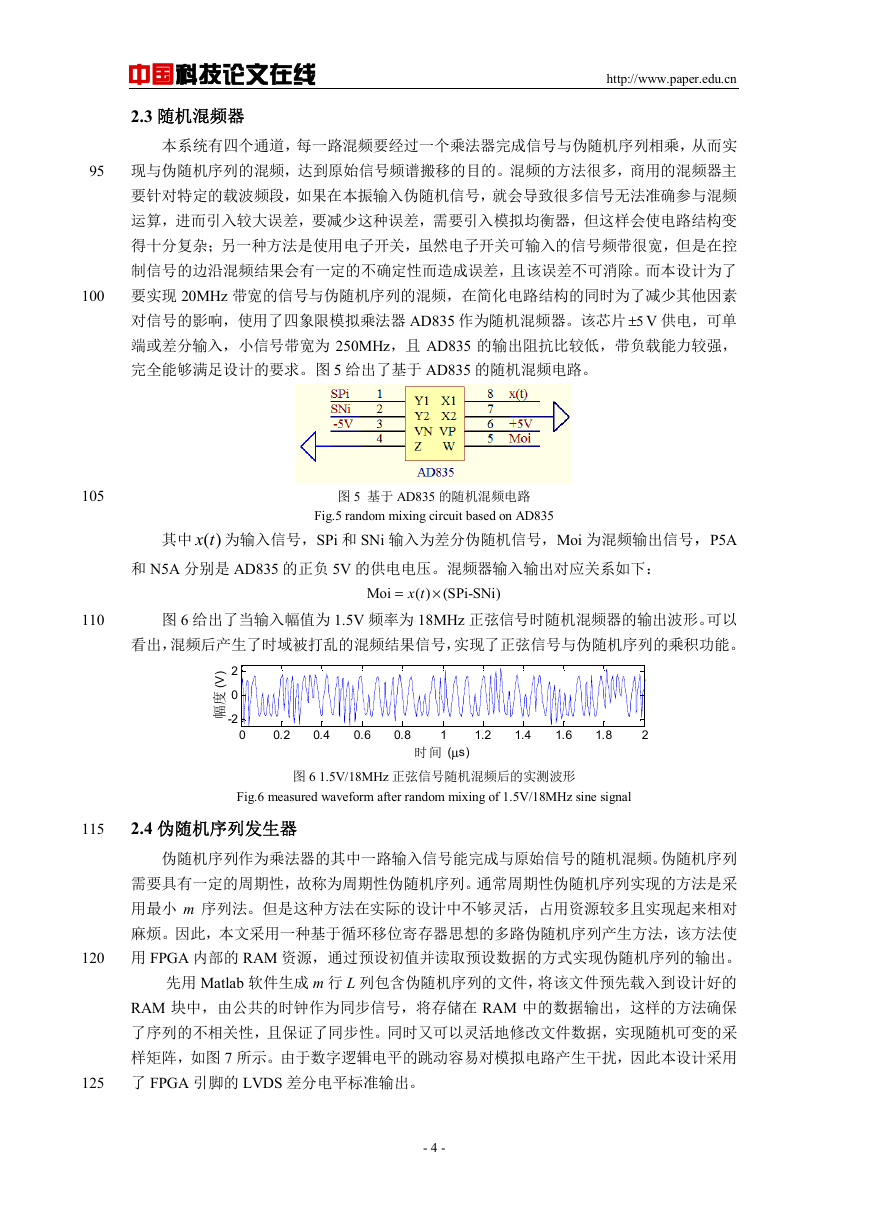

2.4 伪随机序列发生器

伪随机序列作为乘法器的其中一路输入信号能完成与原始信号的随机混频。伪随机序列

需要具有一定的周期性,故称为周期性伪随机序列。通常周期性伪随机序列实现的方法是采

用最小 m 序列法。但是这种方法在实际的设计中不够灵活,占用资源较多且实现起来相对

麻烦。因此,本文采用一种基于循环移位寄存器思想的多路伪随机序列产生方法,该方法使

用 FPGA 内部的 RAM 资源,通过预设初值并读取预设数据的方式实现伪随机序列的输出。

先用 Matlab 软件生成 m 行 L 列包含伪随机序列的文件,将该文件预先载入到设计好的

RAM 块中,由公共的时钟作为同步信号,将存储在 RAM 中的数据输出,这样的方法确保

了序列的不相关性,且保证了同步性。同时又可以灵活地修改文件数据,实现随机可变的采

样矩阵,如图 7 所示。由于数字逻辑电平的跳动容易对模拟电路产生干扰,因此本设计采用

了 FPGA 引脚的 LVDS 差分电平标准输出。

120

125

- 4 -

�

中国科技论文在线

http://www.paper.edu.cn

图 7 四路同步伪随机序列发生器电路

Fig.7 four-channel synchronous pseudo-random sequence generator circuit

图 8 给出了其中一路伪随机序列的部分波形。可以看出,所产生的信号没有明显的规

130

律,同时使用的差分电平标准恰好使得输出信号为所需的±1V 电平形式。

2

0

)

V

(

度

幅

-2

0

0.5

1

1.5

2

时间

(μs)

图 8 伪随机序列一个周期内实测波形片段

Fig.8 partial waveform of pseudo random sequence in one cycle

2.5

2.5 低通滤波器

135

140

145

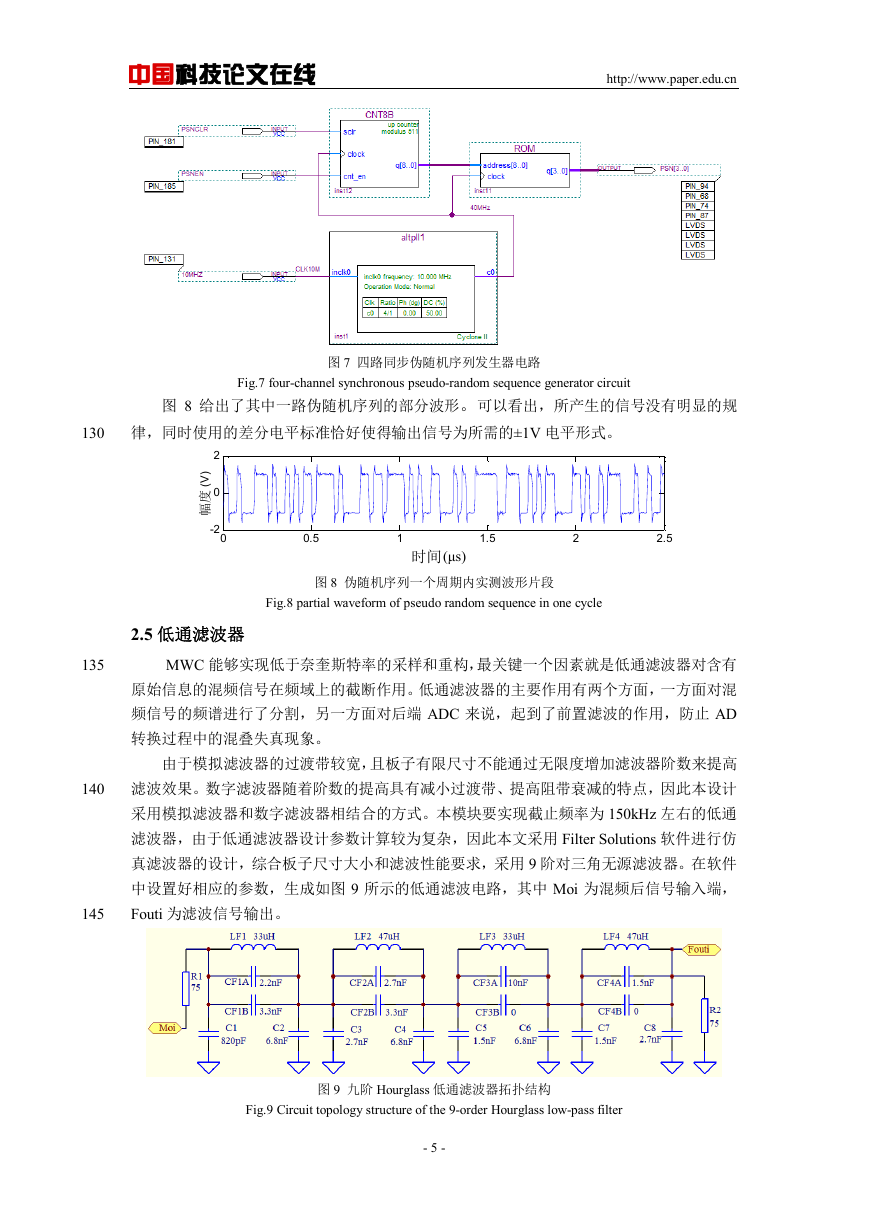

MWC 能够实现低于奈奎斯特率的采样和重构,最关键一个因素就是低通滤波器对含有

原始信息的混频信号在频域上的截断作用。低通滤波器的主要作用有两个方面,一方面对混

频信号的频谱进行了分割,另一方面对后端 ADC 来说,起到了前置滤波的作用,防止 AD

转换过程中的混叠失真现象。

由于模拟滤波器的过渡带较宽,且板子有限尺寸不能通过无限度增加滤波器阶数来提高

滤波效果。数字滤波器随着阶数的提高具有减小过渡带、提高阻带衰减的特点,因此本设计

采用模拟滤波器和数字滤波器相结合的方式。本模块要实现截止频率为 150kHz 左右的低通

滤波器,由于低通滤波器设计参数计算较为复杂,因此本文采用 Filter Solutions 软件进行仿

真滤波器的设计,综合板子尺寸大小和滤波性能要求,采用 9 阶对三角无源滤波器。在软件

中设置好相应的参数,生成如图 9 所示的低通滤波电路,其中 Moi 为混频后信号输入端,

Fouti 为滤波信号输出。

图 9 九阶 Hourglass 低通滤波器拓扑结构

Fig.9 Circuit topology structure of the 9-order Hourglass low-pass filter

- 5 -

�

中国科技论文在线

http://www.paper.edu.cn

150

155

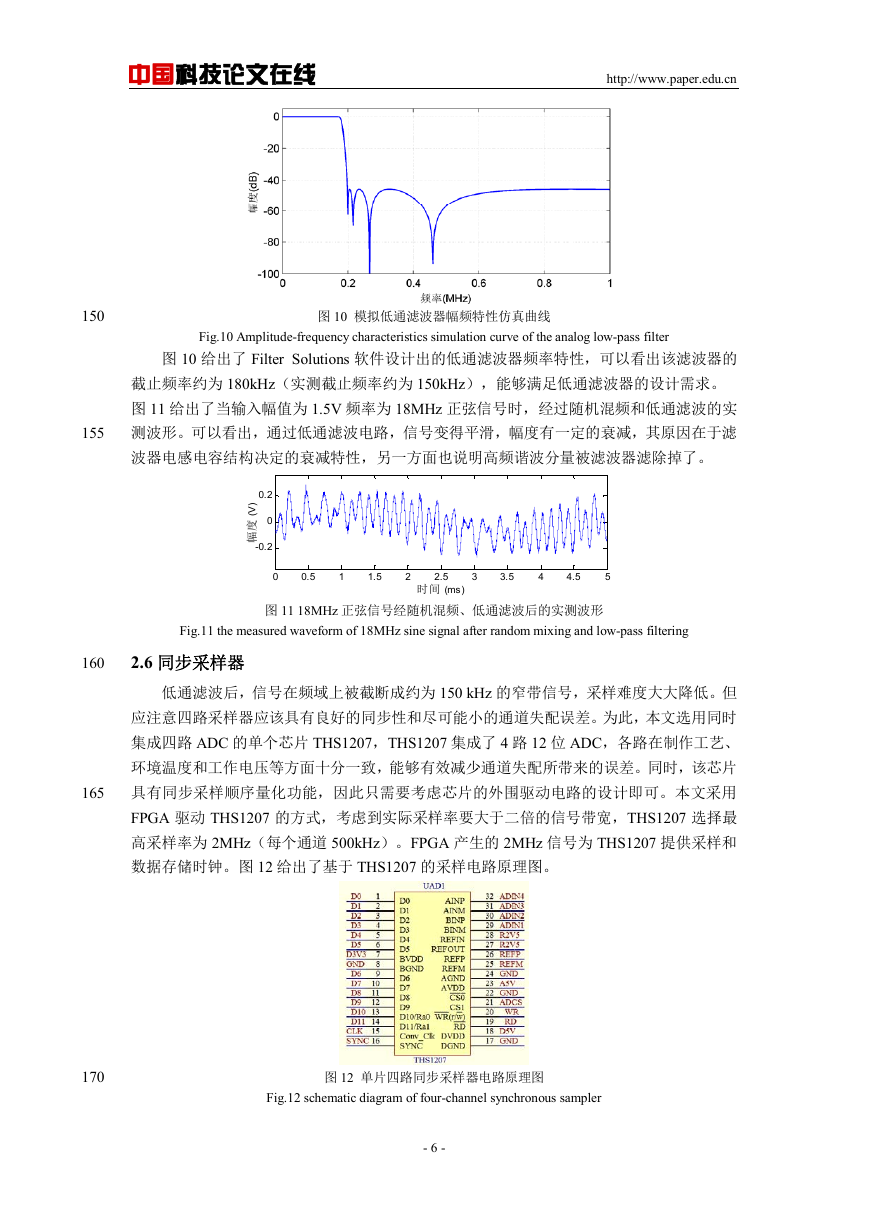

图 10 模拟低通滤波器幅频特性仿真曲线

Fig.10 Amplitude-frequency characteristics simulation curve of the analog low-pass filter

图 10 给出了 Filter Solutions 软件设计出的低通滤波器频率特性,可以看出该滤波器的

截止频率约为 180kHz(实测截止频率约为 150kHz),能够满足低通滤波器的设计需求。

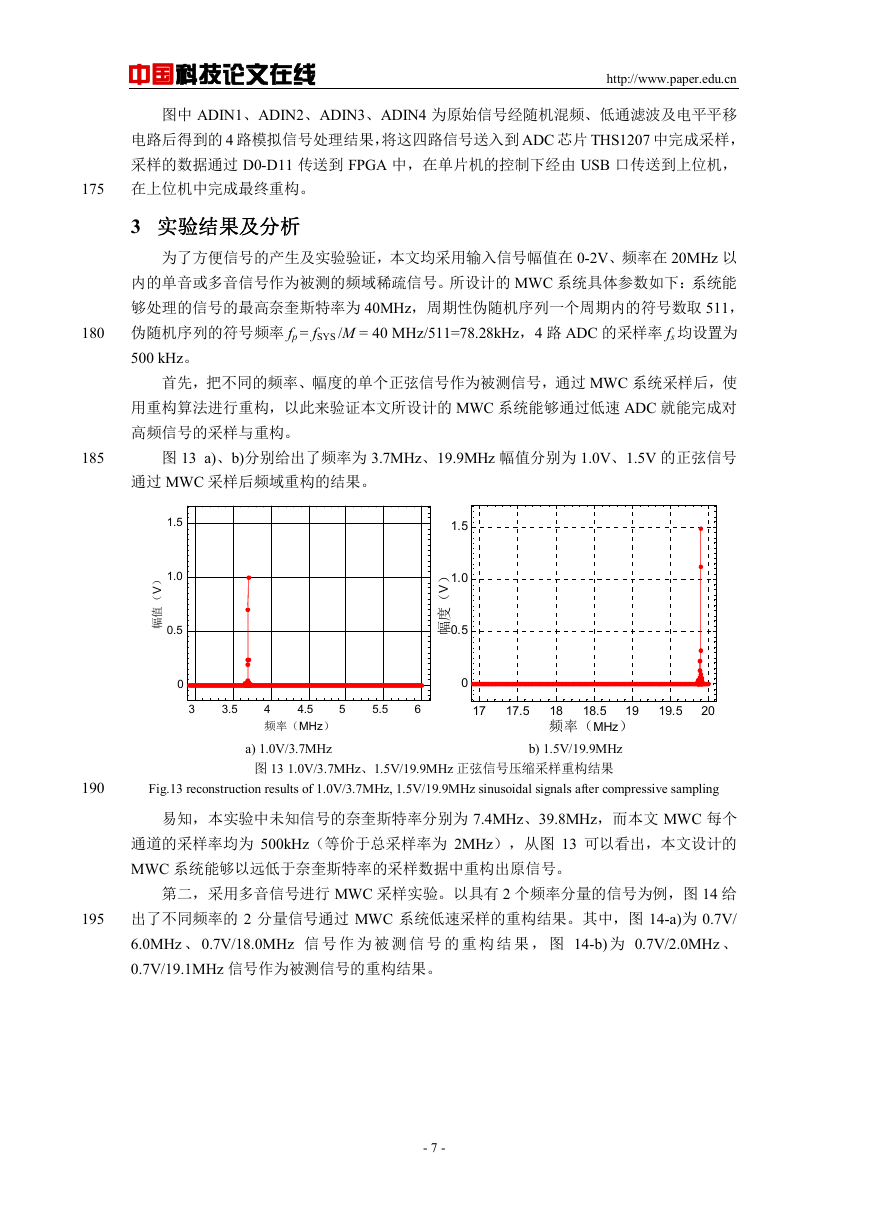

图 11 给出了当输入幅值为 1.5V 频率为 18MHz 正弦信号时,经过随机混频和低通滤波的实

测波形。可以看出,通过低通滤波电路,信号变得平滑,幅度有一定的衰减,其原因在于滤

波器电感电容结构决定的衰减特性,另一方面也说明高频谐波分量被滤波器滤除掉了。

0.2

0

-0.2

)

V

(

度

幅

0

0.5

1

1.5

2

2.5

时间 (ms)

3

3.5

4

4.5

5

图 11 18MHz 正弦信号经随机混频、低通滤波后的实测波形

Fig.11 the measured waveform of 18MHz sine signal after random mixing and low-pass filtering

160

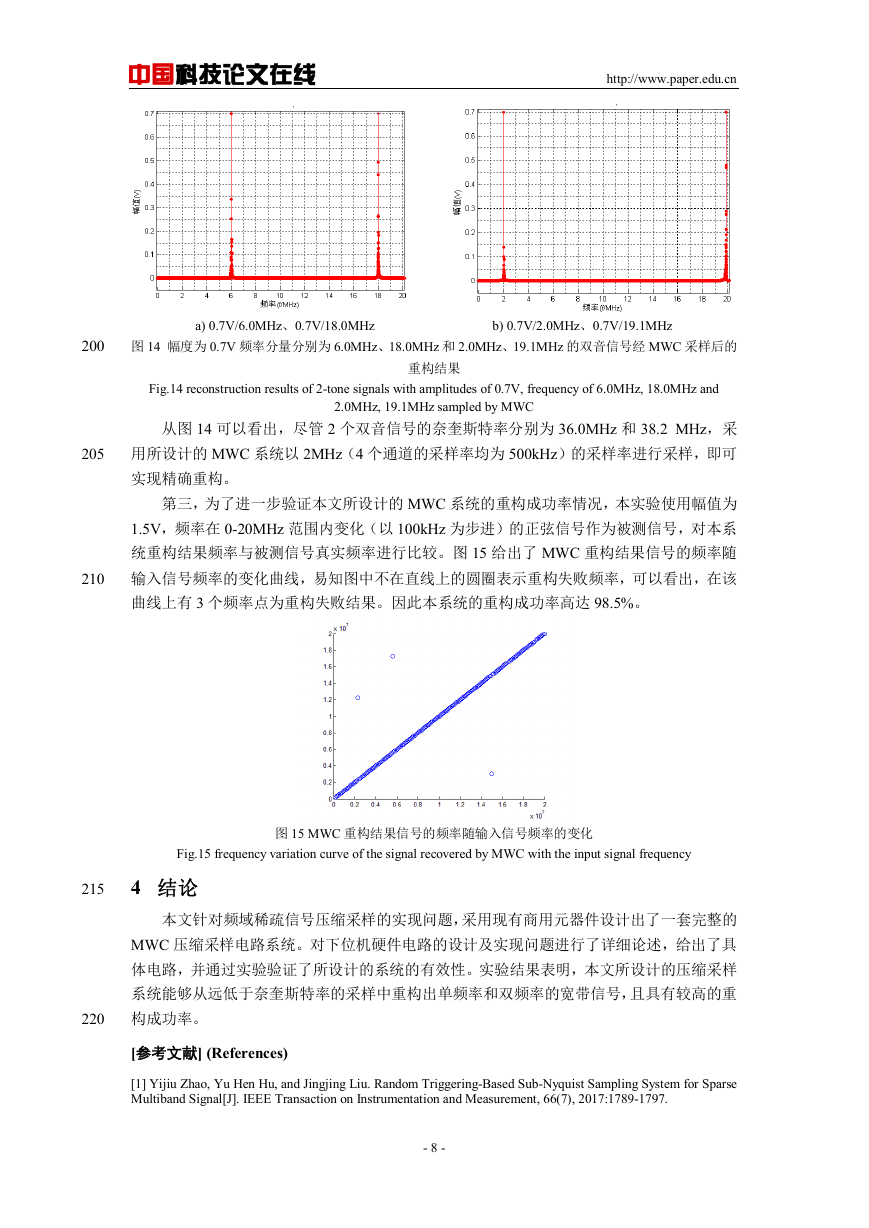

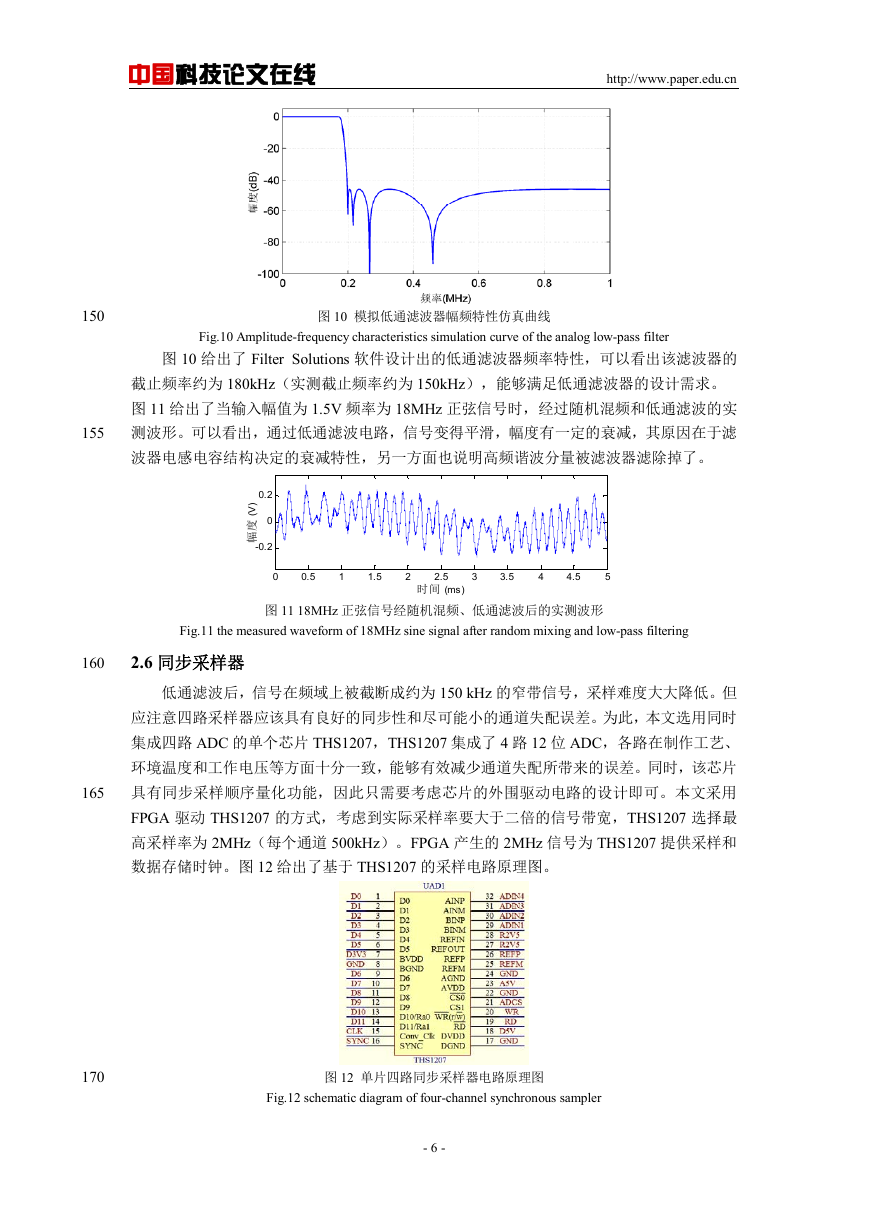

2.6 同步采样器

低通滤波后,信号在频域上被截断成约为 150 kHz 的窄带信号,采样难度大大降低。但

应注意四路采样器应该具有良好的同步性和尽可能小的通道失配误差。为此,本文选用同时

集成四路 ADC 的单个芯片 THS1207,THS1207 集成了 4 路 12 位 ADC,各路在制作工艺、

环境温度和工作电压等方面十分一致,能够有效减少通道失配所带来的误差。同时,该芯片

具有同步采样顺序量化功能,因此只需要考虑芯片的外围驱动电路的设计即可。本文采用

FPGA 驱动 THS1207 的方式,考虑到实际采样率要大于二倍的信号带宽,THS1207 选择最

高采样率为 2MHz(每个通道 500kHz)。FPGA 产生的 2MHz 信号为 THS1207 提供采样和

数据存储时钟。图 12 给出了基于 THS1207 的采样电路原理图。

图 12 单片四路同步采样器电路原理图

Fig.12 schematic diagram of four-channel synchronous sampler

- 6 -

165

170

�

175

180

185

190

195

中国科技论文在线

http://www.paper.edu.cn

图中 ADIN1、ADIN2、ADIN3、ADIN4 为原始信号经随机混频、低通滤波及电平平移

电路后得到的 4 路模拟信号处理结果,将这四路信号送入到 ADC 芯片 THS1207 中完成采样,

采样的数据通过 D0-D11 传送到 FPGA 中,在单片机的控制下经由 USB 口传送到上位机,

在上位机中完成最终重构。

3 实验结果及分析

为了方便信号的产生及实验验证,本文均采用输入信号幅值在 0-2V、频率在 20MHz 以

内的单音或多音信号作为被测的频域稀疏信号。所设计的 MWC 系统具体参数如下:系统能

够处理的信号的最高奈奎斯特率为 40MHz,周期性伪随机序列一个周期内的符号数取 511,

伪随机序列的符号频率 fp = fSYS /M = 40 MHz/511=78.28kHz,4 路 ADC 的采样率 fs 均设置为

500 kHz。

首先,把不同的频率、幅度的单个正弦信号作为被测信号,通过 MWC 系统采样后,使

用重构算法进行重构,以此来验证本文所设计的 MWC 系统能够通过低速 ADC 就能完成对

高频信号的采样与重构。

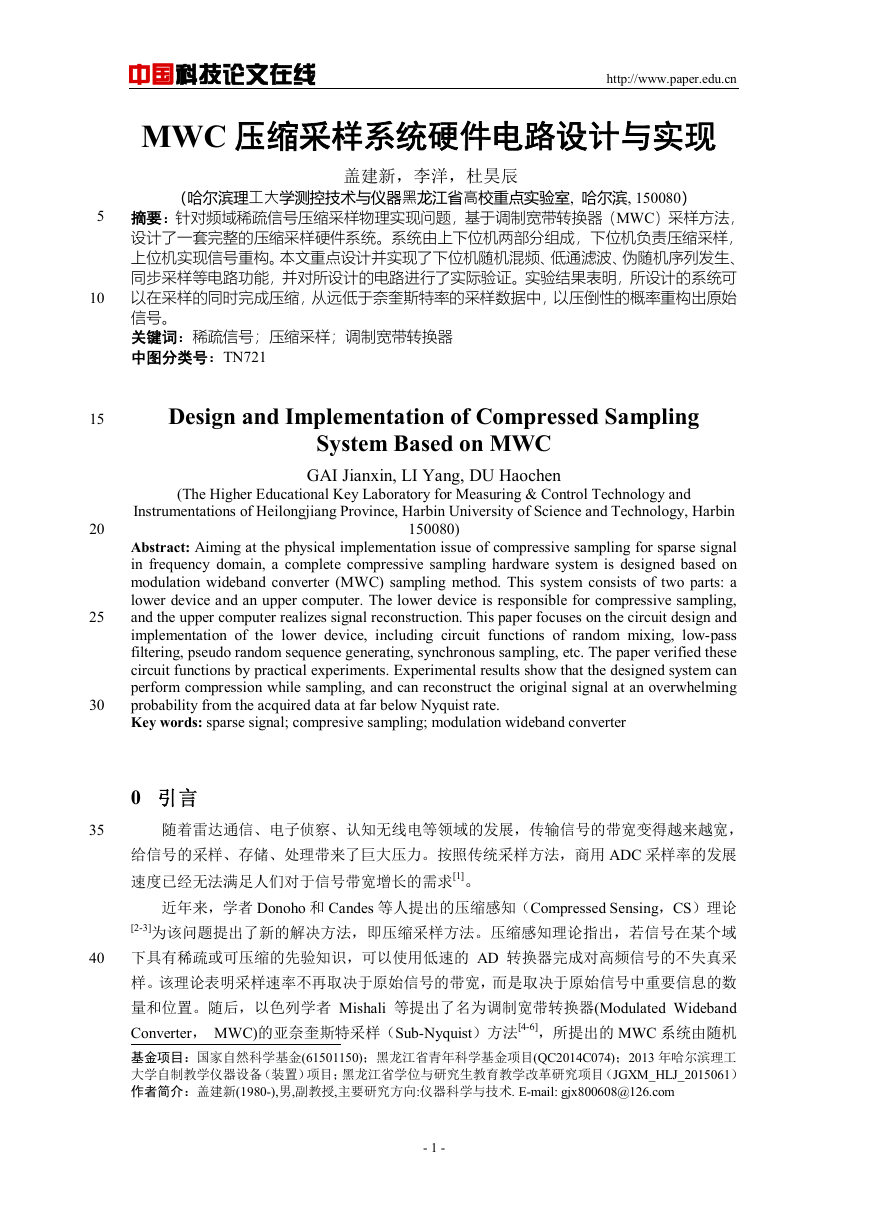

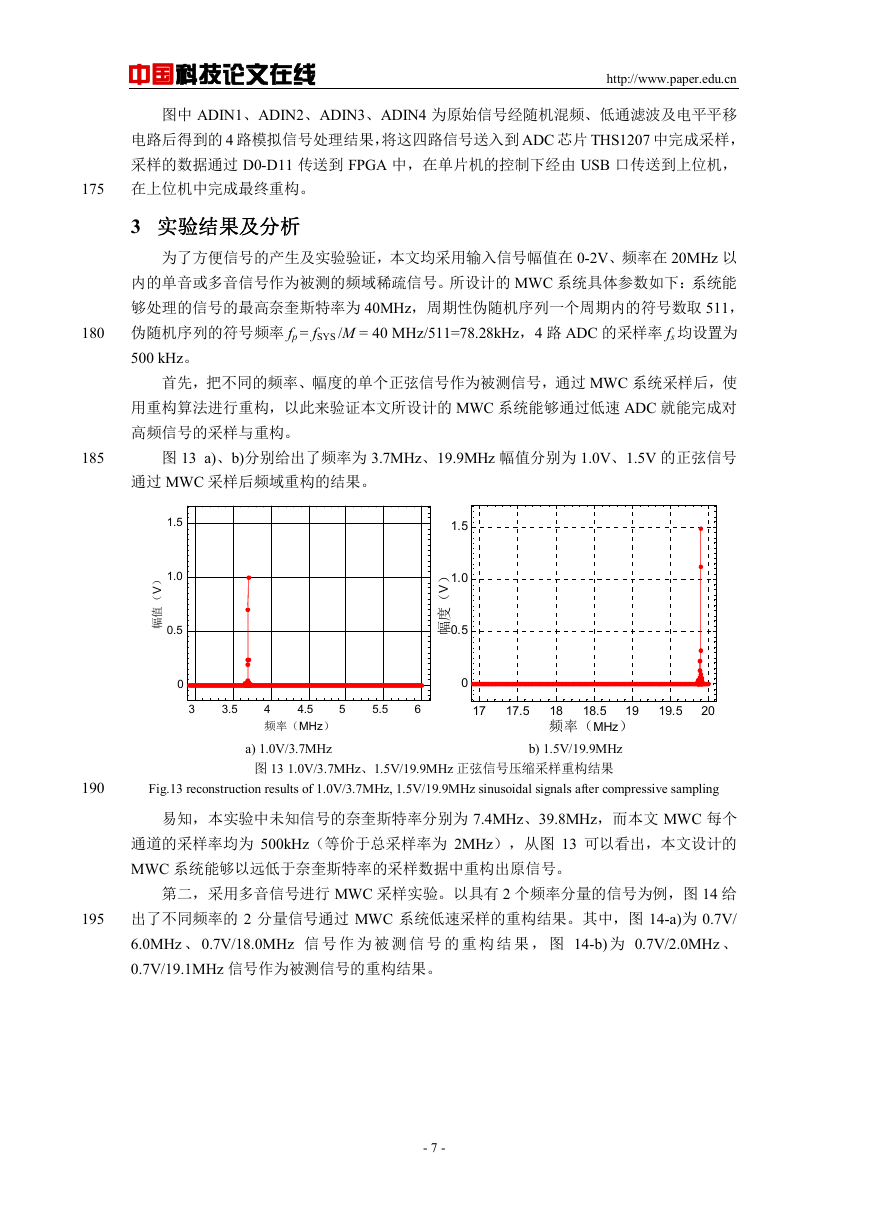

图 13 a)、b)分别给出了频率为 3.7MHz、19.9MHz 幅值分别为 1.0V、1.5V 的正弦信号

通过 MWC 采样后频域重构的结果。

)

V

(

值

幅

1.5

1.0

0.5

0

3

3.5

1.5

1.0

)

V

(

度

幅

0.5

0

5.5

6

4.5

5

4

频率(MHz)

18

19

频率( )MHz

a) 1.0V/3.7MHz b) 1.5V/19.9MHz

图 13 1.0V/3.7MHz、1.5V/19.9MHz 正弦信号压缩采样重构结果

18.5

17

17.5

19.5

20

Fig.13 reconstruction results of 1.0V/3.7MHz, 1.5V/19.9MHz sinusoidal signals after compressive sampling

易知,本实验中未知信号的奈奎斯特率分别为 7.4MHz、39.8MHz,而本文 MWC 每个

通道的采样率均为 500kHz(等价于总采样率为 2MHz),从图 13 可以看出,本文设计的

MWC 系统能够以远低于奈奎斯特率的采样数据中重构出原信号。

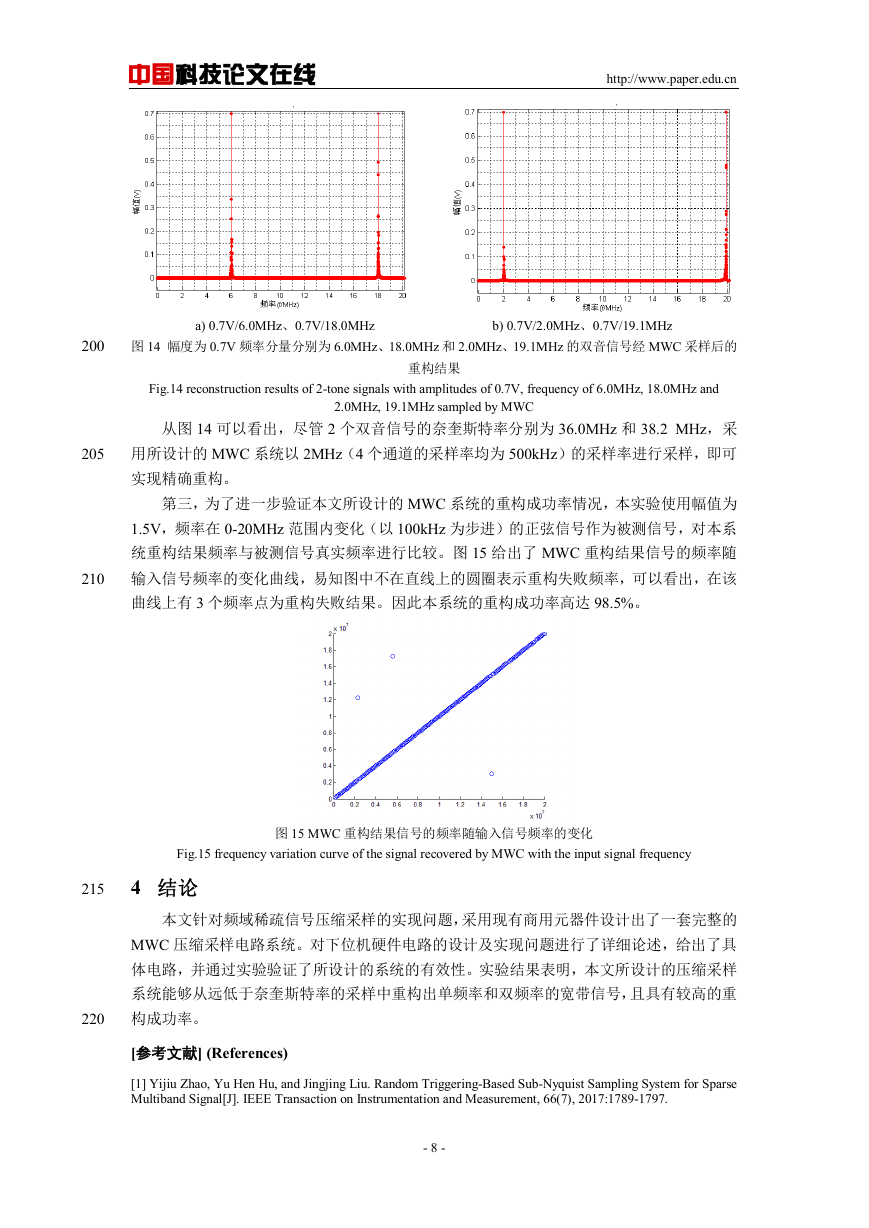

第二,采用多音信号进行 MWC 采样实验。以具有 2 个频率分量的信号为例,图 14 给

出了不同频率的 2 分量信号通过 MWC 系统低速采样的重构结果。其中,图 14-a)为 0.7V/

6.0MHz 、 0.7V/18.0MHz 信 号 作 为 被 测 信 号 的 重 构 结 果 , 图 14-b) 为 0.7V/2.0MHz 、

0.7V/19.1MHz 信号作为被测信号的重构结果。

- 7 -

�

中国科技论文在线

http://www.paper.edu.cn

a) 0.7V/6.0MHz、0.7V/18.0MHz b) 0.7V/2.0MHz、0.7V/19.1MHz

200

图 14 幅度为 0.7V 频率分量分别为 6.0MHz、18.0MHz 和 2.0MHz、19.1MHz 的双音信号经 MWC 采样后的

重构结果

Fig.14 reconstruction results of 2-tone signals with amplitudes of 0.7V, frequency of 6.0MHz, 18.0MHz and

2.0MHz, 19.1MHz sampled by MWC

205

210

从图 14 可以看出,尽管 2 个双音信号的奈奎斯特率分别为 36.0MHz 和 38.2 MHz,采

用所设计的 MWC 系统以 2MHz(4 个通道的采样率均为 500kHz)的采样率进行采样,即可

实现精确重构。

第三,为了进一步验证本文所设计的 MWC 系统的重构成功率情况,本实验使用幅值为

1.5V,频率在 0-20MHz 范围内变化(以 100kHz 为步进)的正弦信号作为被测信号,对本系

统重构结果频率与被测信号真实频率进行比较。图 15 给出了 MWC 重构结果信号的频率随

输入信号频率的变化曲线,易知图中不在直线上的圆圈表示重构失败频率,可以看出,在该

曲线上有 3 个频率点为重构失败结果。因此本系统的重构成功率高达 98.5%。

图 15 MWC 重构结果信号的频率随输入信号频率的变化

Fig.15 frequency variation curve of the signal recovered by MWC with the input signal frequency

215

4 结论

本文针对频域稀疏信号压缩采样的实现问题,采用现有商用元器件设计出了一套完整的

MWC 压缩采样电路系统。对下位机硬件电路的设计及实现问题进行了详细论述,给出了具

体电路,并通过实验验证了所设计的系统的有效性。实验结果表明,本文所设计的压缩采样

系统能够从远低于奈奎斯特率的采样中重构出单频率和双频率的宽带信号,且具有较高的重

220

构成功率。

[参考文献] (References)

[1] Yijiu Zhao, Yu Hen Hu, and Jingjing Liu. Random Triggering-Based Sub-Nyquist Sampling System for Sparse

Multiband Signal[J]. IEEE Transaction on Instrumentation and Measurement, 66(7), 2017:1789-1797.

- 8 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc