一、课程设计题目

ADC 有效位数的测量

二、课程设计目的

1、掌握 ADC 有效位数的测量方法。

2、掌握 Quartus II 和 Matlab 的使用。

3、掌握 ADC 电路的设计方法。

4、掌握数字前端调理电路设计方法。

三、课程设计内容

1、ADC 的基本参数

(1)信噪比(SNR)

信噪比使输入单频正弦波信号和噪声(不包括任何谐波以及直流)的功率比,

是定义噪声大小的基本参数。典型值以分贝表示:

(1)

理想状态下,最小转换噪声的理论值只包括量化噪声。

(2)

(2)无杂散动态范围(SFDR)

ADC 输入单频正弦波的有效值与在频域观察到的杂散信号的有效值之比。

典型值以分贝表示。

(3)信噪失真比(SINAD)

指 ADC 满量程单频理想正弦波输入信号的有效值与 ADC 输出信号的

Nyquist 带宽的全部其它频率分量(包括谐波分量,但不包括直流分量)的总有

效值之比。

(4)有效位数(ENOB)

(3)

ENOB 是在 ADC 器件信噪比基础上计算出来的,它将传输信号质量转换为

等效比特分辨率。实际上系统噪声使输出信号失真,失真大小就反映在信噪比上。

(4)

1

i20lgsgnalSNRnoise(6.021.76)SNRNdB20lgsignalSINADnoiseharmonics1.766.02SINADENOB�

(5)总谐波失真(THD)

出现在输入频率整数倍频点(谐波)的失真有效值与输入正弦波的有效值之

比。测量中仅包括奈奎斯特频限内的谐波,典型值以分贝表示:

(5)

(6)微分非线性(DNL)

理论上,模数器件相邻两个数据之间,模拟量的差值都是一样的。但实际上,

相邻两刻度之间的间距不可能都是相等的。所以 ADC 相邻两刻度之间最大的差

异就叫微分非线性。

(7)积分非线性(INL)

积分非线性表示了 ADC 器件在所有的数值点上对应的模拟值和真实值之间

的误差最大的那一点误差值,也就是输出数值偏离线性最大的距离。

2、 ADC 有效位数的计算方法

(1)快速傅里叶变换法

FFT 法是对时域采集的一组数据进行 FFT 运算,得到采样信号的傅里叶频

谱,然后从频谱中计算信号、噪声及谐波分量的功率,求出信噪比失真比 SINAD,

在计算出 ENOBS。FFT 法的优点是数学运算容易、运算速度高、程序编制容易。

几乎所有 ADC 的失真都可在其输出频谱上表现出来,但它不能避免 ADC 以为

的误差源对测试带来的影响。

(2)正弦拟合法

正弦拟合法是对测试数据按照某种拟合残差为最小的准则,以正弦函数为回

归模型的一种最小二乘回归分析方法,首先将 ADC 所能接受的满量程正弦信号

送给 ADC 数字化,其结果存在储存器中,然后利用输入信号的数据记录拟合一

个正弦函数,进一步计算出理想正弦函数与实际拟合函数之间的均方根误差后,

即可计算出 ENOB。

3、 ADC 数字前端调理电路的设计

(1) 调理电路

将输入的模拟信号变换为用于数据采集、控制过程、执行计算显示读出和其

他目的的信号的电路。

(2) 基本作用

2

20lgsignalTHDdistortion�

模拟传感器可测量很多物理量,但由于传感器信号不能直接转换为数字数

据,这是因为传感器输出是相当小的电压、电流或电阻变化,因此,在变换为数

字信号之前必须进行调理。调理就是放大,缓冲或定标模拟信号等,使其适合于

模/数转换器(ADC)的输入。然后,ADC 对模拟信号进行数字化,并把数字信号

送到 MCU 或其他数字器件,以便用于系统的数据处理

(3) 电路组成

包括放大电路、衰减电路、隔离电路、补偿电路、整形电路、滤波电路等。

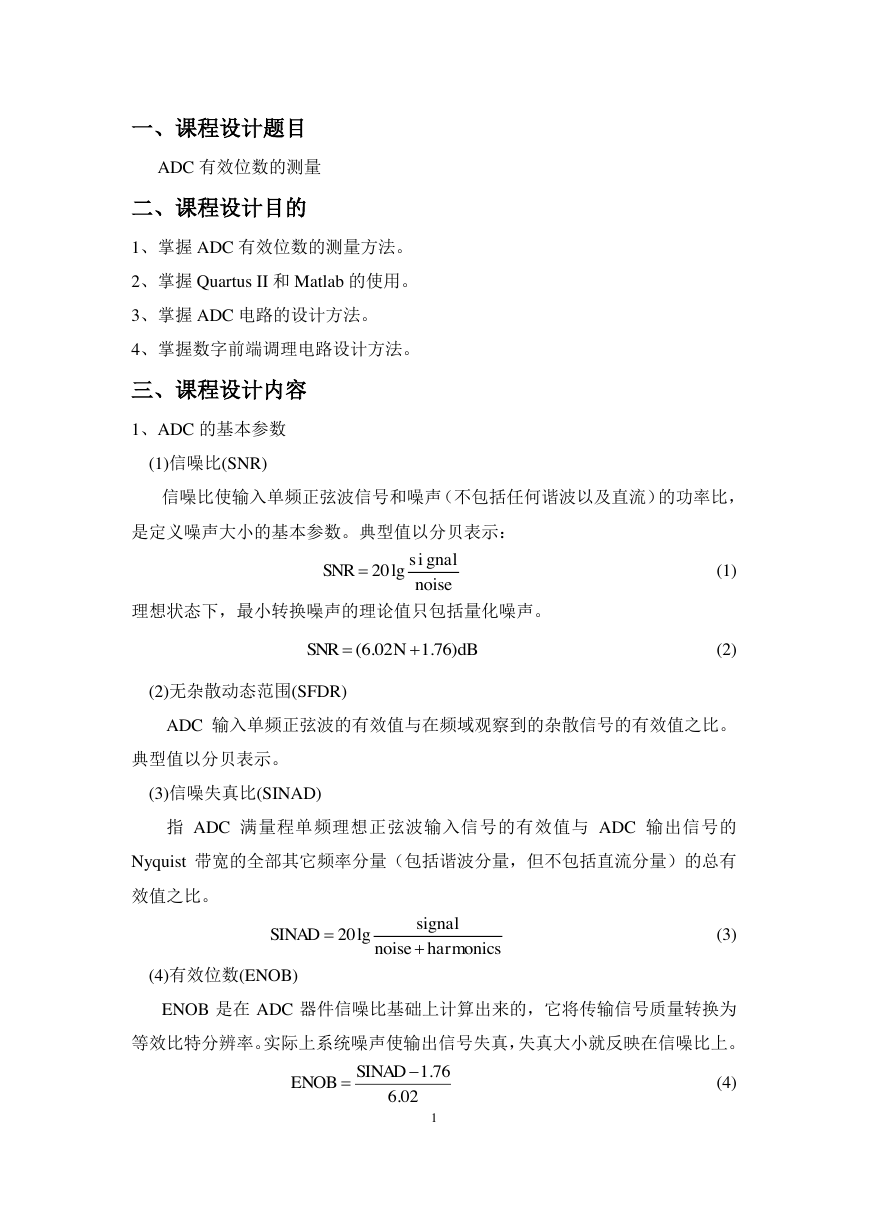

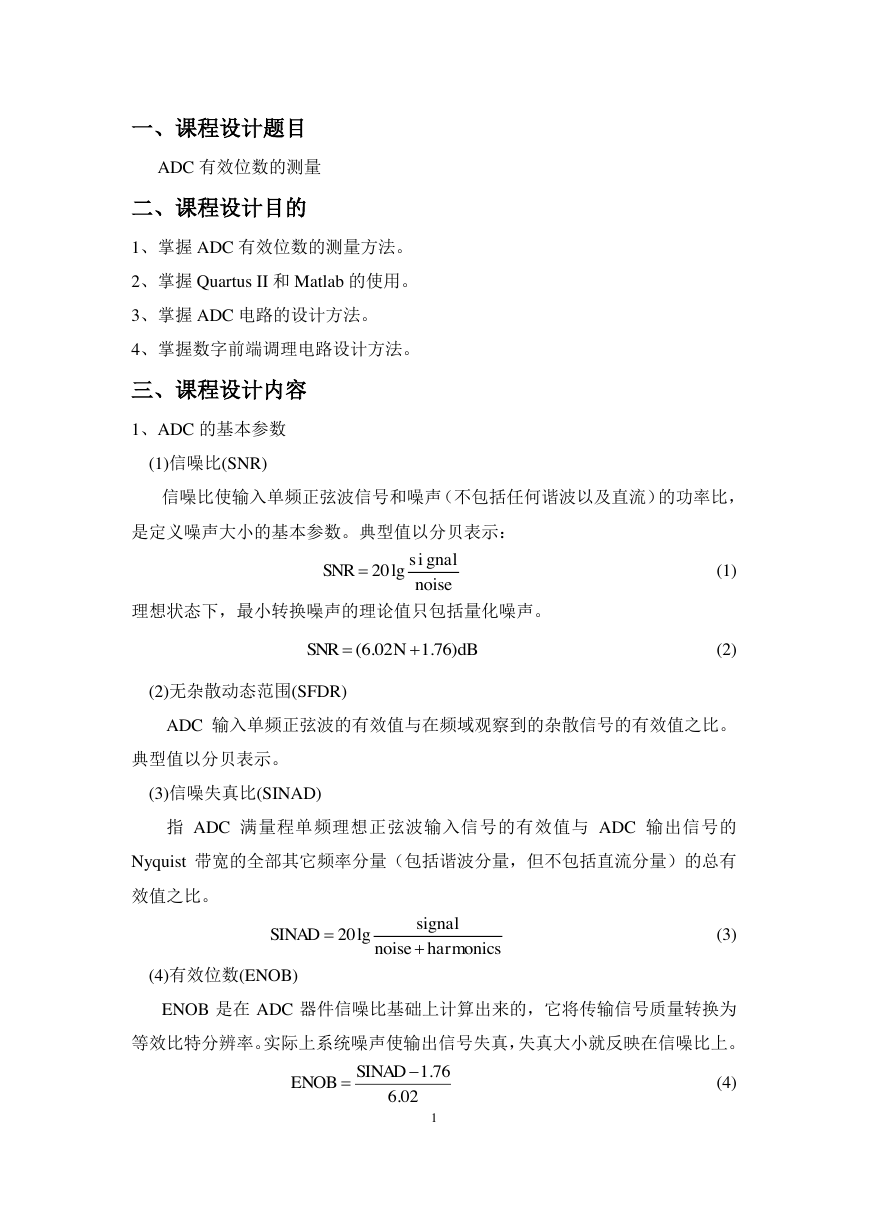

(4) 调理电路基本方案

图 1 电路方案

基本电路方案如图 1 所示,第一级使用 OPA842 进行跟随,第二级采用

THS3201 三级运算放大电路,第三极用 OPA842 做-3dB 截止频率为 10MHz 的低

通滤波器。

4、 电路仿真

仿真平台为美国德州仪器公司的 TI-TINA。

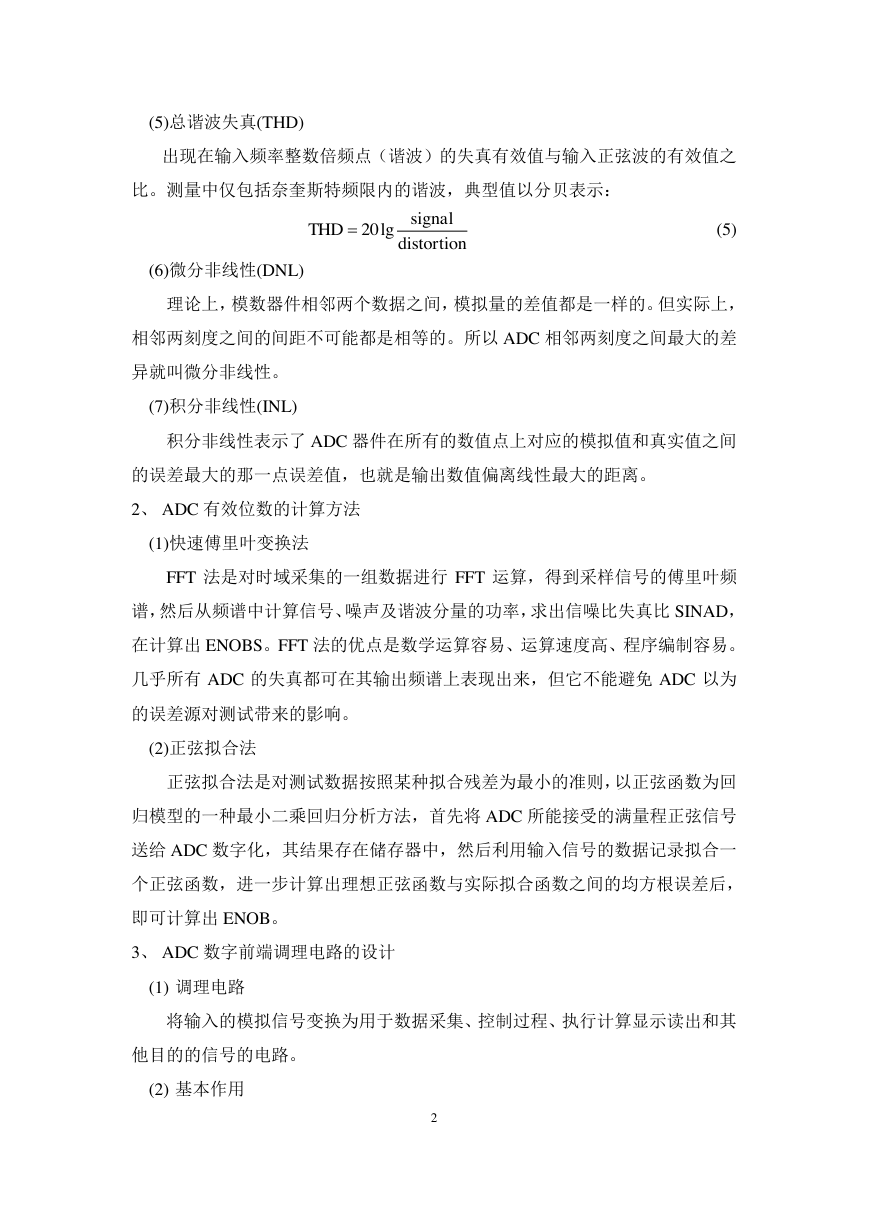

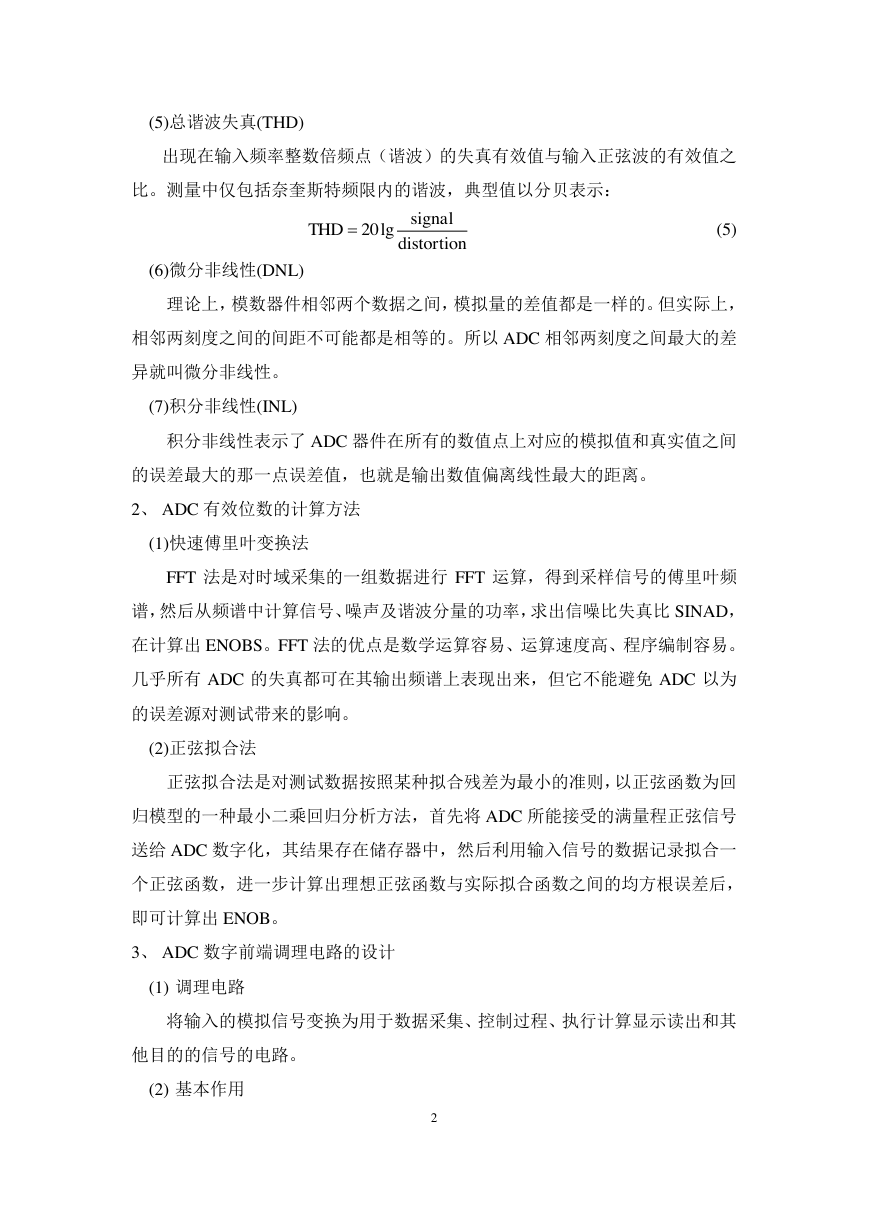

(1) 跟随器仿真电路及结果

图 2 跟随器电路

3

跟随器三级放大器低通滤波器-++U1 OPA842+VG1V1 -5V2 5VF1 VF2 R2 50R1 50R3 20�

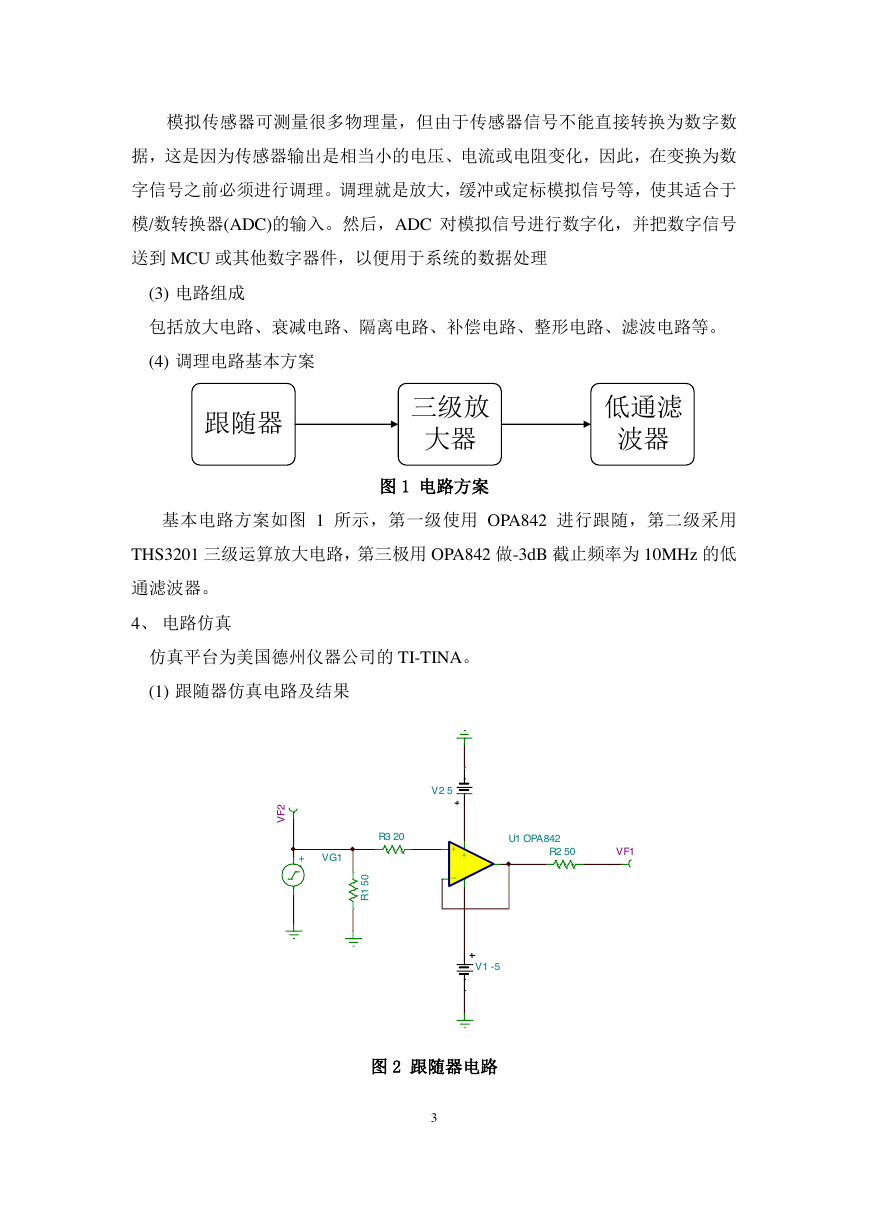

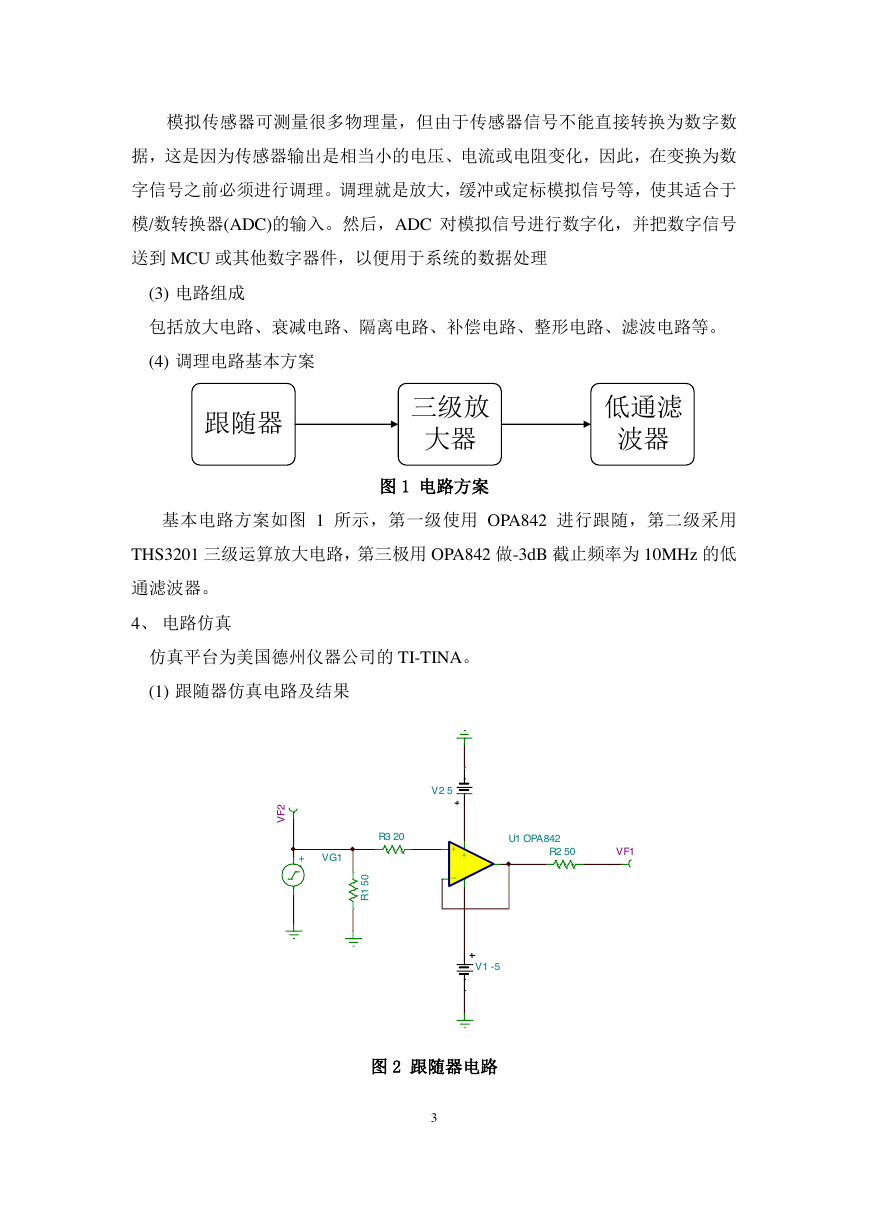

图 3 跟随器幅相频特性曲线

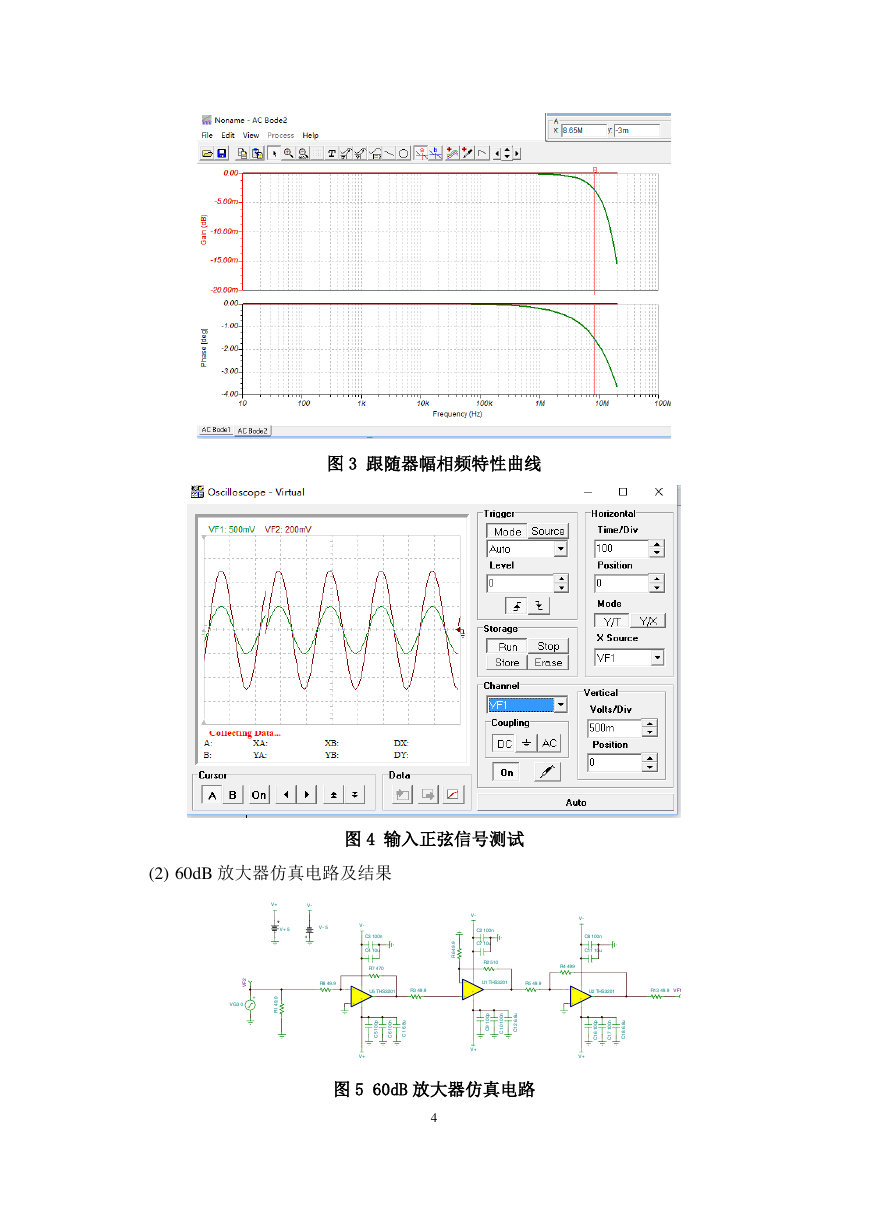

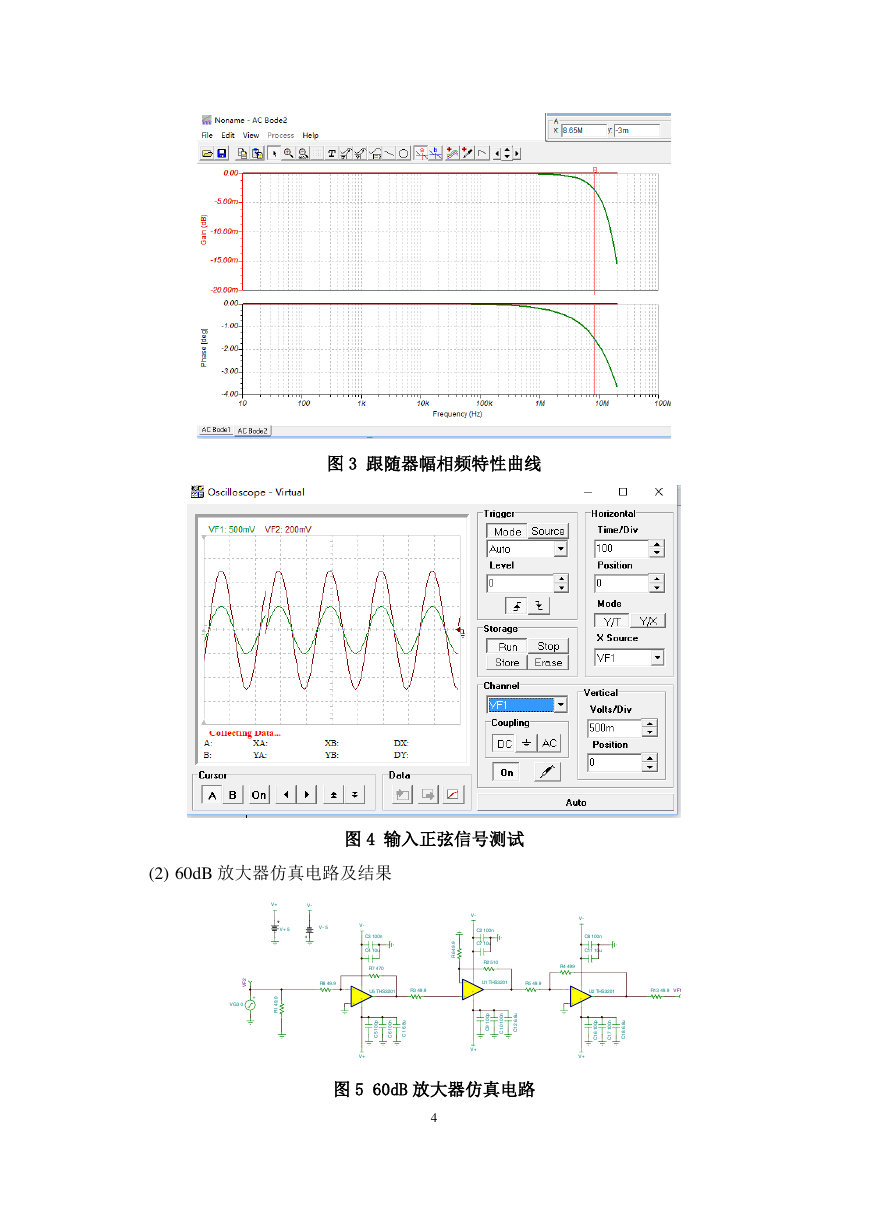

图 4 输入正弦信号测试

(2) 60dB 放大器仿真电路及结果

图 5 60dB 放大器仿真电路

4

V+V-V+V-V+V-V-V+V- 5V+ 5R7 470R8 49.9-++U5 THS3201C3 100nC5 100pC6 100nC1 6.8uR2 510R3 49.9-++U1 THS3201C9 100pC10 100nC12 6.8uR4 499R5 49.9-++U2 THS3201C16 100pC17 100nC18 6.8u+VG3 0R13 49.9VF2 R1 49.9VF1 C4 10uC2 100nC7 10uC8 100nC11 10uR6 49.9�

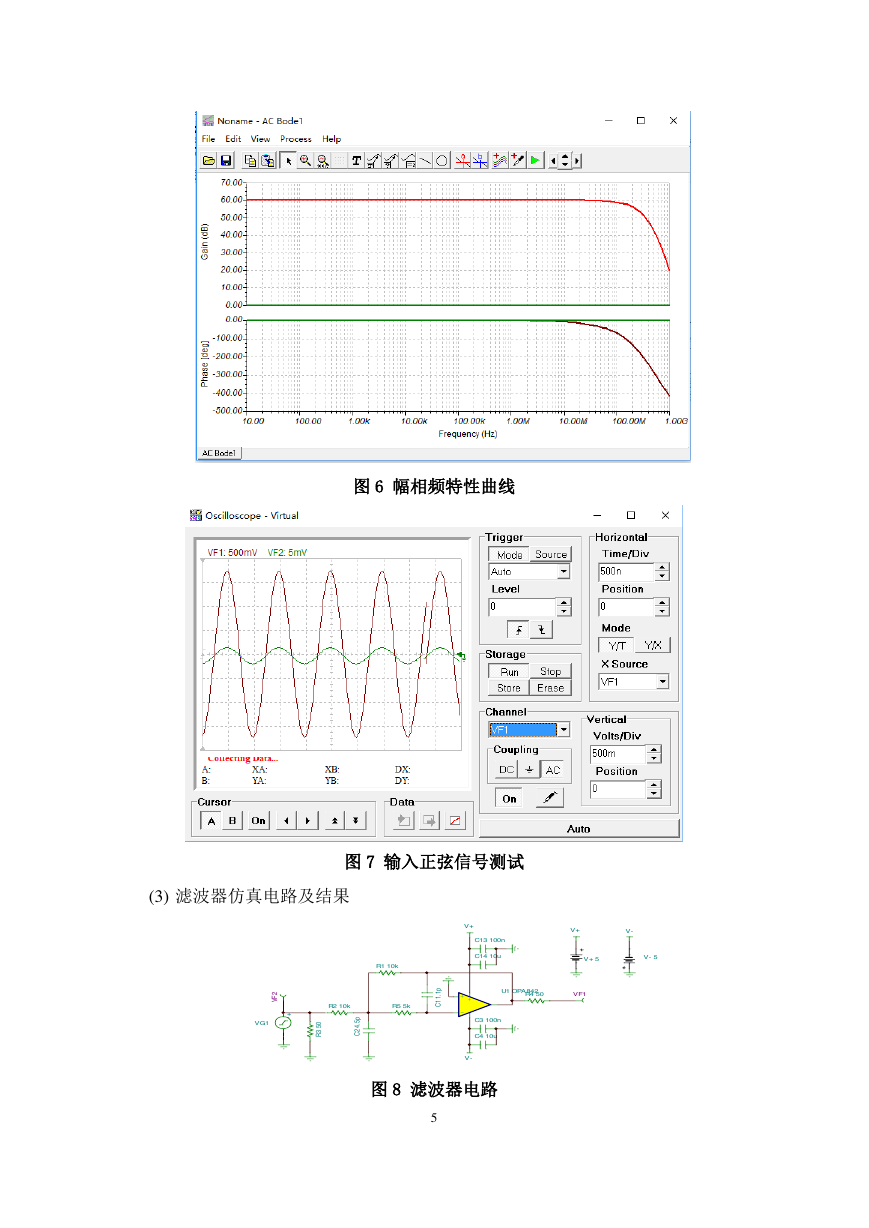

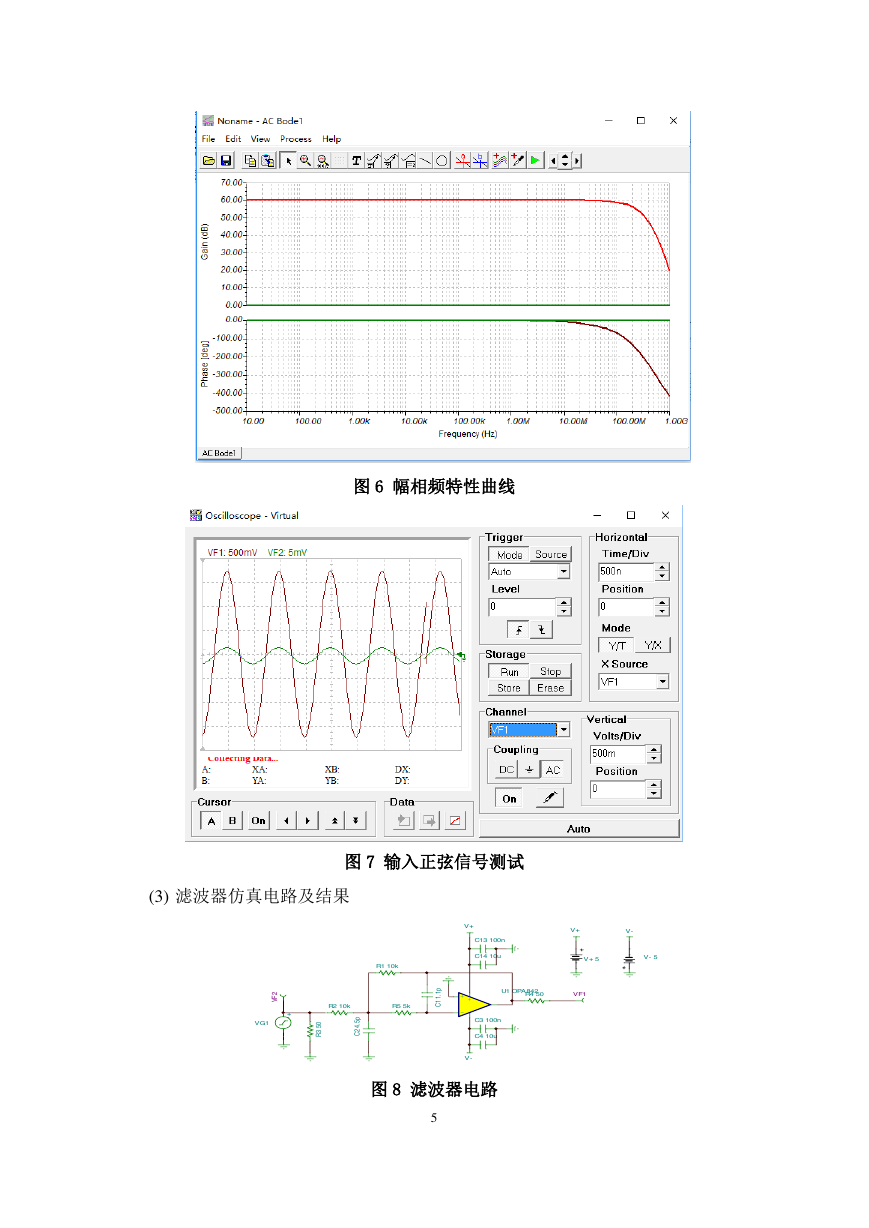

图 6 幅相频特性曲线

图 7 输入正弦信号测试

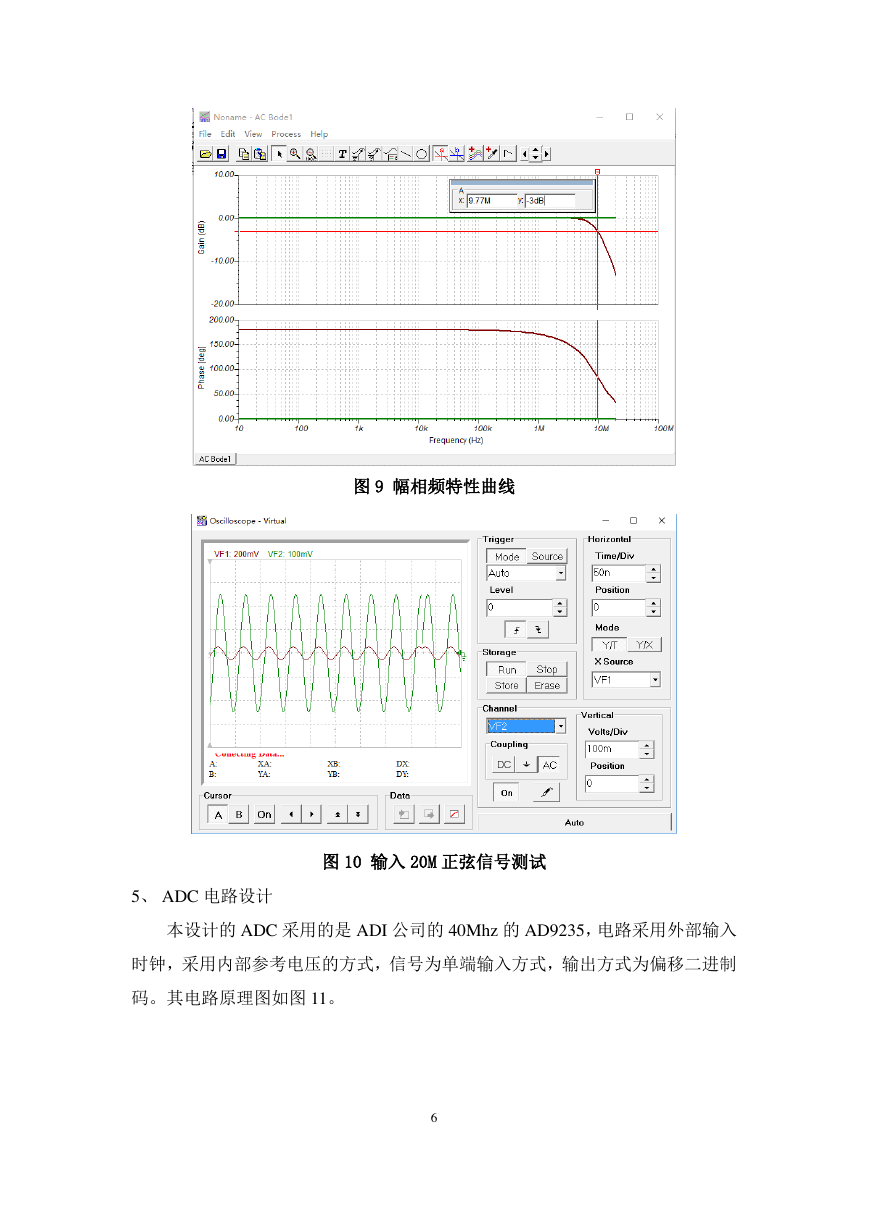

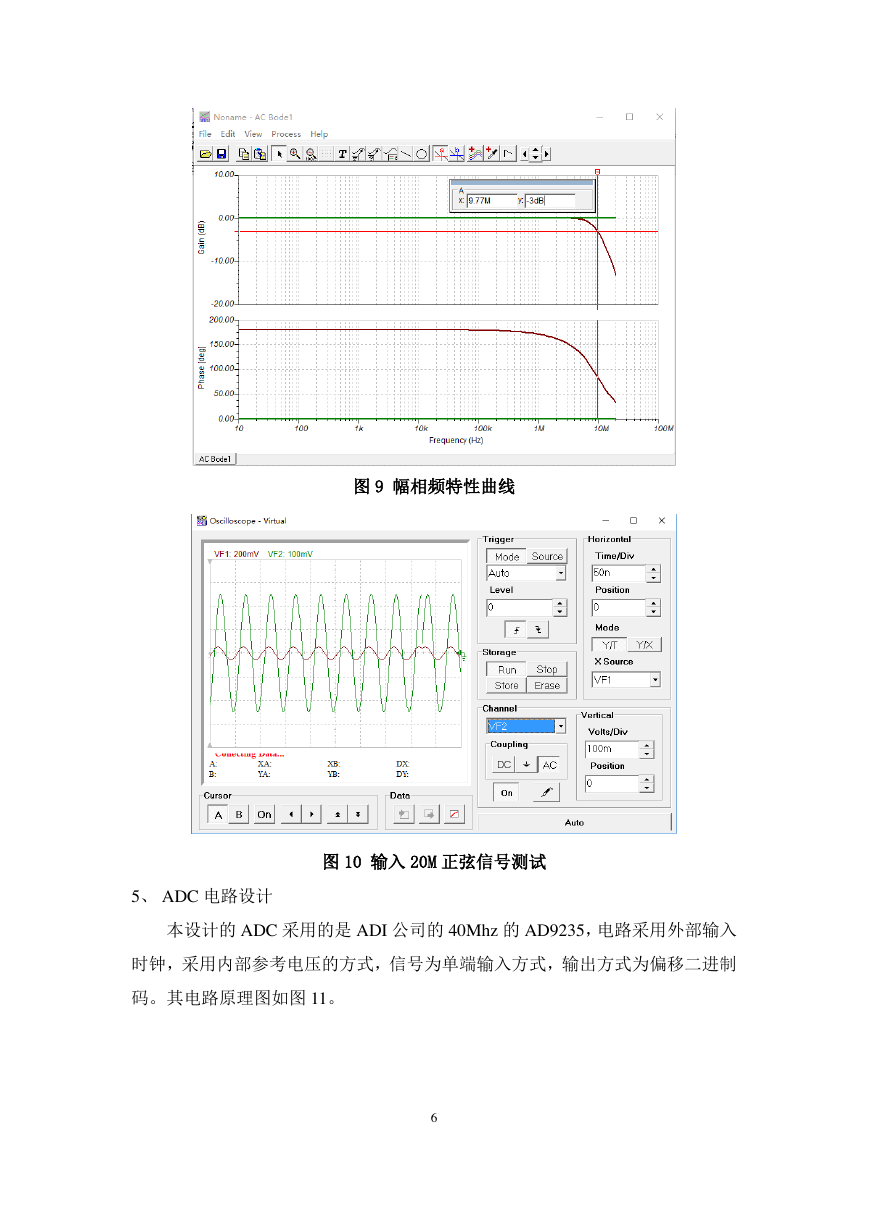

(3) 滤波器仿真电路及结果

图 8 滤波器电路

5

V-V+V-V+-++U1 OPA842R1 10kR2 10kC2 4.5p+VG1VF2 R3 50R4 50VF1 R5 5kC1 1.1pC13 100nC14 10uC3 100nC4 10uV- 5V+ 5�

图 9 幅相频特性曲线

图 10 输入 20M 正弦信号测试

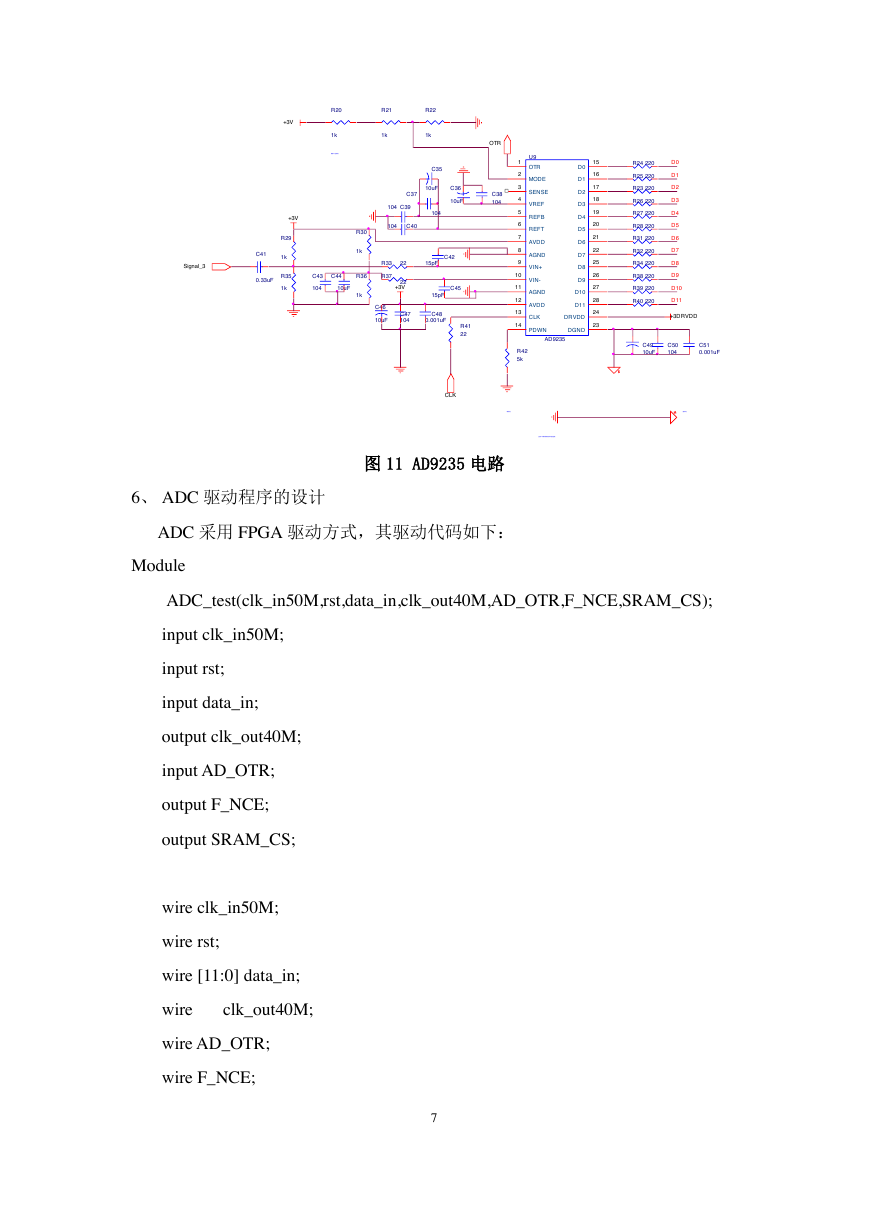

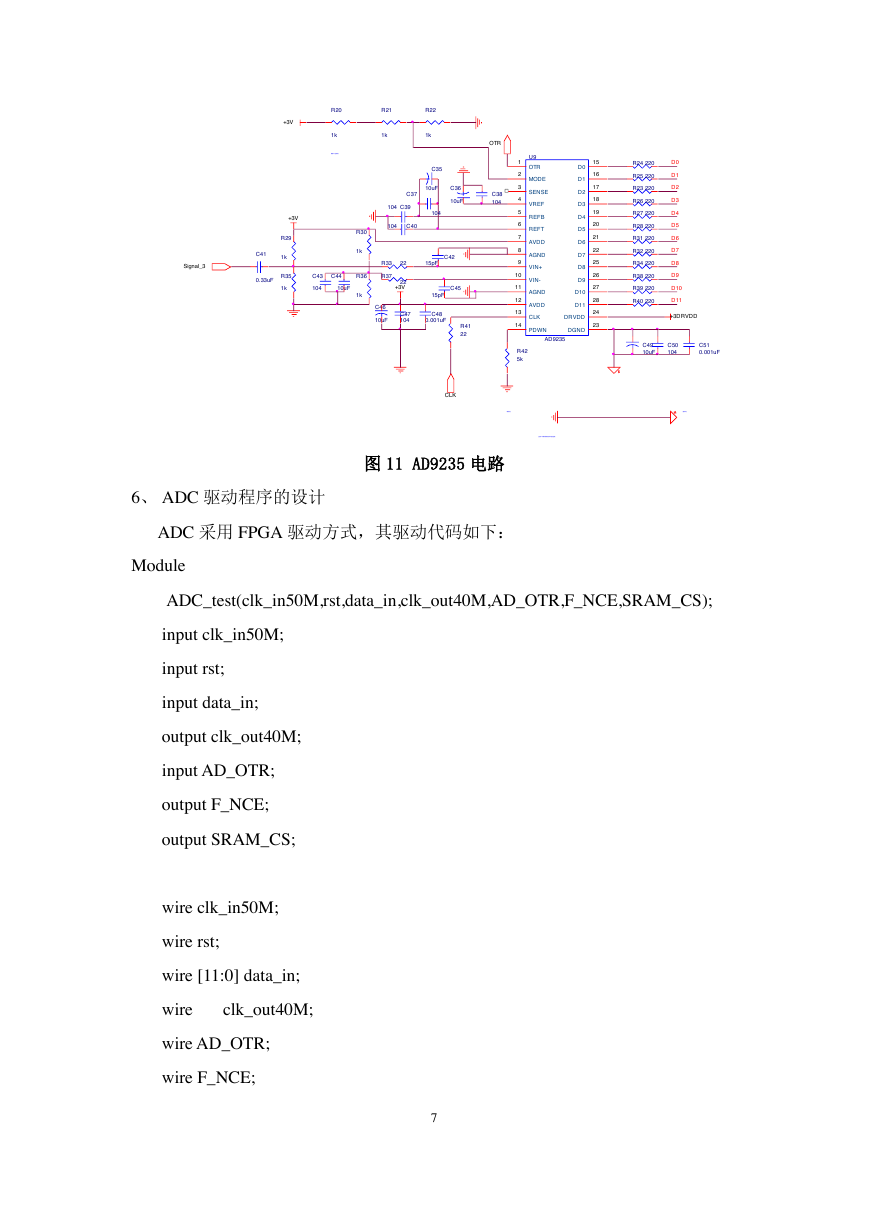

5、 ADC 电路设计

本设计的 ADC 采用的是 ADI 公司的 40Mhz 的 AD9235,电路采用外部输入

时钟,采用内部参考电压的方式,信号为单端输入方式,输出方式为偏移二进制

码。其电路原理图如图 11。

6

�

图 11 AD9235 电路

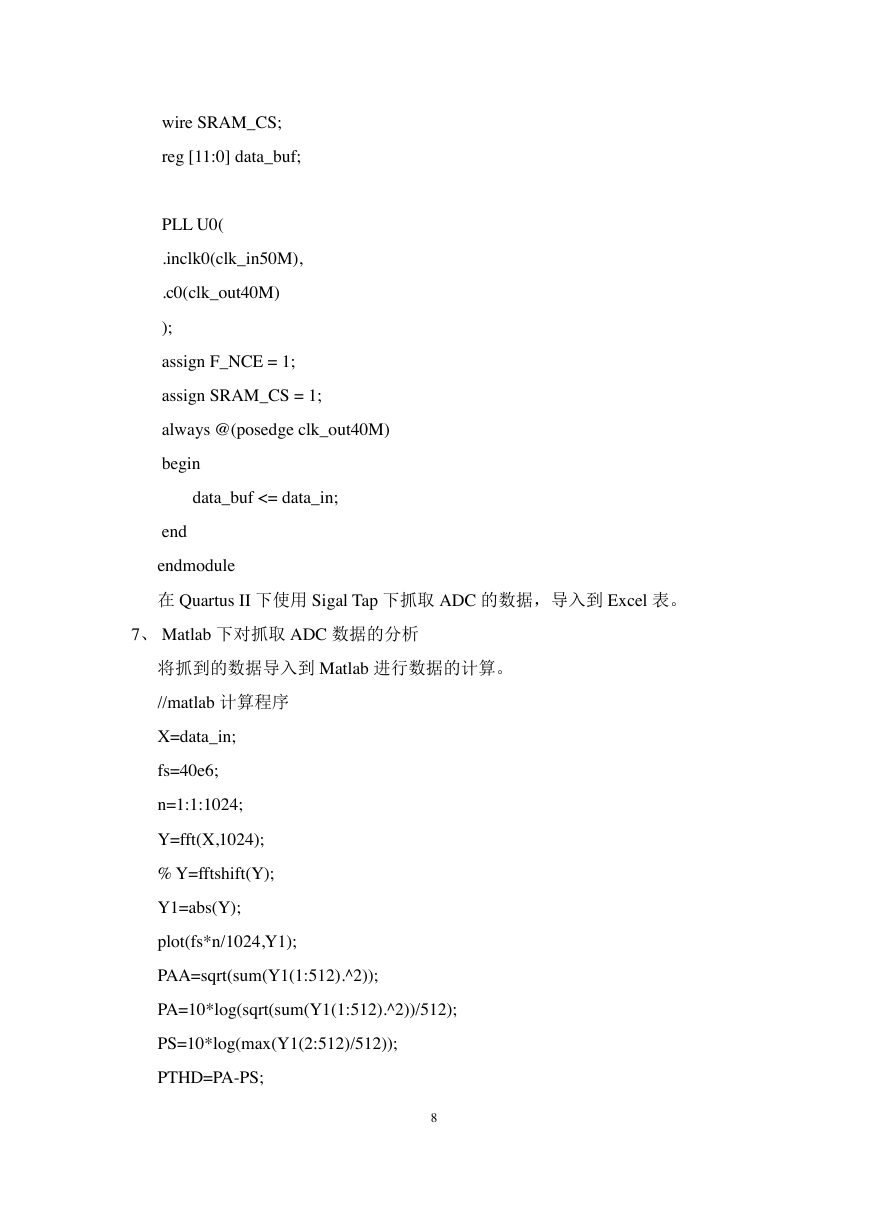

6、 ADC 驱动程序的设计

ADC 采用 FPGA 驱动方式,其驱动代码如下:

Module

ADC_test(clk_in50M,rst,data_in,clk_out40M,AD_OTR,F_NCE,SRAM_CS);

input clk_in50M;

input rst;

input data_in;

output clk_out40M;

input AD_OTR;

output F_NCE;

output SRAM_CS;

wire clk_in50M;

wire rst;

wire [11:0] data_in;

wire

clk_out40M;

wire AD_OTR;

wire F_NCE;

7

+3DRVDDC3510uFC3610uFC38104+3VR201kR211kR221k偏移二进制码CLKC4910uFC50104C510.001uFR425kR24220R25220R23220R26220R27220R28220R31220R32220R34220R38220R39220R40220D2D1D0D6D5D4D3D10D9D8D7D11AD9235U9OTR1MODE2SENSE3VREF4REFB5REFT6AVDD7AGND8VIN+9VIN-10AGND11AVDD12CLK13PDWN14D015D116D217D318D419D520D621D722DGND23DRVDD24D825D926D1027D1128模拟地数字地C4610uFC47104C480.001uFR4122R3322C4215pFR291kR351kSignal_3C410.33uF+3VR3722C4515pFR301kR361k+3VC4410uFC43104注意PCB模拟地和数字地的连接C39104C40104C37104OTR�

wire SRAM_CS;

reg [11:0] data_buf;

PLL U0(

.inclk0(clk_in50M),

.c0(clk_out40M)

);

assign F_NCE = 1;

assign SRAM_CS = 1;

always @(posedge clk_out40M)

begin

data_buf <= data_in;

end

endmodule

在 Quartus II 下使用 Sigal Tap 下抓取 ADC 的数据,导入到 Excel 表。

7、 Matlab 下对抓取 ADC 数据的分析

将抓到的数据导入到 Matlab 进行数据的计算。

//matlab 计算程序

X=data_in;

fs=40e6;

n=1:1:1024;

Y=fft(X,1024);

% Y=fftshift(Y);

Y1=abs(Y);

plot(fs*n/1024,Y1);

PAA=sqrt(sum(Y1(1:512).^2));

PA=10*log(sqrt(sum(Y1(1:512).^2))/512);

PS=10*log(max(Y1(2:512)/512));

PTHD=PA-PS;

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc