S5P4418

Important Notice

Trademarks

Chip Handling Guide

Revision History

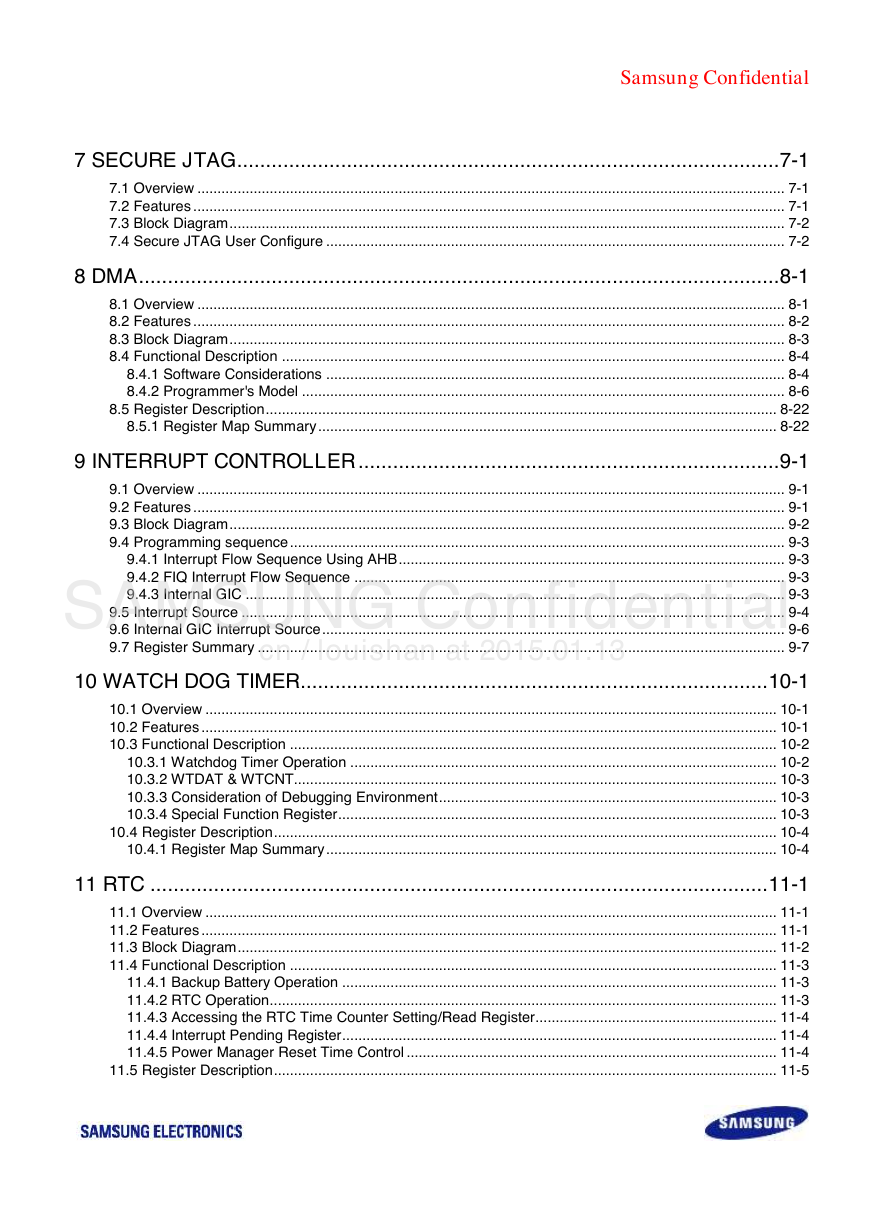

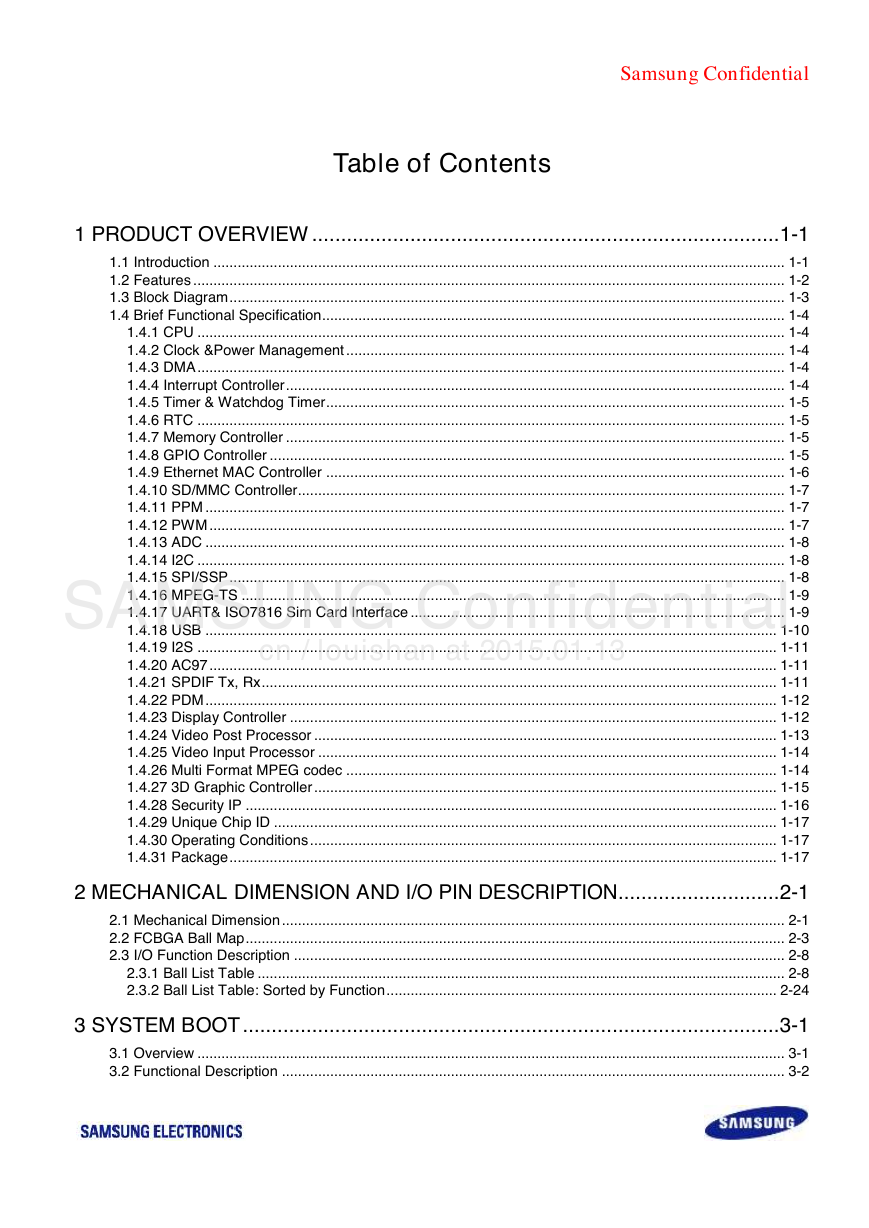

Table of Contents

List of Figures

List of Tables

List of Examples

List of Conventions

List of Acronyms

1 Product Overview

1.1 Introduction

1.2 Features

1.3 Block Diagram

1.4 Brief Functional Specification

1.4.1 CPU

1.4.2 Clock &Power Management

1.4.3 DMA

1.4.4 Interrupt Controller

1.4.5 Timer & Watchdog Timer

1.4.6 RTC

1.4.7 Memory Controller

1.4.8 GPIO Controller

1.4.9 Ethernet MAC Controller

1.4.10 SD/MMC Controller

1.4.11 PPM

1.4.12 PWM

1.4.13 ADC

1.4.14 I2C

1.4.15 SPI/SSP

1.4.16 MPEG-TS

1.4.17 UART& ISO7816 Sim Card Interface

1.4.18 USB

1.4.19 I2S

1.4.20 AC97

1.4.21 SPDIF Tx, Rx

1.4.22 PDM

1.4.23 Display Controller

1.4.24 Video Post Processor

1.4.25 Video Input Processor

1.4.26 Multi Format MPEG codec

1.4.27 3D Graphic Controller

1.4.28 Security IP

1.4.29 Unique Chip ID

1.4.30 Operating Conditions

1.4.31 Package

2 Mechanical Dimension and I/O Pin Description

2.1 Mechanical Dimension

2.2 FCBGA Ball Map

2.3 I/O Function Description

2.3.1 Ball List Table

2.3.2 Ball List Table: Sorted by Function

2.3.2.1 MCU-A

2.3.2.2 MCU-S

2.3.2.3 Digital RGB

2.3.2.4 HDMI

2.3.2.5 LVDS

2.3.2.6 MIPI DSI

2.3.2.7 MIPI CSI

2.3.2.8 VIP

2.3.2.9 Ethernet MAC

2.3.2.10 MPEG-TS Interface

2.3.2.11 UART_ISO7816

2.3.2.12 I2C

2.3.2.13 SPI/SSP

2.3.2.14 PWM

2.3.2.15 PPM

2.3.2.16 PDM

2.3.2.17 SPDIF

2.3.2.18 SD/MMC

2.3.2.19 USB2.0 HOST

2.3.2.20 USB2.0 HSIC HOST

2.3.2.21 USB2.0 OTG

2.3.2.22 I2S& AC97

2.3.2.23 ADC

2.3.2.24 ALIVE GPIO

2.3.2.25 JTAG

2.3.2.26 Crystal PLL & RTC

2.3.2.27 Miscellaneous

2.3.2.28 Power: VDD

2.3.2.29 Power: GND

3 System Boot

3.1 Overview

3.2 Functional Description

3.2.1 System Configuration

3.3 External Static Memory Boot

3.3.1 External Static Memory Boot Features

3.3.2 External Static Memory Boot System Configuration

3.3.3 External Static Memory Boot Operation

3.4 Internal ROM Boot

3.4.1 Features

3.4.2 System Configuration for the Internal ROM booting

3.4.3 USB BOOT

3.4.3.1 Features

3.4.3.2 Operation

3.4.3.3 USB Descriptors

3.4.4 SDHCBOOT

3.4.4.1 Features

3.4.4.2 Operation

3.4.5 NANDBOOT with Error Correction

3.4.5.1 Features

3.4.5.2 Operation

3.4.5.3 How to Store User Boot code into the NAND Flash Memory

3.4.6 Additional Information

3.4.6.1 ALIVE POWER Control

3.4.6.2 Exception Vector Redirection

3.4.6.3 Parity Generation for Error Correction

3.4.6.4 CRC32 Error Check

3.4.6.5 Data Decryption with AES128 ECB Mode to Use Hidden Key

4 System Control

4.1 Overview

4.2 Features

4.3 Block Diagram

4.4 Functional Description

4.4.1 PLL (Phase Locked Loop)

4.4.1.1 PMS Value

4.4.1.2 Setting Guide of SSCG_EN, SEL_PF, MFR and MRR

4.4.1.3 PDIV/MDIV/SDIV Values for PLL0, PLL1

4.4.1.4 PDIV/MDIV/SDIV Values for PLL2, PLL3

4.4.1.5 PLL Power Down

4.4.2 Change PLL Value

4.4.3 Clock Generator

4.4.3.1 Clocks Summary

4.4.3.2 CPU0 Clock

4.4.3.3 System Bus Clock (Core clock)

4.4.3.4 Memory Bus Clock (MCU Clock)

4.4.3.5 GPU (Graphic Processing Unit) clock

4.4.3.6 MFC (Multi-Function Codec) clock

4.5 Power Manager

4.5.1 Power Manager Overview

4.5.2 Power Down Mode Operation

4.5.2.1 IDLE Mode

4.5.2.2 STOP Mode

4.5.2.3 SLEEP Mode 1, SLEEP Mode 2

4.5.2.4 GPIO as a Wake up Source

4.6 Reset Generation

4.6.1 Power on Reset Sequence

4.6.2 Sleep Mode Wakeup Sequence

4.6.3 Power off Sequence

4.6.4 Software Reset and GPIO Reset

4.6.5 Watchdog Reset

4.6.5.1 nPORST, Software Reset, Watchdog Reset and GPIO Reset

4.7 Tie Off

4.8 AXI BUS

4.8.1 Programmable Quality of Service (ProgQoS)

4.8.2 Arbitration scheme

4.8.2.1 RR schemes

4.9 Register Description

4.9.1 Register Map Summary

4.9.1.1 Clock/Power Manager/Boot

4.9.1.1.1 CLKMODEREG0

4.9.1.1.2 CLKMODEREG1

4.9.1.1.3 PLLSETREG0

4.9.1.1.4 PLLSETREG1

4.9.1.1.5 PLLSETREG2

4.9.1.1.6 PLLSETREG3

4.9.1.1.7 CLKDIVREG0

4.9.1.1.8 CLKDIVREG1

4.9.1.1.9 CLKDIVREG2

4.9.1.1.10 CLKDIVREG3

4.9.1.1.11 CLKDIVREG4

4.9.1.1.12 PLLSETREG0_SSCG

4.9.1.1.13 PLLSETREG1_SSCG

4.9.1.1.14 PLLSETREG2_SSCG

4.9.1.1.15 PLLSETREG3_SSCG

4.9.1.1.16 GPIOWAKEUPRISEENB

4.9.1.1.17 GPIOWAKEUPFALLENB

4.9.1.1.18 GPIORSTENB

4.9.1.1.19 GPIOWKENB

4.9.1.1.20 INTENB

4.9.1.1.21 GPIOINTPEND

4.9.1.1.22 RESETSTATUS

4.9.1.1.23 INTENABLE

4.9.1.1.24 INTPEND

4.9.1.1.25 PWRCONT

4.9.1.1.26 PWRMODE

4.9.1.1.27 PADSTRENGTHGPIOAL

4.9.1.1.28 SYSRSTCONFIG

4.9.1.2 Tie Off

4.9.1.2.1 TIEOFFREG00

4.9.1.2.2 TIEOFFREG01

4.9.1.2.3 TIEOFFREG02

4.9.1.2.4 TIEOFFREG03

4.9.1.2.5 TIEOFFREG04

4.9.1.2.6 TIEOFFREG05

4.9.1.2.7 TIEOFFREG06

4.9.1.2.8 TIEOFFREG07

4.9.1.2.9 TIEOFFREG08

4.9.1.2.10 TIEOFFREG09

4.9.1.2.11 TIEOFFREG10

4.9.1.2.12 TIEOFFREG11

4.9.1.2.13 TIEOFFREG12

4.9.1.2.14 TIEOFFREG13

4.9.1.2.15 TIEOFFREG14

4.9.1.2.16 TIEOFFREG15

4.9.1.2.17 TIEOFFREG16

4.9.1.2.18 TIEOFFREG17

4.9.1.2.19 TIEOFFREG18

4.9.1.2.20 TIEOFFREG19

4.9.1.2.21 TIEOFFREG20

4.9.1.2.22 TIEOFFREG21

4.9.1.2.23 TIEOFFREG22

4.9.1.2.24 TIEOFFREG23

4.9.1.2.25 TIEOFFREG24

4.9.1.2.26 TIEOFFREG25

4.9.1.2.27 TIEOFFREG26

4.9.1.2.28 TIEOFFREG27

4.9.1.2.29 TIEOFFREG28

4.9.1.2.30 TIEOFFREG29

4.9.1.2.31 TIEOFFREG30

4.9.1.2.32 TIEOFFREG31

4.9.1.2.33 TIEOFFREG32

4.9.1.3 IP Reset

4.9.1.3.1 IP RESET REGISTER 0

4.9.1.3.2 IP RESET REGISTER 1

4.9.1.3.3 IP RESET REGISTER 2

4.9.1.4 AXI BUS

4.9.1.4.1 Programmable Quality of Service (ProgQoS)

4.9.1.4.2 Arbitration control

5 Clock Generator

5.1 IP Clock Generator Overview

5.1.1 Clock Generator Level 0

5.1.1.1 Block Diagram

5.1.1.2 Register Map Summary

5.1.1.2.1 CODA960CLKENB

5.1.1.2.2 CRYPTOCLKENB

5.1.1.2.3 I2CCLKENB

5.1.1.2.4 3D GPUCLKENB

5.1.1.2.5 MPEGTSICLKENB

5.1.1.2.6 PDMCLKENB

5.1.1.2.7 SCALERCLKENB

5.1.1.2.8 DEINTERLACECLKENB

5.1.1.2.9 MLCCLKENB

5.1.2 Clock Generator Level 1

5.1.2.1 Block Diagram

5.1.2.2 Register Map Summary

5.1.2.2.1 MIPICSICLKENB

5.1.2.2.2 MIPICSICLKGEN0L

5.1.2.2.3 PPMCLKENB

5.1.2.2.4 PPMCLKGEN0L

5.1.2.2.5 PWMTIMERCLKENB

5.1.2.2.6 PWMTIMERCLKGEN0L

5.1.2.2.7 SDMMCCLKENB

5.1.2.2.8 SDMMCCLKGEN0L

5.1.2.2.9 SPDIFTXCLKENB

5.1.2.2.10 SPDIFTXCLKGEN0L

5.1.2.2.11 SSPCLKENB

5.1.2.2.12 SSPCLKGEN0L

5.1.2.2.13 UARTCLKENB

5.1.2.2.14 UARTCLKGEN0L

5.1.2.2.15 VIPCLKENB

5.1.2.2.16 VIPCLKGEN0L

5.1.3 Clock Generator Level 2

5.1.3.1 Block Diagram

5.1.3.2 Register Map Summary

5.1.3.2.1 GMACCLKENB

5.1.3.2.2 GMACCLKGEN0L

5.1.3.2.3 GMACCLKGEN1L

5.1.3.2.4 I2SCLKENB

5.1.3.2.5 I2SCLKGEN0L

5.1.3.2.6 I2SCLKGEN1L

5.1.3.2.7 USBHOSTOTGCLKENB

5.1.3.2.8 USBHOSTOTGCLKGEN0L

5.1.3.2.9 USBHOSTOTGCLKGEN1L

5.1.3.2.10 DPCCLKENB

5.1.3.2.11 DPCCLKGEN0L

5.1.3.2.12 DPCCLKGEN1L

5.1.3.2.13 LVDSCLKENB

5.1.3.2.14 LVDSCLKGEN0L

5.1.3.2.15 LVDSCLKGEN1L

5.1.3.2.16 HDMICLKENB

5.1.3.2.17 HDMICLKGEN0L

5.1.3.2.18 HDMICLKGEN1L

5.1.3.2.19 MIPIDSICLKENB

5.1.3.2.20 MIPIDSICLKGEN0L

5.1.3.2.21 MIPIDSICLKGEN1L

6 System L2 Cache (PL-310 L2C)

6.1 Overview

6.2 Features

6.3 Block Diagram

6.4 Functional Description

6.4.1 L2 Cache User Configure

6.4.2 Initialization Sequence

6.5 Register Description

6.5.1.1 Register Map Summary

6.5.1.1.1 REG0_CACHE_ID

6.5.1.1.2 REG0_CACHE_TYPE

6.5.1.1.3 REG1_CONTROL

6.5.1.1.4 AUX_CONTROL

6.5.1.1.5 REG1_TAG_RAM_CONTROL/ REG1_DATA_RAM_CONTROL

6.5.1.1.6 REG2_EV_COUNTER_CTRL

6.5.1.1.7 REG2_EV_COUNTER1_CFG/ REG2_EV_COUNTER0_CFG

6.5.1.1.8 REG2_EV_COUNTER1/ REG2_EV_COUNTER0

6.5.1.1.9 REG2_INT_MASK

6.5.1.1.10 REG2_INT_MASK_STATUS

6.5.1.1.11 REG2_INT_RAW_STATUS

6.5.1.1.12 REG2_INT_CLEAR

6.5.1.1.13 REG7_CACHE_SYNC

6.5.1.1.14 REG7_INV_PA

6.5.1.1.15 REG7_INV_WAY

6.5.1.1.16 REG7_CLEAN_PA

6.5.1.1.17 REG7_CLEAN_INDEX

6.5.1.1.18 REG7_CLEAN_WAY

6.5.1.1.19 REG7_CLEAN_INV_PA

6.5.1.1.20 REG7_CLEAN_INV_INDEX

6.5.1.1.21 REG7_CLEAN_INV_WAY

6.5.1.1.22 REG9_D_LOCKDOWN 0~7

6.5.1.1.23 REG9_I_LOCKDOWN 0~7

6.5.1.1.24 REG9_LOCK_LINE_EN

6.5.1.1.25 REG9_UNLOCK_WAY

6.5.1.1.26 REG12_ADDR_FILTERING_START

6.5.1.1.27 REG12_ADDR_FILTERING_END

6.5.1.1.28 REG15_DEBUG_CTRL

6.5.1.1.29 REG15_PREFETCH_CTRL

6.5.1.1.30 REG15_POWER_CTRL

7 Secure JTAG

7.1 Overview

7.2 Features

7.3 Block Diagram

7.4 Secure JTAG User Configure

8 DMA

8.1 Overview

8.2 Features

8.3 Block Diagram

8.4 Functional Description

8.4.1 Software Considerations

8.4.2 Programmer's Model

8.4.2.1 About the programmer's Model

8.4.2.2 Programming the DMAC

8.4.2.3 Register Name Description

8.4.2.4 Peripheral DMA Request ID

8.4.2.5 Address Generation

8.4.2.6 Scatter/gather

8.4.2.7 Interrupt requests

8.4.2.8 DMAC Data Flow

8.5 Register Description

8.5.1 Register Map Summary

8.5.1.1 Interrupt Status Register

8.5.1.2 Interrupt Terminal Count Status Register

8.5.1.3 Interrupt Terminal Count Clear Register

8.5.1.4 Interrupt Error Status Register

8.5.1.5 Interrupt Error Clear Register

8.5.1.6 Raw Interrupt Terminal Count Status Register

8.5.1.7 Raw Error Interrupt Status Register

8.5.1.8 Enabled Channel Register

8.5.1.9 Software Burst Request Register

8.5.1.10 Software Single Request Register

8.5.1.11 Software Last Burst Request Register

8.5.1.12 Software Last Single Request Register

8.5.1.13 Configuration Register

8.5.1.14 Synchronization Register

8.5.1.15 Channel Source Address Registers_n (n = 0 to 7)

8.5.1.16 Channel Destination Address Registers_n (n = 0 to 7)

8.5.1.17 Channel Linked List Item Registers_n (n = 0 to 7)

8.5.1.18 Channel Control Registers_n (n = 0 to 7)

8.5.1.19 Channel Configuration Registers_n (n = 0 to 7)

9 Interrupt Controller

9.1 Overview

9.2 Features

9.3 Block Diagram

9.4 Programming sequence

9.4.1 Interrupt Flow Sequence Using AHB

9.4.2 FIQ Interrupt Flow Sequence

9.4.3 Internal GIC

9.5 Interrupt Source

9.6 Internal GIC Interrupt Source

9.7 Register Summary

9.7.1.1 VICIRQSTATUS

9.7.1.2 VICFIQSTATUS

9.7.1.3 VICRAWINTR

9.7.1.4 VICINTSELECT

9.7.1.5 VICINTENABLE

9.7.1.6 VICINTENCLEAR

9.7.1.7 VICSOFTINT

9.7.1.8 VICSOFTINTCLEAR

9.7.1.9 VICPROTECTION

9.7.1.10 VICSWPRIORITYMASK

9.7.1.11 VICVECTPRIORITYDAISY

9.7.1.12 VICVECTADDR0

9.7.1.13 VICVECTADDR1

9.7.1.14 VICVECTADDR2

9.7.1.15 VICVECTADDR3

9.7.1.16 VICVECTADDR4

9.7.1.17 VICVECTADDR5

9.7.1.18 VICVECTADDR6

9.7.1.19 VICVECTADDR7

9.7.1.20 VICVECTADDR8

9.7.1.21 VICVECTADDR9

9.7.1.22 VICVECTADDR10

9.7.1.23 VICVECTADDR11

9.7.1.24 VICVECTADDR12

9.7.1.25 VICVECTADDR13

9.7.1.26 VICVECTADDR14

9.7.1.27 VICVECTADDR15

9.7.1.28 VICVECTADDR16

9.7.1.29 VICVECTADDR17

9.7.1.30 VICVECTADDR18

9.7.1.31 VICVECTADDR19

9.7.1.32 VICVECTADDR20

9.7.1.33 VICVECTADDR21

9.7.1.34 VICVECTADDR22

9.7.1.35 VICVECTADDR23

9.7.1.36 VICVECTADDR24

9.7.1.37 VICVECTADDR25

9.7.1.38 VICVECTADDR26

9.7.1.39 VICVECTADDR27

9.7.1.40 VICVECTADDR28

9.7.1.41 VICVECTADDR29

9.7.1.42 VICVECTADDR30

9.7.1.43 VICVECTADDR31

9.7.1.44 VICVECTPRIORITY0

9.7.1.45 VICVECTPRIORITY1

9.7.1.46 VICVECTPRIORITY2

9.7.1.47 VICVECTPRIORITY3

9.7.1.48 VICVECTPRIORITY4

9.7.1.49 VICVECTPRIORITY5

9.7.1.50 VICVECTPRIORITY6

9.7.1.51 VICVECTPRIORITY7

9.7.1.52 VICVECTPRIORITY8

9.7.1.53 VICVECTPRIORITY9

9.7.1.54 VICVECTPRIORITY10

9.7.1.55 VICVECTPRIORITY11

9.7.1.56 VICVECTPRIORITY12

9.7.1.57 VICVECTPRIORITY13

9.7.1.58 VICVECTPRIORITY14

9.7.1.59 VICVECTPRIORITY15

9.7.1.60 VICVECTPRIORITY16

9.7.1.61 VICVECTPRIORITY17

9.7.1.62 VICVECTPRIORITY18

9.7.1.63 VICVECTPRIORITY19

9.7.1.64 VICVECTPRIORITY20

9.7.1.65 VICVECTPRIORITY21

9.7.1.66 VICVECTPRIORITY22

9.7.1.67 VICVECTPRIORITY23

9.7.1.68 VICVECTPRIORITY24

9.7.1.69 VICVECTPRIORITY25

9.7.1.70 VICVECTPRIORITY26

9.7.1.71 VICVECTPRIORITY27

9.7.1.72 VICVECTPRIORITY28

9.7.1.73 VICVECTPRIORITY29

9.7.1.74 VICVECTPRIORITY30

9.7.1.75 VICVECTPRIORITY31

9.7.1.76 VICADDRESS

9.7.1.77 VICPERIPHID0

9.7.1.78 VICPERIPHID1

9.7.1.79 VICPERIPHID2

9.7.1.80 VICPERIPHID3

9.7.1.81 VICPCELLID0

9.7.1.82 VICPCELLID1

9.7.1.83 VICPCELLID2

9.7.1.84 VICPCELLID3

10 Watch Dog Timer

10.1 Overview

10.2 Features

10.3 Functional Description

10.3.1 Watchdog Timer Operation

10.3.2 WTDAT & WTCNT

10.3.3 Consideration of Debugging Environment

10.3.4 Special Function Register

10.3.4.1 Memory map

10.3.4.2 Watchdog Timer Control (WTCON) Register

10.3.4.3 Watchdog Timer Data (WTDAT) Register

10.3.4.4 Watchdog Timer Count (WTCNT) Register

10.3.4.5 Watchdog Timer Interrupt (WTCLRINT) Register

10.4 Register Description

10.4.1 Register Map Summary

10.4.1.1 WTCON

10.4.1.2 WTDAT

10.4.1.3 WTCNT

10.4.1.4 WTCLRINT

11 RTC

11.1 Overview

11.2 Features

11.3 Block Diagram

11.4 Functional Description

11.4.1 Backup Battery Operation

11.4.2 RTC Operation

11.4.3 Accessing the RTC Time Counter Setting/Read Register

11.4.4 Interrupt Pending Register

11.4.5 Power Manager Reset Time Control

11.5 Register Description

11.5.1 Register Map Description

11.5.1.1 RTCCNTWRITE

11.5.1.2 RTCCNTREAD

11.5.1.3 RTCALARM

11.5.1.4 RTCCTRL

11.5.1.5 RTCINTENB

11.5.1.6 RTCINTPND

11.5.1.7 RTCCORERSTIMESEL

11.5.1.8 WTCON

12 Alive

12.1 Overview

12.2 Features

12.3 Power Isolation

12.3.1 Core Power Off

12.3.2 Power Gating

12.4 Alive Registers

12.4.1 Alive GPIO Detect Registers

12.4.2 Scratch Register

12.4.3 Alive GPIO Control Registers

12.5 Momentary Power Control

12.5.1 CoreVDD Powering On

12.5.2 CoreVDD Powering Off

12.6 SLEEP Mode

12.7 PMU (Power management Unit)

12.7.1 Overview

12.7.2 Power Mode Table

12.7.3 Power Switch Control Sequence

12.8 Register Description

12.8.1 Register Map Summary

12.8.1.1 ALIVEPWRGATEREG

12.8.1.2 ALIVEGPIOASYNCDETECTMODERSTREG0

12.8.1.3 ALIVEGPIOASYNCDETECTMODERSTREG1

12.8.1.4 ALIVEGPIOASYNCDETECTMODESETREG0

12.8.1.5 ALIVEGPIOASYNCDETECTMODESETREG1

12.8.1.6 ALIVEGPIOLOWASYNCDETECTMODEREADREG

12.8.1.7 ALIVEGPIOHIGHASYNCDETECTMODEREADREG

12.8.1.8 ALIVEGPIODETECTMODERSTREG0

12.8.1.9 ALIVEGPIODETECTMODERSTREG1

12.8.1.10 ALIVEGPIODETECTMODERSTREG2

12.8.1.11 ALIVEGPIODETECTMODERSTREG3

12.8.1.12 ALIVEGPIODETECTMODESETREG0

12.8.1.13 ALIVEGPIODETECTMODESETREG1

12.8.1.14 ALIVEGPIODETECTMODESETREG2

12.8.1.15 ALIVEGPIODETECTMODESETREG3

12.8.1.16 ALIVEGPIOFALLDETECTMODEREADREG

12.8.1.17 ALIVEGPIORISEDETECTMODEREADREG

12.8.1.18 ALIVEGPIOLOWDETECTMODEREADREG

12.8.1.19 ALIVEGPIOHIGHDETECTMODEREADREG

12.8.1.20 ALIVEGPIODETECTENBRSTREG

12.8.1.21 ALIVEGPIODETECTENBSETREG

12.8.1.22 ALIVEGPIODETECTENBREADREG

12.8.1.23 ALIVEGPIOINTENBRSTREG

12.8.1.24 ALIVEGPIODETECTENABLESETREG

12.8.1.25 ALIVEGPIOINTENBREADREG

12.8.1.26 ALIVEGPIODETECTPENDREG

12.8.1.27 ALIVESCRATCHRSTREG

12.8.1.28 ALIVESCRATCHSETREG

12.8.1.29 ALIVESCRATCHREADREG

12.8.1.30 ALIVEGPIOPADOUTENBRSTREG

12.8.1.31 ALIVEGPIOPADOUTENBSETREG

12.8.1.32 ALIVEGPIOPADOUTENBREADREG

12.8.1.33 ALIVEGPIOPADPULLUPRSTREG

12.8.1.34 ALIVEGPIOPADPULLUPSETREG

12.8.1.35 ALIVEGPIOPADPULLUPREADREG

12.8.1.36 ALIVEGPIOPADOUTRSTREG

12.8.1.37 ALIVEGPIOPADOUTSETREG

12.8.1.38 ALIVEGPIOPADOUTREADREG

12.8.1.39 VDDCTRLRSTREG

12.8.1.40 VDDCTRLSETREG

12.8.1.41 VDDCTRLREADREG

12.8.1.42 ALIVECLEARWAKEUPSTATUSREGISTER

12.8.1.43 ALIVESLEEPWAKEUPSTATUSREGISTER

12.8.1.44 ALIVESCRATCHRSTREG1

12.8.1.45 ALIVESCRATCHRSTREG2

12.8.1.46 ALIVESCRATCHRSTREG3

12.8.1.47 ALIVESCRATCHRSTREG4

12.8.1.48 ALIVESCRATCHRSTREG5

12.8.1.49 ALIVESCRATCHRSTREG6

12.8.1.50 ALIVESCRATCHRSTREG7

12.8.1.51 ALIVESCRATCHRSTREG8

12.8.1.52 ALIVESCRATCHSETREG1

12.8.1.53 ALIVESCRATCHSETREG2

12.8.1.54 ALIVESCRATCHSETREG3

12.8.1.55 ALIVESCRATCHSETREG4

12.8.1.56 ALIVESCRATCHSETREG5

12.8.1.57 ALIVESCRATCHSETREG6

12.8.1.58 ALIVESCRATCHSETREG7

12.8.1.59 ALIVESCRATCHSETREG8

12.8.1.60 ALIVESCRATCHREADREG1

12.8.1.61 ALIVESCRATCHREADREG2

12.8.1.62 ALIVESCRATCHREADREG3

12.8.1.63 ALIVESCRATCHREADREG4

12.8.1.64 ALIVESCRATCHREADREG5

12.8.1.65 ALIVESCRATCHREADREG6

12.8.1.66 ALIVESCRATCHREADREG7

12.8.1.67 ALIVESCRATCHREADREG8

12.8.1.68 VDDOFFDELAYRSTREGISTER

12.8.1.69 VDDOFFDELAYSETREGISTER

12.8.1.70 VDDOFFDELAYVALUEREGISTER

12.8.1.71 VDDOFFDELAYTIMEREGISTER

12.8.1.72 ALIVEGPIOINPUTVALUE

12.8.1.73 PMUNISOLATE

12.8.1.74 PMUNPWRUPPRE

12.8.1.75 PMUNPWRUP

12.8.1.76 PMUNPWRUPACK

13 ID Register

13.1 Overview

13.2 Features

13.3 Functional Description

13.3.1 AC Timing

13.3.2 Sense Mode Timing

13.3.3 Scan-latch Mode Timing

13.3.4 Stand-by Mode Timing

13.3.5 Program Mode Timing

13.4 Register Description

13.4.1 Register Map Summary

13.4.1.1 ECID0

13.4.1.2 ECID1

13.4.1.3 ECID2

13.4.1.4 ECID3

13.4.1.5 CHIP_NAME_03_00

13.4.1.6 CHIP_NAME_07_04

13.4.1.7 CHIP_NAME_11_08

13.4.1.8 CHIP_NAME_15_12

13.4.1.9 CHIP_NAME_19_16

13.4.1.10 CHIP_NAME_23_20

13.4.1.11 CHIP_NAME_27_24

13.4.1.12 CHIP_NAME_31_28

13.4.1.13 CHIP_NAME_35_32

13.4.1.14 CHIP_NAME_39_36

13.4.1.15 CHIP_NAME_43_40

13.4.1.16 CHIP_NAME_47_44

13.4.1.17 GUID0

13.4.1.18 GUID1_2

13.4.1.19 GUID3_0

13.4.1.20 GUID3_1

13.4.1.21 EC0

13.4.1.22 EC1

13.4.1.23 EC2

13.5 Application Notes

14 Memory Controller

14.1 Overview

14.1.1 Unified Memory Architecture (UMA)

14.2 Block Diagram

14.3 Functional Description

14.3.1 MCU-A Bank Feature

14.3.2 MCU-S Bank Feature

14.3.3 Memory Map

14.3.4 MCU-A Address Mapping

14.3.4.1 Linear Mapping

14.3.4.2 Interleaved Mapping

14.3.5 Low Power Operation

14.3.5.1 AXI Low Power Channel

14.3.5.2 Dynamic Power Down

14.3.5.3 Dynamic Self Refresh

14.3.5.4 Clock Stop

14.3.5.5 Direct Command

14.3.6 MCU-A APPLICATION NOTE

14.3.6.1 DREX Initialization

14.3.6.1.1 LPDDR2/3

14.3.6.1.2 DDR3

14.3.6.2 DDRPHY Initialization

14.3.6.2.1 Write Leveling

14.3.6.2.2 CA Calibration

14.3.6.2.3 Gate Leveling

14.3.6.2.4 Read DQ Calibration (=Read Leveling, Read De-skewing)

14.3.6.2.5 Write DQ Calibration (=Write Deskewing)

14.3.7 DLL Lock and ZQ I/O Calibration

14.3.7.1 Static Memory Map Shadow

14.3.7.2 Interface

14.3.8 NAND Overview

14.3.8.1 Normal Access Sequence

14.3.8.2 ECC (BCH)

14.4 Register Description

14.4.1 Register Map Summary

14.4.1.1 DREX Register

14.4.1.1.1 ConControl

14.4.1.1.2 MemControl

14.4.1.1.3 MemConfig0

14.4.1.1.4 MemConfig1

14.4.1.1.5 DirectCmd

14.4.1.1.6 PrechConfig

14.4.1.1.7 PhyControl0

14.4.1.1.8 PwrdnConfig

14.4.1.1.9 TimingPZQ

14.4.1.1.10 TimingAref

14.4.1.1.11 TimingRow

14.4.1.1.12 TimingData

14.4.1.1.13 TimingPower

14.4.1.1.14 PhyStatus

14.4.1.1.15 ChipStatus

14.4.1.1.16 MrStatus

14.4.1.1.17 QosControl n (n = 0 to 15)

14.4.1.1.18 WrTraConfig

14.4.1.1.19 RdlvlConfig

14.4.1.1.20 BRBRSVCONTROL

14.4.1.1.21 BRBRSVCONFIG

14.4.1.1.22 BRBQOSCONFIG

14.4.1.1.23 MemBaseConfig0

14.4.1.1.24 MemBaseConfig1

14.4.1.1.25 WRLVLCONFIG0

14.4.1.1.26 WRLVLCONFIG1

14.4.1.1.27 WRLVLSTATUS

14.4.1.1.28 CTRL_IO_RDATA

14.4.1.1.29 CACAL_CONFIG0

14.4.1.1.30 CACAL_CONFIG1

14.4.1.1.31 CACAL_STATUS

14.4.1.2 DDRPHY Register

14.4.1.2.1 PHY_CON0

14.4.1.2.2 PHY_CON1

14.4.1.2.3 PHY_CON2

14.4.1.2.4 PHY_CON3

14.4.1.2.5 PHY_CON4

14.4.1.2.6 PHY_CON5

14.4.1.2.7 PHY_CON6

14.4.1.2.8 PHY_CON8

14.4.1.2.9 PHY_CON9

14.4.1.2.10 PHY_CON10

14.4.1.2.11 PHY_CON12

14.4.1.2.12 PHY_CON13

14.4.1.2.13 PHY_CON14

14.4.1.2.14 PHY_CON15

14.4.1.2.15 PHY_CON16

14.4.1.2.16 PHY_CON17

14.4.1.2.17 PHY_CON18

14.4.1.2.18 PHY_CON19

14.4.1.2.19 PHY_CON20

14.4.1.2.20 PHY_CON21

14.4.1.2.21 PHY_CON22

14.4.1.2.22 PHY_CON23

14.4.1.2.23 PHY_CON24

14.4.1.2.24 PHY_CON25

14.4.1.2.25 PHY_CON26

14.4.1.2.26 PHY_CON27

14.4.1.2.27 PHY_CON28

14.4.1.2.28 PHY_CON29

14.4.1.2.29 PHY_CON30

14.4.1.2.30 PHY_CON31

14.4.1.2.31 PHY_CON32

14.4.1.2.32 PHY_CON33

14.4.1.2.33 PHY_CON34

14.4.1.2.34 PHY_CON37

14.4.1.2.35 PHY_CON39

14.4.1.2.36 PHY_CON40

14.4.1.2.37 PHY_CON41

14.4.1.2.38 PHY_CON42

14.4.1.3 MCUS Memory Control Register

14.4.1.3.1 MEMBW

14.4.1.3.2 MEMTIMEACSL

14.4.1.3.3 MEMTIMEACSH

14.4.1.3.4 MEMTIMECOSL

14.4.1.3.5 MEMTIMECOSH

14.4.1.3.6 MEMTIMEACC0

14.4.1.3.7 MEMTIMEACC1

14.4.1.3.8 MEMTIMEACC2

14.4.1.3.9 MEMTIMEACC3

14.4.1.3.10 MEMTIMESACC0

14.4.1.3.11 MEMTIMESACC1

14.4.1.3.12 MEMTIMESACC2

14.4.1.3.13 MEMTIMESACC3

14.4.1.3.14 MEMTIMECOHL

14.4.1.3.15 MEMTIMECOHH

14.4.1.3.16 MEMTIMECAHL

14.4.1.3.17 MEMTIMECAHH

14.4.1.3.18 MEMBURSTL

14.4.1.3.19 MEMWAIT

14.4.1.3.20 NFCONTROL

14.4.1.3.21 NFECCTRL

14.4.1.3.22 NFCNT

14.4.1.3.23 NFECCSTATUS

14.4.1.3.24 NFTIMEACS

14.4.1.3.25 NFTIMECOS

14.4.1.3.26 NFTIMEACC0

14.4.1.3.27 NFTIMEOCH

14.4.1.3.28 NFTIMECAH

14.4.1.3.29 NFECCn (n = 0 to 26)

14.4.1.3.30 NFORGECCn (n = 0 to 26)

14.4.1.3.31 NFSYNDROMEn (n = 0 to 29)

14.4.1.3.32 NFELPn (n = 0 to 59)

14.4.1.3.33 NFERRORLOCATIONn (n = 0 to 59)

14.4.1.3.34 AUTO SYNDROM REGISTER(AUTOSYND)

14.4.1.3.35 NFWSYNDRONEn (n = 0 to 29)

14.4.1.4 MCUS Memory Control Register

14.4.1.4.1 NFDATA

14.4.1.4.2 NFCMD

14.4.1.4.3 NFADDR

15 GPIO Controller

15.1 Overview

15.1.1 Features

15.2 Block Diagram

15.3 Functional Description

15.3.1 Input Operation

15.3.2 Output Operation

15.3.3 Alternate Function Operation

15.4 Register Description

15.4.1 Register Map Summary

15.4.1.1 GPIOxOUT

15.4.1.2 GPIOxOUTENB

15.4.1.3 GPIOxDETMODE0

15.4.1.4 GPIOxDETMODE1

15.4.1.5 GPIOxINTENB

15.4.1.6 GPIOxDET

15.4.1.7 GPIOxPAD

15.4.1.8 GPIOxALTFN0

15.4.1.9 GPIOxALTFN1

15.4.1.10 GPIOxDETMODEEX

15.4.1.11 GPIOxDETENB

15.4.1.12 GPIOx_SLEW

15.4.1.13 GPIOx_SLEW_DISABLE_DEFAULT

15.4.1.14 GPIOx_DRV1

15.4.1.15 GPIOx_DRV1_DISABLE_DEFAULT

15.4.1.16 GPIOx_DRV0

15.4.1.17 GPIOx_DRV0_DISABLE_DEFAULT

15.4.1.18 GPIOx_PULLSEL

15.4.1.19 GPIOx_PULLSEL_DISABLE_DEFAULT

15.4.1.20 GPIOx_PULLENB

15.4.1.21 GPIOx_PULLENB_DISABLE_DEFAULT

16 Ethernet MAC

16.1 Overview

16.1.1 MAC Core Features

16.1.2 DMA Block Features

16.2 Block Diagram

16.3 Register Description

16.3.1 Register Map Summary

16.3.1.1 MAC DMA Register

16.3.1.1.1 Ethernet MAC DMA Register 0

16.3.1.1.2 Ethernet MAC DMA Register 1

16.3.1.1.3 Ethernet MAC DMA Register 2

16.3.1.1.4 Ethernet MAC DMA Register 3

16.3.1.1.5 Ethernet MAC DMA Register 4

16.3.1.1.6 Ethernet MAC DMA Register 5

16.3.1.1.7 Ethernet MAC DMA Register 6

16.3.1.1.8 Ethernet MAC DMA Register 7

16.3.1.1.9 Ethernet MAC DMA Register 8

16.3.1.1.10 Ethernet MAC DMA Register 18

16.3.1.1.11 Ethernet MAC DMA Register 19

16.3.1.1.12 Ethernet MAC DMA Register 20

16.3.1.1.13 Ethernet MAC DMA Register 21

16.3.1.2 MAC Core Register

16.3.1.2.1 Ethernet MAC Register 0

16.3.1.2.2 Ethernet MAC Register 1

16.3.1.2.3 Ethernet MAC Register 2

16.3.1.2.4 Ethernet MAC Register 3

16.3.1.2.5 Ethernet MAC Register 4

16.3.1.2.6 Ethernet MAC Register 5

16.3.1.2.7 Ethernet MAC Register 6

16.3.1.2.8 Ethernet MAC Register 7

16.3.1.2.9 Ethernet MAC Register 8

16.3.1.2.10 Ethernet MAC Register 9

16.3.1.2.11 Ethernet MAC Register 14

16.3.1.2.12 Ethernet MAC Register 15

16.3.1.2.13 Ethernet MAC Register 16

16.3.1.2.14 Ethernet MAC Register 17

16.3.1.2.15 Ethernet MAC Register 18

16.3.1.2.16 Ethernet MAC Register 19

16.3.1.2.17 Ethernet MAC Register 20 ~ 47

16.3.1.2.18 Ethernet MAC Register 48

16.3.1.2.19 Ethernet MAC Register 49

16.3.1.2.20 Ethernet MAC Register 50

16.3.1.2.21 Ethernet MAC Register 51

16.3.1.2.22 Ethernet MAC Register 52

16.3.1.2.23 Ethernet MAC Register 53

16.3.1.2.24 Ethernet MAC Register 54

16.3.1.2.25 Ethernet MAC Register 448

16.3.1.2.26 Ethernet MAC Register 449

16.3.1.2.27 Ethernet MAC Register 450

16.3.1.2.28 Ethernet MAC Register 451

16.3.1.2.29 Ethernet MAC Register 452

16.3.1.2.30 Ethernet MAC Register 453

16.3.1.2.31 Ethernet MAC Register 454

16.3.1.2.32 Ethernet MAC Register 455

16.3.1.2.33 Ethernet MAC Register 456

16.3.1.2.34 Ethernet MAC Register 457

16.3.1.2.35 Ethernet MAC Register 458

16.3.1.2.36 Ethernet MAC Register 512 ~ 543

17 SD/MMC Controller

17.1 Overview

17.1.1 Features

17.1.1.1 Features of Mobile Storage Host

17.2 Block Diagram

17.2.1.1 Clock Phase Shifter

17.3 Register Description

17.3.1 Register Map Summary

17.3.1.1 CTRL

17.3.1.2 POWER_ENABLE

17.3.1.3 CLKDIV

17.3.1.4 CLK_SOURCE

17.3.1.5 CLKENA

17.3.1.6 TMOUT

17.3.1.7 CTYPE

17.3.1.8 BLKSIZ

17.3.1.9 BYTCNT

17.3.1.10 INTMASK

17.3.1.11 CMDARG

17.3.1.12 CMD

17.3.1.13 RESP0

17.3.1.14 RESP1

17.3.1.15 RESP2

17.3.1.16 RESP3

17.3.1.17 MINTSTS

17.3.1.18 RINTSTS

17.3.1.19 STATUS

17.3.1.20 FIFOTH

17.3.1.21 CDETECT

17.3.1.22 WRTPRT

17.3.1.23 TCBCNT

17.3.1.24 TBBCNT

17.3.1.25 DEBNCE

17.3.1.26 USRID

17.3.1.27 VERID

17.3.1.28 UHS_REG

17.3.1.29 RST_n

17.3.1.30 BMODE

17.3.1.31 PLDMND

17.3.1.32 DBADDR

17.3.1.33 IDSTS

17.3.1.34 IDINTEN

17.3.1.35 DSCADDR

17.3.1.36 BUFADDR

17.3.1.37 CARDTHRCTL

17.3.1.38 BACK_END_POWER

17.3.1.39 EMMC_DDR_REG

17.3.1.40 EMMC_DDR_REG

17.3.1.41 Data

18 Pulse Period Measurement (PPM)

18.1 Overview

18.1.1 Features

18.1.2 Block Diagram

18.2 Functional Description

18.2.1 IR Remote Protocol Example

18.2.2 Timing

18.2.3 Flowchart

18.3 Register Description

18.3.1 Register Map Summary

18.3.1.1 PPMCTRL

18.3.1.2 PPMSTATUS

18.3.1.3 PPMLOWPERIOD

18.3.1.4 PPMHIGHPERIOD

19 Pulse Width Modulation (PWM) Timer

19.1 Overview

19.2 Features

19.3 Block Diagram

19.4 Functional Description

19.4.1 Prescaler & Divider

19.4.2 Basic Timer Operation

19.4.3 Auto-Reload and Double Buffering

19.4.4 Initialize Timer (Setting Manual-Up Data and Inverter)

19.4.5 Output Level Control

19.4.6 Dead Zone Generator

19.4.7 Timer Interrupt Generation

19.5 Register Description

19.5.1 Register Map Summary

19.5.1.1 TCFG0

19.5.1.2 TCFG1

19.5.1.3 TCON

19.5.1.4 TCNTB0

19.5.1.5 TCMPB0

19.5.1.6 TCNTO0

19.5.1.7 TCNTB1

19.5.1.8 TCMPB1

19.5.1.9 TCNTO1

19.5.1.10 TCNTB2

19.5.1.11 TCMPB2

19.5.1.12 TCNTO2

19.5.1.13 TCNTB3

19.5.1.14 TCMPB3

19.5.1.15 TCNTO3

19.5.1.16 TCNTB4

19.5.1.17 TCNTO4

19.5.1.18 TINT_CSTAT

20 Analog Digital Converter (ADC)

20.1 Overview

20.2 Features

20.3 Block Diagram

20.4 Functional Description

20.4.1 I/O Chart

20.4.2 Timing

20.4.3 Analog Input Selection Table

20.4.4 Flowchart

20.5 Register Description

20.5.1 Register Map Summary

20.5.1.1 ADCCON

20.5.1.2 ADCDAT

20.5.1.3 ADCINTENB

20.5.1.4 ADCINTCLR

21 I2C Controller

21.1 Overview

21.2 Features

21.3 Functional Description

21.3.1 The Concept of the I2C-Bus

21.3.2 IC Protocol

21.3.3 Start/Stop Operation

21.3.4 Data Format

21.3.5 Data Transfer

21.3.6 Arbitration

21.3.7 Synchronization

21.3.8 Acknowledge

21.3.9 Read/Write Operation

21.3.10 Configuration I2C-Bus

21.3.11 Operations

21.3.12 Interrupt Generation

21.3.13 System Bus Reset

21.4 Programming Guide

21.4.1 I2C-Bus Initialize

21.4.2 Commands

21.4.2.1 Master Transmitter Mode (M/Tx)

21.4.2.2 Master Receiver Mode (M/Rx)

21.4.2.3 Slave Transmitter Mode (S/Tx)

21.4.2.4 Slave Receiver Mode (S/Rx)

21.5 Design Issues

21.5.1 Software Layer

21.5.2 Delays between I2C-Bus Commands

21.6 Register Description

21.6.1 Register Map Summary

21.6.1.1 ICCR

21.6.1.2 ICSR

21.6.1.3 IAR

21.6.1.4 IDSR

21.6.1.5 STOPCON

22 SPI/SSP

22.1 Overview

22.2 Features

22.3 Block Diagram

22.4 Functional Description

22.4.1 Clock Generation Configuration

22.4.2 Clock Ratios

22.4.2.1 Programming the Serial Clock Rate

22.4.3 Operation

22.4.3.1 Transmit and Receive Operation

22.4.3.2 Reset Operation

22.4.3.3 Interrupts

22.4.4 Frame Format

22.4.4.1 Texas Instruments Synchronous Serial Frame Format

22.4.4.2 Motorola SPI Frame Format

22.4.4.3 Motorola SPI Format with SPO = 0, SPH = 0

22.4.4.4 Motorola SPI Format with SPO = 0, SPH = 1

22.4.4.5 Motorola SPI Format with SPO = 1, SPH = 0

22.4.4.6 Motorola SPI Format with SPO = 1, SPH = 1

22.4.4.7 National Semiconductor Microwire Frame Format

22.5 Register Description

22.5.1 Register Map Summary

22.5.1.1 SSPCR0

22.5.1.2 SSPCR1

22.5.1.3 SSPDR

22.5.1.4 SSPSR

22.5.1.5 SSPCPSR

22.5.1.6 SSPIMSC

22.5.1.7 SSPRIS

22.5.1.8 SSPMIS

22.5.1.9 SSPICR

22.5.1.10 SSPDMACR

23 MPEG-TS Interface

23.1 Overview

23.2 Features

23.3 Functional Description

23.3.1 Timing

23.4 Register Description

23.4.1 Register Map Summary

23.4.1.1 CAP_CTRL0

23.4.1.2 CAP_CTRL1

23.4.1.3 CAP_WR_PID_VAL

23.4.1.4 CAP_WR_PID_ADDR

23.4.1.5 CAP0_CAPDATA

23.4.1.6 CAP1_CAPDATA

23.4.1.7 CORE_TRDATA

23.4.1.8 CORE_CTRL

23.4.1.9 IDMA_STATUS

23.4.1.10 IDMA_CON

23.4.1.11 IDMA_INT

23.4.1.12 IDMA0_ADDR

23.4.1.13 IDMA1_ADDR

23.4.1.14 IDMA2_ADDR

23.4.1.15 IDMA3_ADDR

23.4.1.16 IDMA0_LEN

23.4.1.17 IDMA1_LEN

23.4.1.18 IDMA2_LEN

23.4.1.19 IDMA3_LEN

23.5 PID Filter Data Structure

24 UART_ISO7816

24.1 Overview

24.2 Features

24.3 Block Diagram

24.3.1 IrDA SIR ENDEC Functional Description

24.3.1.1 IrDA SIR Transmit Encoder

24.3.1.2 IrDA SIR Receive Decoder

24.4 Operation

24.4.1 Interface Reset

24.4.2 Clock Signals

24.4.3 UART Operation

24.4.4 UART Character Frame

24.4.5 IrDA Data Modulation

24.4.6 UART Modem Operation

24.4.7 UART DMA Interface

24.4.8 Interrupts

24.4.9 ISO-7816

24.5 Register Description

24.5.1 Register Map Summary

24.5.1.1 UARTDR

24.5.1.2 UARTRSR/UARTECR

24.5.1.3 UARTFR

24.5.1.4 UARTILPR

24.5.1.5 UARTIBRD

24.5.1.6 UARTFBRD

24.5.1.7 UARTLCR_H

24.5.1.8 UARTCR

24.5.1.9 UARTIFLS

24.5.1.10 UARTIMSC

24.5.1.11 UARTRIS

24.5.1.12 UARTMIS

24.5.1.13 UARTICR

24.5.1.14 UARTDMACR

25 USB2.0 OTG

25.1 Overview

25.2 Features

25.3 Block Diagram

25.4 I/O Pin Description

25.5 Functional Description

25.5.1 End Point Packet Size

25.5.2 USB 5V Power Detection

25.5.3 Force Power Down

25.5.4 External Charge Pump

25.5.5 Modes of Operation

25.6 Programming User Configure of PHY and OTG LINK

25.7 Register Description

25.7.1 Register Map Summary

25.7.1.1 Core Global Registers (USB_OTG_GCSR)

25.7.1.1.1 GOTGCTL

25.7.1.1.2 GOTGINT

25.7.1.1.3 GAHBCFG

25.7.1.1.4 GUSBCFG

25.7.1.1.5 GRSTCTL

25.7.1.1.6 GINTSTS

25.7.1.1.7 GINTMSK

25.7.1.1.8 GRXSTSR (Host Mode)

25.7.1.1.9 GRXSTSP (Device Mode)

25.7.1.1.10 GRXFSIZ

25.7.1.1.11 GNPTXFSIZ

25.7.1.1.12 GNPTXSTS

25.7.1.1.13 HPTXFSIZ

25.7.1.1.14 DPTXFSIZn (DPTXFSIZ1, DPTXFSIZ2, …, DPTXFSIZ15)

25.7.1.2 Host Mode Registers (USB_OTG_HMCSR)

25.7.1.2.1 HCFG

25.7.1.2.2 HFIR

25.7.1.2.3 HFNUM

25.7.1.2.4 HPTXSTS

25.7.1.2.5 HAINT

25.7.1.2.6 HAINTMSK

25.7.1.2.7 HPRT

25.7.1.2.8 HCCHARn (0 ( n ( 15, HCCHAR0, HCCHAR1, …, HCCHAR15)

25.7.1.2.9 HCSPLTn (0 ( n ( 15, HCSPLT0, HCSPLT1, …, HCSPLT15)

25.7.1.2.10 HCINTn (0 ( n ( 15, HCINT0, HCINT1, …, HCINT15)

25.7.1.2.11 HCINTMSKn (0 ( n ( 15, HCINTMSK0, HCINTMSK1, …, HCINTMSK15)

25.7.1.2.12 HCTSIZn (0 ( n ( 15, HCTSIZ0, HCTSIZ1, …, HCTSIZ15)

25.7.1.2.13 HCDMAn (0 ( n ( 15, HCDMA0, HCDMA1, …, HCDMA15)

25.7.1.3 Device Mode Registers (USB_OTG_DMCSR)

25.7.1.3.1 DCFG

25.7.1.3.2 DCTL

25.7.1.3.3 DSTS

25.7.1.3.4 DIEPMSK

25.7.1.3.5 DOEPMSK

25.7.1.3.6 DAINT

25.7.1.3.7 DAINTMSK

25.7.1.3.8 DTKNQR1

25.7.1.3.9 DTKNQR2

25.7.1.3.10 DVBUSDIS

25.7.1.3.11 DVBUSPULSE

25.7.1.3.12 DTKNQR3

25.7.1.3.13 DTKNQR4

25.7.1.3.14 DIEPCTL0

25.7.1.3.15 DIEPINT0

25.7.1.3.16 DIEPTSIZ0

25.7.1.3.17 DIEPDMA0

25.7.1.3.18 DIEPCTLn (1 ( n ( 15, DIEPCTL1, DIEPCTL2, …, DIEPCTL15)

25.7.1.3.19 DIEPINTn (1 ( n ( 7, DIEPINT1, DIEPINT2, …, DIEPINT7)

25.7.1.3.20 DIEPTSIZn (1 ( n ( 7, DIEPTSIZ1, DIEPTSIZ2, …, DIEPTSIZ7)

25.7.1.3.21 DIEPDMAn (1 ( n ( 7, DIEPDMA1, DIEPDMA2, …, DIEPDMA7)

25.7.1.3.22 DOEPCTL0

25.7.1.3.23 DOEPINT0

25.7.1.3.24 DOEPTSIZ0

25.7.1.3.25 DOEPDMA0

25.7.1.3.26 DOEPCTLn (1 ( n ( 15, DOEPCTL1, DOEPCTL2, …, DOEPCTL15)

25.7.1.3.27 DOEPINTn (1 ( n ( 7, DOEPINT1, DOEPINT2, …, DOEPINT7)

25.7.1.3.28 DOEPTSIZn (1 ( n ( 7, DOEPTSIZ1, DOEPTSIZ2, …, DOEPTSIZ7)

25.7.1.3.29 DOEPDMAn (1 ( n ( 7, DOEPDMA1, DOEPDMA2, …, DOEPDMA7)

25.7.1.4 Power and Clock Gating Registers (USB_OTG_PCGCCTL)

25.7.1.4.1 PCGCCTL

26 USB2.0 HOST

26.1 Overview

26.2 Features

26.3 Block Diagram

26.4 Functional Description

26.4.1 Programming User Configure of PHY and LINK in EHCI or OHCI

26.4.2 Programming User Configure of PHY and LINK in HSIC

26.4.3 Attention Point of HSIC Programming

26.5 Register Description

26.5.1 Register Map Summary

26.5.1.1 HCCAPBASE

26.5.1.2 HCSPARAMS

26.5.1.3 HCCPARAMS

26.5.1.4 USBCMD

26.5.1.5 USBSTS

26.5.1.6 USBINTR

26.5.1.7 FRINDEX

26.5.1.8 CTRLDSSEGMEN

26.5.1.9 PERIODICLISTBASE

26.5.1.10 ASYNCLISTADDR

26.5.1.11 CONFIGFLAG

26.5.1.12 PORTSC_1 to 15

26.5.1.13 INSNREG00

26.5.1.14 INSNREG01

26.5.1.15 INSNREG02

26.5.1.16 INSNREG03

26.5.1.17 INSNREG04

26.5.1.18 INSNREG05

26.5.1.19 INSNREG06

26.5.1.20 INSNREG07

26.5.1.21 INSNREG08

27 I2S

27.1 Overview

27.2 Features

27.3 Block Diagram

27.4 Functional Description

27.4.1 Basic Clock Tree

27.4.2 I2S-bus Format

27.4.3 Sampling Frequency and Master Clock

27.4.4 I2S Clock Mapping Table

27.5 Programming Guide

27.5.1 Tx Channel

27.5.2 Rx Channel

27.5.3 I2S-Controller Initialize

27.5.4 Notes

27.6 Register Description

27.6.1 Register Map Summary

27.6.1.1 I2SCON

27.6.1.2 ICSR

27.6.1.3 I2SFIC

27.6.1.4 I2SPSR

27.6.1.5 I2STXD

27.6.1.6 I2SRXD

28 AC97

28.1 Overview

28.2 Features

28.3 Block Diagram

28.4 Functional Description

28.4.1 Internal Data Path

28.4.2 Operation Flow Chart

28.4.3 AC-link Digital Interface Protocol

28.4.3.1 AC-link Output Frame (SDATA_OUT)

28.4.3.2 AC-link Input Frame (SDATA_IN)

28.4.4 AC97 Power-down

28.4.4.1 Powering Down the AC-Link

28.4.4.2 Waking Up the AC-Link - Wake Up Triggered by the AC97 Controller

28.4.4.3 Cold AC97 Reset

28.4.4.4 Warm AC97 Reset

28.4.4.5 AC97 State Diagram

28.5 Register Description

28.5.1 Register Map Summary

28.5.1.1 AC_GLBCTRL

28.5.1.2 AC_GLBSTAT

28.5.1.3 AC_CODEC_CMD

28.5.1.4 AC_CODEC_STAT

28.5.1.5 AC_PCMADDR

28.5.1.6 AC_MICADDR

28.5.1.7 AC_PCMDATA

28.5.1.8 AC_MICDATA

29 SPDIF TX

29.1 Overview

29.2 Features

29.3 Block Diagram

29.4 Functional Description

29.4.1 Data Format of SPDIF

29.4.1.1 Frame Format

29.4.1.2 Sub-frame Format (IEC 60958)

29.4.2 Channel Coding

29.4.3 Preamble

29.4.4 Non-Linear PCM Encoded Source (IEC 61937)

29.4.5 SPDIF Operation

29.4.6 Shadowed Register

29.5 Register Description

29.5.1 Register Map Summary

29.5.1.1 SPDCLKCON

29.5.1.2 SPDCON

29.5.1.3 SPDBSTAS

29.5.1.4 SPDCSTAS

29.5.1.5 SPDDAT

29.5.1.6 SPDCNT

29.5.1.7 SPDBSTAS_SHD

29.5.1.8 SPDCNT_SHD

29.5.1.9 USERBIT1

29.5.1.10 USERBIT2

29.5.1.11 USERBIT3

29.5.1.12 USERBIT1_SHD

29.5.1.13 USERBIT2_SHD

29.5.1.14 USERBIT3_SHD

29.5.1.15 VERSION_INFO

30 SPDIF RX

30.1 Overview

30.2 Features

30.3 Block Diagram

30.4 Functional Description

30.5 Register Description

30.5.1 Register Map Summary

30.5.1.1 SPDIF_CTRL

30.5.1.2 SPDIF_ENBIRQ

30.5.1.3 REGUSERA0

30.5.1.4 REGUSERA1

30.5.1.5 REGUSERA2

30.5.1.6 REGUSERA3

30.5.1.7 REGUSERA4

30.5.1.8 REGUSERA5

30.5.1.9 REGUSERB0

30.5.1.10 REGUSERB1

30.5.1.11 REGUSERB2

30.5.1.12 REGUSERB3

30.5.1.13 REGUSERB4

30.5.1.14 REGUSERB5

30.5.1.15 REGSTATA0

30.5.1.16 REGSTATA1

30.5.1.17 REGSTATA2

30.5.1.18 REGSTATA3

30.5.1.19 REGSTATA4

30.5.1.20 REGSTATA5

30.5.1.21 REGSTATB0

30.5.1.22 REGSTATB1

30.5.1.23 REGSTATB2

30.5.1.24 REGSTATB3

30.5.1.25 REGSTATB4

30.5.1.26 REGSTATB5

31 PDM

31.1 Overview

31.2 Features

31.3 Block Diagram

31.4 PDM Application Note

31.4.1 Butterworth Filter Configuration

31.5 Register Description

31.5.1 Register Map Summary

31.5.1.1 PDM_CTRL

31.5.1.2 PDM_gain0

31.5.1.3 PDM_gain1

31.5.1.4 PDM_coeff

31.5.1.5 PDM_data

31.5.1.6 PDM_ctrl1

31.5.1.7 PDM_irqctrl

32 Display Architecture

32.1 Overview

32.2 Features

32.3 Block Diagram

32.4 TFT/MPU Interface

32.5 Register Description

32.5.1 Register Map Summary

32.5.1.1 HDMI_MUXCTRL

32.5.1.2 LVDS_MUXCTRL

32.5.1.3 HDMI_SYNCCTRL0

32.5.1.4 HDMI_SYNCCTRL1

32.5.1.5 HDMI_SYNCCTRL2

32.5.1.6 HDMI_ SYNCCTRL3

32.5.1.7 TFT_MUXCTRL

33 Multi Layer Controller (MLC)

33.1 Overview

33.2 Features

33.3 Block Diagram

33.4 Dual Register Set Architecture

33.5 MLC Global Parameters

33.5.1 Screen Size

33.5.2 Priority

33.5.3 Field Mode

33.5.4 Background Color

33.6 Per-layer Parameters

33.6.1 Enable

33.6.2 Lock Control

33.6.3 Position

33.6.4 Pixel Format

33.6.4.1 RGB Layer Format

33.6.4.2 Video Layer Format

33.6.4.3 Layer Blending

33.6.5 Address Generation

33.6.5.1 RGB Layer Address Generation

33.6.5.2 Video Layer Address Generation

33.6.6 Video Layer Specific Parameters

33.6.7 Scale Function

33.6.7.1 Color Control

33.6.7.2 Luminance Enhancement

33.6.7.3 Chrominance Enhancement

33.6.8 Gamma Correction

33.7 Clock Generation

33.8 Register Description

33.8.1 Register Map Summary

33.8.1.1 MLCCONTROLT

33.8.1.2 MLCSCREENSIZE

33.8.1.3 MLCBGCOLOR

33.8.1.4 MLCLEFTRIGHT0

33.8.1.5 MLCTOPBOTTOM0

33.8.1.6 MLCLEFTRIGHT0_0

33.8.1.7 MLCTOPBOTTOM0_0

33.8.1.8 MLCLEFTRIGHT0_1

33.8.1.9 MLCTOPBOTTOM0_1

33.8.1.10 MLCCONTROL0

33.8.1.11 MLCHSTRIDE0

33.8.1.12 MLCVSTRIDE0

33.8.1.13 MLCTPCOLOR0

33.8.1.14 MLCINVCOLOR0

33.8.1.15 MLCADDRESS0

33.8.1.16 MLCLEFTright1

33.8.1.17 MLCtopBOTTOM1

33.8.1.18 MLCLEFTRIGHT1_0

33.8.1.19 MLCTOPBOTTOM1_0

33.8.1.20 MLCLEFTRIGHT1_1

33.8.1.21 MLCTOPBOTTOM1_1

33.8.1.22 MLCCONTROL1

33.8.1.23 MLCHSTRIDE1

33.8.1.24 MLCVSTRIDE1

33.8.1.25 MLCTPCOLOR1

33.8.1.26 MLCINVCOLOR1

33.8.1.27 MLCADDRESS1

33.8.1.28 MLCLEFright2

33.8.1.29 MLCtopBOTTOM2

33.8.1.30 MLCCONTROL2

33.8.1.31 MLCVSTRIDE3

33.8.1.32 MLCTPCOLOR3

33.8.1.33 MLCADDRESS3

33.8.1.34 MLCADDRESSCB

33.8.1.35 MLCADDRESSCR

33.8.1.36 MLCVSTRIDECB

33.8.1.37 MLCVSTRIDECR

33.8.1.38 MLCHScALE

33.8.1.39 MLCVSCALE

33.8.1.40 MLCLUENH

33.8.1.41 MLCCHENH0

33.8.1.42 MLCCHENH1

33.8.1.43 MLCCHENH2

33.8.1.44 MLCCHENH3

33.8.1.45 MLCGAMMACONT

33.8.1.46 MLCRGAMMATABLEWRITE

33.8.1.47 MLCGGAMMATABLEWRITE

33.8.1.48 MLCBGAMMATABLEWRITE

33.8.1.49 MLCCLKENB

34 Display Controller (DPC)

34.1 Overview

34.2 Features

34.3 Block Diagram

34.4 Sync Generator

34.4.1 Clock Generation

34.4.1.1 Peripheral Clock Generation

34.4.1.2 Video Clock Generation

34.4.2 Format

34.4.2.1 RGB Format

34.4.2.2 YCbCr Format

34.4.3 Sync Signals

34.4.3.1 Horizontal Timing Interface

34.4.3.2 Vertical Timing Interface

34.4.3.3 AC Timing

34.4.3.4 UPSCALER (Only Secondary Display)

34.4.3.5 Embedded Sync

34.4.4 Scan Mode

34.4.5 Delay

34.4.6 Interrupt

34.4.7 MPU (i80) Type Sync Signals

34.4.8 Odd/Even Field Flag

34.5 Register Description

34.5.1 Register Map Summary

34.5.1.1 DPCHTOTAL

34.5.1.2 DPCHSWIDTH

34.5.1.3 DPCHASTART

34.5.1.4 DPCHAEND

34.5.1.5 DPCVTOTAL

34.5.1.6 DPCVSWIDTH

34.5.1.7 DPCVASTART

34.5.1.8 DPCVAEND

34.5.1.9 DPCCTRL0

34.5.1.10 DPCCTRL1

34.5.1.11 DPCEVTOTAL

34.5.1.12 DPCEVSWIDTH

34.5.1.13 DPCEVASTART

34.5.1.14 DPCEVAEND

34.5.1.15 DPCCTRL2

34.5.1.16 DPCVSEOFFSET

34.5.1.17 DPCVSSOFFSET

34.5.1.18 DPCEVSEOFFSET

34.5.1.19 DPCEVSSOFFSET

34.5.1.20 DPCDELAY0

34.5.1.21 DPUPSCALECON0

34.5.1.22 DPUPSCALECON1

34.5.1.23 DPCDELAY1

34.5.1.24 DPCmputime0

34.5.1.25 DPCmputime1

34.5.1.26 dpcmpuwrdatal

34.5.1.27 dpcmpuindex

34.5.1.28 dpcmpustatus

34.5.1.29 dpcmPUDatah

34.5.1.30 dpcmpurdatal

34.5.1.31 dpccmdbufferrdatal

34.5.1.32 dpccmdbufferrdataH

34.5.1.33 DPCmputime1

34.5.1.34 DPCpadposition0

34.5.1.35 DPCpadposition1

34.5.1.36 DPCpadposition2

34.5.1.37 DPCpadposition3

34.5.1.38 DPCpadposition4

34.5.1.39 DPCpadposition5

34.5.1.40 DPCpadposition6

34.5.1.41 DPCpadposition7

34.5.1.42 DPCRGBMASK0

34.5.1.43 DPCRGBMASK1

34.5.1.44 DPCRGBSHIFT

34.5.1.45 dpcdataflush

34.5.1.46 DPCCLKENB

34.5.1.47 DPCCLKGEN0L

34.5.1.48 DPCCLKGEN0h

34.5.1.49 DPCCLKGEN1L

34.5.1.50 DPCCLKGEN1h

35 Scaler

35.1 Overview

35.2 Features

35.3 Block Diagram

35.4 Functional Description

35.4.1 Digital Filter Characteristics

35.4.1.1 Horizontal Filter (5-Tab FIR Filter) Frequency Response and Group Delay

35.4.1.2 Vertical Filter (3-Tab FIR Filter) Frequency Response and Group Delay

35.5 Programming Guide

35.5.1 Configuration

35.5.2 RUN

35.6 Register Description

35.6.1 Register Map Summary

35.6.1.1 SCRUNREG

35.6.1.2 SCCFGREG

35.6.1.3 SCINTREG

35.6.1.4 SCSRCADDRREG

35.6.1.5 SCSRCADDRREG

35.6.1.6 SCSRCSIZEREG

35.6.1.7 SCDESTADDR0

35.6.1.8 SCDESTSTREDE0

35.6.1.9 SCDESTADDR1

35.6.1.10 SCDESTADDR1

35.6.1.11 SCDESTSIZE

35.6.1.12 DELTAXREG

35.6.1.13 DELTAYREG

35.6.1.14 HVSOFTREG

35.6.1.15 CMDBUFADDR

35.6.1.16 CMDBUFCON

35.6.1.17 YVFILTER[N]_00_03

35.6.1.18 YVFILTER[N]_04_07

35.6.1.19 YVFILTER[N]_08_11

35.6.1.20 YVFILTER[N]_12_15

35.6.1.21 YVFILTER[N]_16_19

35.6.1.22 YVFILTER[N]_20_23

35.6.1.23 YVFILTER[N]_24_27

35.6.1.24 YVFILTER[N]_28_31

35.6.1.25 YVFILTER2_00_03

35.6.1.26 YHFILTER[N]_00_01

35.6.1.27 YHFILTER[N]_02_03

35.6.1.28 YHFILTER[N]_04_05

35.6.1.29 YHFILTER[N]_06_07

35.6.1.30 YHFILTER[N]_08_09

35.6.1.31 YHFILTER[N]_10_11

35.6.1.32 YHFILTER[N]_12_13

35.6.1.33 YHFILTER[N]_14_15

35.6.1.34 YHFILTER[N]_16_17

35.6.1.35 YHFILTER[N]_18_19

35.6.1.36 YHFILTER[N]_20_21

35.6.1.37 YHFILTER[N]_22_23

35.6.1.38 YHFILTER[N]_24_25

35.6.1.39 YHFILTER[N]_26_27

35.6.1.40 YHFILTER[N]_28_29

35.6.1.41 YHFILTER[N]_30_31

36 LVDS

36.1 Overview

36.2 Features

36.3 Block Diagram

36.4 Functional Description

36.4.1 LVDS Data Packing Format

36.4.2 LVDS Application Note

36.4.3 Skew Control between Output Data and Clock

36.4.4 Electrical Characteristics

36.5 Register Description

36.5.1 Register Map Summary

36.5.1.1 LVDSCTRL0

36.5.1.2 LVDSCTRL1

36.5.1.3 LVDSCTRL2

36.5.1.4 LVDSCTRL3

36.5.1.5 LVDSCTRL4

36.5.1.6 LVDSLOC0

36.5.1.7 LVDSLOC1

36.5.1.8 LVDSLOC2

36.5.1.9 LVDSLOC3

36.5.1.10 LVDSLOC4

36.5.1.11 LVDSLOC5

36.5.1.12 LVDSLOC6

36.5.1.13 LVDSLOCMASK0

36.5.1.14 LVDSLOCMASK1

36.5.1.15 LVDSLOCPOL0

36.5.1.16 LVDSLOCPOL1

36.5.1.17 LVDSTMODE0

36.5.1.18 LVDSTMODE1

36.5.1.19 DisplayTop Register Summary

36.5.1.19.1 LVDS_MUXCTRL

37 HDMI

37.1 Overview

37.2 Features

37.3 Block Diagram

37.4 Functional Description

37.4.1 Select RGB Video data for HDMI

37.4.2 HDMI Converter

37.4.3 HDMI LINK

37.4.3.1 Video Input Interface

37.4.3.2 Audio Input Interface

37.4.3.3 HPD

37.4.3.4 CEC

37.4.3.5 Interrupt Timing

37.4.3.6 HDCP KEY Management

37.5 Register Description

37.5.1 Register Map Summary

37.5.1.1 Control Registers

37.5.1.1.1 INTC_CON_0

37.5.1.1.2 INTC_FLAG_0

37.5.1.1.3 AESKEY_VALID

37.5.1.1.4 HPD

37.5.1.1.5 INTC_CON_1

37.5.1.1.6 INTC_FLAG_1

37.5.1.1.7 PHY_STATUS_0

37.5.1.1.8 PHY_STATUS_CMU

37.5.1.1.9 PHY_STATUS_PLL

37.5.1.1.10 PHY_CON_0

37.5.1.1.11 HPD_CTRL

37.5.1.1.12 HPD_STATUS

37.5.1.1.13 HPD_TH_x

37.5.1.2 Core Registers

37.5.1.2.1 HDMI_CON_0

37.5.1.2.2 HDMI_CON_1

37.5.1.2.3 HDMI_CON_2

37.5.1.2.4 STATUS

37.5.1.2.5 STATUS_EN

37.5.1.2.6 MODE_SEL

37.5.1.2.7 ENC_EN

37.5.1.2.8 HDMI_YMAX

37.5.1.2.9 HDMI_YMIN

37.5.1.2.10 HDMI_CMAX

37.5.1.2.11 HDMI_CMIN

37.5.1.2.12 H_BLANK_0

37.5.1.2.13 H_BLANK_1

37.5.1.2.14 V2_BLANK_0

37.5.1.2.15 V2_BLANK_1

37.5.1.2.16 V1_BLANK_0

37.5.1.2.17 V1_BLANK_1

37.5.1.2.18 V_LINE_0

37.5.1.2.19 V_LINE_1

37.5.1.2.20 H_LINE_0

37.5.1.2.21 H_LINE_1

37.5.1.2.22 HSYNC_POL

37.5.1.2.23 VSYNC_POL

37.5.1.2.24 INT_PRO_MODE

37.5.1.2.25 V_BLANK_F0_0

37.5.1.2.26 V_BLANK_F0_1

37.5.1.2.27 V_BLANK_F1_0

37.5.1.2.28 V_BLANK_F1_1

37.5.1.2.29 H_SYNC_START_0

37.5.1.2.30 H_SYNC_START_1

37.5.1.2.31 H_SYNC_END_0

37.5.1.2.32 H_SYNC_END_1

37.5.1.2.33 V_SYNC_LINE_BEF_2_0

37.5.1.2.34 V_SYNC_LINE_BEF_2_1

37.5.1.2.35 V_SYNC_LINE_BEF_1_0

37.5.1.2.36 V_SYNC_LINE_BEF_1_1

37.5.1.2.37 V_SYNC_LINE_AFT_2_0

37.5.1.2.38 V_SYNC_LINE_AFT_2_1

37.5.1.2.39 V_SYNC_LINE_AFT_1_0

37.5.1.2.40 V_SYNC_LINE_AFT_1_1

37.5.1.2.41 V_SYNC_LINE_AFT_PXL_2_0

37.5.1.2.42 V_SYNC_LINE_AFT_PXL_2_1

37.5.1.2.43 V_SYNC_LINE_AFT_PXL_1_0

37.5.1.2.44 V_SYNC_LINE_AFT_PXL_1_1

37.5.1.2.45 V_BLANK_F2_0

37.5.1.2.46 V_BLANK_F2_1

37.5.1.2.47 V_BLANK_F3_0

37.5.1.2.48 V_BLANK_F3_1

37.5.1.2.49 V_BLANK_F4_0

37.5.1.2.50 V_BLANK_F4_1

37.5.1.2.51 V_BLANK_F5_0

37.5.1.2.52 V_BLANK_F5_1

37.5.1.2.53 V_SYNC_LINE_AFT_3_0

37.5.1.2.54 V_SYNC_LINE_AFT_3_1

37.5.1.2.55 V_SYNC_LINE_AFT_4_0

37.5.1.2.56 V_SYNC_LINE_AFT_4_1

37.5.1.2.57 V_SYNC_LINE_AFT_5_0

37.5.1.2.58 V_SYNC_LINE_AFT_5_1

37.5.1.2.59 V_SYNC_LINE_AFT_6_0

37.5.1.2.60 V_SYNC_LINE_AFT_6_1

37.5.1.2.61 V_SYNC_LINE_AFT_PXL_3_0

37.5.1.2.62 V_SYNC_LINE_AFT_PXL_3_1

37.5.1.2.63 V_SYNC_LINE_AFT_PXL_4_0

37.5.1.2.64 V_SYNC_LINE_AFT_PXL_4_1

37.5.1.2.65 V_SYNC_LINE_AFT_PXL_5_0

37.5.1.2.66 V_SYNC_LINE_AFT_PXL_5_1

37.5.1.2.67 V_SYNC_LINE_AFT_PXL_6_0

37.5.1.2.68 V_SYNC_LINE_AFT_PXL_6_1

37.5.1.2.69 VACT_SPACE1_0

37.5.1.2.70 VACT_SPACE1_1

37.5.1.2.71 VACT_SPACE2_0

37.5.1.2.72 VACT_SPACE2_1

37.5.1.2.73 VACT_SPACE3_0

37.5.1.2.74 VACT_SPACE3_1

37.5.1.2.75 VACT_SPACE4_0

37.5.1.2.76 VACT_SPACE4_1

37.5.1.2.77 VACT_SPACE5_0

37.5.1.2.78 VACT_SPACE5_1

37.5.1.2.79 VACT_SPACE6_0

37.5.1.2.80 VACT_SPACE6_1

37.5.1.2.81 GCP_CON

37.5.1.2.82 GCP_BYTE1

37.5.1.2.83 GCP_BYTE2

37.5.1.2.84 GCP_BYTE3

37.5.1.2.85 ASP_CON

37.5.1.2.86 ASP_SP_FLAT

37.5.1.2.87 ASP_CHCFG0

37.5.1.2.88 ASP_CHCFG1

37.5.1.2.89 ASP_CHCFG2

37.5.1.2.90 ASP_CHCFG3

37.5.1.2.91 ACR_CON

37.5.1.2.92 ACR_MCTS0

37.5.1.2.93 ACR_MCTS1

37.5.1.2.94 ACR_MCTS2

37.5.1.2.95 ACR_N0

37.5.1.2.96 ACR_N1

37.5.1.2.97 ACR_N2

37.5.1.2.98 ACP_CON

37.5.1.2.99 ACP_TYPE

37.5.1.2.100 ACP_DATAx

37.5.1.2.101 ISRC_CON

37.5.1.2.102 ISRC1_HEADER1

37.5.1.2.103 ISRC1_DATAx

37.5.1.2.104 ISRC2_DATAx

37.5.1.2.105 AVI_CON

37.5.1.2.106 AVI_HEADER0

37.5.1.2.107 AVI_HEADER1

37.5.1.2.108 AVI_HEADER2

37.5.1.2.109 AVI_CHECK_SUM

37.5.1.2.110 AVI_BYTEx

37.5.1.2.111 AUI_CON

37.5.1.2.112 AUI_HEADER0

37.5.1.2.113 AUI_HEADER1

37.5.1.2.114 AUI_HEADER2

37.5.1.2.115 AUI_CHECK_SUM

37.5.1.2.116 AUI_BYTEx

37.5.1.2.117 MPG_CON

37.5.1.2.118 MPG_CHECK_SUM

37.5.1.2.119 MPG_DATAx

37.5.1.2.120 SPD_CON

37.5.1.2.121 SPD_HEADER0

37.5.1.2.122 SPD_HEADER1

37.5.1.2.123 SPD_HEADER2

37.5.1.2.124 SPD_DATAx

37.5.1.2.125 GAMUT_CON

37.5.1.2.126 GAMUT_HEADER0

37.5.1.2.127 GAMUT_HEADER1

37.5.1.2.128 GAMUT_HEADER2

37.5.1.2.129 GAMUT_METADATAx

37.5.1.2.130 VSI_CON

37.5.1.2.131 VSI_HEADER0

37.5.1.2.132 VSI_HEADER1

37.5.1.2.133 VSI_HEADER2

37.5.1.2.134 VSI_DATAx

37.5.1.2.135 DC_CONTROL

37.5.1.2.136 VIDEO_PATTERN_GEN

37.5.1.2.137 An_Seed_Sel

37.5.1.2.138 An_Seed_0

37.5.1.2.139 An_Seed_1

37.5.1.2.140 An_Seed_2

37.5.1.2.141 An_Seed_3

37.5.1.2.142 HDCP_SHA1_x

37.5.1.2.143 HDCP_KSV_LIST_x

37.5.1.2.144 HDCP_KSV_LIST_CON

37.5.1.2.145 HDCP_SHA_RESULT

37.5.1.2.146 HDCP_CTRL1

37.5.1.2.147 HDCP_CTRL2

37.5.1.2.148 HDCP_CHECK_RESULT

37.5.1.2.149 HDCP_BKSV_x

37.5.1.2.150 HDCP_AKSV_x

37.5.1.2.151 HDCP_An_x

37.5.1.2.152 HDCP_BCAPS

37.5.1.2.153 HDCP_BSTATUS_0

37.5.1.2.154 HDCP_BSTATUS_1

37.5.1.2.155 HDCP_Ri_0

37.5.1.2.156 HDCP_Ri_1

37.5.1.2.157 HDCP_I2C_INT

37.5.1.2.158 HDCP_AN_INT

37.5.1.2.159 HDCP_WATCGDOG_INT

37.5.1.2.160 HDCP_Ri_INT

37.5.1.2.161 HDCP_Ri_Compare_0

37.5.1.2.162 HDCP_Ri_Compare_1

37.5.1.2.163 HDCP_Frame_Count

37.5.1.2.164 RGB_ROUND_EN

37.5.1.2.165 VACT_SPACE_R_0

37.5.1.2.166 VACT_SPACE_R_1

37.5.1.2.167 VACT_SPACE_G_0

37.5.1.2.168 VACT_SPACE_G_1

37.5.1.2.169 VACT_SPACE_B_0

37.5.1.2.170 VACT_SPACE_B_1

37.5.1.2.171 BLUE_SCREEN_R_0

37.5.1.2.172 BLUE_SCREEN_R_1

37.5.1.2.173 BLUE_SCREEN_G_0

37.5.1.2.174 BLUE_SCREEN_G_1

37.5.1.2.175 BLUE_SCREEN_B_0

37.5.1.2.176 BLUE_SCREEN_B_1

37.5.1.3 AES Registers

37.5.1.3.1 AES_START

37.5.1.3.2 AES_DATA_SIZE_L

37.5.1.3.3 AES_DATA_SIZE_H

37.5.1.3.4 AES_DATA

37.5.1.4 SPDIF Registers

37.5.1.4.1 SPDIFIN_CLK_CTRL

37.5.1.4.2 SPDIFIN_OP_CTRL

37.5.1.4.3 SPDIFIN_IRQ_MASK

37.5.1.4.4 SPDIFIN_IRQ_STATUS

37.5.1.4.5 SPDIFIN_CONFIG_1

37.5.1.4.6 SPDIFIN_CONFIG_2

37.5.1.4.7 SPDIFIN_USER_VALUE_1

37.5.1.4.8 SPDIFIN_USER_VALUE_2

37.5.1.4.9 SPDIFIN_USER_VALUE_3

37.5.1.4.10 SPDIFIN_USER_VALUE_4

37.5.1.4.11 SPDIFIN_CH_STATUS_0_1

37.5.1.4.12 SPDIFIN_CH_STATUS_0_2

37.5.1.4.13 SPDIFIN_CH_STATUS_0_3

37.5.1.4.14 SPDIFIN_CH_STATUS_0_4

37.5.1.4.15 SPDIFIN_CH_STATUS_1

37.5.1.4.16 SPDIFIN_FRAME_PERIOD_1

37.5.1.4.17 SPDIFIN_FRAME_PERIOD_2

37.5.1.4.18 SPDIFIN_Pc_INFO_1

37.5.1.4.19 SPDIFIN_Pc_INFO_2

37.5.1.4.20 SPDIFIN_Pd_INFO_1

37.5.1.4.21 SPDIFIN_Pd_INFO_2

37.5.1.4.22 SPDIFIN_DATA_BUF_0_1

37.5.1.4.23 SPDIFIN_DATA_BUF_0_2

37.5.1.4.24 SPDIFIN_DATA_BUF_0_3

37.5.1.4.25 SPDIFIN_USER_BUF_0

37.5.1.4.26 SPDIFIN_DATA_BUF_1_1

37.5.1.4.27 SPDIFIN_DATA_BUF_1_2

37.5.1.4.28 SPDIFIN_DATA_BUF_1_3

37.5.1.4.29 SPDIFIN_USER_BUF_1

37.5.1.5 I2S Registers

37.5.1.5.1 I2S_CLK_CON

37.5.1.5.2 I2S_CON_1

37.5.1.5.3 I2S_CON_2

37.5.1.5.4 I2S_PIN_SEL_0

37.5.1.5.5 I2S_PIN_SEL_1

37.5.1.5.6 I2S_PIN_SEL_2

37.5.1.5.7 I2S_PIN_SEL_3

37.5.1.5.8 I2S_DSD_CON

37.5.1.5.9 I2S_MUX_CON

37.5.1.5.10 I2S_CH_ST_CON

37.5.1.5.11 I2S_CH_ST_0

37.5.1.5.12 I2S_CH_ST_1

37.5.1.5.13 I2S_CH_ST_2

37.5.1.5.14 I2S_CH_ST_3

37.5.1.5.15 I2S_CH_ST_4

37.5.1.5.16 I2S_CH_ST_SH_0

37.5.1.5.17 I2S_CH_ST_SH_1

37.5.1.5.18 I2S_CH_ST_SH_2

37.5.1.5.19 I2S_CH_ST_SH_3

37.5.1.5.20 I2S_CH_ST_SH_4

37.5.1.5.21 I2S_VD_DATA

37.5.1.5.22 I2S_MUX_CH

37.5.1.5.23 I2S_MUX_CUV

37.5.1.5.24 I2S_CH0_L_0

37.5.1.5.25 I2S_CH0_L_1

37.5.1.5.26 I2S_CH0_L_2

37.5.1.5.27 I2S_CH0_R_0

37.5.1.5.28 I2S_CH0_R_1

37.5.1.5.29 I2S_CH0_R_2

37.5.1.5.30 I2S_CH0_R_3

37.5.1.5.31 I2S_CH1_L_0

37.5.1.5.32 I2S_CH1_L_1

37.5.1.5.33 I2S_CH1_L_2

37.5.1.5.34 I2S_CH1_L_3

37.5.1.5.35 I2S_CH1_R_0

37.5.1.5.36 I2S_CH1_R_1

37.5.1.5.37 I2S_CH1_R_2

37.5.1.5.38 I2S_CH1_R_3

37.5.1.5.39 I2S_CH2_L_0

37.5.1.5.40 I2S_CH2_L_1

37.5.1.5.41 I2S_CH2_L_2

37.5.1.5.42 I2S_CH2_L_3

37.5.1.5.43 I2S_CH2_R_0

37.5.1.5.44 I2S_CH2_R_1

37.5.1.5.45 I2S_CH2_R_2

37.5.1.5.46 I2S_Ch2_R_3

37.5.1.5.47 I2S_CH3_L_0

37.5.1.5.48 I2S_CH3_L_1

37.5.1.5.49 I2S_CH3_L_2

37.5.1.5.50 I2S_CH3_R_0

37.5.1.5.51 I2S_CH3_R_1

37.5.1.5.52 I2S_CH3_R_2

37.5.1.5.53 I2S_CUV_L_R

37.5.1.6 CEC Registers

37.5.1.6.1 CEC_TX_STATUS_0

37.5.1.6.2 CEC_TX_STATUS_1

37.5.1.6.3 CEC_RX_STATUS_0

37.5.1.6.4 CEC_RX_STATUS_1

37.5.1.6.5 CEC_INTR_MASK

37.5.1.6.6 CEC_INTR_CLEAR

37.5.1.6.7 CEC_LOGIC_ADDR

37.5.1.6.8 CEC_DIVISOR_0

37.5.1.6.9 CEC_DIVISOR_1

37.5.1.6.10 CEC_DIVISOR_2

37.5.1.6.11 CEC_DIVISOR_3

37.5.1.6.12 CEC_TX_CTRL

37.5.1.6.13 CEC_TX_BYTE_NUM

37.5.1.6.14 CEC_TX_STATUS_2

37.5.1.6.15 CEC_TX_STATUS_3

37.5.1.6.16 CEC_TX_BUFFER_x

37.5.1.6.17 CEC_RX_CTRL

37.5.1.6.18 CEC_RX_STATUS_2

37.5.1.6.19 CEC_RX_STATUS_3

37.5.1.6.20 CEC_RX_BUFFER_x

37.5.1.6.21 CEC_FILTER_CTRL

37.5.1.6.22 CEC_FILTER_TH

37.6 HDMI PHY

37.6.1 PHY Configuration Change through APB

37.6.2 PHY Ready Sequence

37.6.3 HDMI PHY Configuration

37.6.4 Register Description

37.6.4.1 Register Map Summary

37.6.4.1.1 HDMI PHY

37.6.4.1.1.1 HDMIPHY 4h register

37.6.4.1.1.2 HDMIPHY 24h register

37.6.4.1.1.3 HDMIPHY 3ch register

37.6.4.1.1.4 HDMIPHY 40h register

37.6.4.1.1.5 HDMIPHY 5ch register

37.6.4.1.1.6 HDMIPHY 74h register

37.6.4.1.1.7 HDMIPHY 78h register

37.6.4.1.1.8 HDMIPHY 7Ch register

37.6.4.2 HDMI Application Sequences

37.6.4.2.1 DisplayTop Register Summary

37.6.4.2.1.1 HDMI_MUXCTRL

37.6.4.2.1.2 HDMI_syncctrl0

37.6.4.2.1.3 HDMI_syncctrl1

37.6.4.2.1.4 HDMI_syncctrl2

37.6.4.2.1.5 HDMI_syncctrl3

38 MIPI

38.1 Overview

38.2 Features

38.3 DSIM

38.3.1 Block Diagram of MIPI DSI System

38.3.1.1 Internal Primary FIFOs

38.3.1.2 Packet Header Arbitration

38.3.1.3 RxFIFO Structure

38.3.2 Interfaces and Protocol

38.3.2.1 Display Controller Interface

38.3.2.2 RGB Interface

38.3.2.3 HSA Mode

38.3.2.4 HSE Mode

38.3.2.5 Transfer General Data in Video Mode

38.3.2.6 MIPI DSIM Converts RGB Interface to Video Mode

38.3.3 Configuration

38.3.4 PLL

38.3.5 Buffer

38.4 Register Description

38.4.1 Register Map Summary

38.4.1.1 DSIM_STATUS

38.4.1.2 DSIM_SWRST

38.4.1.3 DSIM_CLKCTRL

38.4.1.4 DSIM_TIMEOUT

38.4.1.5 DSIM_CONFIG

38.4.1.6 DSIM_ESCMODE

38.4.1.7 DSIM_MDRESOL

38.4.1.8 DSIM_MVPORCH

38.4.1.9 DSIM_MHPORCH

38.4.1.10 DSIM_MSYNC

38.4.1.11 DSIM_SDRESOL

38.4.1.12 DSIM_INTSRC

38.4.1.13 DSIM_INTMSK

38.4.1.14 DSIM_PKTHDR

38.4.1.15 DSIM_PAYLOAD

38.4.1.16 DSIM_RXFIFO

38.4.1.17 DSIM_FIFOTHLD

38.4.1.18 DSIM_FIFOCTRL

38.4.1.19 DSIM_MEMACCHR

38.4.1.20 DSIM_PLLCTRL

38.4.1.21 DSIM_PLLCTRL1

38.4.1.22 DSIM_PLLCTRL2

38.4.1.23 DSIM_PLLTMR

38.4.1.24 DSIM_PHYCTRL

38.4.1.25 DSIM_PHYCTRL1

38.4.1.26 DSIM_PHYTIMING

38.4.1.27 DSIM_PHYTIMING1

38.4.1.28 DSIM_PHYTIMING2

38.4.1.29 DSIM_VERSION

38.4.1.30 DSIM_S3D_CTL

38.4.1.31 DSIM_P3D_CTL

38.4.1.32 DSIM_MIC_CTL

38.4.1.33 DSIM_P3D_ON_MIC_OFF_HORIZONTAL

38.4.1.34 DSIM_P3D_OFF_MIC_ON_HORIZONTAL

38.4.1.35 DSIM_P3D_ON_MIC_ON_HORIZONTAL

38.4.1.36 DSIM_P3D_ON_MIC_OFF_HFP

38.4.1.37 DSIM_P3D_OFF_MIC_ON_HFP

38.4.1.38 DSIM_P3D_ON_MIC_ON_HFP

38.5 CSIS

38.5.1 Interfaces and Protocol

38.5.1.1 D-PHY layer FSM

38.5.1.2 PPI Interface Timing & Protocol

38.5.1.2.1 High Speed Data Transfer

38.5.1.2.2 Ultra-Low Power Mode

38.5.1.2.3 ISP (CAM I/F) Interface

38.5.2 Configuration

38.5.2.1 Image Resolution

38.5.3 Interrupt

38.5.4 Clock Specification

38.5.5 Register Description

38.5.5.1 Register Map Summary

38.5.5.1.1 CSIS

38.5.5.1.1.1 CSIS_CTRL

38.5.5.1.1.2 CSIS_DPHYCTRL

38.5.5.1.1.3 CSIS_CONFIG_CH0

38.5.5.1.1.4 CSIS_DPHYSTS

38.5.5.1.1.5 CSIS_INTMSK

38.5.5.1.1.6 CSIS_INTSRC

38.5.5.1.1.7 CSIS_CTRL2

38.5.5.1.1.8 CSIS_VERSION

38.5.5.1.1.9 B_DphyCtrl

38.5.5.1.1.10 S_DphyCtrl

38.5.5.1.1.11 CSIS_RESOL_CH0

38.5.5.1.1.12 SDW_CONFIG_CH0

38.5.5.1.1.13 SDW_RESOL_CH0

38.5.5.1.1.14 Non-Image Data Register

38.6 D-PHY

38.6.1 Architecture

38.6.1.1 PLL and Clock Lane Connection

38.6.1.2 Data Lane Connection

38.6.1.3 IP Structure

38.6.1.4 Power Consumption

38.6.1.5 Signals

38.6.1.6 Package and Board Connection Guideline

38.6.1.7 Core Interface Timing Diagram

39 Video Input Processor (VIP)

39.1 Overview

39.2 Features

39.3 VIP Interconnection

39.3.1 Block Diagram

39.3.2 Clock Generation

39.4 Video Input Port

39.4.1 Block Diagram

39.4.2 Sync Generation

39.4.3 External Data Valid and Field

39.4.4 Data Order

39.4.5 Status

39.4.6 FIFO Controls

39.4.7 Recommend Setting for Video Input Port

39.5 Clipper & Decimator

39.5.1 Clipping & Scale-down

39.5.2 Output Data Format

39.5.3 Interlace Scan Mode

39.5.4 Pixels Alignment

39.6 Interrupt Generation

39.7 Register Description

39.7.1 Register Map Summary

39.7.1.1 VIP_CONFIG

39.7.1.2 VIP_INTCTRL

39.7.1.3 VIP_SYNCCTRL

39.7.1.4 VIP_SYNCMON

39.7.1.5 VIP_VBEGIN

39.7.1.6 VIP_VEND

39.7.1.7 VIP_HBEGIN

39.7.1.8 VIP_HEND

39.7.1.9 VIP_FIFOCTRL

39.7.1.10 VIP_HCOUNT

39.7.1.11 VIP_VCOUNT

39.7.1.12 VIP_CDENB

39.7.1.13 VIP_ODINT

39.7.1.14 VIP_IMGWIDTH

39.7.1.15 VIP_IMGHEIGHT

39.7.1.16 CLIP_LEFT

39.7.1.17 CLIP_RIGHT

39.7.1.18 CLIP_TOP

39.7.1.19 CLIP_BOTTOM

39.7.1.20 DECI_TARGETW

39.7.1.21 DECI_TARGETH

39.7.1.22 DECI_DELTAW

39.7.1.23 DECI_DELTAH

39.7.1.24 DECI_CLEARW

39.7.1.25 DECI_CLEARH

39.7.1.26 DECI_LUSEG

39.7.1.27 DECI_CRSEG

39.7.1.28 DECI_CBSEG

39.7.1.29 DECI_FORMAT

39.7.1.30 DECI_ROTFLIP

39.7.1.31 DECI_LULEFT

39.7.1.32 DECI_CRLEFT

39.7.1.33 DECI_CBLEFT

39.7.1.34 DECI_LURIGHT

39.7.1.35 DECI_CRRIGHT

39.7.1.36 DECI_CBRIGHT

39.7.1.37 DECI_LUTOP

39.7.1.38 DECI_CRTOP

39.7.1.39 DECI_CBTOP

39.7.1.40 DECI_LUBOTTOM

39.7.1.41 DECI_CRBOTTOM

39.7.1.42 DECI_CBBOTTOM

39.7.1.43 CLIP_LUSEG

39.7.1.44 CLIP_CRSEG

39.7.1.45 CLIP_CBSEG

39.7.1.46 CLIP_FORMAT

39.7.1.47 CLIP_ROTFLIP

39.7.1.48 CLIP_LULEFT

39.7.1.49 CLIP_CRLEFT

39.7.1.50 CLIP_CBLEFT

39.7.1.51 CLIP_LURIGHT

39.7.1.52 CLIP_CRRIGHT

39.7.1.53 CLIP_CBRIGHT

39.7.1.54 CLIP_LUTOP

39.7.1.55 CLIP_CRTOP

39.7.1.56 CLIP_CBTOP

39.7.1.57 CLIP_LUBOTTOM

39.7.1.58 CLIP_CRBOTTOM

39.7.1.59 CLIP_CBBOTTOM

39.7.1.60 VIP_SCANMODE

39.7.1.61 CLIP_YUYVENB

39.7.1.62 CLIP_BASEADDRH

39.7.1.63 CLIP_BASEADDRL

39.7.1.64 CLIP_STRIDEH

39.7.1.65 CLIP_STRIDEL

40 Multi-Format Video Codec

40.1 Overview

40.2 Functional Description

40.2.1 List of Video CODECs

40.2.2 Supported Video Encoding Tools

40.2.3 Supported Video Decoding Tools

40.2.4 Supported JPEG Tools

40.2.5 Non-codec related features

41 3D Graphic Engine

41.1 Overview

41.2 Features

41.2.1 Pixel Processor Features

41.2.2 Geometry Processor Features

41.2.3 Level 2 Cache Controller Features

41.2.4 MMU

41.2.5 PMU

41.3 Operation

41.3.1 Clock

41.3.2 Reset

41.3.3 Interrupt

42 Crypto Engine

42.1 Overview

42.2 Features

42.3 Block Diagram

42.4 Functional Description

42.4.1 Polling Mode

42.4.2 Mode

42.5 Register Description

42.5.1 Register Map Summary

42.5.1.1 CRT_CTRL0

42.5.1.2 AES_CTRL0

42.5.1.3 AES_iv0

42.5.1.4 AES_iv1

42.5.1.5 AES_iv2

42.5.1.6 AES_iv3

42.5.1.7 AES_key0

42.5.1.8 AES_key1

42.5.1.9 AES_key2

42.5.1.10 AES_key3

42.5.1.11 AES_key4

42.5.1.12 AES_key5

42.5.1.13 AES_key6

42.5.1.14 AES_key7

42.5.1.15 AES_TEXTIN0

42.5.1.16 AES_TEXTIN1

42.5.1.17 AES_TEXTIN2

42.5.1.18 AES_TEXTIN3

42.5.1.19 AES_TEXTOUT0

42.5.1.20 AES_TEXTOUT1

42.5.1.21 AES_TEXTOUT2

42.5.1.22 AES_TEXTOUT3

42.5.1.23 DES_CTRL0

42.5.1.24 DES_iv0

42.5.1.25 DES_iv1

42.5.1.26 DES_KEY0_0

42.5.1.27 DES_KEY0_1

42.5.1.28 DES_KEY1_0

42.5.1.29 DES_KEY1_1

42.5.1.30 DES_KEY2_0

42.5.1.31 DES_KEY2_1

42.5.1.32 DES_TEXTIN0

42.5.1.33 DES_TEXTIN1

42.5.1.34 DES_TEXTOUT0

42.5.1.35 DES_TEXTOUT1

42.5.1.36 BDMAR

42.5.1.37 BDMAW

42.5.1.38 HDMAR

42.5.1.39 HASH_CTRL0

42.5.1.40 HASH_iv0

42.5.1.41 HASH_iv1

42.5.1.42 HASH_iv2

42.5.1.43 HASH_iv3

42.5.1.44 HASH_iv4

42.5.1.45 HASH_TEXTOUT0

42.5.1.46 HASH_TEXTOUT1

42.5.1.47 HASH_TEXTOUT2

42.5.1.48 HASH_TEXTOUT3

42.5.1.49 HASH_TEXTOUT4

42.5.1.50 HASH_TEXTIN

42.5.1.51 HASH_MSG_SIZE

42.5.1.52 HASH_MSG_SIZE

43 Electrical Characteristics

43.1 Absolute Maximum Ratings

43.2 Recommended Operating Conditions

43.3 D.C. Electrical Characteristics

1.pdf

Important Notice

Trademarks

Chip Handling Guide

Revision History

Table of Contents

List of Figures

List of Tables

List of Examples

List of Conventions

List of Acronyms

nexell.pdf

Important Notice

Trademarks

Chip Handling Guide

Revision History

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc