第 33卷 第 2期

2010年 4月

电 子 器 件

Chinese Journal of Electron Devices

Vo1.33 No.2

Apr. 2010

Design and Im plem entation of CIC Filter with M atlab and FPGA

L/U Binbin.LIN Wei

(Fufian Key Laboratory ofMicroelectronics& Integrated Circuits,Fuzhou 350002,China)

Abstract:This article describes the design of a CIC filter based on the signal processing theory. Because of its

structure only using the adder and the delay devices without multiplier,it is very suitable for FPGA to achieve the

CIC filter.This article first analyses the theory ,performance and impact parameters of the CIC filter.Then,design

the CIC filter to meet the system requirements with the FDATool of MATLAB.and use simulink to set up a model

and simulate to veilfy whether the perform ance of the CIC filter meets the requirements. In the end,we achieves

the CIC filter of this structure with FPGA,and carries out the simulation,integrated authentication.

Key words:CIC filter;FIR decimation filter;FPGA Matlab

EEA CC :1270

基 于 Matlab和 FPGA 的 CIC滤 波 器 的 设 计 木

刘 彬 彬 ,林 伟

(福 建 省 微 电子 与集 成 电 路 重 点 实 验 室 ,福 州 350002)

摘 要 :基于多速率信号处理原理,设计了用于下变频的 CIC抽取滤波器 ,由于 CIC滤波器结构只用到加法器和延迟器,没

有乘法器 ,很适合用 FPGA来实现 ,所 以本 文分析 了 CIC滤波器的原理 ,性 能及影响参 数 ,借 助 MATLAB的 FDATool工具箱设

计符 合 系统 要 求 CIC滤 波器 ,并 利 用 Simulink结 合 具 体 的 结 构 建 模 仿 真 ,验 证 CIC滤 波 器 性 能 是 否 达 到要 求 ,最 后 在 FPGA 上

实现 这 个 结 构 的 CIC滤 波器 设 计 ,并 进 行 了模 拟 仿 真 ,综 合 验 证 。

关 键 词 :CIC滤波器 ;FIR抽取滤 波器 ;FPGA Matlab

中图分 类号 :TN713

文 献标 识码 :A 文章编 号 :1005-9490(2010)02—0231-04

随 着数字 信号 处 理 技 术 的 发展 ,软件 无 线 电技

术 … 也 出现 了新 的 景象 ,软 件 无 线 电逐 渐 取 代 了传

1 CIC滤 波 器 的原 理

统 的“纯 硬件 电路 ”的无 线通 信 模 式 ,其 思想 是 在 特

1.1 单级 CIC 滤波 器

定 的硬件 平 台上用 软 件 实 现 通信 的功 能 ,但 随 着 采

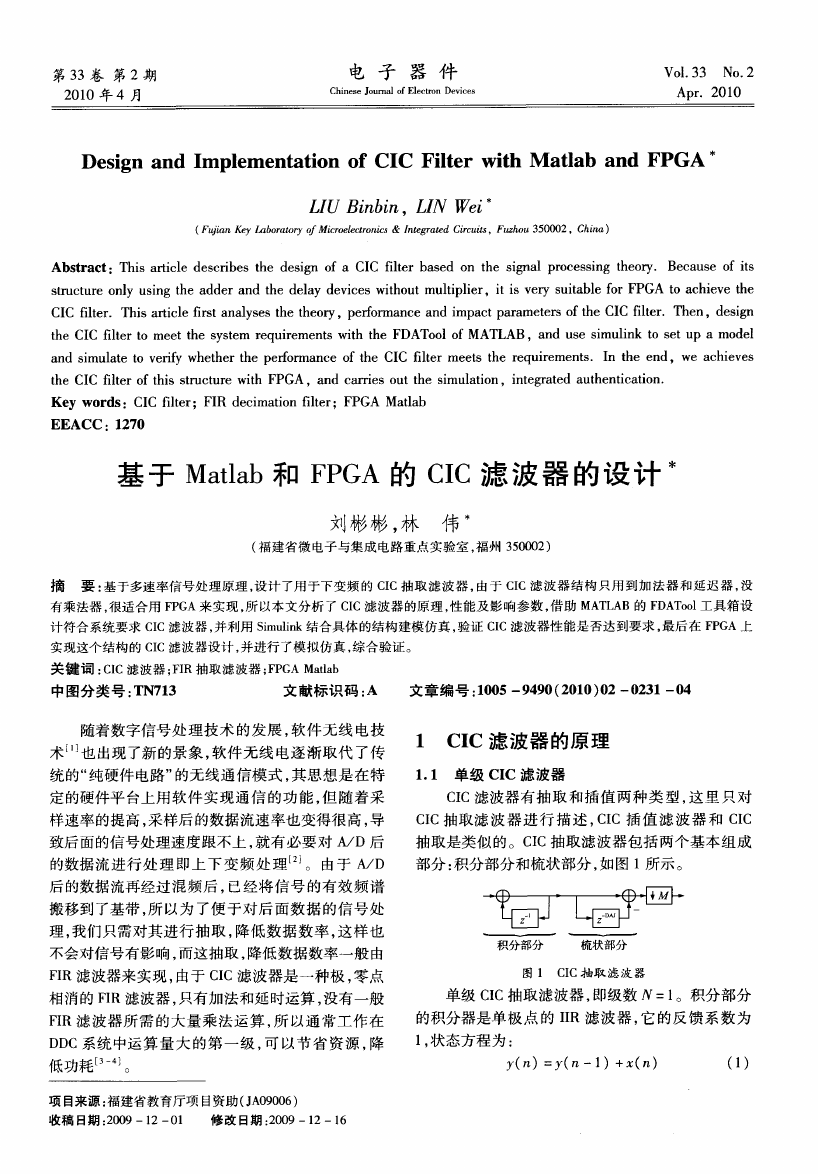

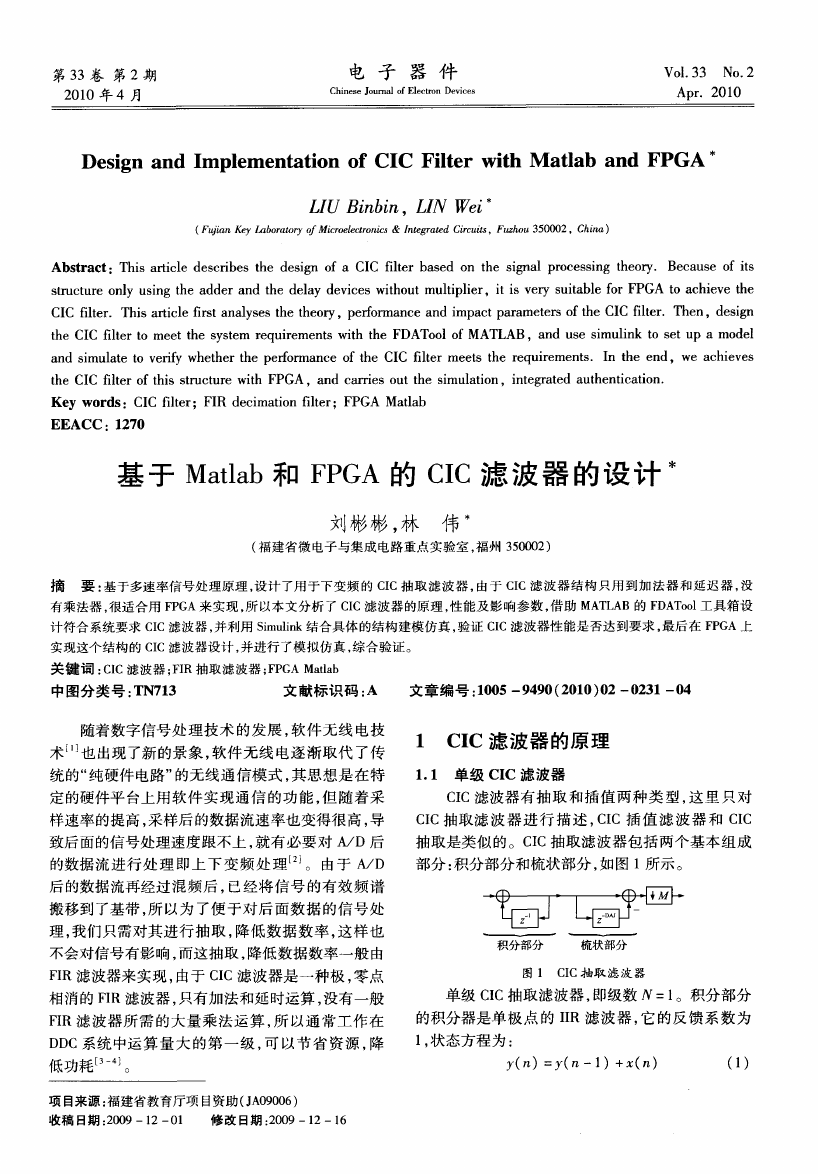

CIC滤 波器 有 抽 取 和 插 值 两 种 类 型 ,这 里 只对

样速 率 的提高 ,采样 后 的数据 流速 率也 变得很 高 ,导

CIC抽取 滤 波 器 进 行 描 述 ,CIC插 值 滤 波 器 和 CIC

致后 面 的信 号处 理速 度跟 不上 ,就 有 必要 对 A/D后

抽取 是类 似 的 。CIC抽 取 滤波 器包 括 两个 基 本组 成

的数据 流进 行 处 理 即 上 下 变频 处 理 。 由于 A/D

部分 :积 分部 分 和梳状 部分 ,如 图 1所 示 。

后 的数据 流再经 过 混 频后 ,已经将 信 号 的有 效 频谱

搬移 到 了基 带 ,所 以为 了便 于对 后 面数 据 的信 号处

理 ,我 们 只需对 其进 行 抽 取 ,降低 数 据数 率 ,这样 也

不会对 信号 有影 响 ,而这抽 取 ,降低数 据数 率一 般 由

FIR滤 波器来 实现 ,由于 CIC滤波 器是 一 种 极 ,零点

积 分 部 分

梳 状 部 分

图 1 CIC 抽 取 滤 波 器

相消 的 FIR滤波 器 ,只有加 法和延 时运算 ,没有 一般

单级 CIC抽 取滤 波器 ,即级 数 N=1。积 分部 分

FIR滤 波 器 所 需 的大 量 乘 法 运算 ,所 以 通 常工 作 在

的积 分器 是单 极 点 的 IIR滤 波 器 ,它 的反 馈 系 数 为

DDC系统 中运算 量 大 的 第 一 级 ,可 以 节 省 资 源 ,降

低 功耗 I4]

1,状 态方 程为 :

Y(n)=Y(n一1)+ (n)

(1)

项 目来 源 :福 建 省 教 育 厅 项 目资 助 (JA09006)

收 稿 日期 :2009—12—01 修 改 日期 :2009—12—16

�

232

电 子 器 件

第 33卷

根据 状态方 程 (1)可 以得 出 积分 器也 可 以看成 是 累

瓣 宽度 以及抽 取后 的数 据 数率 。因此 ,必 须 根 据 工

加器 。根 据 Z变换 ,积分 器 的传输 函数 为 :

程 中对数 据 和时钟速 率 ,通 带带 宽 ,通 带和 阻带 的衰

日l(z)=-

(2)

减 等指标 要求 全面考 虑这 几个参 数 的选取 。

梳状 器是一个 对 称 的 FIR滤 波 器 ,其 状 态方 程 可 以

2 CIC滤 波器 的参 数 设 计 与验 证

表示 为 :

2.1 整个 下变 频 内超 滤 波器模块

),(n)= (n)一 (/Z—DM)

(3)

在 多级 内插 滤波 器 的设 计 时应 考 虑两 点 :一是

在公 式 (3)中 , 为 整数 的频 率变 换 因子 ,D是 微 分

每 级滤 波器 的 通带 宽度 不 能小 于信 号带 宽 ;二 是

延迟 因子 ,D 是滤波 器设计 的一 个重 要参 数 ,可 以用

过 渡带 可变 ,取 决 于每一级 的抽 取倍数 ,即过 渡带 的

来控 制滤 波器 的频 率 响应 ,在 工程 实 践 当中一 般 取

截 止频率 . 不 能大 于该级 的输 出取样 率 的一半 。

值为 1或者 2,称为 微分延 迟 ,其传输 函数 为 :

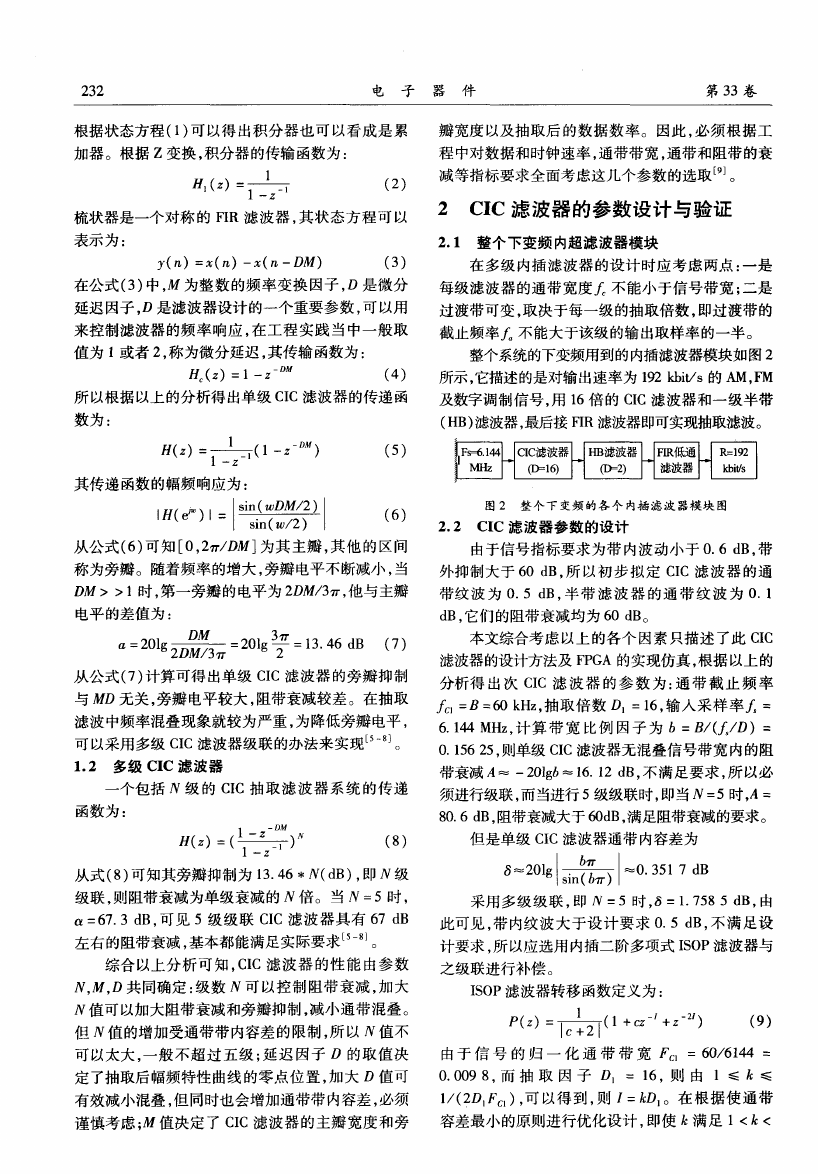

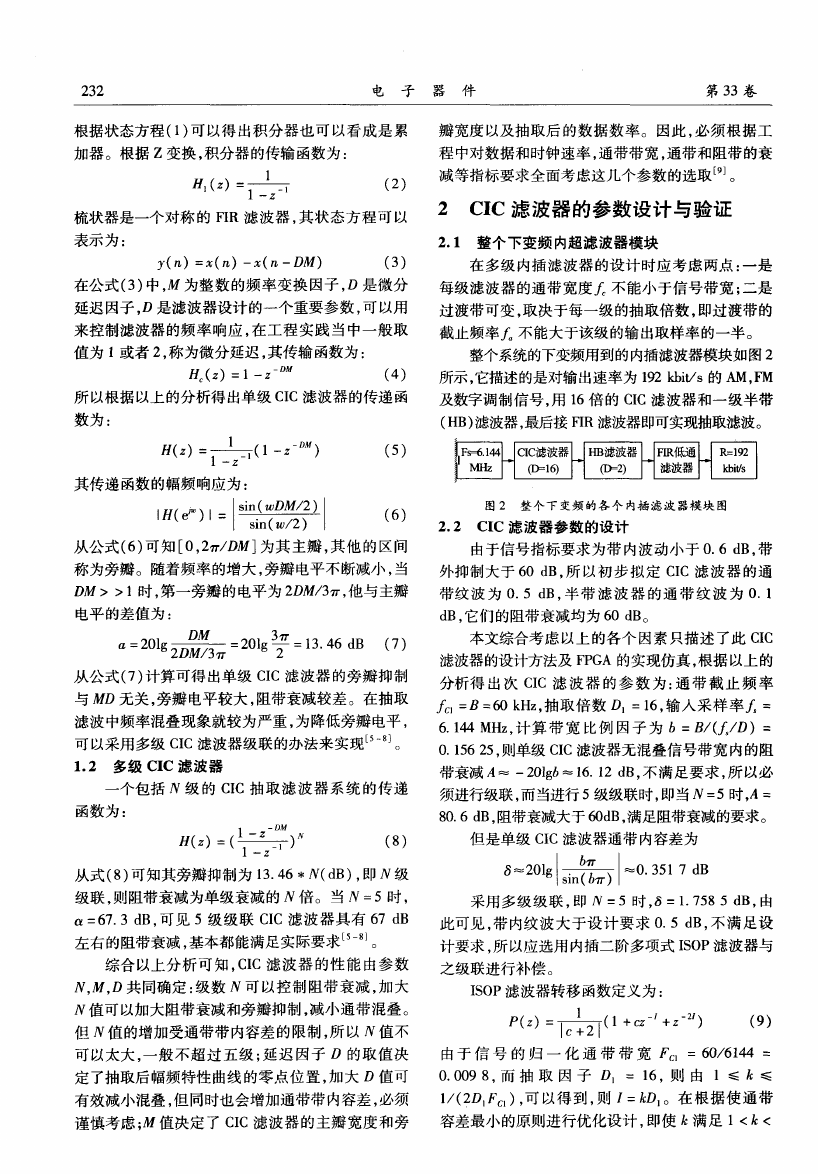

整个系统 的下变频用到 的内插 滤波器模块 如图 2

( )=1一z一删

(4)

所示 ,它描述 的是对输 出速率为 192 kbit/s的 AM,FM

所 以根据 以上 的分析 得 出单级 CIC滤 波器 的传递 函

及数字调 制信 号 ,用 16倍 的 CIC滤 波器 和一 级 半带

数 为 :

(HB)滤波器 ,最后接 FIR滤波器 即可实现抽取滤波。

H( )=七 (1一 一删)

(5)

其传 递 函数 的幅频 响应 为 :

删 =I l (6)

IⅣ(e, )I=I :; l (6)

2.2 CIC滤 波器 参数 的设计

图 2 整 个 下 变 频 的 各 个 内 插 滤 波 器 模 块 图

从公式(6)可知[0,27r/ ]为其主瓣 ,其他的区间

由于信号 指标要 求 为带 内波动 小 于 0.6 dB,带

称 为旁瓣 。随 着频率 的增 大 ,旁 瓣 电平不 断减小 ,当

外 抑制 大于 60 dB,所 以初 步 拟 定 CIC滤 波 器 的通

DM >>1时 ,第 一旁瓣 的电平 为 2DM/3rr,他 与主瓣

带 纹 波 为 0.5 dB,半 带 滤 波 器 的 通 带 纹 波 为 0.1

电平 的差 值为 :

。 =201g D M

= 20lg =13.46 dB (7)

从公 式 (7)计算 可得 出单 级 CIC滤 波 器 的旁瓣 抑 制

与 MD无关 ,旁瓣电平较大 ,阻带衰减较差。在抽取

滤 波 中频 率混 叠现 象就 较为严 重 ,为降低 旁瓣 电平 ,

可 以采用 多级 CIC滤 波器 级联 的办法 来实 现 H8_。

1.2 多级 CIC滤 波器

一 个 包括 Ⅳ 级 的 CIC抽 取 滤 波 器 系统 的传 递

函数为 :

1

一DM

H( ):(

.

)

dB,它 们 的阻带 衰减均 为 60 dB。

本文综合 考虑 以上 的各个 因素 只描 述 了此 CIC

滤 波器的设计方法及 FPGA的实 现仿真 ,根据 以上 的

分 析得 出次 CIC滤 波 器 的参 数 为 :通 带 截 止 频 率

A。=B=60 kHz,抽 取 倍 数 D =16,输 入 采 样 率 =

6.144 MHz,计 算 带 宽 比例 因子 为 b=B/(f/D)=

0.156 25,则单级 CIC滤波 器无 混叠信 号带 宽 内的 阻

带 衰减 A一 一201gb 16.12 dB,不满 足要 求 ,所 以必

须 进行级联 ,而 当进行 5级级联 时 ,即当 N=5时 ,A=

80.6 dB,阻带衰减大 于 60dB,满足阻带 衰减 的要求 。

(8)

但 是单 级 CIC滤波器 通带 内容差 为

l ^一 I

从 式 (8)可知 其旁 瓣抑制 为 13.46 N(dB),即 Ⅳ级

级联 ,则阻带 衰减 为单 级衰减 的 Ⅳ倍 。 当 N=5时 ,

~201gI__

l 0.351 7 dB

I sin O"/T J l

采用 多级 级联 ,即 N=5时 ,6=1.758 5 dB,由

= 67.3 dB,可见 5级 级 联 CIC滤波 器 具 有 67 dB

此可 见 ,带 内纹 波 大 于 设 计 要 求 0.5 dB,不 满 足设

左 右 的阻带 衰减 ,基本都 能满 足实 际要求 _5 。

计要 求 ,所 以应选 用 内插二 阶多项 式 ISOP滤波 器与

综 合 以上 分 析 可 知 ,CIC滤 波器 的性 能 由参 数

之级 联进行 补偿 。

Ⅳ, ,D共 同确定 :级 数 Ⅳ可 以控制 阻带 衰 减 ,加 大

Ⅳ值 可 以加 大 阻带衰减 和旁 瓣抑 制 ,减 小 通带 混叠 。

但 Ⅳ值 的增加 受通 带带 内容 差 的限制 ,所 以 Ⅳ值不

ISOP滤 波器 转移 函数定 义为 :

1

一

..

P(z)=1__÷ (1+cz + )

l C 十 二 I

(9)

可以太 大 ,一 般 不 超 过 五 级 ;延 迟 因子 D 的取 值 决

由于 信 号 的 归 一 化 通 带 带 宽 F 。=60/6144 :

定 了抽 取后 幅频特 性 曲线 的零 点 位 置 ,加大 D 值可

0.009 8,而 抽 取 因 子 D = 16,则 由 1≤ k≤

有 效减 小混 叠 ,但 同时也 会增 加通 带带 内容 差 ,必须

l/(2D。F ),可 以得 到 ,则 ,=kD 。在 根 据 使 通 带

谨慎考虑 ; 值决定 了 CIC滤波器的主瓣宽度和旁

容差 最小 的原则 进行优 化设 计 ,即使 k满 足 1

第 2期

刘彬彬 ,林 伟 等 :基 于 Matlab和 FPGA的 CIC滤 波器 的设计

233

4,而本 文 是通过 FDATool设计 ISOP滤 波器 的 ,通 过

调节 它 的参数满 足 性 能 的要 求 的 ,不 过 补 偿 是 以减

3 CIC 滤 波 器 的 FPGA 实 现

小阻 带衰减 为代 价 的 。

本文是 采 用 Verilog语 言描 述 ,在 Xilinx ISE9.1

从 以上 的分析综 合 :本 文选 用 5级 级联 的 CIC滤

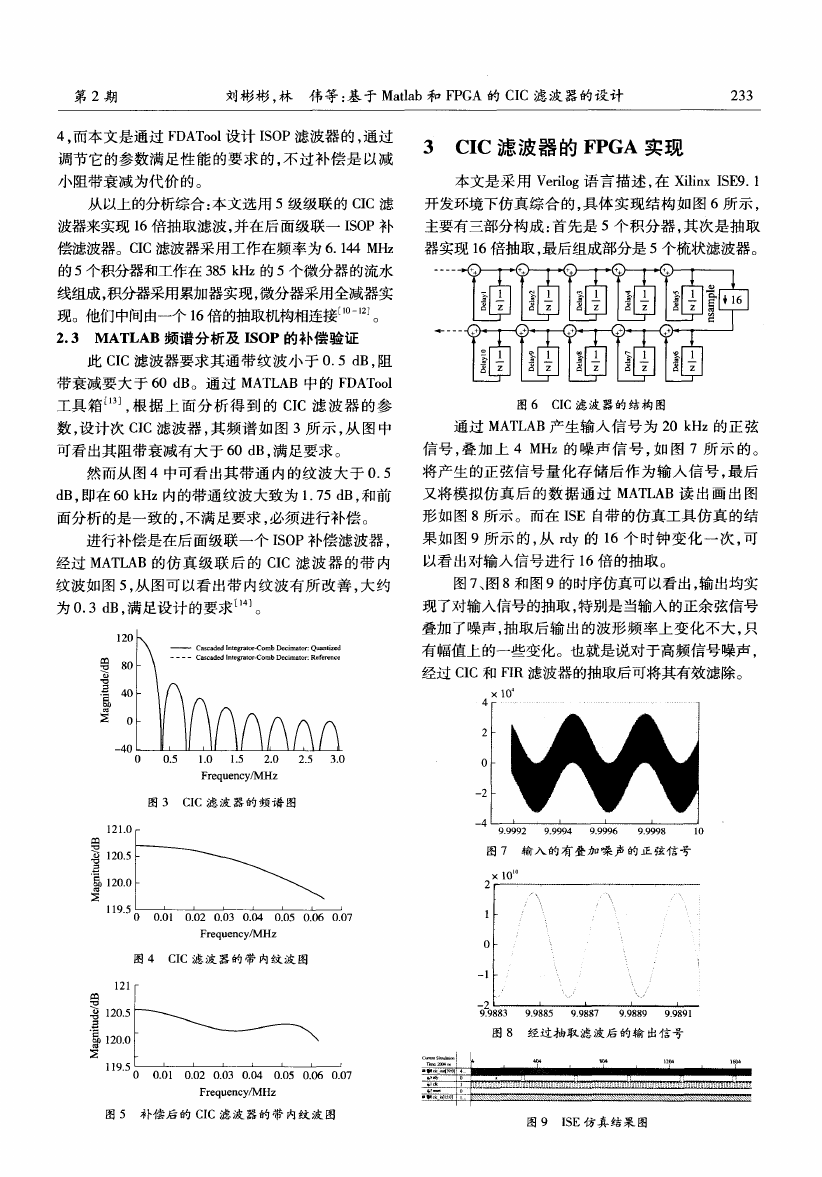

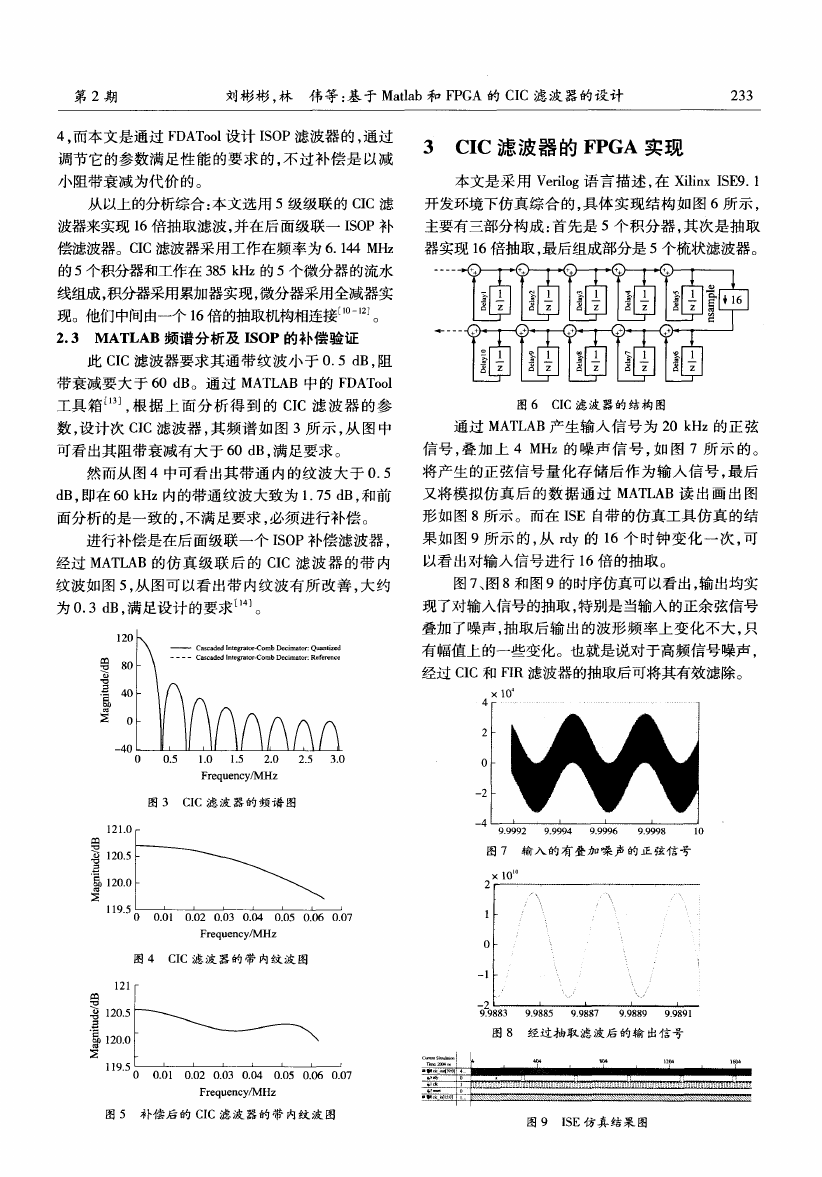

开发环境 下仿 真综 合 的 ,具体 实 现 结构 如 图 6所示 ,

波器来实现 16倍抽 取滤 波 ,并在后 面 级联一 ISOP补

主要有 三部 分构 成 :首先 是 5个 积分 器 ,其次 是 抽取

偿滤 波器 。CIC滤波器采 用工 作在 频率 为 6.144 MHz

器实现 16倍 抽取 ,最后组 成部分是 5个梳状滤波器 。

的 5个积分器和工 作在 385 kHz的 5个微 分器 的流水

线组成 ,积 分器采用累加器实现 ,微分器 采用全减 器实

现 。他们中间由一个 16倍 的抽取机构相连接 1 』。

2.3 MATLAB频谱 分析 及 ISOP的补偿 验证

此 CIC滤波 器要 求其 通 带纹 波 小 于 0.5 dB,阻

带 衰减要 大 于 60 dB。通 过 MATLAB 中的 FDATool

工具 箱 _】 ,根 据 上 面 分 析 得 到 的 CIC滤 波 器 的参

图 6 CIC 滤 波 器 的 结 构 图

数 ,设 计 次 CIC滤波器 ,其 频 谱 如 图 3所 示 ,从 图 中

通 过 MATLAB产 生输人 信 号 为 20 kHz的 正 弦

可看 出其 阻带 衰减有 大 于 6O dB,满 足要 求 。

信 号 ,叠 加 上 4 MHz的 噪 声 信 号 ,如 图 7所 示 的。

然而从 图 4中可看 出其 带 通 内的纹 波 大 于 0.5

将产 生 的正 弦信 号量 化 存 储 后 作 为输 入 信 号 ,最 后

dB,即在 60 kHz内的带通 纹波 大致 为 1.75 dB,和前

又将 模拟 仿 真 后 的数 据 通 过 MATLAB读 出画 出图

4 2 0

4

面分 析 的是 一致 的 ,不 满 足要求 ,必须 进行 补偿 。

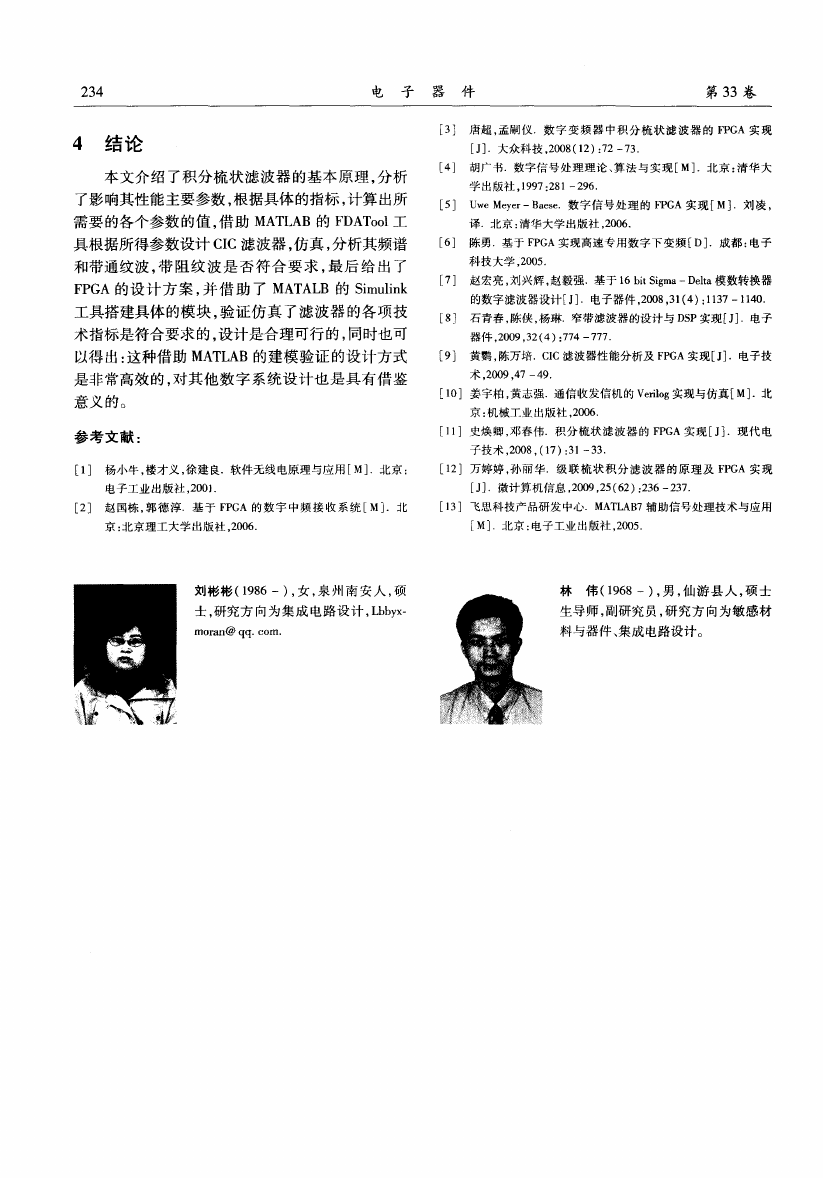

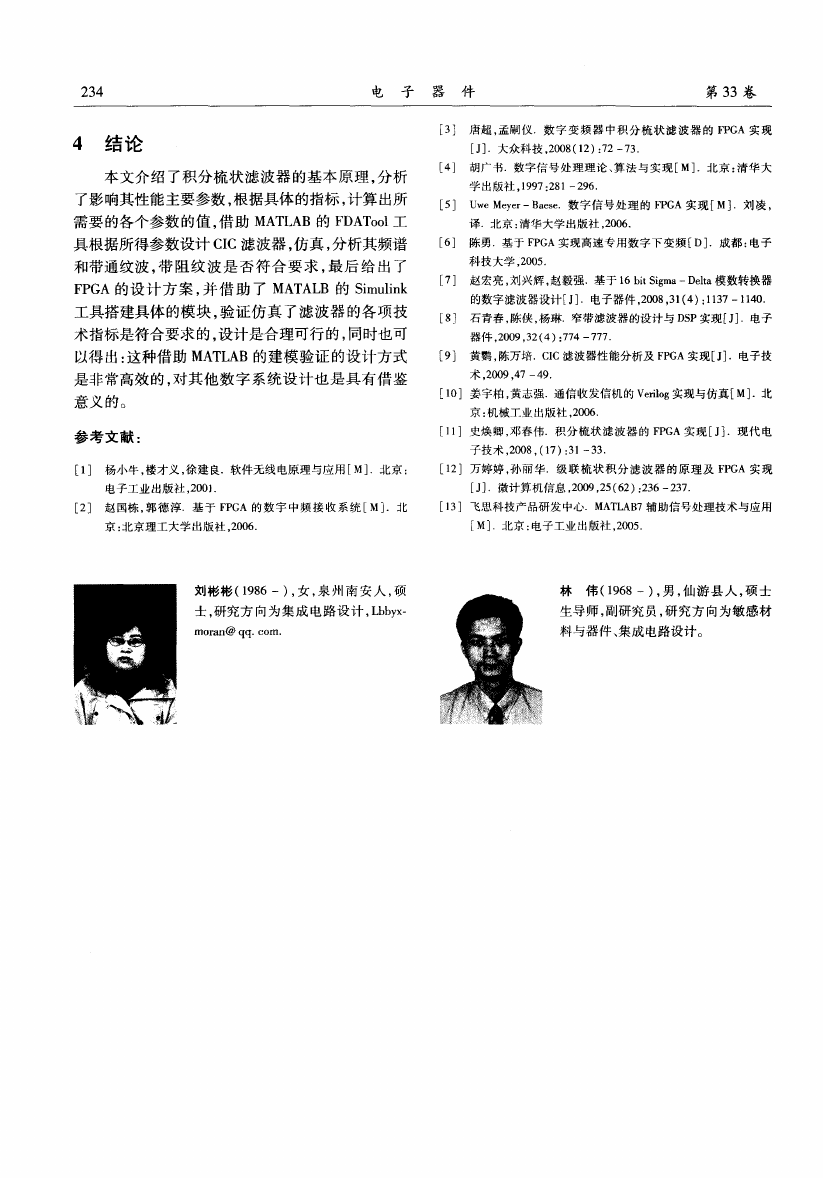

形如 图 8所 示 。而 在 ISE 自带 的仿 真工具 仿 真 的结

进 行补偿 是 在后 面级联 一个 ISOP补偿 滤 波器 ,

果如 图 9所 示 的 ,从 rdy的 16个 时 钟 变 化 一 次 ,可

经 过 MATLAB的仿 真级 联 后 的 CIC滤 波 器 的带 内

以看 出对输 入 信号进 行 l6倍 的抽 取 。

纹 波如 图 5,从 图可 以看 出带 内纹 波 有 所 改善 ,大 约

图 7、图 8和图 9的时序仿 真可 以看 出 ,输 出均实

为 0.3 dB,满 足设 计 的要 求 。

现了对输入信 号的抽取 ,特 别是 当输 入 的正 余 弦信号

叠 加 了噪声 ,抽 取后 输 出的波 形频 率 上变 化 不大 ,只

有 幅值上 的一些 变化 。也 就是说对 于高频 信号 噪声 ,

经过 CIC和 FIR滤波器 的抽 取后可将 其有效滤 除。

× 1 04

Frequency/M Hz

图 3 CIC 滤 波 器 的频 谱 图

Frequency/M H z

图 4 CIC滤 波 器 的 带 内纹 波 图

9.9992 9.9994 9.9996 9.9998

10

图 7 输入 的 有 叠 加 噪 声 的 正 弦信 号

图 8 经过 抽 取 滤 波后 的 输 出信 号

Frequency/M Hz

图 5 补 偿 后 的 CIC滤 波 器 的 带 内纹 波 图

图 9 ISE仿 真 结果 图

�

234

电 子 器 件

第 33卷

4 结论

本文 介绍 了积 分梳 状 滤 波器 的基本 原 理 ,分 析

了影 响其性 能 主要参数 ,根 据具 体 的指标 ,计 算 出所

[3] 唐超 ,孟嗣仪.数 字 变频器 中积分 梳状滤 波器 的 FPGA实 现

[J].大众科技 ,2008(12):72—73.

[4] 胡 广 书 .数 字 信 号 处 理 理 论 、算 法 与 实 现 [M].北 京 :清 华 大

学 出 版社 ,1997:281—296.

[5] Uwe Meyer—Baese.数字 信号处理 的 FPGA实现 f M].刘凌 ,

需 要 的各个参 数 的值 ,借 助 MATLAB的 FDATool工

译 .北 京 :清 华 大 学 出 版社 ,2006.

具 根据 所得参 数设 计 CIC滤 波器 ,仿真 ,分析 其频谱

[6] 陈勇.基于 FPGA实现高速专用数字 下变频 [D].成都 :电子

和带 通纹波 ,带 阻 纹 波 是 否 符 合 要 求 ,最 后 给 出 了

FPGA的设 计 方 案 ,并 借 助 了 MATALB的 Simulink

工具 搭建具 体 的模 块 ,验 证仿 真 了滤 波 器 的各 项 技

科 技 大学 ,2005.

[7] 赵宏亮 ,刘兴辉 ,赵毅强.基于 l6 bit Sigma—Delta模数转换器

的数字滤波器设计 [J].电子器件 ,2008,31(4):1137—1140.

[8] 石青春 ,陈侠,杨琳.窄带滤波器的设计与 DSP实现 [J].电子

术指 标是符 合要 求 的 ,设计 是合 理可行 的 ,同时也 可

器 件 ,2009,32(4):774—777.

以得 出 :这种 借助 MATLAB的建模 验 证 的设 计 方 式

[9] 黄鹦 ,陈万培 .CIC滤波器性能分析及 FPGA实现 [J].电子技

是非 常高效 的 ,对其 他 数 字 系统 设 计 也是 具 有 借 鉴

术 ,2009,47~49.

意 义的 。

参考 文献 :

[1O]姜宇柏 ,黄志强.通信收发信机的 Verilog实现 与仿真 [M].北

京 :机 械 丁 业 出版 社 ,2006.

[11]史焕卿 ,邓 春伟.积 分梳状滤波器 的 FPGA实现 [J].现代 电

子 技 术 ,2008,(17):31—33.

杨小牛 ,楼才义 ,徐 建良.软件无线 电原理 与应用 [M].北京 :

[12]万婷婷 ,孙丽华.级 联梳状 积分 滤波器 的原 理及 FPGA实现

电 子 工业 出版 社 ,2001.

[J].微计算机信息 ,2009,25(62):236—237,

[2]

赵国栋,郭德 淳.基 于 FPGA 的数 字 中频接 收 系统 [M].北

[13]飞思科技产品研发 中心.MATLAB7辅助信号处理技术与应用

京 :北 京 理 工大 学 出版 社 ,2006.

[M].北京 :电子工业出版社 ,2005.

刘 彬 彬 (1986一),女 ,泉 州 南 安 人 ,硕

林 伟 (1968一),男 ,仙 游 县 人 ,硕 士

士 .研究方 向为集 成 电路设计 ,Lbbyx—

生 导 师 ,副 研 究 员 ,研 究 方 向 为 敏 感 材

moran@ qq.CO1TI.

料 与 器件 、集 成 电 路 设 计 。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc