期

第

!"

$%%&

卷第

年

$

#

月

南 京 航 空 航 天 大 学 学 报

’()*+,-(./,+01+23+145*6178(.95*(+,)71:6; 967*(+,)71:6

<(-=!"/(=#

?5@=$%%&

>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>

>

全并行结构

的

AAB

ACDE

实现

王旭东 刘 渝

南京航空航天大学信息科学与技术学院

F

南京

G

G$#%%#&H

摘 要

提出了一种基于

I

?JK9

实现的全并行结构

??L

设计方法

采用

G

描 述语言

和图形输入相结合的方法

中完成设计的输入

在

G

NST&U#

通过利用

结果表明

Z

G

?JK9

MNON/M

综合

V

V

公司最新器件

<1*75PNNJ*(G

用硬件

编译及布局布线

并用

W(X5-S1Y

逻 辑 单 元 及 存 储 器 等 硬 件 资

G

器件中大 量 的 乘 法 器

V

第

期

5

王旭东

等

%

全并行结构

Y

的

&&’

&$AB

实现

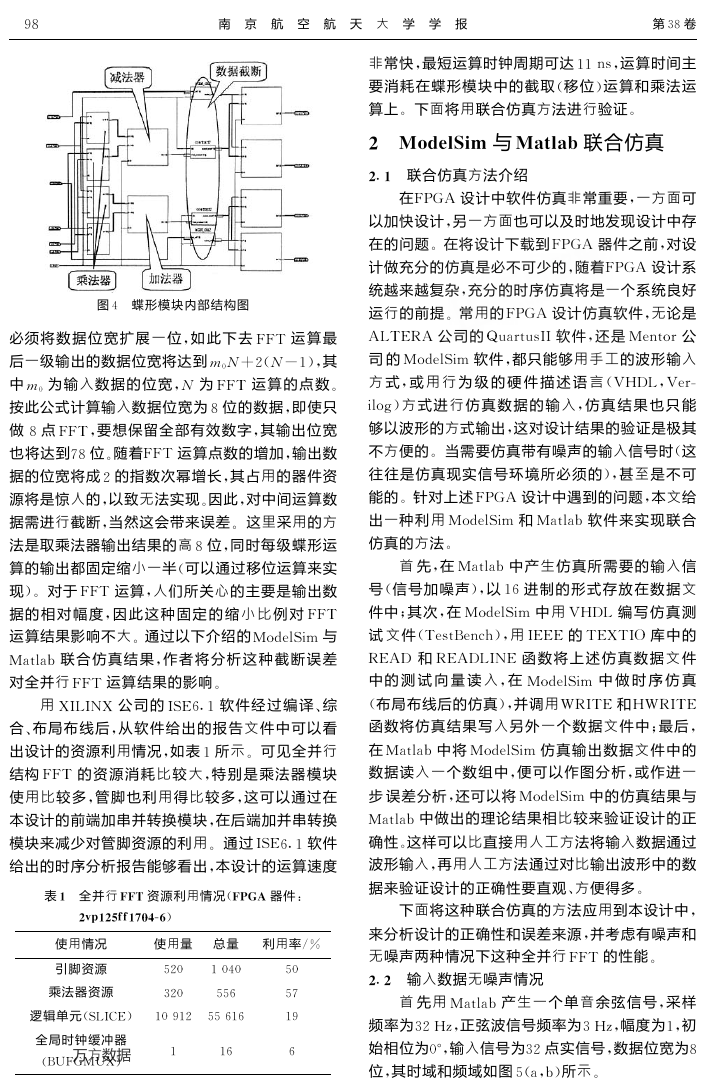

cF

脚是 设 计 的 输 入 管 脚

这 里 采 用 的 数 据 位 宽 为

%

]

位

右边是输出管脚

Z

数据位宽也是

%

位

]

中间是结

Z

构完全相同的蝶形模块

其输入输出管脚如图

%

所

C

位的复数输入信号和一个复数的

以 及 时 钟 输 入 信 号

输 出 则 是

%

示

输入是两个

(

]

旋转因子 输 入 信 号

%

两个复数的运算结果

(

器向导

的方法指定用

!

"#$

模块生成乘法器

用这

%

种乘 法 器 来 做 蝶 形

然 后 用 多 个 蝶 形 来 构 成

&&’

核心运算的

设 计 的 输 入 采 用 硬 件 描 述 语 言

%

再将多级串连

运算级

%

即可实现

%

&&’

全 并行流 水 结 构

)*"+,-.和图形输入相结合的方法

司的 软 件

%

中 完 成 设 计 的 输 入

(

在

0#2345

编 译

布 局 布 线 等 操 作

%

最 后 用

%

软件对设计做了联合仿真

行 综 合

软件和

6

6

7>?;>@

公

/0+01/

并 对 设 计 进

789:;#<=

结果表

(

明

通过利用

%

&$AB

器件中大量 的 乘 法 器

逻 辑 单

6

采用全并行加流水结构

点

C-

运算的功能

&&’

可 对 采 样 速 率 为

可

%

设

%

-4F

6

元

存储器等硬件资源

%

在一个时钟节拍内完成

计最 高 运 算 速 度 可 达

55DE%

的输入数据进行实时处理

(

A*G

H

H4H

算法及

实现

IJKL

全并行

算法介绍

IIM

算法公式为

"&’

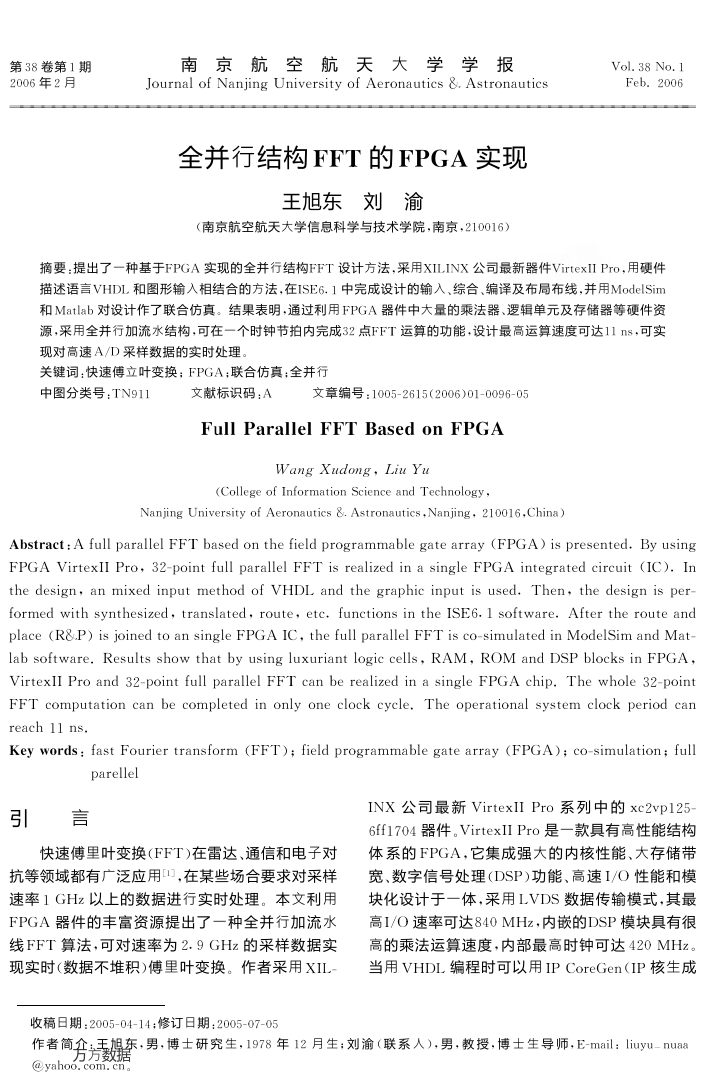

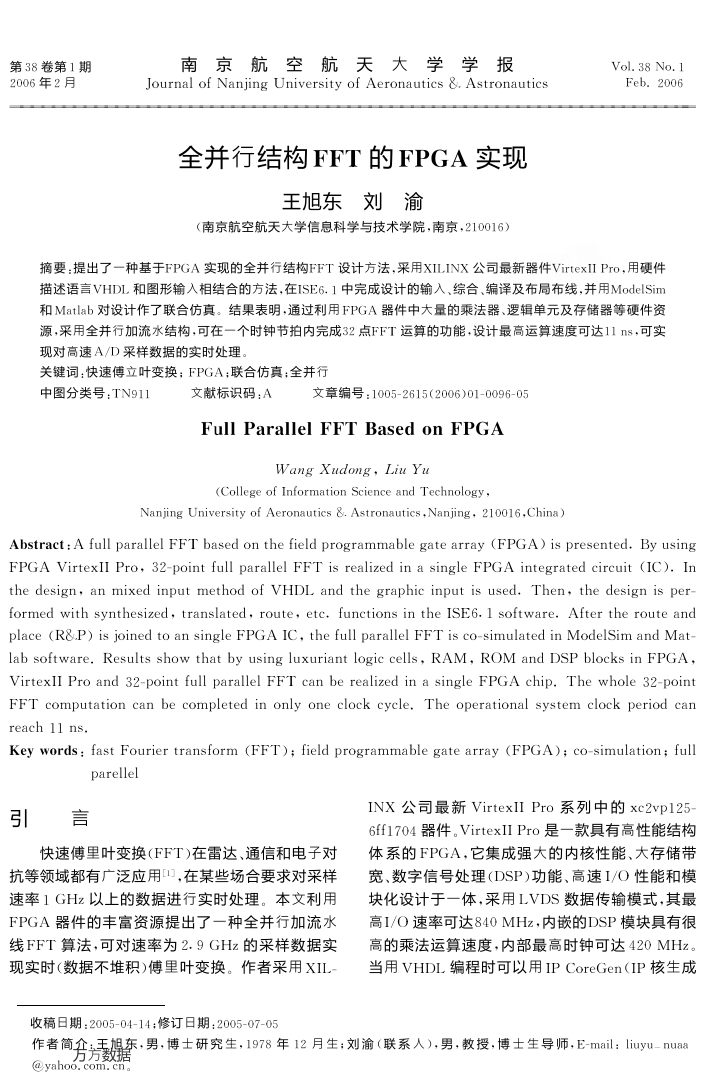

为了作图的方便

这里以基

%

时间抽

-

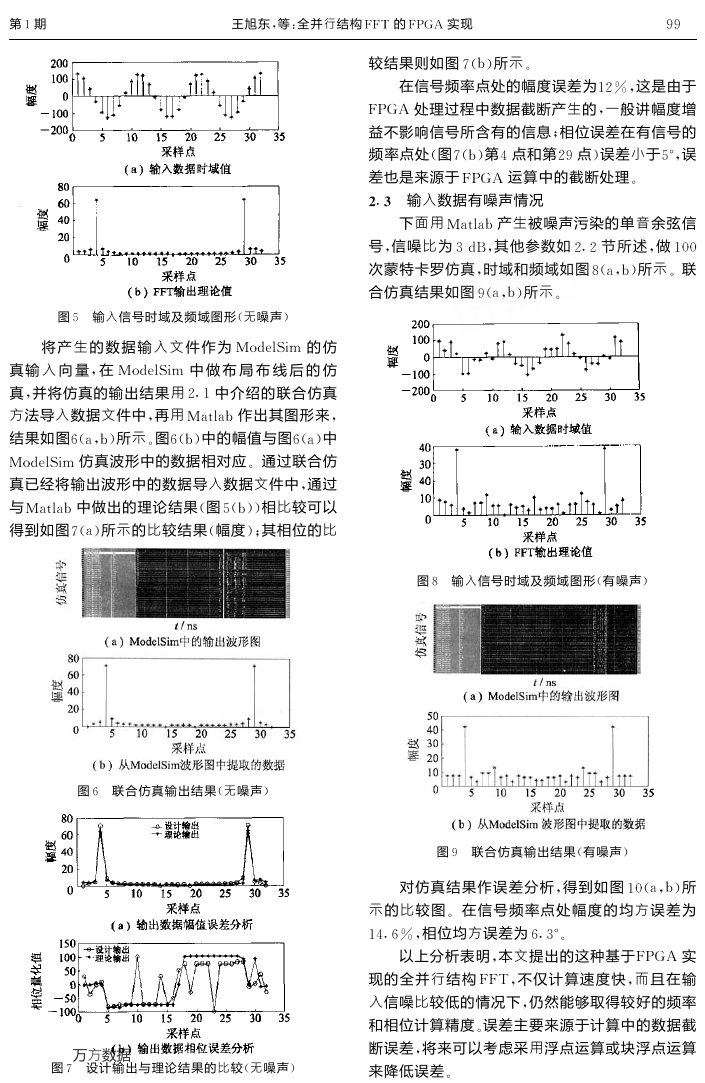

图

-

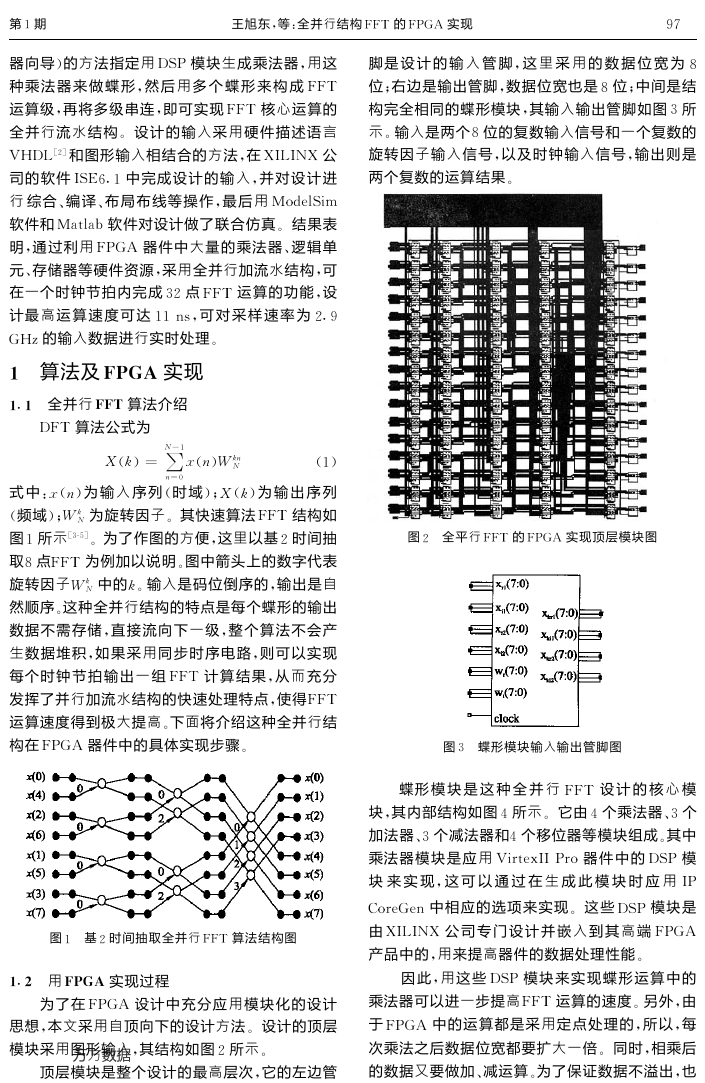

全平行

的

&&’

&$AB

实现顶层模块图

ST 5

NOP!Q R

为 输 入 序 列

UQ V

时 域

O

(

WOU!XPU

S

O5!

!ZNOP!

为 输 出 序 列

为旋转因子

其快速算法

结构如

&&’

式 中

频域

YWOU!

!ZXP

所示 ,C[\.(

点

S

&&’

5

]

O

图

取

为例加以说明

图中箭头上的数字代表

(

旋转因子

中的

输入是码位倒序的

XP

S

P(

输出是自

%

然顺序

这种全并行结构的特点是每个蝶形的输出

(

数据不需 存 储

直 接 流 向 下 一 级

%

整 个 算 法 不 会 产

%

生数据堆 积

如 果 采 用 同 步 时 序 电 路

则 可 以 实 现

%

每个 时 钟 节 拍 输 出 一 组

%

计 算 结 果

&&’

从 而 充 分

%

&&’

下面将介绍这种全并行结

%

发挥了并行加流水结构的快速处理特点

使得

运算速度得到极大提高

(

构在

&$AB

器件中的具体实现步骤

(

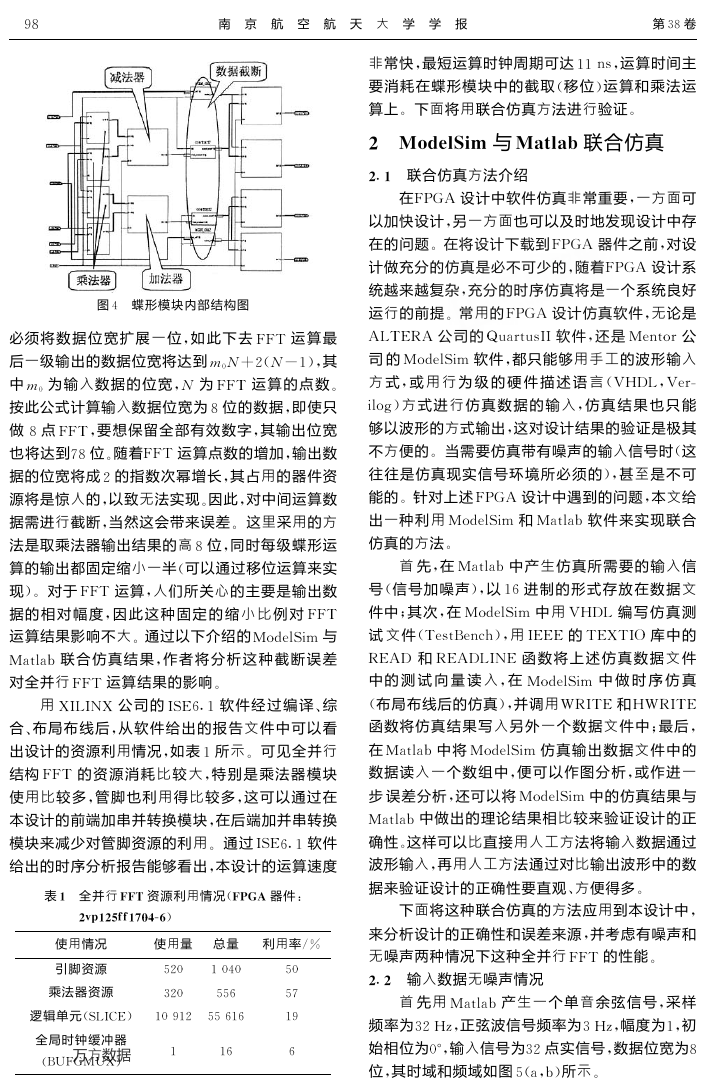

图

C

蝶形模块输入输出管脚图

蝶形 模 块 是 这 种 全 并 行

设 计 的 核 心 模

块

其内部结构如图

所示

%

加法器

_

个减法器和

6C

_

乘法 器 模 块 是 应 用

&&’

它由

_

(

个乘法器

个移位器等模块组成

个

6C

其中

(

模

器 件 中 的

"#$

这 可 以 通 过 在 生 成 此 模 块 时 应 用

)<‘?:a00$‘8

%

中相应的 选项来实现

这些

"#$

公 司 专 门 设 计 并 嵌 入 到 其 高 端

(

0$

模块 是

&$AB

块 来 实 现

b8‘:A:D

由

/0+01/

产品中的

用来提高器件的数据处理性能

%

(

模 块 来 实 现 蝶 形 运 算 中 的

因 此

用 这 些

"#$

乘法器可以进一步提高

%

&&’

运算的速度

另外

(

中的运 算都是采用定 点 处 理 的

所 以

由

%

每

%

%

同时

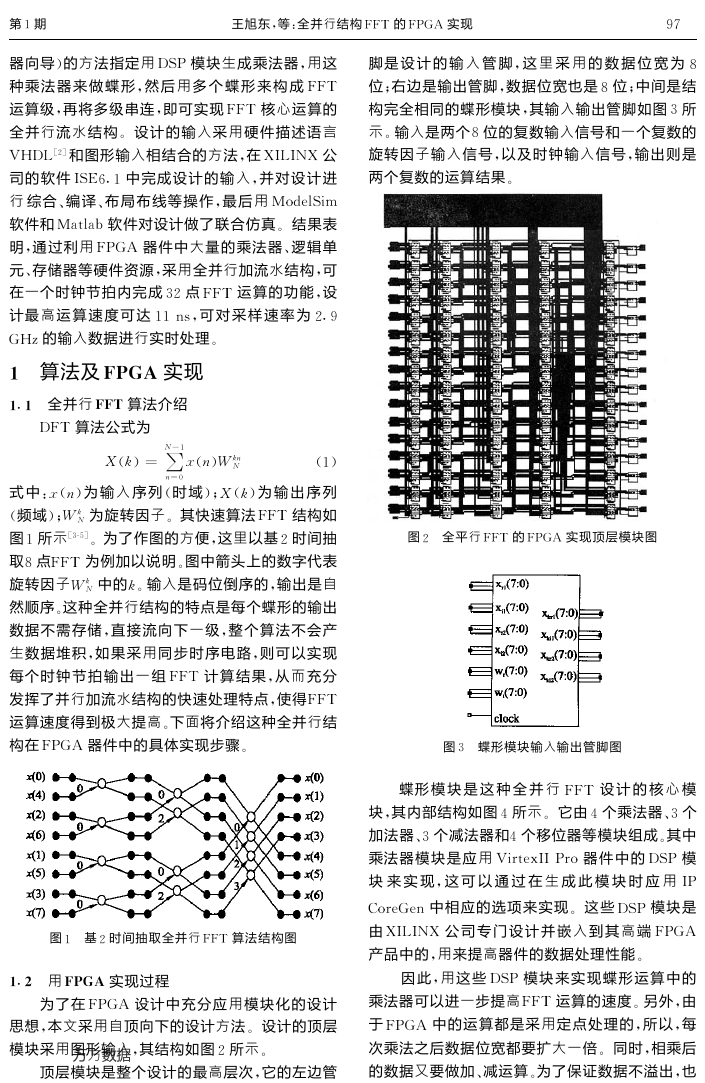

设计的顶层

于

&$AB

(

它的左边管

%

次乘法之后数据位宽都要扩大一倍

(

相乘后

%

的数据又要做加

减运算

6

为了保证数据不溢出

(

也

%

图

5

基

时间抽取全并行

-

&&’

算法结构图

用

H4^

IJKL

实现过程

为了在

设计 中充 分 应 用 模 块 化 的 设 计

&$AB

思想

本文采用自顶向下的设计方法

%

模块采用图形输入

万方数据

其结构如图

%

-

顶层模块是整个设计的最高层次

(

所示

�

/Z

南 京 航 空 航 天 大 学 学 报

第

卷

X/

非常快

最短运算时钟周期可达

"

,,^_"

运算时间主

要 消 耗在蝶形模块中的 截 取

移 位

运 算 和 乘 法 运

*

-

算上

.

下面将用联合仿真方法进行验证

.

K ‘abcdefg

与

联合仿真

‘hidhj

联合仿真方法介绍

KBD

在

#k]l

设计中软件仿真非常重要

一方面可

"

以加快设计

另一方面也可以及时地发现设计中存

在的问题

.

"

在将设计下载到

#k]l

器件之前

对设

"

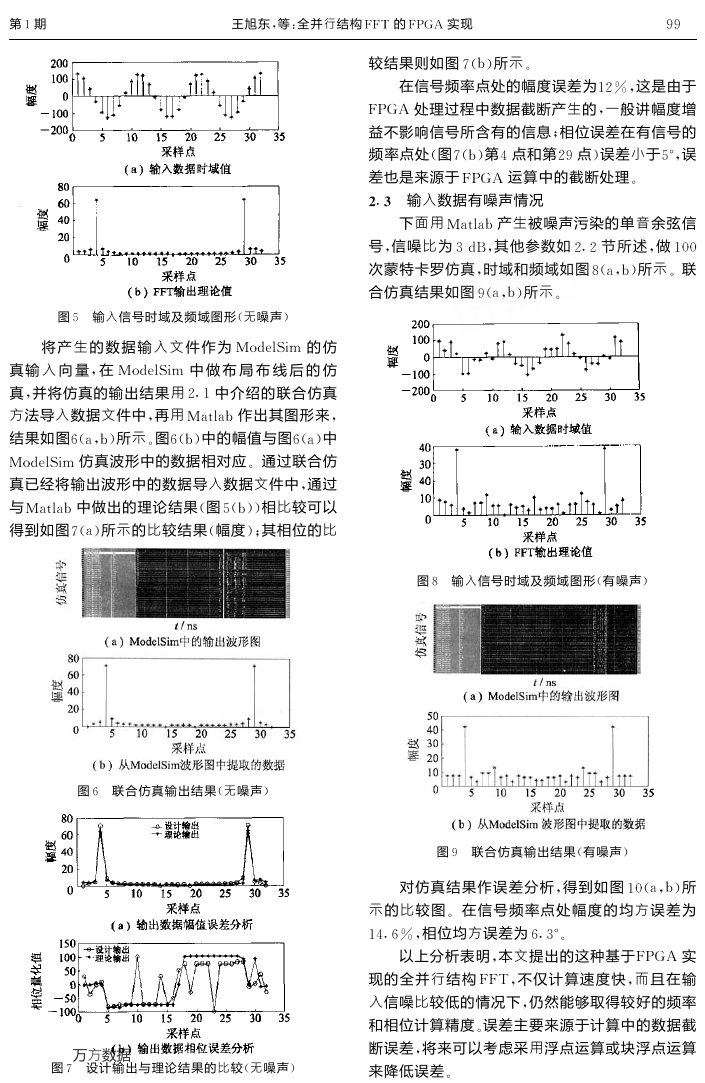

图

!

蝶形模块内部结构图

运行的前提

计做充分的仿真是必不可少的

随着

"

#k]l

设计系

统越来越复杂

充分的时序仿真将是一个系统良好

"

常用的

.

公 司 的

#k]l

no9p:o_==

设计仿真软件

无论是

"

软 件

还 是

"

公

14^:2p

软件

都只能够用手工的波形输入

l>$@ml

司 的

必须 将 数 据 位 宽 扩 展 一 位

如 此 下 去

"

##$

运 算 最

后一级输出的数据位宽将达到

中

为 输 入 数 据 的 位 宽

%&

"’

按此公式计算输入数据位宽为

其

%&’()*’+,-"

运 算 的 点 数

为

##$

位的数据

/

即使只

"

其输出位 宽

"

方 式

.

"

12345678

或 用 行 为 级 的 硬 件 描 述 语 言

"

方 式 进 行 仿 真 数 据 的 输 入

752u-

够以波形的方式输出

*qrs>"q4pt

仿 真 结 果 也 只 能

"

这对设计结果的验证是极其

"

出设计的资源利用情况

如表

"

所示

,

.

可见全并行

在

中 将

19:59;

12345678

仿 真 输 出 数 据 文 件 中 的

做

点

/

也 将达到

##$"

位

0/

据的位宽将成

源将是惊人的

据需进行截断

要 想保留 全部有效数字

随着

.

##$

运算点数的增加

输出数

"

的指数次幂增长

其占用的器件资

)

以致无法实现

"

因此

.

"

当然这会带来误差

"

对中间运算数

"

这里采用的方

.

同时每级蝶形运

法是取乘法器输出结果的高

位

/

"

算的输出都固定缩小一半

可以通过移位运算来实

*

现

-.

对于

##$

运算

人们所关心的主要是输出数

"

据的 相 对 幅 度

因 此 这 种 固 定 的 缩 小 比 例 对

"

19:59;

对全并行

运算结果影响不大

通过以下介绍的

.

12345678

联 合 仿 真 结 果

作 者 将 分 析 这 种 截 断 误 差

"

运算结果的影响

##$

用

<=>=?<

=6@AB,

公 司 的

.

软 件 经 过 编 译

综

C

合

布局 布 线 后

从 软 件 给 出 的 报 告 文 件 中 可 以 看

C

"

##$

与

结构

##$

使用比较 多

的 资 源 消 耗 比 较 大

特 别 是 乘 法 器 模 块

"

管 脚 也 利 用 得 比 较 多

"

这 可 以 通 过 在

"

本设计的前端加串并转换模块

在后端加并串转换

"

模块来减少对管脚资源的利用

通过

.

软件

=6@AB,

给出的时序分析报告能够看出

本设计的运算速度

"

表

D

全并行

资源利用情况

EEF

*EGHI

器件

J

KLMDKNOODPQRST-

使用情况

使用量 总量

利用率

引脚资源

乘法器资源

W)& ,&!&

X)&

WWA

逻辑单元

*6>=Y@- ,&Z,) WWA,A

全局时钟缓冲器

万方数据

*[\#]1\<-

,

,A

W&

W0

,Z

A

不方便的

.

当需要仿真带有噪声的输入信号时

这

*

往 往是 仿真现实 信 号 环 境 所 必 须 的

甚 至 是 不 可

-"

能的

针对上述

.

#k]l

设计中遇到的问题

本文给

"

12345678

和

软 件 来 实 现 联 合

19:59;

出一种 利 用

仿真的方法

.

在

首 先

中 产 生 仿 真 所 需 要 的 输 入 信

信 号 加 噪 声

以

进 制 的 形 式 存 放 在 数 据 文

"

19:59;

号

*

件中

v

试 文 件

其 次

在

"

-"

,A

12345678

用

中 用

编 写 仿 真 测

qrs>

的

库 中 的

*$4_:[4^wx-"

和

=@@@

函 数 将 上 述 仿 真 数 据 文 件

$@<$=y

m@ls

中 的 测 试 向 量 读 入

m@ls>=?@

在

"

12345678

中 做 时 序 仿 真

布局布线后的仿真

并调用

*

函 数将仿 真 结 果 写 入 另 外 一 个 数 据 文 件 中

zm=$@

-"

和

rzm=$@

最 后

v

"

数 据读入 一 个 数 组 中

便 可 以 作 图 分 析

"

步 误差分析

还可以将

"

12345678

或 作 进 一

"

中的仿真结果与

中做出的理论结果相比较来验证设 计的正

这样可以比直接用人工方法将输入数据通过

19:59;

确性

.

波形输入

再用人工方法通过对比输出波形中的数

"

据来验证设计的正确性要直观

方便得多

C

.

下面将这种联合仿真的方法应用到本设计中

"

来分析设计的正确性和误差来源

并考虑有噪声和

"

##$

的性能

.

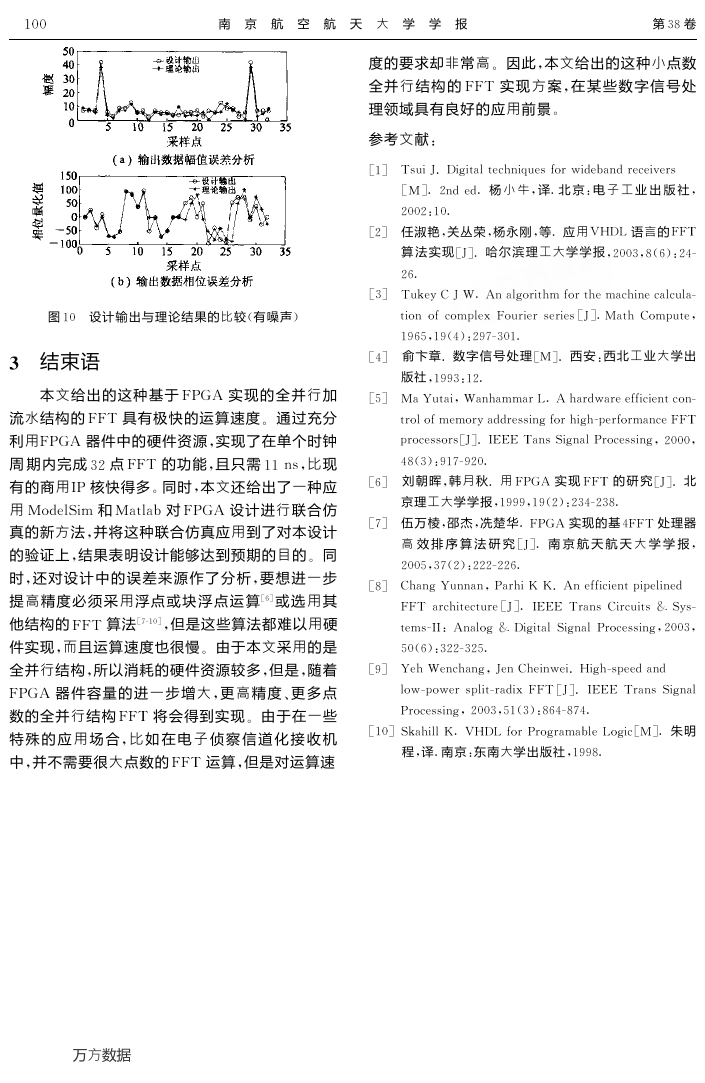

输入数据无噪声情况

KBK

首 先 用

产 生 一 个 单 音 余 弦 信 号

采 样

19:59;

频 率为

正弦波信号频率为

X)r{"

始相位为

输入信号为

&|"

点实信号

X)

"

位

其时域和频域如图

"

所示

W*9";-

.

"

幅度为

初

Xr{"

,"

数据位宽为

/

UV

无噪声两种情况下这种全并行

�

第

期

/

王旭东

等

,

全并行结构

F

的

88E

89:;

实现

==

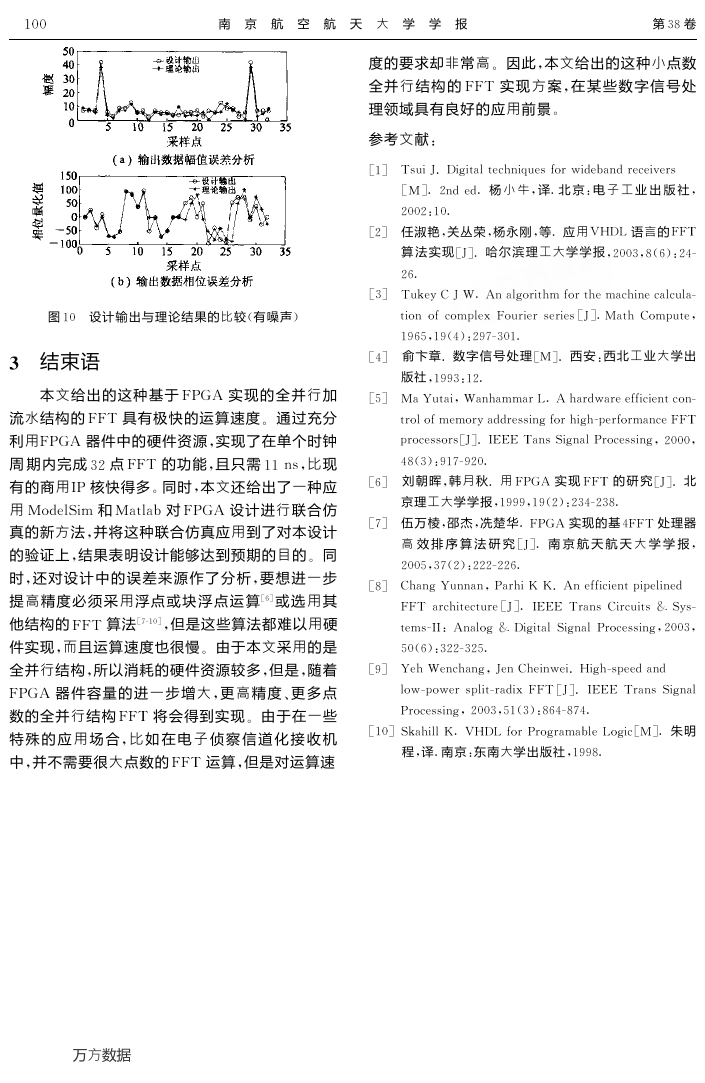

较结果则如图

所示

5"2#

4

在信号频率点处的幅度误差为

处理过程中数据截断产生的

89:;

益不影响信号所含有的信息

这是由于

/-7,

一般讲幅度增

,

相位误差在有信号的

6

频 率点处

图

"

差也是来源于

5"2#

第

点和第

<

点

-=

误差小于

#

误

!>,

89:;

运算中的截断处理

4

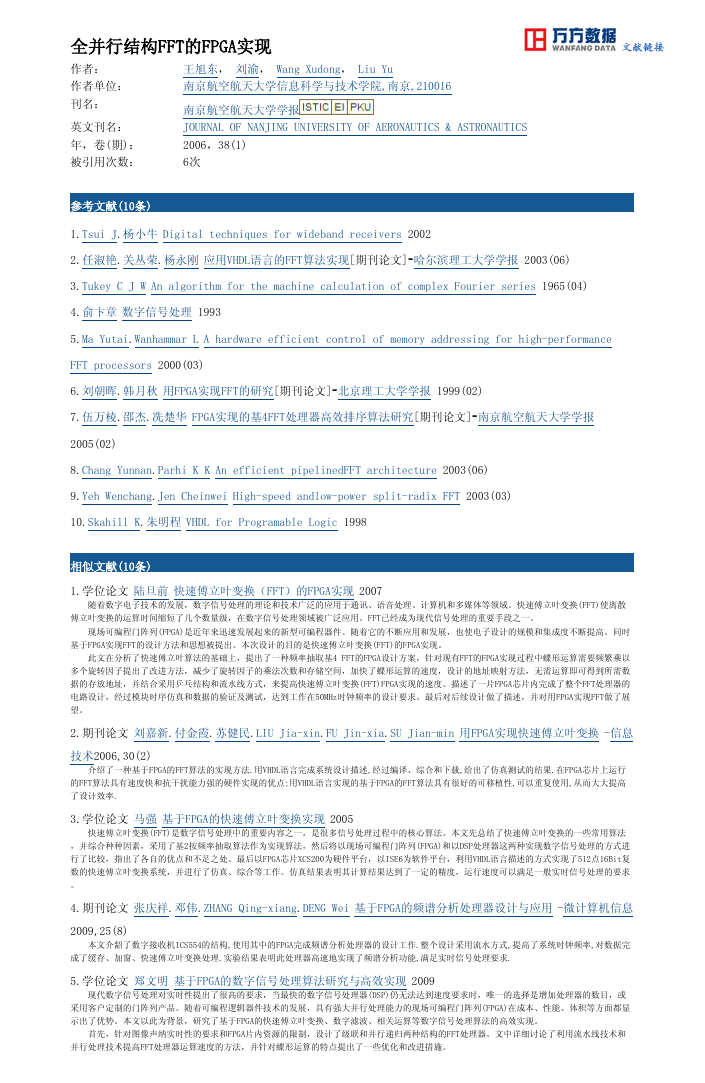

输入数据有噪声情况

?.@

下面用

产生被噪声污染的单音余弦信

$01(02

号

信噪比为

,

A&B,

次蒙特卡罗仿真

时域和频域如图

其他参数 如

节 所 述

做

-.-

,

所示

/CC

联

4

D"0,2#

,

图

!

输入信号时域及频域图形

无噪声

"

#

将 产 生 的 数 据 输 入 文 件 作 为

合仿真结果如图

所示

="0,2#

4

的 仿

真 输 入 向 量

在

$%&’()*+

并将仿真的输出结果用

,

真

,

$%&’()*+

中 做 布 局 布 线 后 的 仿

中介绍的联合仿真

-./

作出其图形来

方法导入数据文件中

再用

,

结果如图

3"0,2#

所示

图

4

3"2#

$01(02

中的幅值与图

,

中

3"0#

仿真波形中的数据相对应

通过联合仿

$%&’()*+

真已经将输出波形中的数据导入数据文件中

4

通过

,

与

$01(02

得到如图

中做出的理论结果

图

"

所示的比较结果

!"2##

幅度

"

#6

相比较可以

其相位的比

5"0#

图

D

输入信号时域及频域图形

有噪声

"

#

图

3

联合仿真输出结果

无噪声

"

#

图

=

联合仿真输出结果

有噪声

"

#

对仿真 结果作误差分析

得到如 图

,

/C"0,2#

所

示 的 比较 图

4

在 信 号 频 率 点 处 幅 度 的 均 方 误 差 为

/<.37,

相位均方误差为

3.A>4

以上分析表明

本文提出的这种基于

,

不仅计 算 速 度 快

现的全并 行结构

88E,

入信噪比较低的情况下

实

89:;

而 且 在 输

,

仍然能够取得较好的频率

,

万方数据

5

设计输出与理论结果的比较

图

无噪声

"

#

和相位计算精度

误差主要来源于计算中的数据截

4

断误差

将来可以考虑采用浮点运算或块浮点运算

,

来降低误差

4

�

""!

南 京 航 空 航 天 大 学 学 报

第

卷

-S

度的要求却非常高

因此

+

本文给出的这种小点数

,

图

!"

设计输出与理论结果的比较

有噪声

#

$

+

,

对

设计进行联合仿

京理工大学学报

,![[[,![#.$C.-TA.-SF

全并 行 结 构 的

&&*

实 现 方 案

在 某 些 数 字 信 号 处

,

理领域具有良好的应用前景

+

参考文献

C

=!? *0D8EFG8H8;:6;5IJ/8KD50L3MN845<:/4M5I58O5M0

=2?F./454F

杨 小 牛

译

,

北 京

F

电 子 工 业 出 版 社

C

,

=.?

."".C!"F

任淑艳

,

算 法 实 现

关丛荣

杨永刚

等

应用

,

哈 尔 滨 理 工 大 学 学 报

,

F

PQGR

语言的

&&*

,.""-,S#>$C.TA

=E?F

.>F

=-? *DU5VWEXF)/:6H3M8;J9 L3M;J59:IJ8/5I:6ID6:A

;83/ 3LI39Y65Z&3DM85M05M850=E?F2:;JW39YD;5,

![>\,![#T$C.[@A-"!F

数 字 信 号 处 理

俞 卞 章

F

=T?

版社

,![[-C!.F

西 安

=2?F

西 北 工 业 大 学 出

C

=\? 2:]D;:8,X:/J:99:MRF) J:M4N:M55LL8I85/;I3/A

;M363L9593MV:44M5008/HL3MJ8HJAY5ML3M9:/I5&&*

YM3I5003M0=E?F1^^^*:/078H/:6’M3I5008/H,.""",

TS#-$C[!@A[."F

刘 朝 晖

韩 月 秋

,

用

&’()

实 现

&&*

的 研 究

北

=E?F

F

=>?

=@?

伍万棱

邵杰

,

冼楚华

,

F&’()

实现的基

T&&*

处理器

高 效 排 序 算 法 研 究

=E?F

南 京 航 天 航 天 大 学 学 报

,

.""\,-@#.$C...A..>F

=S? WJ:/H]D//:/,’:MJ8_ _F)/5LL8I85/;Y8Y568/54

&&* :MIJ8;5I;DM5=E?F1^^^ *M:/0W8MID8;0‘ 7V0A

;590A11C)/:63H‘ G8H8;:678H/:6’M3I5008/H,.""-,

\"#>$C-..A-.\F

=[? ]5JX5/IJ:/H,E5/WJ58/N58FQ8HJA0Y554:/4

63NAY3N5M0Y68;AM:48Z&&*=E?F1^^^ *M:/078H/:6

’M3I5008/H,.""-,\!#-$CS>TAS@TF

=!"?7U:J866_FPQGRL3M’M3HM:9:<65R3H8I=2?F

朱 明

程

译

,

南京

F

东南大学出版社

C

,![[SF

结束语

%

本文给 出 的这种基 于

流水结构的

具有极快的运算速度

&&*

器件中的硬件资源

实 现 的 全 并 行 加

&’()

通过充分

+

实现了在单个时钟

,

点

&&*

-.

核快得多

的功能

且只需

,

比现

!!/0,

同时

本文还给出了一种应

利用

&’()

周 期内完成

有的商用

用

1’

和

,

,

,

23456789

2:;6:<

&’()

真的新方法

并将这种联合仿真应用到了对本设计

的验证上

结果表明设计能够达到预期的目的

,

同

+

时

还对 设 计 中 的 误 差 来 源 作 了 分 析

,

要 想 进 一 步

,

提 高 精 度 必 须 采 用 浮 点 或 块 浮 点 运 算 =>?或 选 用 其

他结构的

&&*

算法 =@A!"?,

但是这些算法都难以用硬

件实现

而且运算速度也很慢

由于本文采用的是

+

,

更 高 精 度

,

随着

,

更 多 点

B

全并行结构

所以消耗的硬件资源较多

但是

器 件 容 量 的 进 一 步 增 大

&’()

数的全并行结构

&&*

将会得到实现

由于在一些

+

特 殊 的 应 用 场 合

比 如 在 电 子 侦 察 信 道 化 接 收 机

,

中

并不需要很大点数的

,

运算

&&*

但是对运算速

,

万方数据

�

全并行结构FFT的FPGA实现

作者:

王旭东, 刘渝, Wang Xudong, Liu Yu

作者单位:

刊名:

南京航空航天大学信息科学与技术学院,南京,210016

南京航空航天大学学报

英文刊名:

JOURNAL OF NANJING UNIVERSITY OF AERONAUTICS & ASTRONAUTICS

年,卷(期):

2006,38(1)

6次

被引用次数:

参考文献(10条)

1.Tsui J.杨小牛 Digital techniques for wideband receivers 2002

2.任淑艳.关丛荣.杨永刚 应用VHDL语言的FFT算法实现[期刊论文]-哈尔滨理工大学学报 2003(06)

3.Tukey C J W An algorithm for the machine calculation of complex Fourier series 1965(04)

4.俞卞章 数字信号处理 1993

5.Ma Yutai.Wanhammar L A hardware efficient control of memory addressing for high-performance

FFT processors 2000(03)

6.刘朝晖.韩月秋 用FPGA实现FFT的研究[期刊论文]-北京理工大学学报 1999(02)

7.伍万棱.邵杰.冼楚华 FPGA实现的基4FFT处理器高效排序算法研究[期刊论文]-南京航空航天大学学报

2005(02)

8.Chang Yunnan.Parhi K K An efficient pipelinedFFT architecture 2003(06)

9.Yeh Wenchang.Jen Cheinwei High-speed andlow-power split-radix FFT 2003(03)

10.Skahill K.朱明程 VHDL for Programable Logic 1998

相似文献(10条)

1.学位论文 陆旦前 快速傅立叶变换(FFT)的FPGA实现 2007

随着数字电子技术的发展,数字信号处理的理论和技术广泛的应用于通讯、语音处理、计算机和多媒体等领域。快速傅立叶变换(FFT)使离散

傅立叶变换的运算时间缩短了几个数量级,在数字信号处理领域被广泛应用。FFT已经成为现代信号处理的重要手段之一。

现场可编程门阵列(FPGA)是近年来迅速发展起来的新型可编程器件。随着它的不断应用和发展,也使电子设计的规模和集成度不断提高。同时

基于FPGA实现FFT的设计方法和思想被提出。本次设计的目的是快速傅立叶变换(FFT)的FPGA实现。

此文在分析了快速傅立叶算法的基础上,提出了一种频率抽取基4 FFT的FPGA设计方案,针对现有FFT的FPGA实现过程中蝶形运算需要频繁乘以

多个旋转因子提出了改进方法,减少了旋转因子的乘法次数和存储空间,加快了蝶形运算的速度,设计的地址映射方法,无需运算即可得到所需数

据的存放地址,并结合采用乒乓结构和流水线方式,来提高快速傅立叶变换(FFT)FPGA实现的速度。描述了一片FPGA芯片内完成了整个FFT处理器的

电路设计,经过模块时序仿真和数据的验证及测试,达到工作在50MHz时钟频率的设计要求。最后对后续设计做了描述,并对用FPGA实现FFT做了展

望。

2.期刊论文 刘嘉新.付金霞.苏健民.LIU Jia-xin.FU Jin-xia.SU Jian-min 用FPGA实现快速傅立叶变换 -信息

技术2006,30(2)

介绍了一种基于FPGA的FFT算法的实现方法.用VHDL语言完成系统设计描述,经过编译、综合和下载,给出了仿真测试的结果.在FPGA芯片上运行

的FFT算法具有速度快和抗干扰能力强的硬件实现的优点;用VHDL语言实现的基于FPGA的FFT算法具有很好的可移植性,可以重复使用,从而大大提高

了设计效率.

3.学位论文 马强 基于FPGA的快速傅立叶变换实现 2005

快速傅立叶变换(FFT)是数字信号处理中的重要内容之一,是很多信号处理过程中的核心算法。本文先总结了快速傅立叶变换的一些常用算法

,并综合种种因素,采用了基2按频率抽取算法作为实现算法,然后将以现场可编程门阵列(FPGA)和以DSP处理器这两种实现数字信号处理的方式进

行了比较,指出了各自的优点和不足之处。最后以FPGA芯片XCS200为硬件平台,以ISE6为软件平台,利用VHDL语言描述的方式实现了512点16Bit复

数的快速傅立叶变换系统,并进行了仿真、综合等工作。仿真结果表明其计算结果达到了一定的精度,运行速度可以满足一般实时信号处理的要求

。

4.期刊论文 张庆祥.邓伟.ZHANG Qing-xiang.DENG Wei 基于FPGA的频谱分析处理器设计与应用 -微计算机信息

2009,25(8)

本文介龆了数字接收机ICS554的结构,使用其中的FPGA完成频谱分析处理器的设计工作.整个设计采用流水方式,提高了系统时钟频率,对数据完

成了缓存、加窗、快速傅立叶变换处理.实验结果表明此处理器高速地实现了频谱分析功能,满足实时信号处理要求.

5.学位论文 郑文明 基于FPGA的数字信号处理算法研究与高效实现 2009

现代数字信号处理对实时性提出了很高的要求,当最快的数字信号处理器(DSP)仍无法达到速度要求时,唯一的选择是增加处理器的数目,或

采用客户定制的门阵列产品。随着可编程逻辑器件技术的发展,具有强大并行处理能力的现场可编程门阵列(FPGA)在成本、性能、体积等方面都显

示出了优势。本文以此为背景,研究了基于FPGA的快速傅立叶变换、数字滤波、相关运算等数字信号处理算法的高效实现。

首先,针对图像声纳实时性的要求和FPGA片内资源的限制,设计了级联和并行递归两种结构的FFT处理器。文中详细讨论了利用流水线技术和

并行处理技术提高FFT处理器运算速度的方法,并针对蝶形运算的特点提出了一些优化和改进措施。

�

其次,分析了具有相同结构的数字滤波和相关运算的特点,采用了有乘法器和无乘法器两种结构实现乘累加(MAC)运算。无乘法器结构采用分

布式算法(DA),将乘法运算转化为FPGA易于实现的查表和移位累加操作,显著提高了运算效率。此外,还对相关运算的时域多MAC方法及频域FFT方

法进行了研究。

最后,完成了图像声纳预处理模块。在一片EP2S60上实现了对160路信号的接收、滤波、正交变换以及发送等处理。实验表明,本论文所有算

法均达到了设计要求。

6.学位论文 邓小川 16位定点FFT-DSP的FPGA实现 2004

随着计算机技术以及VLSI技术的高速发展,数字信号处理中的核心技术——快速傅立叶变换(FFT)技术应用越来越广,得到了很快的发展,广泛应

用于通信系统、图像处理、雷达、生物医学电子学、电子测试设备以及数字声频和视频设备等方面.但是对于一些具有很高实时要求的系统:如

OFDM和DMT系统来说,用通用的DSP芯片很难完成.本论文主要研究了一种高速FFT信号处理器(DSP)的硬件实现结构,这种结构与目前通用DSP所采用的

基于时间抽取算法(DIT)的MAC(乘-累加运算)结构有所不同,采用的是一种更适合于频率抽取算法(DIF)的硬件结构来实现.这种FFT实现结构仅增加

了少量的附加数据通路电路,并没有改变传统的DSP运算结构单元结构,因此它的硬件花费很小,而速度提升很大.整个硬件结构模型用Verilog-HDL完

成设计,并在Altera公司的大规模可编程器件FLEX10KE上完成原型机验证.通过对比该硬件结构完成256点FFT运算的仿真值和Matlab的理论计算值

,两者的误差很小.

7.期刊论文 段玉波.刘继新.刘树庆.DUAN Yu-bo.LIU Ji-xin.LIU Shu-qing 基于FPGA的快速傅立叶变换

(FFT)处理器的设计 -自动化技术与应用2006,25(4)

文章针对目前数字信号处理中大量采用的快速傅立叶变换(FFT)算法采用软件编程来处理的应用现状,在对FFT算法进行分析的基础上,给出了用

FPGA(Field Programmable Gate Array)实现的8点32位FFT处理器方案,并得到了系统的仿真结果.最后在Altera公司FLEX10K系列FPGA芯片上成功地

实现了综合.

8.学位论文 陈立强 基于FPGA的水下远程遥控解码电路的设计与研究 2004

随着计算机和集成电路技术的不断发展,基于EDA技术的芯片设计正在成为电子系统设计的主流.现场可编程门阵列(FPGA)作为一种可编程专用

集成电路(ASIC)已经广泛应用于计算机、通信、航空航天等各个领域.一般来讲,FPGA多用于高速通信和高速信号处理领域,以发挥其处理速度快的

特点,本文将其应用于一低速低功耗系统——某水下远程遥控接收系统,主要用其在频域来实现水下远程遥控的解码,取得了令人满意的效果.该文主

要做了以下几方面的工作.首先,深入研究和分析了在频域实现水下远程遥控解码的原理并进行了遥控指令编码设计;其次,用ALTERA公司的

CYCLONE系列FPGA芯片完成了水下远程遥控FPGA解码芯片的设计工作,包括硬件描述语言(VHDL)编码、电路前后仿真、综合和布局布线工作,并对设

计的FPGA解码芯片进行了初步的功耗估算:最后设计制作了一块FPGA解码芯片电路验证测试板,并完成了电路调试和测试.实验测试结果表明,用

FPGA实现水下远程遥控解码电路的方案是可行的,可以有效地缩小系统体积、提高系统可靠性,在保证系统性能情况下做到更低的功耗,还可以实现

在系统配置和编程,使得系统的调试、升级和维护更加灵活方便.

9.期刊论文 连冰.宫丰奎.张力.李兵兵 基于FPGA的快速傅立叶变换 -国外电子元器件2003,""(12)

在对FFT(快速傅立叶变换)算法进行研究的基础上,描述了用FPGA实现FFT的方法,并对其中的整体结构、蝶形单元及性能等进行了分析.

10.期刊论文 吕琛.杨会成.王小雪 FFT算法的FPGA实现 -电子技术2010,47(3)

在信号处理中,FFT占有很重要的位置,其运算时间影响整个系统的性能.传统的实现方法速度很慢,难以满足信号处理的实时性要求.针对这个问

题,本文研究了基于FPGA芯片的FFT算法,把FFT算法对实时性的要求和FPGA芯片设计的灵活性结合起来,采用Alter公司 CycloneⅡ系列FPGA芯片

EP2C35F672C8,用VHDL语言编程,最后分别使用Quartus Ⅱ和Matlab软件开发工具验证实现.

引证文献(6条)

1.淮永进.屈晓声 具有蝶型单元的FFT在FPGA上的实现[期刊论文]-微电子学 2008(3)

2.王旭东.刘渝.邓振淼 基于修正Rife算法的正弦波频率估计及FPGA实现[期刊论文]-系统工程与电子技术

2008(4)

3.范展.梁国龙.刘洋 基于FPGA的新型浮点FFT处理器设计[期刊论文]-电子技术应用 2008(5)

4.陈立万.冯地耘 基于FPGA的数字化频分副载频解调器分析[期刊论文]-重庆大学学报(自然科学版)

2008(4)

5.李伟.孙进平.王俊.李少洪 一种基于FPGA的超高速32k点FFT处理器[期刊论文]-北京航空航天大学学报

2007(12)

6.王旭东.刘渝 多通道自相关信号检测算法及其FPGA实现[期刊论文]-仪器仪表学报 2007(5)

本文链接:http://d.g.wanfangdata.com.cn/Periodical_njhkht200601019.aspx

授权使用:陕西理工学院(sxlgxy),授权号:f4dd3eb8-5c83-4e8a-bd6a-9df200fed114

下载时间:2010年9月15日

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc