CPRI v8.7

Table of Contents

IP Facts

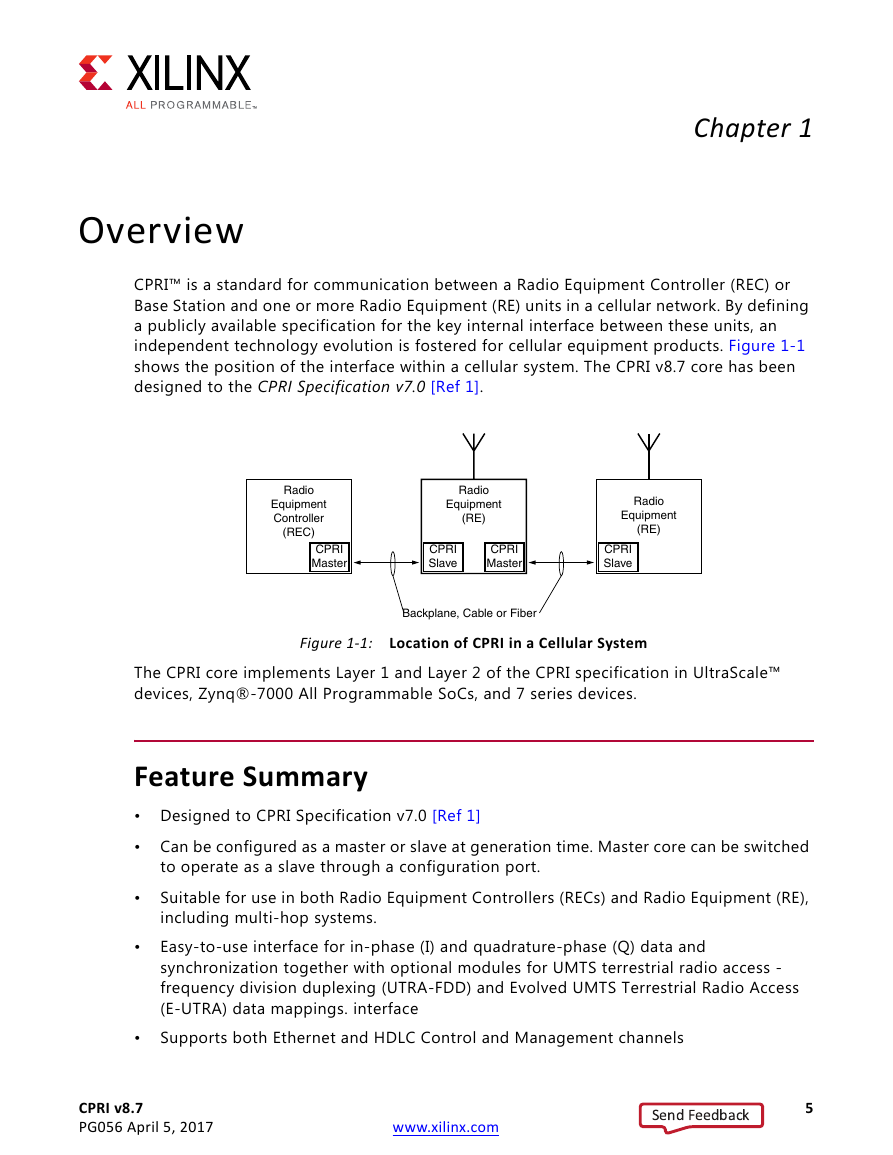

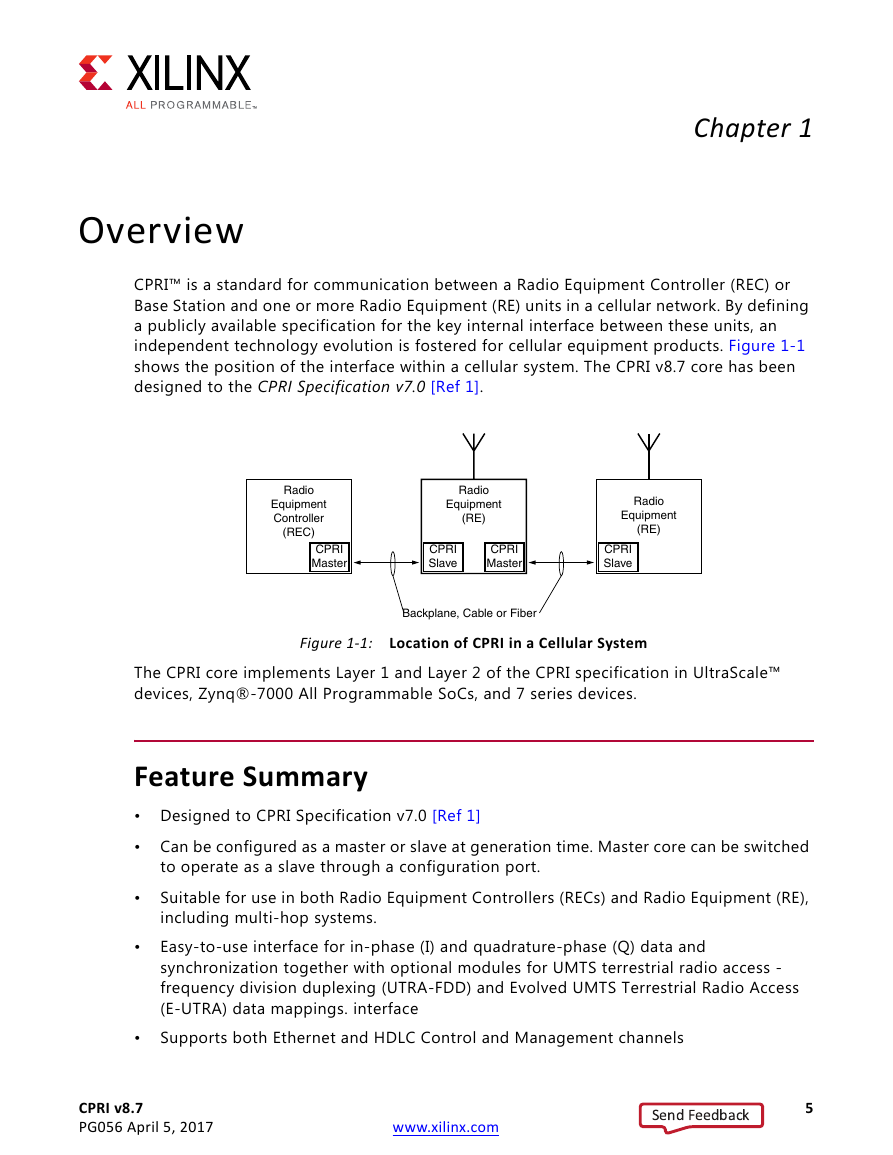

Ch. 1: Overview

Feature Summary

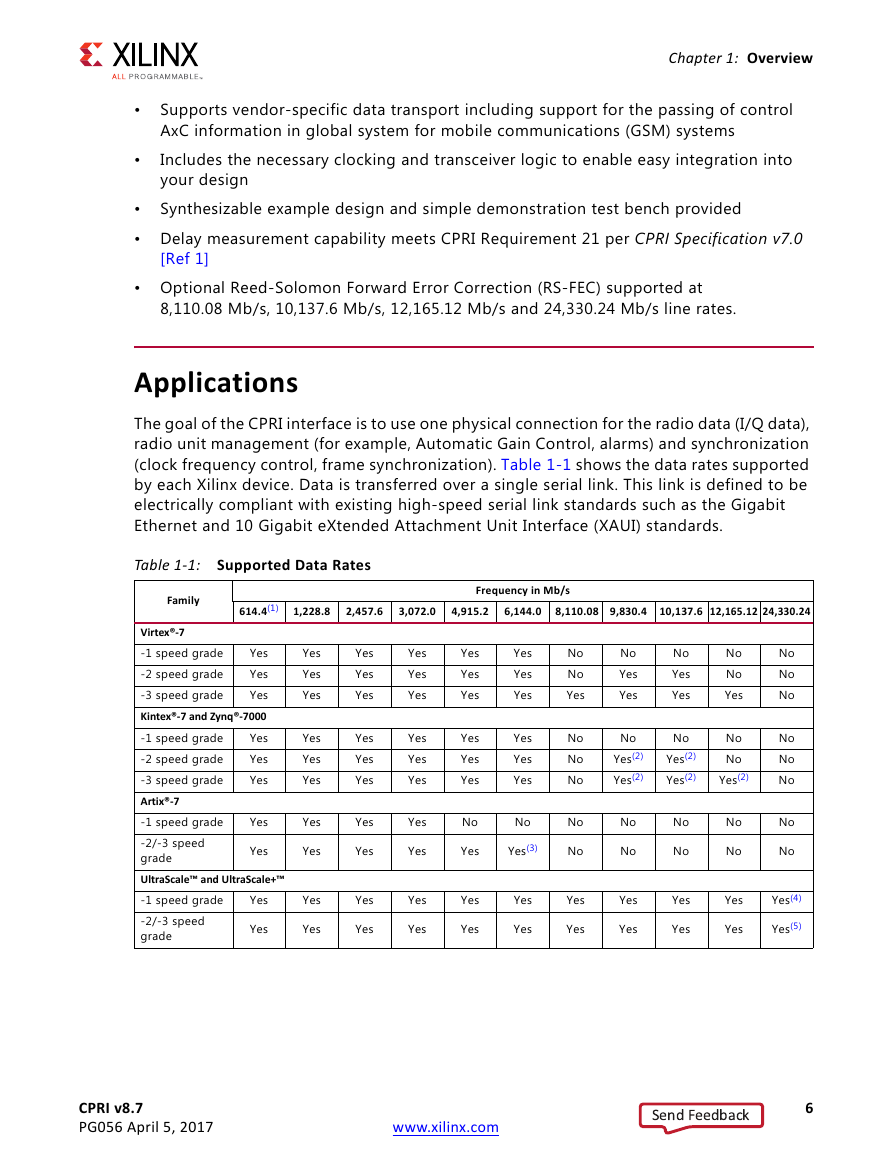

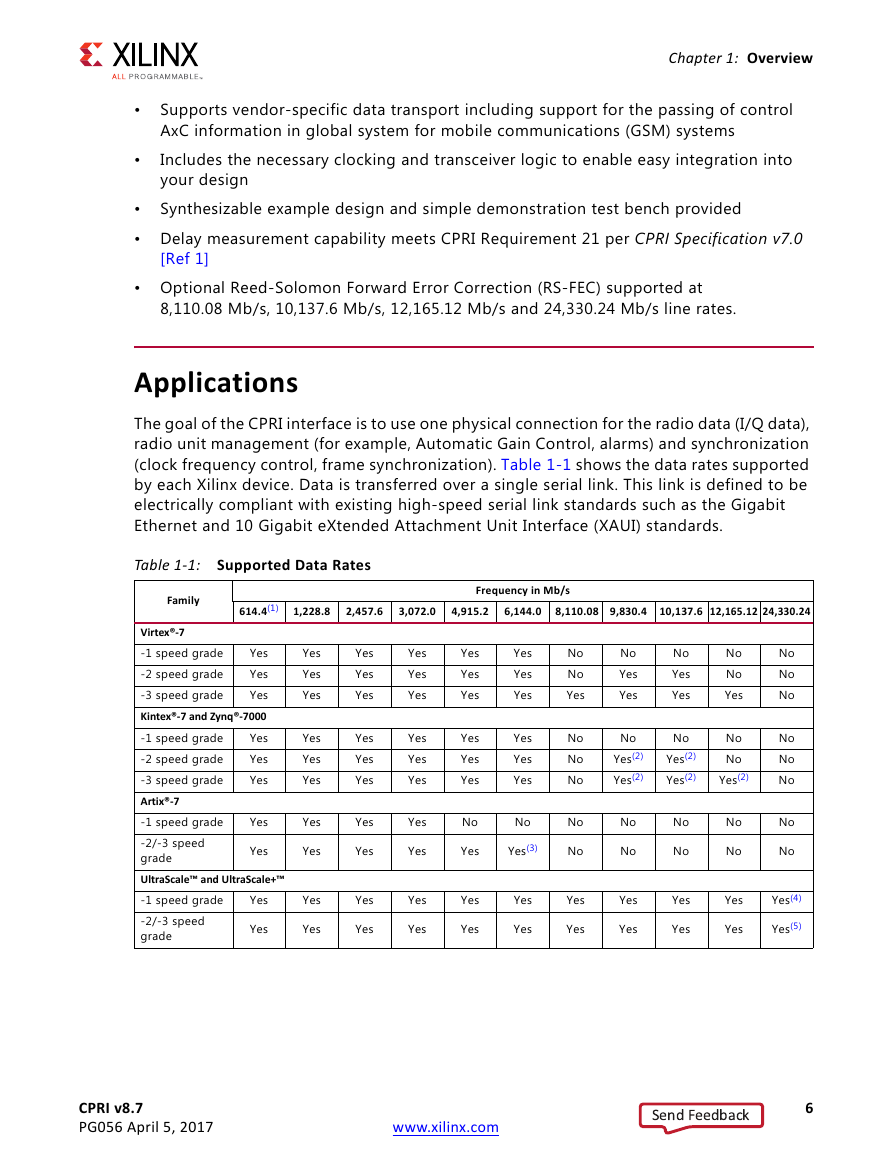

Applications

System Requirements

Recommended Design Experience

Licensing and Ordering Information

License Checkers

License Type

Ch. 2: Product Specification

Chip Period (TC) in This Document

Related Information

Performance

Maximum Frequencies

Resource Utilization

Speed Grade Support

CPRI Core Structure

Port Descriptions

Management Register Map

Status Code and Alarm Register (0x0)

Miscellaneous Status Register (0x1)

Current HDLC Rate Register (0x2)

Current Ethernet Pointer Register (0x3)

Received Subchannel 2, Word 0 Register (0x4)

Received Subchannel 2, Word 1 Register (0x5)

Received Subchannel 2, Word 2 Register (0x6)

Received Subchannel 2, Word 3 Register (0x7)

Transceiver Loopback and Ethernet Reset Request Register (0x8)

Transceiver Barrel Shift Position Register(0x9)

Preferred HDLC Rate Register (0xA)

Preferred Ethernet Pointer Register (0xB)

Current Line Speed Register (0xC)

Line Speed Capability Register (0xD)

General Configuration and Transmit CPRI Alarms Register (0xE)

R21 Timers Register (0xF)

Current Protocol Version Register (0x10)

Preferred Protocol Version Register (0x11)

Scrambler Seed Register (0x12)

Descrambler Seed Register (0x13)

Transmit FIFO Transit Time Register (0x14)

Watchdog Timeout Value Register (0x15)

Gearbox Latency Register (0x16)

FIFO Fill Level Register (0x17)

General Debug Register (0x18)

High Resolution FIFO Transit Time—Integer Part Register (0x19)

High Resolution FIFO Transit Time—Fractional Part Register (0x1A)

FEC Status Register (0x1B)

FEC CW Count Register (0x1C)

FEC Corrected CW Count Register (0x1D)

FEC Uncorrected CW Count Register (0x1E)

Ch. 3: Designing with the Core

General Design Guidelines

Use the Example Design as a Starting Point

Know the Degree of Difficulty

Keep It Registered

Recognize Timing Critical Signals

Use Supported Design Flows

Make Only Allowed Modifications

Clocking and Resets

Interfacing to the Core

Data Interfaces

I/Q Interface

UTRA-FDD I/Q Module

E-UTRA I/Q Module

Legacy Raw I/Q Module

Vendor-Specific Data Interface

Real Time Vendor-Specific Support

Frame and Synchronization Interface

HDLC Interface

Ethernet Interface

MII Interface

GMII Interface

Bandwidth Timing on the MII Interface

Connecting the CPRI core to an Ethernet MAC on the FPGA

Interface with Ethernet Frame Buffers Bypassed

ORI Module

Serial Interface

Transceiver Interface

Transceiver Debug Interface

Transceiver Data Monitor Interface

Management Interface

AXI4-Lite Memory Mapped Interface

Status and Alarm Interfaces

Static Configuration Interface

Dynamic Configuration Interface

Ch. 4: Design Considerations

Reference Clock Selection

Clock Configuration

Virtex-7, Zynq-7000, and Kintex-7 Devices

Supporting Line Rates up to 3,072.0 Mb/s

Supporting Line Rates up to 6,144.0 Mb/s

Supporting Line Rates up to 9,830.4 Mb/s

Supporting Line Rates up to 10,137.6 Mb/s

Supporting Line Rates up to 12,165.12 Mb/s

Artix-7 Devices

Supporting Line Rates up to 3,072.0 Mb/s

Supporting Line Rates up to 6,144.0 Mb/s

UltraScale Architecture Devices

Supporting Line Rates up to 3,072.0 Mb/s and 6,144 Mb/s

Supporting Line Rates up to 9,830.4 Mb/s

Supporting Line Rates up to 10,137.6 Mb/s and 12,165.12 Mb/s

Supporting Line Rates up to 24,330.24 Mb/s

UltraScale GTYE3-based Devices (368.64 MHz Reference Clock)

UltraScale GTYE3-based and UltraScale+ GTYE4-based Devices (245.76 MHz Reference Clock)

Free Running Receiver Reference Clock (Artix-7 Only)

Using the PLL to Generate the Core Clock

Resource Sharing

Transmitter Clock Sharing

Transceiver Common Block Sharing

Core Support Layer

_clocking.vhd

_tx_alignment.vhd

_gt_common.vhd

_resets.vhd

Line Speed Configuration and Negotiation

Single Speed Operation

Multi-speed Operation with Rate Negotiation

Disabling the Core

RS-FEC Enabled Mode

Using an External GMII Interface

Delay Measurement and Requirement 21 (R21)

Delay Model

Delay Through the GTXE2 Transceiver

Delay Through the GTHE2 Transceiver

Delay Through the GTPE2 Transceiver

Delay Through the GTHE3 Transceiver

Delay Through the GTYE3 Transceiver

Delay Across the CDC FIFO

Overall Delay

Core I/Q Interface

UTRA-FDD I/Q Module

R21 Calculation

Coarse Delay Measurement

Additional Pipeline Delays

Cores Supporting 3,072.0 Mb/s

Cores Supporting 4,915.2/6,144.0 Mb/s

Cores Supporting 9,830.4 Mb/s

Cores Supporting 10,137.6 Mb/s

Cores Supporting 12,165.12 Mb/s and Above

Cores supporting FEC Enabled Mode

Performing the Cable Delay Calculation

Calculating T14 (CPRI Master)

Calculating Toffset (CPRI Slave)

Calculating the Cable Delay

Example R21 Delay Calculation

R21A Calculation

R19 Calculation

Ch. 5: Design Flow Steps

Customizing and Generating the Core

Component Name

Master/Slave

Speed and Reference Clock Selection

Use 32-bit Datapath

Use 64-bit Datapath

Free Running Receive Clock

Management Clock Rate

Transceiver Settings

Transceiver Location

Reference Clock Location

GT Type

Additional Transceiver Control and Status Ports

Optional Features

Include R21 Timers

AXI4-Lite Management Interface

ORI Support

Include Ethernet Logic

Use GMII Interface

Bypass Ethernet FIFOs

Real Time Vendor-Specific Support

Line Rate Support

FEC Enabled Mode

Shared Logic

Advanced

User Parameters

Output Generation

Constraining the Core

Required Constraints

Device, Package, and Speed Grade Selections

Clock Frequencies and Clock Management

System Clock Domain

Recovered Clock Domain

Management Clock Domain

Reset Block Clock Domain

Ethernet Clock Domain

Hi-Speed Clock Domain

Clock Placement

Banking

Transceiver Placement

I/O Standard and Placement

Simulation

Synthesis and Implementation

Ch. 6: Example Design

Ch. 7: Test Bench

Appx. A: Verification, Compliance, and Interoperability

Simulation

Hardware Testing

Appx. B: Migrating and Upgrading

Migrating to the Vivado Design Suite

Upgrading in the Vivado Design Suite

Device Migration

Port Changes in Version 8.7

Port Changes in Version 8.6

Port Changes in Version 8.5

Port Changes in Version 8.4

Ports Added in Version 8.3

Ports Added in Version 8.2

Ports Added in Version 8.1

Ports Added in Version 8.0

Changed Ports in Version 8.0

Appx. C: Debugging

Finding Help on Xilinx.com

Documentation

Answer Records

Technical Support

Vivado Design Suite Debug Feature

Hardware Debug

Hardware Demonstration Design

General Checks

CPRI Specific Checks

AXI4-Lite Interface Debug

Appx. D: Additional Resources and Legal Notices

Xilinx Resources

References

Revision History

Please Read: Important Legal Notices

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc