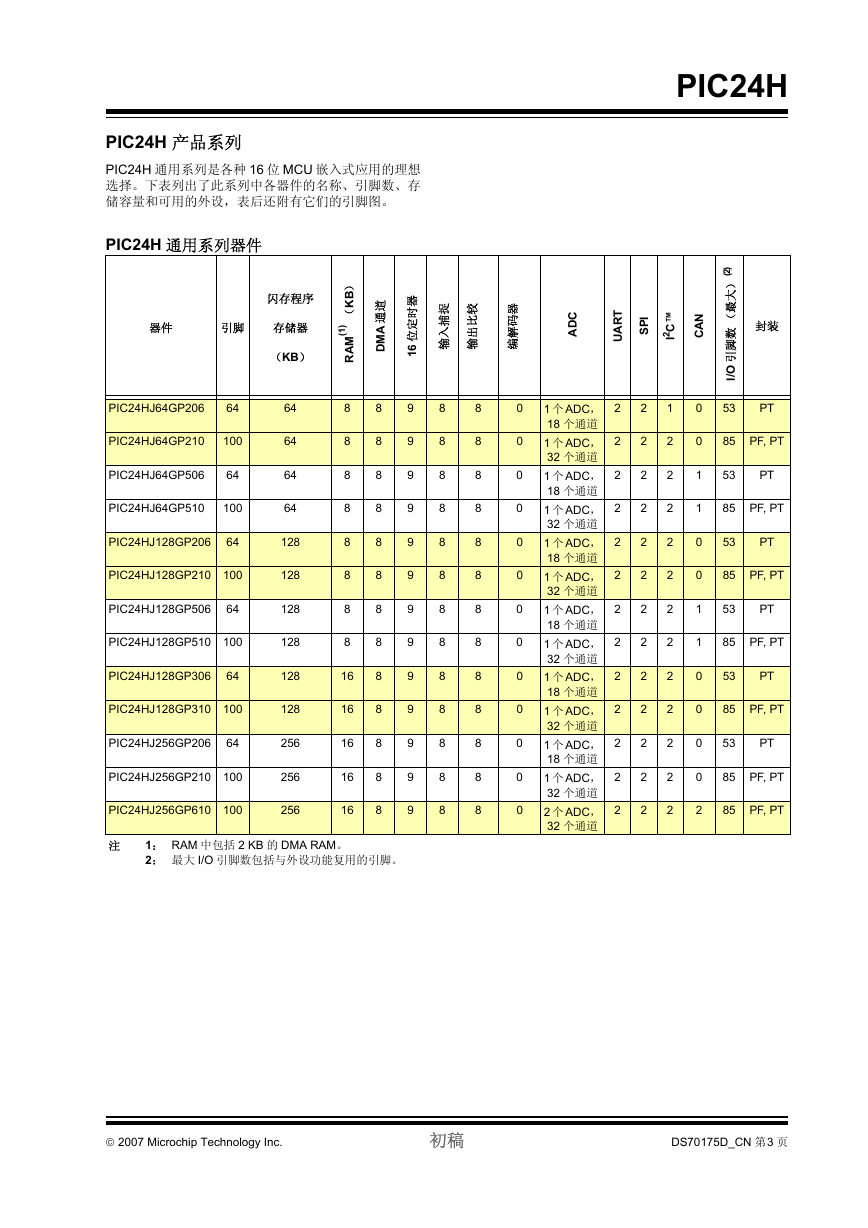

高性能16位单片机

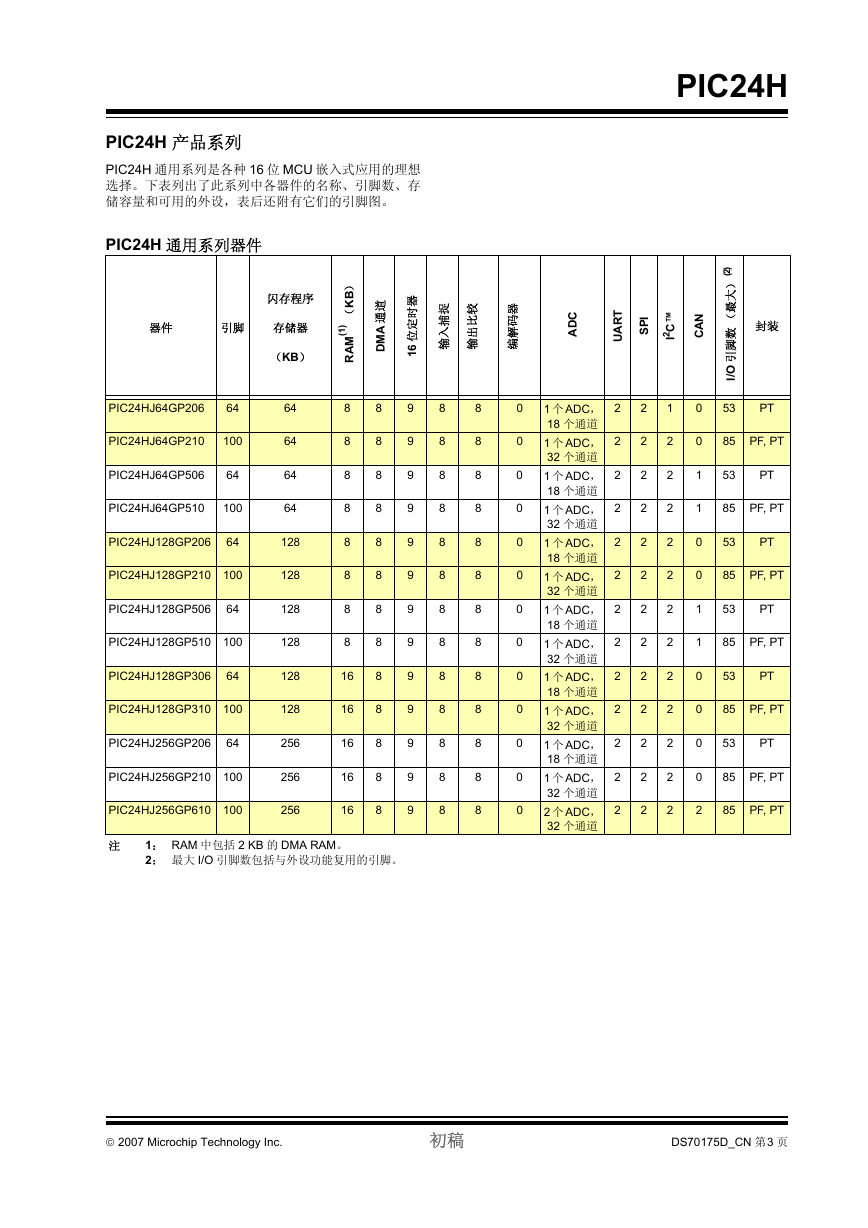

1.0 器件概述

图1-1: PIC24H一般框图

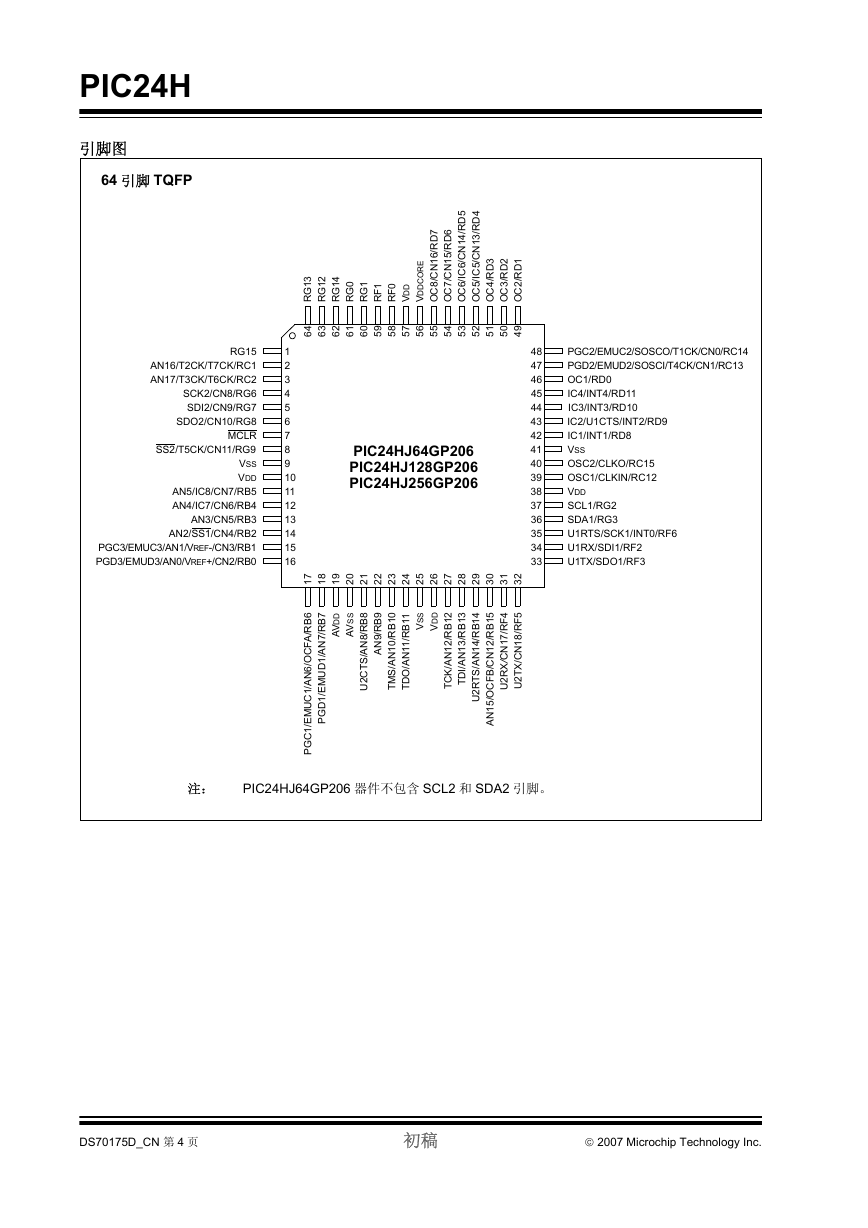

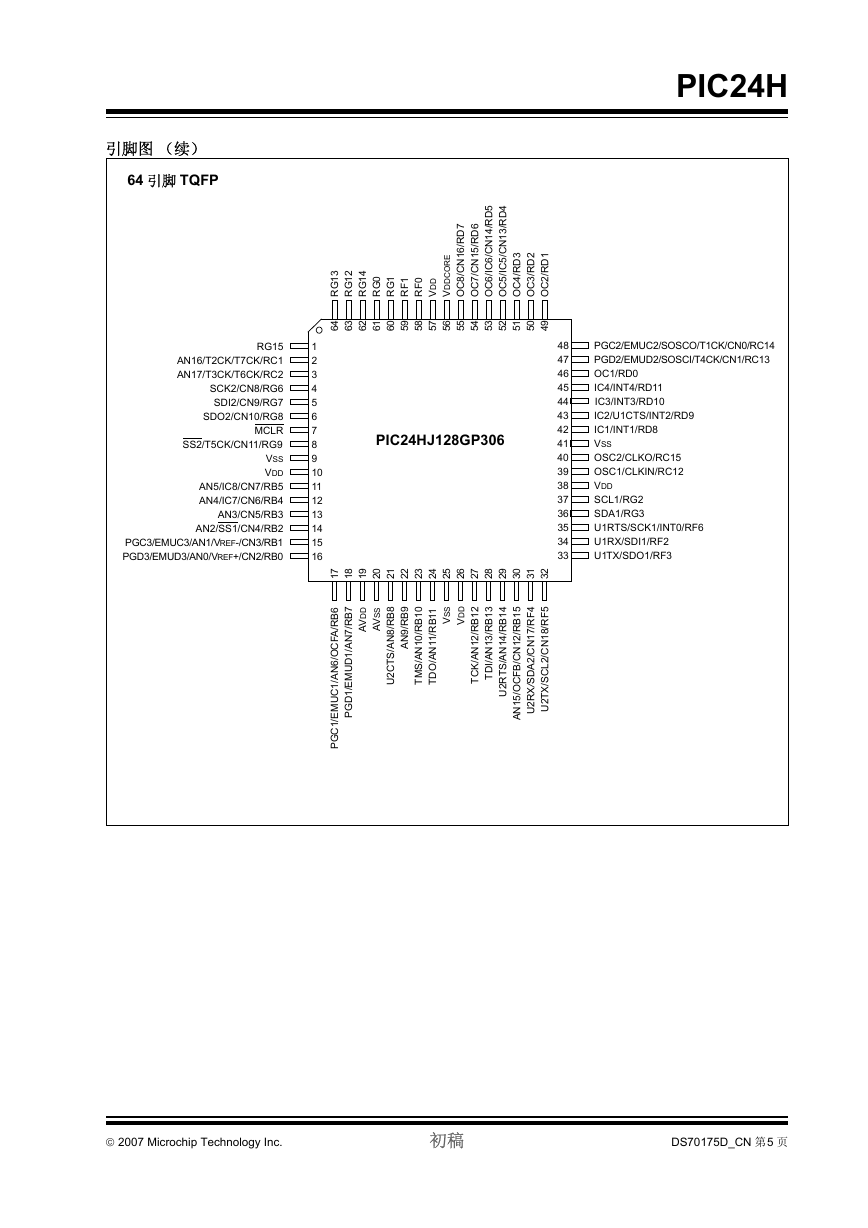

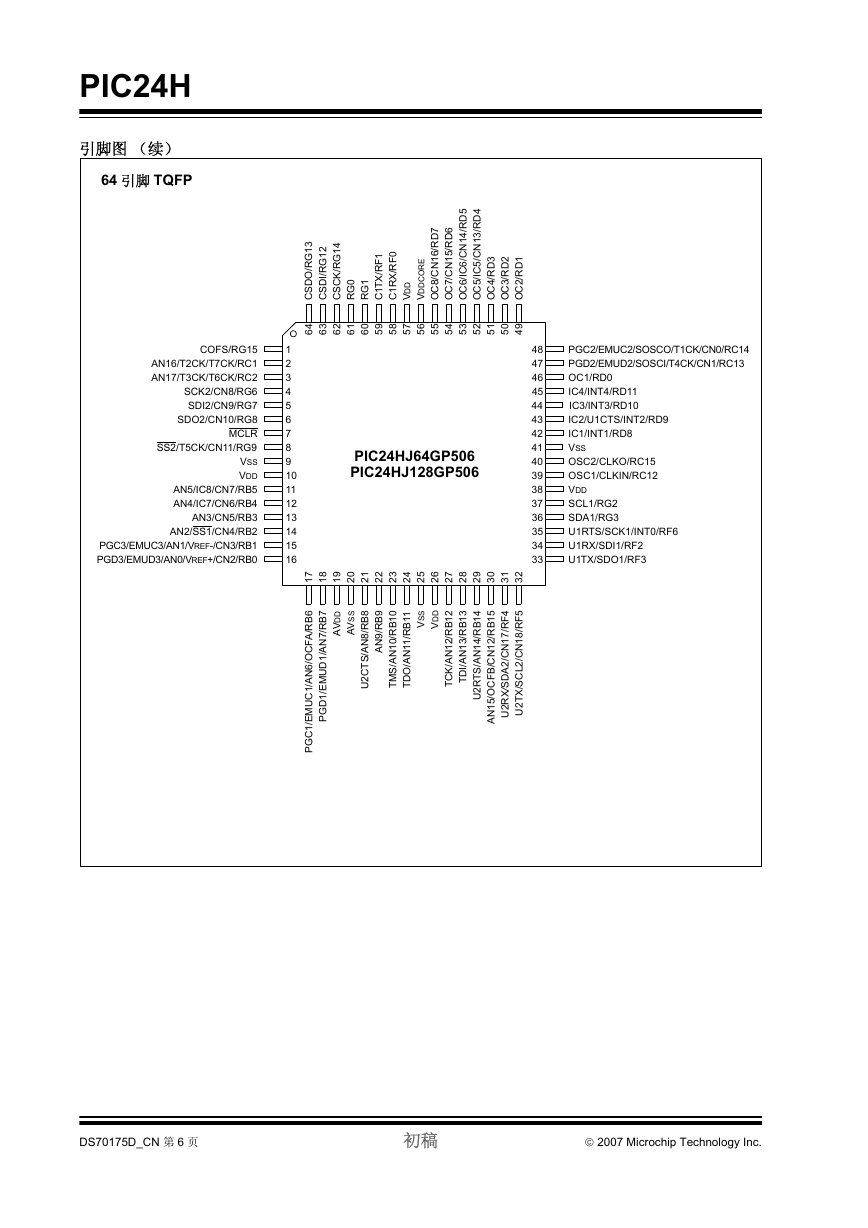

表1-1: 引脚说明

2.0 CPU

2.1 数据寻址概述

2.2 MCU的特性

图2-1: PIC24H CPU内核框图

图2-2: PIC24H编程模型

2.3 CPU控制寄存器

寄存器2-1: SR:CPU状态寄存器

寄存器2-2: CORCON:内核控制寄存器

2.4 算术逻辑单元(ALU)

2.4.1 乘法器

2.4.2 除法器

2.4.3 多位数据移位寄存器

3.0 存储器构成

3.1 程序地址空间

图3-1: PIC24H系列器件的程序存储器映射

3.1.1 程序存储器构成

3.1.2 中断和陷阱向量

图3-2: 程序存储器构成

3.2 数据地址空间

3.2.1 数据空间宽度

3.2.2 数据存储器构成和对齐方式

3.2.3 SFR空间

3.2.4 Near数据空间

图3-3: 带有8 KB RAM的PIC24H器件的数据存储器映射

图3-4: 带有16 KB RAM的PIC24H器件的数据存储器映射

3.2.5 DMA RAM

表3-1: CPU内核寄存器映射

表3-2: 电平变化通知寄存器映射

表3-3: 中断控制器寄存器映射

表3-4: 定时器寄存器映射

表3-5: 输入捕捉寄存器映射

表3-6: 输出比较寄存器映射

表3-7: I2C1寄存器映射

表3-8: I2C2寄存器映射

表3-9: UART1 寄存器映射

表3-10: UART2 寄存器映射

表3-11: SPI1 寄存器映射

表3-12: SPI2 寄存器映射

表3-13: ADC1寄存器映射

表3-14: ADC2 寄存器映射

表3-15: dma 寄存器映射

表3-16: 当C1CTRL1.WIN = 0或 1 时的ECAN1寄存器映射

表3-17: 当C1CTRL1.WIN = 0时的ECAN1寄存器映射

表3-18: 当C1CTRL1.WIN = 1时的ECAN1寄存器映射

表3-19: 当C2CTRL1.WIN = 0或 1时的ECAN2寄存器映射

表3-20: 当C2CTRL1.WIN = 0时的ECAN2寄存器映射

表3-21: 当C2CTRL1.WIN = 1时的ECAN2寄存器映射

表3-22: PORTA寄存器映射(1)

表3-23: PORTB寄存器映射(1)

表3-24: PORTC寄存器映射(1)

表3-25: PORTD寄存器映射(1)

表3-26: PORTE寄存器映射(1)

表3-27: PORTF寄存器映射(1)

表3-28: PORTG寄存器映射(1)

表3-29: 系统控制寄存器映射

表3-30: NVM寄存器映射

表3-31: PMD 寄存器映射

3.2.6 软件堆栈

图 3-5: CALL 堆栈帧

3.2.7 数据RAM保护功能

3.3 指令寻址模式

3.3.1 文件寄存器指令

3.3.2 MCU指令

表3-32: 支持的基本寻址模式

3.3.3 传送指令

3.3.4 其他指令

3.4 程序存储空间与数据存储空间的接口

3.4.1 对程序空间进行寻址

表3-33: 程序空间地址构成

图3-6: 访问程序空间内的数据的地址生成方式

3.4.2 使用表指令访问程序存储器中的数据

图3-7: 使用表指令访问程序存储器

3.4.3 使用程序空间可视性访问程序存储器 中的数据

图3-8: 程序空间可视性操作

4.0 闪存程序存储器

4.1 表指令和闪存编程

图4-1: 表寄存器寻址

4.2 RTSP工作原理

4.3 控制寄存器

4.4 编程操作

寄存器4-1: NVMCON:闪存存储器控制寄存器

4.4.1 闪存程序存储器的编程算法

5.0 复位

图5-1: 复位系统框图

寄存器5-1: RCON:复位控制寄存器(1)

表5-1: 复位标志位

5.1 复位时的时钟源选择

表5-2: 不同复位类型的振荡器选择(使 能时钟切换)

5.2 器件复位时间

表5-3: 各种器件复位的复位延时

5.2.1 POR和长振荡器起振时间

5.2.2 故障保护时钟监视器(FSCM)和器 件复位

5.3 特殊功能寄存器的复位状态

6.0 中断控制器

6.1 中断向量表

6.1.1 备用中断向量表

6.2 复位过程

图6-1: PIC24H中断向量表

表6-1: 中断向量

表6-2: 陷阱向量

6.3 中断控制和状态寄存器

寄存器6-1: SR:CPU状态寄存器(1)

寄存器6-2: CORCON:内核控制寄存器(1)

寄存器6-3: INTCON1:中断控制寄存器1

寄存器6-4: INTCON2:中断控制寄存器2

寄存器6-5: IFS0:中断标志状态寄存器0

寄存器6-6: IFS1:中断标志状态寄存器1

寄存器6-7: IFS2:中断标志状态寄存器2

寄存器6-8: IFS3:中断标志状态寄存器3

寄存器6-9: IFS4:中断标志状态寄存器4

寄存器6-10: IEC0:中断允许控制寄存器 0

寄存器6-11: IEC1:中断允许控制寄存器 1

寄存器6-12: IEC2:中断允许控制寄存器 2

寄存器6-13: IEC3:中断允许控制寄存器 3

寄存器6-14: IEC4:中断允许控制寄存器 4

寄存器6-15: IPC0:中断优先级控制寄存器0

寄存器6-16: IPC1:中断优先级控制寄存器1

寄存器6-17: IPC2:中断优先级控制寄存器2

寄存器6-18: IPC3:中断优先级控制寄存器3

寄存器6-19: IPC4:中断优先级控制寄存器4

寄存器6-20: IPC5:中断优先级控制寄存器5

寄存器6-21: IPC6:中断优先级控制寄存器6

寄存器6-22: IPC7:中断优先级控制寄存器7

寄存器6-23: IPC8:中断优先级控制寄存器8

寄存器6-24: IPC9:中断优先级控制寄存器9

寄存器6-25: IPC10:中断优先级控制寄存器10

寄存器6-26: IPC11:中断优先级控制寄存器11

寄存器6-27: IPC12:中断优先级控制寄存器12

寄存器6-28: IPC13:中断优先级控制寄存器13

寄存器6-29: IPC14:中断优先级控制寄存器14

寄存器6-30: IPC15:中断优先级控制寄存器15

寄存器6-31: IPC16:中断优先级控制寄存器16

寄存器6-32: IPC17:中断优先级控制寄存器17

寄存器6-33: INTTREG:中断控制和状态寄存器

6.4 中断设置过程

6.4.1 初始化

6.4.2 中断服务程序

6.4.3 陷阱服务程序

6.4.4 禁止中断

7.0 直接存储器访问(DMA)

表7-1: 支持DMA的外设

图7-1: 使用专用事务总线的顶层系统架构

7.1 DMAC寄存器

7.2 DMAC工作模式

7.2.1 字节或字传输

7.2.2 寻址模式

7.2.3 DMA传输方向

7.2.4 空数据外设写模式

7.2.5 连续数据块或单数据块的工作

7.2.6 乒乓模式

7.2.7 手动传输模式

7.2.8 DMA请求源选择

7.3 DMA中断和陷阱

7.4 DMA初始化示例

寄存器7-1: DMAxCON:DMA通道x控制寄存器

寄存器7-2: DMAxREQ:DMA通道x控制IRQ选择寄存器

寄存器7-3: DMAxSTA:DMA通道x RAM起始地址寄存器A(1)

寄存器7-4: DMAxSTB:DMA通道x RAM 起始地址寄存器B(1)

寄存器7-5: DMAxPAD:DMA通道x外设地址寄存器(1)

寄存器7-6: DMAxCNT:DMA通道x传输计数寄存器(1)

寄存器7-7: DMACS0:DMA控制器状态寄存器0

寄存器7-8: DMACS1:DMA控制器状态寄存器1

寄存器7-9: DSADR:最近的DMA RAM地址

8.0 振荡器配置

图 8-1: PIC24H 振荡器系统框图

8.1 CPU时钟系统

8.1.1 系统时钟源

8.1.2 系统时钟选择

公式8-1: 器件工作频率

8.1.3 PLL配置

公式8-2: Fosc 计算

公式8-3: 带PLL的XT模式示例

图 8-2: PIC24H PLL框图

表8-1: 用于时钟选择的配置位值

寄存器 8-1: OSCCON:振荡器控制寄存器

寄存器 8-2: CLKDIV: 时钟分频比寄存器

寄存器 8-3: PLLFBD:PLL反馈倍频比寄存器

寄存器 8-4: OSCTUN:FRC振荡器调节寄存器

8.2 时钟切换工作原理

8.2.1 使能时钟切换

8.2.2 振荡器切换序列

8.3 故障保护时钟监视器(FSCM)

9.0 节能特性

9.1 时钟频率和时钟切换

9.2 基于指令的节能模式

9.2.1 休眠模式

9.2.2 空闲模式

9.2.3 在节能指令执行期间的中断

9.3 打盹模式

9.4 禁止外设模块

10.0 I/O端口

10.1 并行I/O(PIO)端口

图10-1: 一个典型共用端口的结构框图

10.2 漏极开路配置

10.3 配置模拟端口引脚

10.4 I/O端口写/读时序

10.5 输入状态变化通知

11.0 Timer1

图11-1: 16位Timer1模块框图

寄存器11-1: T1CON:Timer1控制寄存器

12.0 Timer2/3、Timer4/5、Timer6/ 7和Timer8/9

图12-1: Timer2/3(32位)框图(1)

图12-2: Timer2(16位)框图

寄存器12-1: TxCON(T2CON、T4CON、T6CON或T8CON)控制寄存器

寄存器12-2: TyCON(T3CON、T5CON、T7CON或T9CON)控制寄存器

13.0 输入捕捉

图13-1: 输入捕捉框图

13.1 输入捕捉寄存器

寄存器13-1: ICxCON: 输入捕捉x控制寄存器

14.0 输出比较

14.1 设置产生单个输出脉冲

14.2 设置产生连续输出脉冲

14.3 脉宽调制模式

14.3.1 PWM周期

公式14-1: 计算PWM周期

14.3.2 PWM占空比

公式14-2: 计算最大PWM分辨率

表14-1: 器件工作在4 MIPS(Fcy = 4 MHz)时的PWM频率和分辩率示例

表14-2: 器件工作在16 MIPS(Fcy = 16 MHz)时的PWM频率和分辩率示例

表14-3: 器件工作在40 MIPS(Fcy = 40 MHz)时的PWM频率和分辩率示例

图14-1: 输出比较模块框图

14.4 输出比较寄存器

寄存器14-1: OCxCON: 输出比较x 控制寄存器

15.0 串行外设接口(SPI)

15.1 工作功能说明

图15-1: SPI模块框图

图15-2: SPI主/从连接

图15-3: SPI主控-帧主控模式连接图

图15-4: SPI主控-帧从动模式连接图

图15-5: SPI从动-帧主控模式连接图

图15-6: SPI从动-帧从动模式连接图

公式15-1: 器件工作频率和SPI时钟速度之间的关系

表15-1: SCKx频率示例

寄存器15-1: SPIxSTAT:SPIx 状态和控制寄存器

寄存器15-2: SPIxCON1:SPIx控制寄存器1

寄存器15-3: SPIxCON2:SPIx控制寄存器2

16.0 I2C

16.1 工作模式

16.2 I2C寄存器

16.3 I2C中断

16.4 波特率发生器

图16-1: I2C™ 框图 (x = 1或2)

16.5 I2C模块地址

表16-1: PIC24H支持的7位 I2C™ 从动 地址

16.6 从动地址掩码

16.7 IPMI支持

16.8 广播呼叫地址支持

16.9 自动时钟延长

16.9.1 发送时钟延长

16.9.2 接收时钟延长

16.10 软件控制的时钟延长(STREN = 1)

16.11 斜率控制

16.12 时钟仲裁

16.13 多主机通信、总线冲突和总线仲裁

寄存器16-1: I2CxCON: I2Cx控制寄存器

寄存器16-2: I2CxSTAT: I2Cx状态寄存器

寄存器16-3: I2CxMSK: I2Cx从模式地址掩码寄存器

17.0 通用异步收发器(UART)

图17-1: UART简化框图

17.1 UART 波特率发生器(BRG)

公式17-1: UART波特率 (BRGH = 0)

公式17-2: UART波特率(BRGH = 1)

17.2 在8位数据模式下发送

17.3 在9位数据模式下发送

17.4 间隔或同步发送过程

17.5 在8位或9位数据模式下接收

17.6 使用UxCTS和UxRTS引脚的流控 制

17.7 红外支持

17.7.1 外部IrDA支持――IrDA时钟输出

17.7.2 内置IrDA编码器和解码器

寄存器17-1: UxMODE: UARTx模式寄存器

寄存器17-2: UxSTA:UARTx状态和控制寄存器

18.0 增强型CAN模块

18.1 概述

18.2 帧类型

图18-1: ECAN™ 模块框图

18.3 工作模式

18.3.1 初始化模式

18.3.2 禁止模式

18.3.3 正常工作模式

18.3.4 监听模式

18.3.5 监听所有报文模式

18.3.6 环回模式

18.4 报文接收

18.4.1 接收缓冲器

18.4.2 FIFO缓冲器模式

18.4.3 报文接收过滤器

18.4.4 报文接收过滤器屏蔽寄存器

18.4.5 接收错误

18.4.6 接收中断

18.5 报文发送

18.5.1 发送缓冲器

18.5.2 发送报文优先级

18.5.3 发送过程

18.5.4 远程发送请求的自动处理

18.5.5 中止报文发送

18.5.6 发送错误

18.5.7 发送中断

18.6 波特率设置

18.6.1 位时序

图18-2: ECAN™ 模块的位时序

18.6.2 预分频比设置

公式 18-1: 时钟发生的时间份额

18.6.3 传播时间段

18.6.4 相位段

18.6.5 采样点

18.6.6 同步

寄存器18-1: CiCTRL1: ECAN 模块控制寄存器 1

寄存器18-2: CiCTRL2: ECAN 模块控制寄存器 2

寄存器18-3: CiVEC: ECAN模块中断编码寄存器

寄存器18-4: CiFCTRL: ECAN模块FIFO控制寄存器

寄存器18-5: CiFIFO: ECAN模块FIFO状态寄存器

寄存器18-6: CiINTF: ECAN模块中断标志寄存器

寄存器18-7: CiINTE: ECAN模块中断允许寄存器

寄存器18-8: CiEC: ECAN模块发送/接收错误计数寄存器

寄存器18-9: CiCFG1: ECAN模块波特率配置寄存器1

寄存器18-10: CiCFG2: ECAN模块波特率配置寄存器2

寄存器18-11: CiFEN1: ECAN模块接收过滤器使能寄存器

寄存器18-12: CiBUFPNT1: ECAN模块过滤器0-3缓冲器指针寄存器

寄存器18-13: CiBUFPNT2: ECAN模块过滤器4-7缓冲器指针寄存器

寄存器18-14: CiBUFPNT3: ECAN模块过滤器8-11缓冲器指针寄存器

寄存器18-15: CiBUFPNT4: ECAN模块过滤器12-15缓冲器指针寄存器

寄存器18-16: CiRXFnSID: ECAN模块接收过滤器屏蔽器n标准标识符(n = 0, 1, ..., 15)

寄存器18-17: CiRXFnEID: ECAN模块接收过滤器n扩展标识符(n = 0, 1, ..., 15)

寄存器18-18: CiFMSKSEL1: ECAN模块过滤器7-0屏蔽选择寄存器

寄存器18-19: CiRXMnSID:ECAN模块接收过滤器屏蔽器n标准标识符

寄存器18-20: CiRXMnEID: ECAN 接收过滤器屏蔽器n扩展标识符

寄存器18-21: CiRXFUL1: ECAN模块接收缓冲器满寄存器1

寄存器18-22: CiRXFUL2: ECAN模块接收缓冲器满寄存器2

寄存器18-23: CiRXOVF1: ECAN模块接收缓冲器溢出寄存器1

寄存器18-24: CiRXOVF2: ECAN模块接收缓冲器溢出寄存器2

寄存器18-25: CiTRmnCON: ECAN模块发送/接收缓冲器m 控制寄存器(m = 0,2,4,6; n = 1,3,5,7)

寄存器18-26: CiTRBnSID: ECAN模块缓冲器n标准标识符(n = 0, 1, ..., 31)

寄存器18-27: CiTRBnEID: ECAN模块缓冲器n扩展标识符(n = 0, 1, ..., 31)

寄存器18-28: CiTRBnDLC: ECAN模块缓冲器n数据长度控制(n = 0, 1, ..., 31)

寄存器18-29: CiTRBnDm: ECAN模块缓冲器n数据字段字节m (n = 0, 1, ..., 31; m = 0, 1, ..., 7)(1)

寄存器18-30: CiTRBnSTAT: ECAN模块接收缓冲器n状态寄存器(n = 0, 1, ..., 31)

19.0 10位/12位A/D转换器

19.1 主要特性

19.2 A/D初始化

19.3 ADC和DMA

图19-1: ADC1模块框图

图19-2: ADC2模块框图(1)

公式19-1: A/D转换时钟周期

图19-3: A/D传递函数(以10位ADC为例)

图19-4: ADC转换时钟周期框图

寄存器19-1: ADxCON1:ADCx控制寄存器1 (其中x = 1或2)

寄存器19-2: ADxCON2:ADCx控制寄存器2(其中x = 1或2)

寄存器19-3: ADxCON3:ADCx控制寄存器3

寄存器19-4: ADxCON4:ADCx控制寄存器4

寄存器19-5: ADxCHS123: ADCx输入通道1、2和3选择寄存器

寄存器19-6: ADxCHS0: ADCx输入通道0选择寄存器

寄存器19-7: ADxCSSH: ADCx输入扫描选择寄存器的高位字(1)

寄存器19-8: ADxCSSL: ADCx输入扫描选择寄存器的低位字(1)

寄存器19-9: AD1PCFGH:ADC1端口配置寄存器的高位字(1,2)

寄存器19-10: ADxPCFGL:ADCx端口配置寄存器的低位字(1,2)

20.0 特殊功能

20.1 配置位

表20-1: 器件配置寄存器的映射

表20-2: PIC24H配置位的说明

20.2 片内稳压器

图20-1: 片内稳压器的连接(1)

20.3 看门狗定时器(WDT)

图20-2: WDT框图

20.4 JTAG接口

20.5 代码保护和 CodeGuard™ 安全性

20.6 在线串行编程

20.7 在线调试器

21.0 指令集综述

表21-1: 操作码说明中使用的符号

表21-2: 指令集汇总

22.0 开发支持

22.1 MPLAB集成开发环境软件

22.2 MPASM 汇编器

22.3 MPLAB C18和MPLAB C30 C编译器

22.4 MPLINK目标链接器/ MPLIB目标库管理器

22.5 MPLAB ASM30汇编器、 链接器和库管理器

22.6 MPLAB SIM软件模拟器

22.7 MPLAB ICE 2000高性能在线仿真器

22.8 MPLAB REAL ICE在线仿真器系统

22.9 MPLAB ICD 2在线调试器

22.10 MPLAB PM3器件编程器

22.11 PICSTART Plus开发编程器

22.12 PICkit 2开发编程器

22.13 演示、开发和评估板

23.0 电气特性

23.1 直流特性

表 23-1: 工作速度(MIPS)与电压

表 23-2: 热工作条件

表 23-3: 热封装特性

表 23-4: 直流温度和电压规范

表 23-5: 直流特性: 工作电流(Idd)

表 23-6: 直流特性:空闲电流(iidle)

表 23-7: 直流特性:掉电电流(Ipd)

表 23-8: 直流特性:打盹电流(Idoze)

表 23-9: 直流特性: I/O引脚输入规范

表 23-10: 直流特性: I/O引脚输出规范

表 23-11: 直流特性:程序存储器

表 23-12: 内部稳压器规范

23.2 交流特性和时序参数

表 23-13: 温度和电压规范―交流

图23-1: 器件时序规范的负载条件

表 23-14: 输出引脚上的容性负载要求

图23-2: 外部时钟时序

表 23-15: 外部时钟时序要求

表 23-16: PLL时钟时序规范(Vdd = 3.0V至3.6V)

表 23-17: 交流特性: 内部RC精度

表 23-18: 内部RC精度

图23-3: CLKO和I/O时序特性

表 23-19: CLKO和I/O时序要求

图23-4: 复位、看门狗定时器、振荡器起振定时器和上电延时定时器的时序特性

表 23-20: 复位、看门狗定时器、振荡器起振定时器、上电延时定时器和欠压复位时序要求

图23-5: Timer1、Timer2、Timer3、 Timer4、Timer5、Timer6、Timer7、Timer8 和 Timer9外部时钟时序特性

表 23-21: Timer1外部时钟时序要求(1)

表 23-22: Timer2、Timer4、Timer6和Timer8的外部时钟时序要求

表 23-23: Timer3、Timer5、Timer7和Timer9的外部时钟时序要求

图23-6: 输入捕捉(CAPx)时序特性

表 23-24: 输入捕捉时序要求

图23-7: 输出比较模块(OCx)时序特性

表 23-25: 输出比较模块时序要求

图23-8: OC/PWM模块时序特性

表 23-26: 简单OC/PWM模式时序要求

图23-9: SPIx模块主模式(CKE = 0)时序特性

表 23-27: SPIx主模式(CKE = 0)时序要求

图23-10: SPIx模块主模式(CKE = 1)时序特性

表 23-28: SPIx模块主模式(cke = 1)时序要求

图23-11: SPIx模块从模式(CKE = 0)时序特性

表 23-29: SPIx模块从模式(cke = 0)时序要求

图23-12: SPIx模块从模式(CKE = 1)时序特性

表 23-30: SPIx模块从模式(cke = 1)时序要求

图23-13: I2Cx总线启动/停止位时序特性(主模式)

图23-14: I2Cx总线数据时序特性(主模式)

表 23-31: I2Cx总线数据时序要求(主模式)

图23-15: I2Cx总线启动/停止位时序特性(从模式)

图23-16: I2Cx总线数据时序特性(从模式)

表 23-32: I2Cx总线数据时序要求(从模式)

图 23-17: ECAN.模块 I/O时序特性

表 23-33: ECAN.模块 I/O时序要求

表 23-34: A/D模块规范

图23-18: A/D转换(10位模式)时序特性(chps<1:0> = 01,SIMSAM = 0,asam = 0, ssrc<2:0> = 000)

图23-19: A/D转换(10位模式)时序特性(chps<1:0> = 01,SIMSAM = 0,asam = 1, ssrc<2:0> = 111,SAMC<4:0> = 00001)

表 23-35: A/D转换(10位模式)时序要求

图23-20: A/D转换(12位模式)时序特性(asam = 0, ssrc<2:0> = 000)

表 23-36: A/D转换(12位模式)时序要求

24.0 封装信息

24.1 封装标识信息

24.2 封装详细信息

全球销售及服务网点

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc