6

5

4

3

2

1

REVISION RECORD

LTR

ECO NO:

APPROVED:

DATE:

D

C

B

A

R0100

R0201_0R

C0100

C0201_47NF

0.075mm£¬×ßÏß±£»¤

1

0

1

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

[11]

[11]

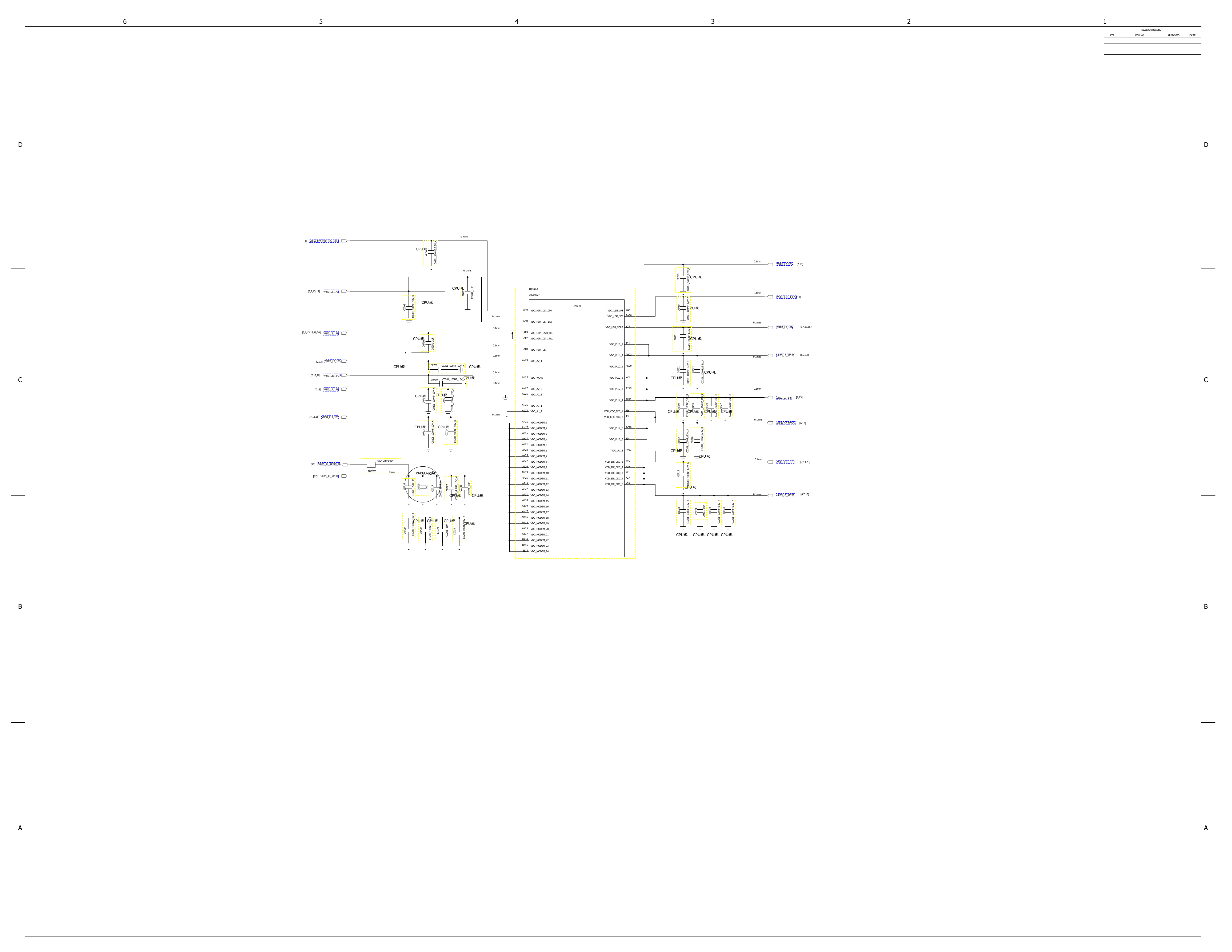

BBCLK1

MSM_BBCLK1_EN

[11]

SLEEP_CLK

[11,23]

[15,23]

PM_PON_RESET_N

MSM_RESOUT_N

[11,23]

MSM_PS_HOLD

[23]

[23]

[23]

[23]

[23]

[23]

JTAG_RESOUT_N

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST_N

[11,15]

VREF_LPDDR3

SH8

QL1022_RF-LNA

SH7

QL1022_WIFI

SH9

QL1022_POWER

SH10

QL1022_RF

SH11

QL1022_PA

SH12

QL1022_FP

F1

F2

F3

F4

FIDUCIAL_WITHPASTE

FIDUCIAL_WITHPASTE

FIDUCIAL_WITHPASTE

FIDUCIAL_WITHPASTE

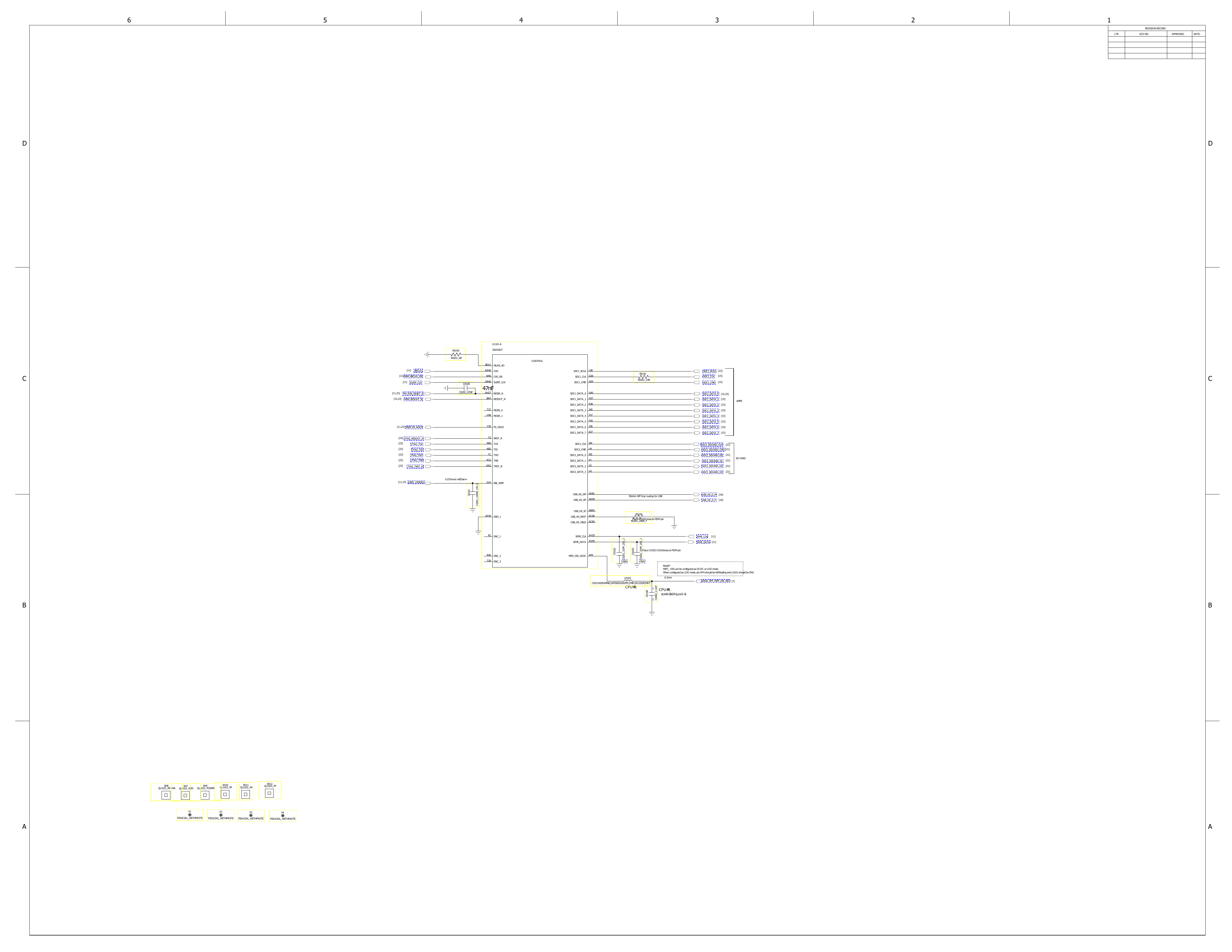

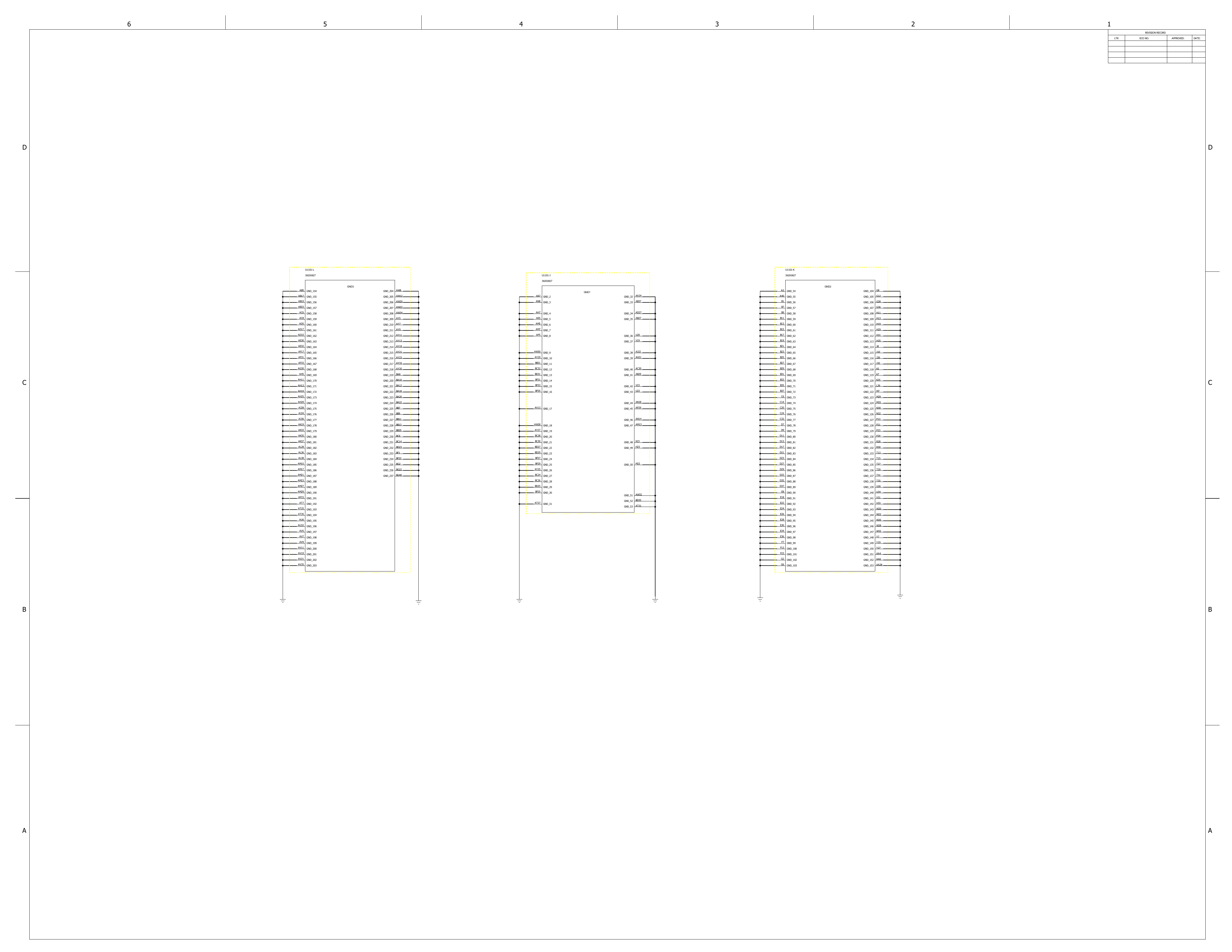

U1101-A

39200827

BD13

AA40

W40

AR40

47nF

AH37

BA4

WLAN_XO

CXO

CXO_EN

SLEEP_CLK

RESIN_N

RESOUT_N

T37

U38

Y39

Y3

AB3

AB1

Y1

AC2

AA2

MODE_0

MODE_1

PS_HOLD

SRST_N

TCK

TDI

TDO

TMS

TRST_N

G14

EBI_VREF

AF39

GND_1

R2

DNC_1

R40

T39

DNC_2

DNC_3

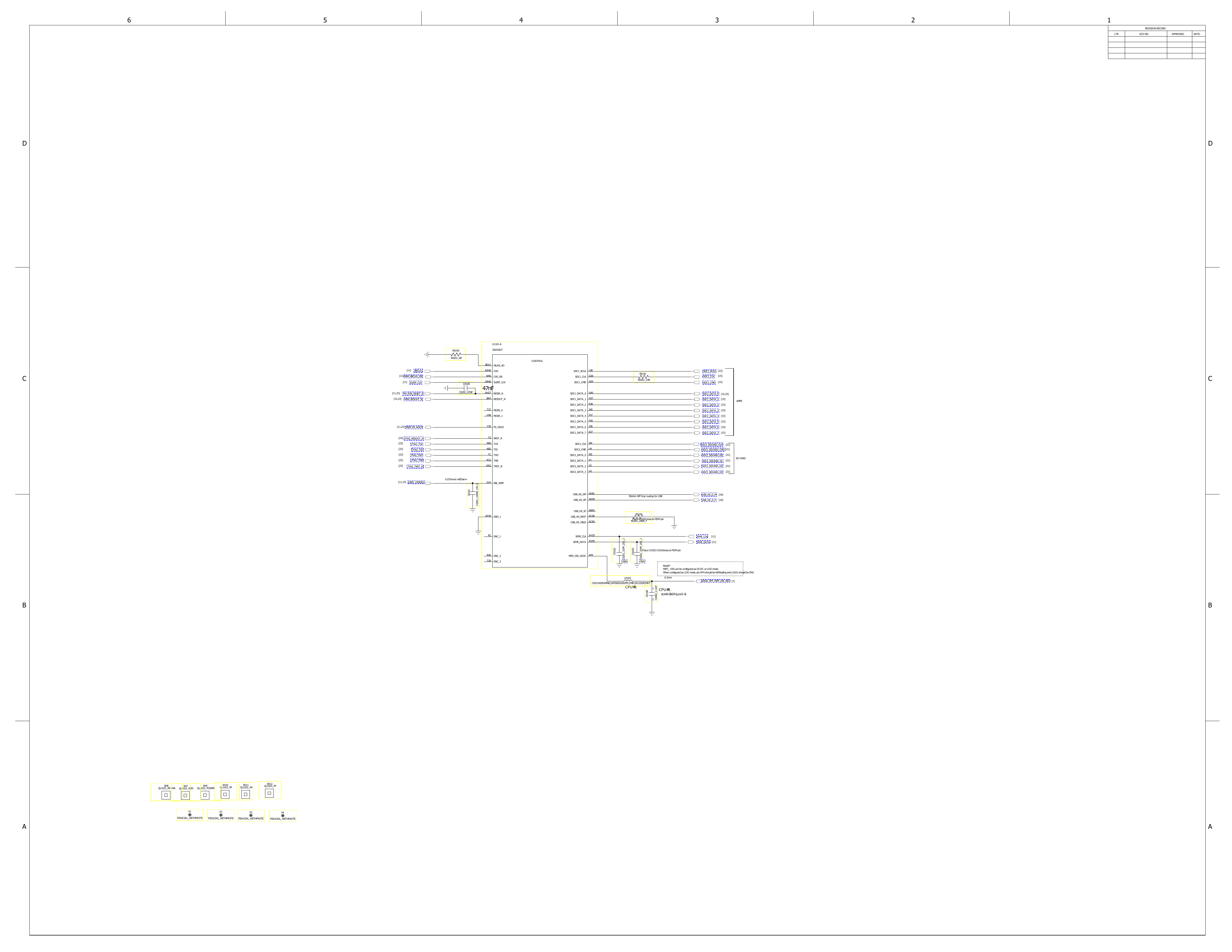

CONTROL

SDC1_RCLK

SDC1_CLK

SDC1_CMD

SDC1_DATA_0

SDC1_DATA_1

SDC1_DATA_2

SDC1_DATA_3

SDC1_DATA_4

SDC1_DATA_5

SDC1_DATA_6

SDC1_DATA_7

SDC2_CLK

SDC2_CMD

SDC2_DATA_0

SDC2_DATA_1

SDC2_DATA_2

SDC2_DATA_3

L38

G38

H39

G40

H37

E38

J40

F37

F39

J38

K37

W4

U4

W2

V1

V3

U2

USB_HS_DM

USB_HS_DP

USB_HS_ID

USB_HS_REXT

USB_HS_VBUS

AE40

AD39

AB39

AC38

AC40

SPMI_CLK

SPMI_DATA

AH39

AG40

MIPI_DSI_DCDC

AF9

R0101

R0201_24R

90ohm Diff Imp routing for USB

R0104

Place R0104 close to MSM pin

R0201_200R_F

2

0

1

0

C

J

_

V

5

2

_

F

P

3

3

_

1

0

2

0

C

GND

3

0

1

0

C

J

_

V

5

2

_

F

P

3

3

_

1

0

2

0

C

GND

Place C0102 C0103close to MSM pin

eMMC

SD CARD

SDC1_RCLK

SDC1_CLK

SDC1_CMD

[15]

[15]

[15]

SDC1_DATA_0

SDC1_DATA_1

SDC1_DATA_2

SDC1_DATA_3

SDC1_DATA_4

SDC1_DATA_5

SDC1_DATA_6

SDC1_DATA_7

[15,23]

[15]

[15]

[15]

[15]

[15]

[15]

[15]

SDC2_SDCARD_CLK

SDC2_SDCARD_CMD

SDC2_SDCARD_D0

SDC2_SDCARD_D1

SDC2_SDCARD_D2

SDC2_SDCARD_D3

[21]

[21]

[21]

[21]

[21]

[21]

USB_HS_D_M

USB_HS_D_P

[16]

[16]

SPMI_CLK

SPMI_DATA

[11]

[11]

CIG21W2R2MNE//APIS05G2R2MT//MPL2012S2R2MHT

L0101

CPU±³²¿

6

0

1

0

C

1

F

U

2

.

2

_

2

0

4

0

C

2

Note£º

MIPI_DSI can be configured as DCDC or LDO mode.

When configured as LDO mode, pin AF9 should be left floating and L0101 should be DNI.

0.2mm

VDDA_0P4_MIPI_DSI_REG

[7]

CPU±³²¿

BOMÑ¡ÓÃÄÍѹֵ10VÎïÁÏ

D

C

B

A

�

6

5

4

3

2

1

REVISION RECORD

LTR

ECO NO:

APPROVED:

DATE:

D

C

B

A

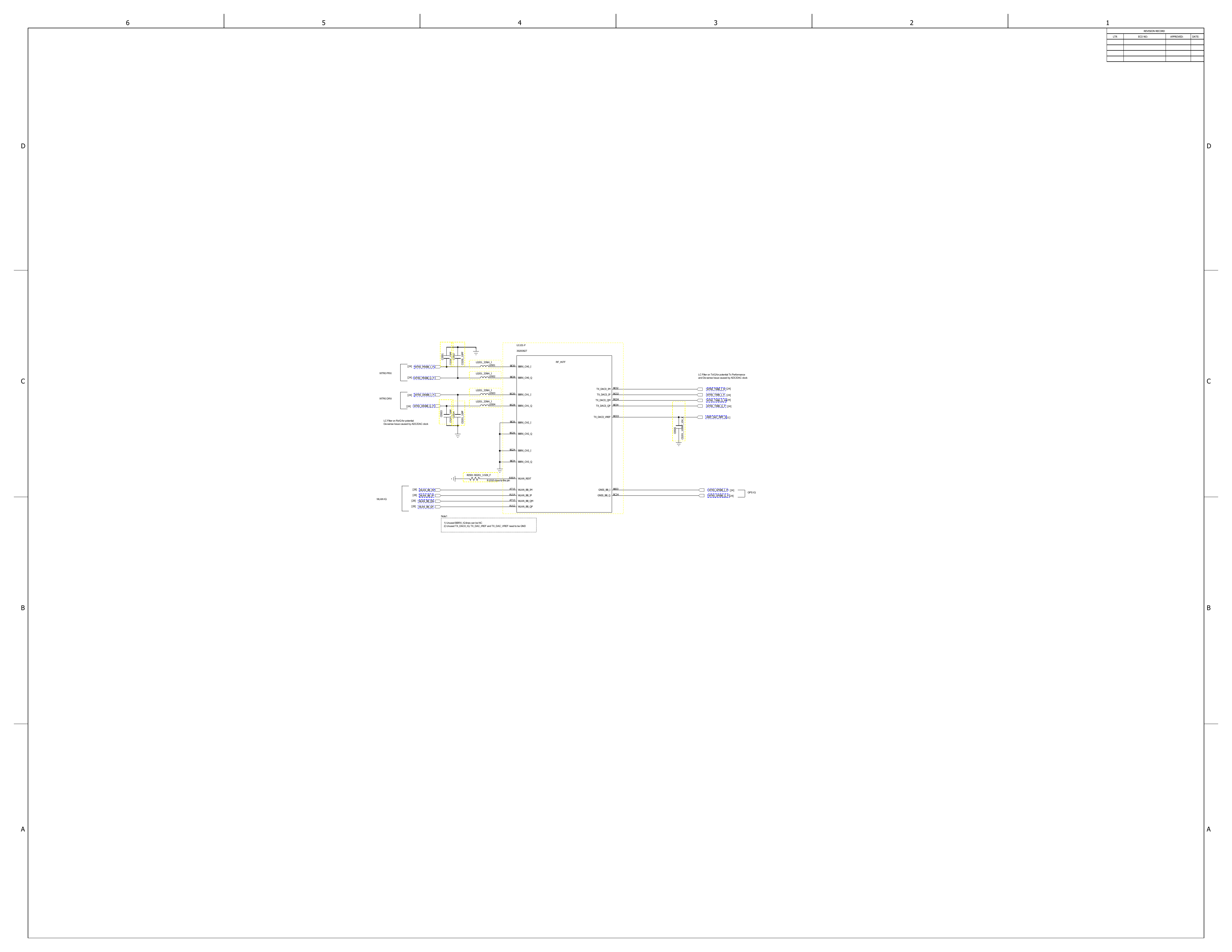

[15]

[15]

[15]

[15]

[15]

[15]

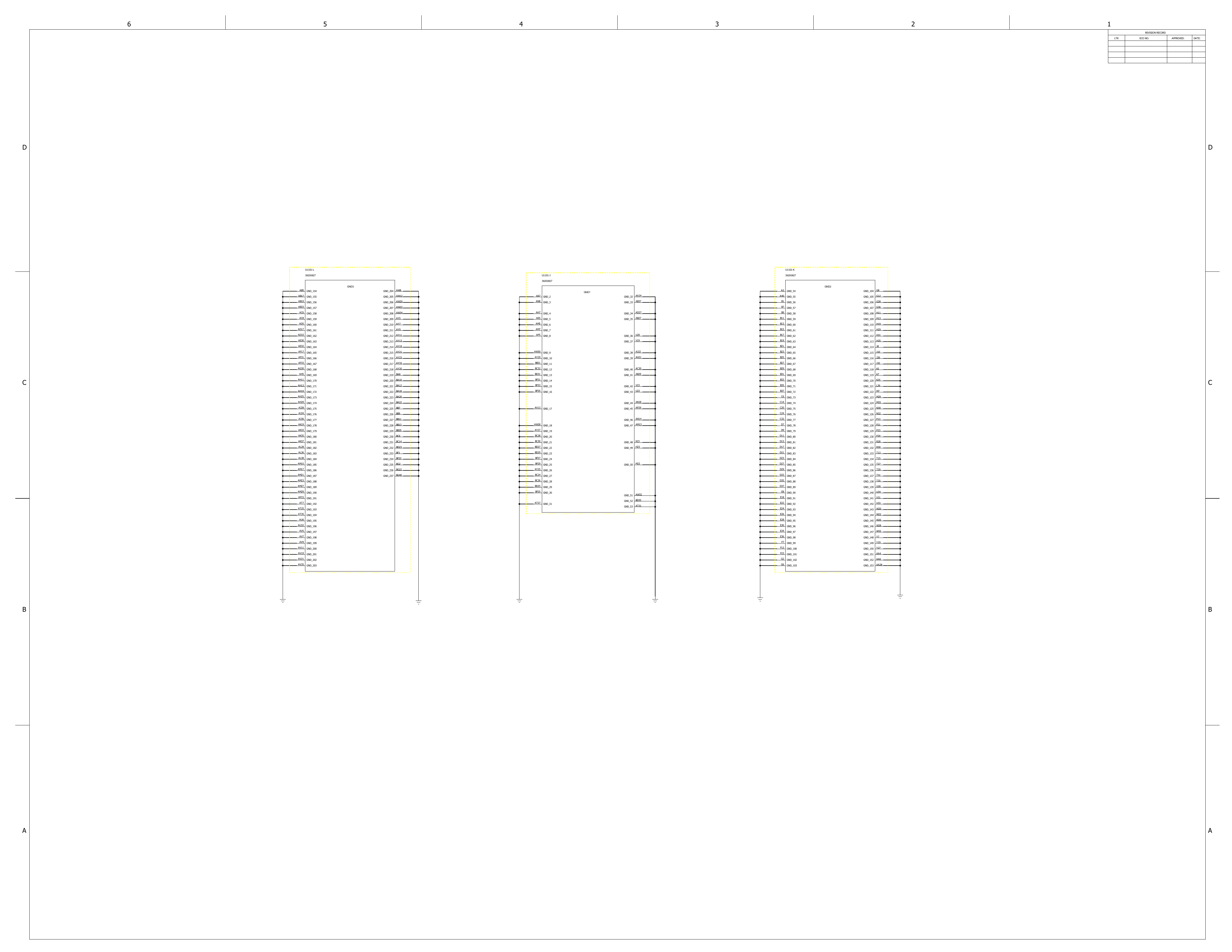

EBI0_CS0_N

EBI0_CS1_N

EBI0_CLK_C

EBI0_CLK_T

EBI0_CKE0

EBI0_CKE1

EBI0_DM[0:3]

[15]

[15]

EBI0_DQS0_C

EBI0_DQS0_T

[15]

[15]

[15]

[15]

[15]

[15]

EBI0_DQS1_C

EBI0_DQS1_T

EBI0_DQS2_C

EBI0_DQS2_T

EBI0_DQS3_C

EBI0_DQS3_T

[15]

EBI0_CA[0:9]

EBI0_DM0

EBI0_DM1

EBI0_DM2

EBI0_DM3

EBI0_CA0

EBI0_CA1

EBI0_CA2

EBI0_CA3

EBI0_CA4

EBI0_CA5

EBI0_CA6

EBI0_CA7

EBI0_CA8

EBI0_CA9

U1101-B

39200827

EBI0_CS_N_0

EBI0_CS_N_1

EBI0_CKB

EBI0_CK

EBI0_CKE_0

EBI0_CKE_1

EBI0_DM_0

EBI0_DM_1

EBI0_DM_2

EBI0_DM_3

EBI0_DQSB_0

EBI0_DQS_0

EBI0_DQSB_1

EBI0_DQS_1

EBI0_DQSB_2

EBI0_DQS_2

EBI0_DQSB_3

EBI0_DQS_3

EBI0_CA_0

EBI0_CA_1

EBI0_CA_2

EBI0_CA_3

EBI0_CA_4

EBI0_CA_5

EBI0_CA_6

EBI0_CA_7

EBI0_CA_8

EBI0_CA_9

C4

D3

G10

E10

C2

D1

C22

C26

D15

C34

F21

E20

D25

F25

E16

F17

E32

G32

A4

B5

B3

E6

D5

E4

F3

F1

E2

G4

EBI0

EBI0_CAL

G18

EBI_CAL_REXT

Place R0200 close to MSM Pin

R0200

R0201_240R_F

EBI0_DQ[0:31]

[15]

EBI0_DQ_0

EBI0_DQ_1

EBI0_DQ_2

EBI0_DQ_3

EBI0_DQ_4

EBI0_DQ_5

EBI0_DQ_6

EBI0_DQ_7

EBI0_DQ_8

EBI0_DQ_9

EBI0_DQ_10

EBI0_DQ_11

EBI0_DQ_12

EBI0_DQ_13

EBI0_DQ_14

EBI0_DQ_15

EBI0_DQ_16

EBI0_DQ_17

EBI0_DQ_18

EBI0_DQ_19

EBI0_DQ_20

EBI0_DQ_21

EBI0_DQ_22

EBI0_DQ_23

EBI0_DQ_24

EBI0_DQ_25

EBI0_DQ_26

EBI0_DQ_27

EBI0_DQ_28

EBI0_DQ_29

EBI0_DQ_30

EBI0_DQ_31

A16

C16

A18

C18

A20

D19

A22

A24

A26

A28

C28

A30

C30

D31

A32

A34

A8

A6

C8

A10

A12

C10

A14

C12

C36

A36

D39

C38

A38

E40

C40

B39

EBI0_DQ0

EBI0_DQ1

EBI0_DQ2

EBI0_DQ3

EBI0_DQ4

EBI0_DQ5

EBI0_DQ6

EBI0_DQ7

EBI0_DQ8

EBI0_DQ9

EBI0_DQ10

EBI0_DQ11

EBI0_DQ12

EBI0_DQ13

EBI0_DQ14

EBI0_DQ15

EBI0_DQ16

EBI0_DQ17

EBI0_DQ18

EBI0_DQ19

EBI0_DQ20

EBI0_DQ21

EBI0_DQ22

EBI0_DQ23

EBI0_DQ24

EBI0_DQ25

EBI0_DQ26

EBI0_DQ27

EBI0_DQ28

EBI0_DQ29

EBI0_DQ30

EBI0_DQ31

D

C

B

A

�

6

5

4

3

2

1

REVISION RECORD

LTR

ECO NO:

APPROVED:

DATE:

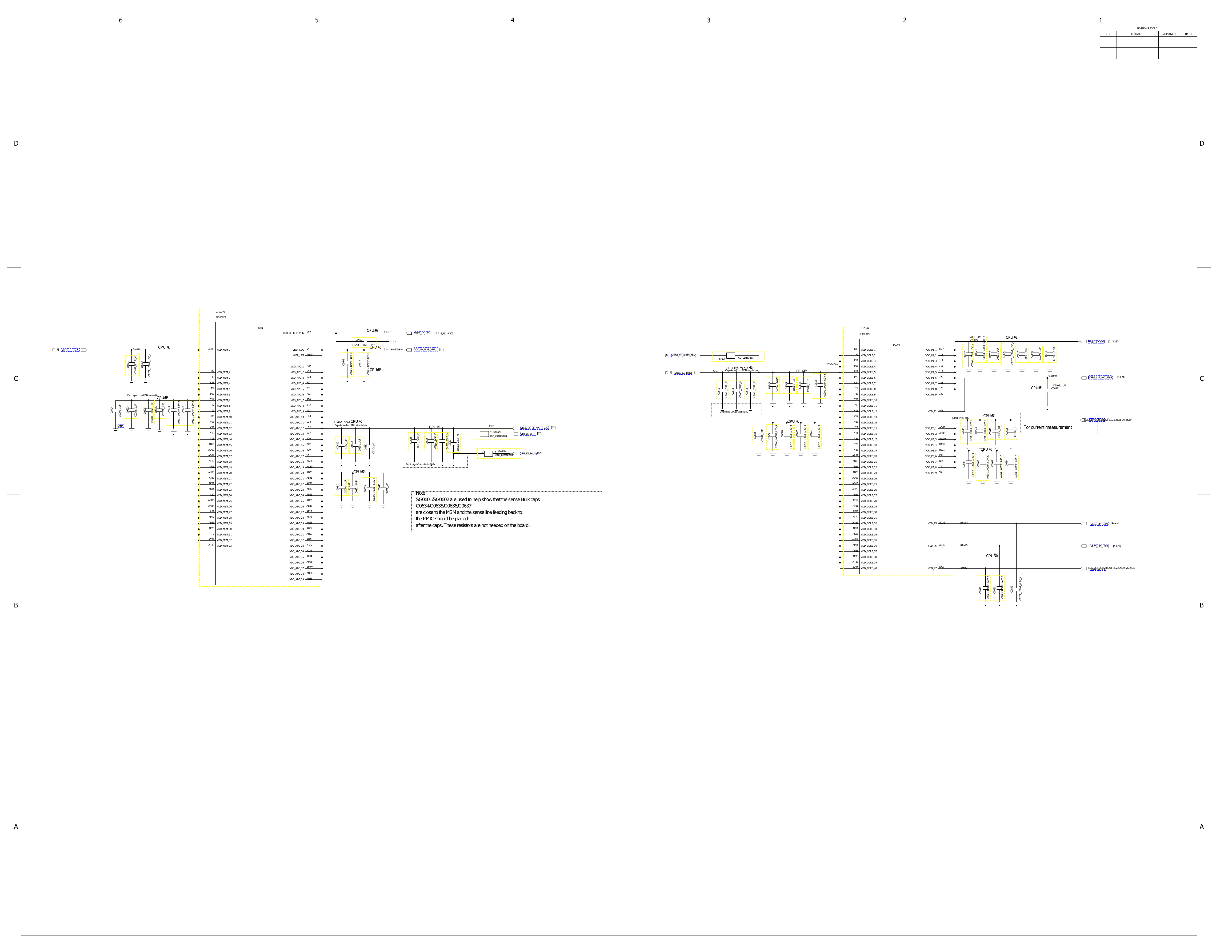

Note: Asterisks (*) indicate modem power management (MPM) wake-up pins

R0311

R0201_1K_F

R0310

R0201_1K_F

U1101-C

39200827

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24

GPIO_25

GPIO_26

GPIO_27

GPIO_28

GPIO_29

GPIO_30

GPIO_31

GPIO_32

GPIO_33

GPIO_34

GPIO_35

GPIO_36

*

*

*

*

*

*

*

*

*

*

*

*

*

U6

P7

T5

P5

P1

R4

P3

T1

BF9

BE8

BG8

BF7

BG14

BF15

BD15

BE14

BD7

BG6

BE6

BF5

AU40

BA40

AT39

AP39

BF11

BG10

N2

N4

M5

M3

M1

K1

L2

L4

H1

K3

J2

GPIO1

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

GPIO_37

GPIO_38

GPIO_39

GPIO_40

GPIO_41

GPIO_42

GPIO_43

GPIO_44

GPIO_45

GPIO_46

GPIO_47

GPIO_48

GPIO_49

GPIO_50

GPIO_51

GPIO_52

GPIO_53

GPIO_54

GPIO_55

GPIO_56

GPIO_57

GPIO_58

GPIO_59

GPIO_60

GPIO_61

GPIO_62

GPIO_63

GPIO_64

GPIO_65

GPIO_66

GPIO_67

GPIO_68

GPIO_69

GPIO_70

GPIO_71

GPIO_72

GPIO_73

P39

H7

J4

H3

M37

K39

M39

N38

P37

R36

AM39

L40

AB35

H5

AE38

AD37

AF37

AG38

AL40

AJ40

AK39

AJ38

U40

V39

V37

W38

N40

R38

BE12

BD11

BF13

BG12

BG18

BF19

BG16

BF17

BE18

Òý³ö²âÊÔµã

[19]

CAM_ID0

UART_MSM_TX

UART_MSM_RX

SMB_FG_I2C_SDA

SMB_FG_I2C_SCL

[23]

[23]

[3,9]

[3,9]

[9]

[3,18]

[3,18]

GP_PDM_A0

TP_I2C_SDA

TP_I2C_SCL

[3,20]

[3,20]

SENSOR_I2C_SDA

SENSOR_I2C_SCL

FP_SPI_MOSI

[20]

[20]

FP_SPI_MISO

FP_SPI_CS

FP_SPI_CLK

PCB_ID3

PCB_ID4

LCM_I2C_SDA

LCM_I2C_SCL

LCD_TE0

[20]

[20]

[22]

[22]

[3,10]

[3,10]

[18]

[19]

[19]

CAM_MCLK0

CAM_MCLK2

Finger Touch_SPI

PCB_ID

[3,19]

[3,19]

[3,19]

[3,19]

[10]

CAM_I2C_SDA0

CAM_I2C_SCL0

CAM_I2C_SDA1

CAM_I2C_SCL1

GPIO_TORCH_EN

FLASH_STROBE_NOW

CAM_PWDN0

[19]

[19]

CAM_RST0

[10]

Òý³ö²âÊÔµã

ALS_INT

ÖжÏÐźÅ

Gsensor_INT

ÖжÏÐźÅ

[23]

FORCE_USB_BOOT

ALSP_INT_N

[20]

[19]

CAM_PWDN2

[19]

CAM_RST1

[19]

CAM_ID2

ACCL_INT1_N

[20]

[20]

CAP_INT_N

LCM_ENN

LCM_ENP

CAM_PWR_EN

FP_INT_N

UIM_BATT_ALARM

[10]

[10]

[19]

[20]

[11]

UIM1_DATA

UIM1_CLK

UIM1_RESET

INT_SIM1

UIM2_DATA

UIM2_CLK

UIM2_RESET

INT_SIM2

LCD_ID0

LCD_RST_N

SMB1360_INT

[21]

[21]

[21]

[21]

[21]

[21]

[21]

[21]

[18]

[18]

[9]

M-Sensor_INT

[11,21]

[18]

INTN_VCHG_LED

[18]

TP_RST_N

[18]

TP_INT_N

LCD_ID1

SDCARD_DET_N

SPKPA_EN

[17]

CDC_PDM_CLK

CDC_PDM_SYNC

CDC_PDM_TX

CDC_PDM_RX0

CDC_PDM_RX1

[14]

[14]

[14]

[14]

[14]

[14]

[28]

[28]

[28]

[28]

[28]

CDC_PDM_RX2

[28]

BT_SSBI

WL_CMD_DATA_2

WL_CMD_DATA_1

WL_CMD_DATA_0

WL_CMD_SET

WL_CMD_CLK

FM_SSBI

[28]

FM_DATA

[28]

[28]

BT_CTL

[28]

BT_DATA

Note

Internal develope use

( Boot_config [5], APPS_BOOT_FROM_ROM )

PCB_ID

[22]

PCB_ID1

[22]

KEY_VOL_UP_N

PCB_ID

[22]

PCB_ID2

Finger Touch

[25,26,30]

[25,26,30]

[20]

[20]

FP_ID

FP_RST_N

MIPI_RFFE1_CLK

MIPI_RFFE1_DATA

[24]

[26]

[26]

[27]

[26]

[26]

GRFC0_PDET_SEL

MB2_PRX_B2/B3_SW

MB3_PRX_B1/B4_SW

HB2_DRX_B7/38/41_SW

HB2_PRX_B38/B41/B7_SW

LB2_PRX_B20/28_SW

BE20

BD5

BC4

BE4

BD3

BG4

BE2

BF3

BD1

BB3

BC2

BC22

BC18

BB19

BC20

BB17

BC16

AD1

Y5

BE16

BD17

BD19

BD21

BG20

BE22

BF21

BC40

BD39

AW40

AV39

AR38

BB39

AU38

BE40

BF39

AT37

U1101-D

39200827

GPIO_74

GPIO_75

GPIO_76

GPIO_77

GPIO_78

GPIO_79

GPIO_80

GPIO_81

GPIO_82

GPIO_83

GPIO_84

GPIO_85

GPIO_86

GPIO_87

GPIO_88

GPIO_89

GPIO_90

GPIO_91

GPIO_92

GPIO_93

GPIO_94

GPIO_95

GPIO_96

GPIO_97

GPIO_98

GPIO_99

GPIO_100

GPIO_101

GPIO_102

GPIO_103

GPIO_104

GPIO_105

GPIO_106

GPIO_107

GPIO_108

GPIO_109

GPIO2

*

*

*

*

*

*

*

GPIO_110

GPIO_111

GPIO_112

GPIO_113

GPIO_114

GPIO_115

GPIO_116

GPIO_117

GPIO_118

GPIO_119

GPIO_120

GPIO_121

GPIO_122

GPIO_123

GPIO_124

GPIO_125

GPIO_126

GPIO_127

GPIO_128

GPIO_129

GPIO_130

GPIO_131

GPIO_132

GPIO_133

BC38

BE38

AV37

AW38

AY37

BA38

BG38

BC36

BB37

AW36

BD37

BE36

BF37

BG36

AP37

BC10

BC12

AY39

BE10

BC8

BD9

M35

P35

N36

*

*

*

*

*

DRX_TUNER_CTRL1

DRX_TUNER_CTRL2

DRX_SPDT_SW1

DRX_SPDT_SW2

DRX_SPDT_SW3

PRX_TUNER_CTRL2

PRX_TUNER_CTRL1

[27]

[27]

[27]

[27]

[27]

[16]

[16]

[29]

EXT_GPS_LNA_EN

CH0_GSM_TX_PHASE_D0

RFFE5_CLK

RFFE5_DATA

[24]

[24]

[24]

CAM_PWR_EN_FRONT

[19]

Note: Do not have pull-ups on the following GPIOs unless intend for boot

or secure- boot related configurations:

GPIO_91, 107, 109

I2C PULL-UP RESISTORS

Note: Ensure SW sets these GPIOs (Sensor, CTP and

Camera I2C bus) to inout pull down when the peripherals

are powered off to eliminate leakage.

G+A Sensor & M-Sensor

SMB1360 Charge IC+ Charge LED IIC

VREG_L6_1P8

[3,6,7,13,18,19,20]

VREG_L5_1P8

[3,6,9,13,14,15,18,20][21,22,23,25,26,28,30]

2

0

3

0

R

K

2

.

2

_

1

0

2

0

R

3

0

3

0

R

K

2

.

2

_

1

0

2

0

R

6

0

3

0

R

K

2

.

2

_

1

0

2

0

R

7

0

3

0

R

K

2

.

2

_

1

0

2

0

R

LCM +/-5V VSP/VSN Driver

0

0

3

0

R

K

2

.

2

_

1

0

2

0

R

1

0

3

0

R

K

2

.

2

_

1

0

2

0

R

VREG_L6_1P8

[3,6,7,13,18,19,20]

[3,10]

[3,10]

LCM_I2C_SDA

LCM_I2C_SCL

GPIO

GPIO_3

GPIO_111

GPIO_112

GPIO_88

BOOT_CONFIG

BOOT_CONFIG[0]/WDOG_DISABLE

BOOT_CONFIG[1]

BOOT_CONFIG[2]

BOOT_CONFIG[3]

BOOT_CONFIG[3:1]

0b000

0b010

0b100

BOOT_CONFIG

SDC1 -> SDC2 -> USB2.0

SDC1

SDC2-> SDC1

Default Boot Config (0b000) is SDC1(eMMC)

[3,20]

[3,20]

SENSOR_I2C_SDA

SENSOR_I2C_SCL

VREG_L5_1P8

[3,6,9,13,14,15,18,20][21,22,23,25,26,28,30]

[3,18]

[3,18]

TP_I2C_SDA

TP_I2C_SCL

TP

8

0

3

0

R

K

2

.

2

_

1

0

2

0

R

9

0

3

0

R

K

2

.

2

_

1

0

2

0

R

[3,9]

[3,9]

SMB_FG_I2C_SDA

SMB_FG_I2C_SCL

VREG_L6_1P8

[3,6,7,13,18,19,20]

[3,19]

CAM_I2C_SDA0

[3,19]

CAM_I2C_SCL0

Rear Camera

VREG_L5_1P8

[3,6,9,13,14,15,18,20][21,22,23,25,26,28,30]

K

2

.

2

_

1

0

2

0

R

5

0

3

0

R

K

2

.

2

_

1

0

2

0

R

4

0

3

0

R

[3,19]

[3,19]

CAM_I2C_SDA1

CAM_I2C_SCL1

Front Camera

K

2

.

2

_

1

0

2

0

R

4

1

3

0

R

K

2

.

2

_

1

0

2

0

R

5

1

3

0

R

D

C

B

A

D

C

B

A

�

6

5

4

3

2

1

REVISION RECORD

LTR

ECO NO:

APPROVED:

DATE:

D

C

B

A

D

C

B

A

REAR CAMERA

FRONT CAMERA

[19]

[19]

[19]

[19]

[19]

[19]

[19]

[19]

[19]

[19]

[19]

[19]

[19]

[19]

[19]

[19]

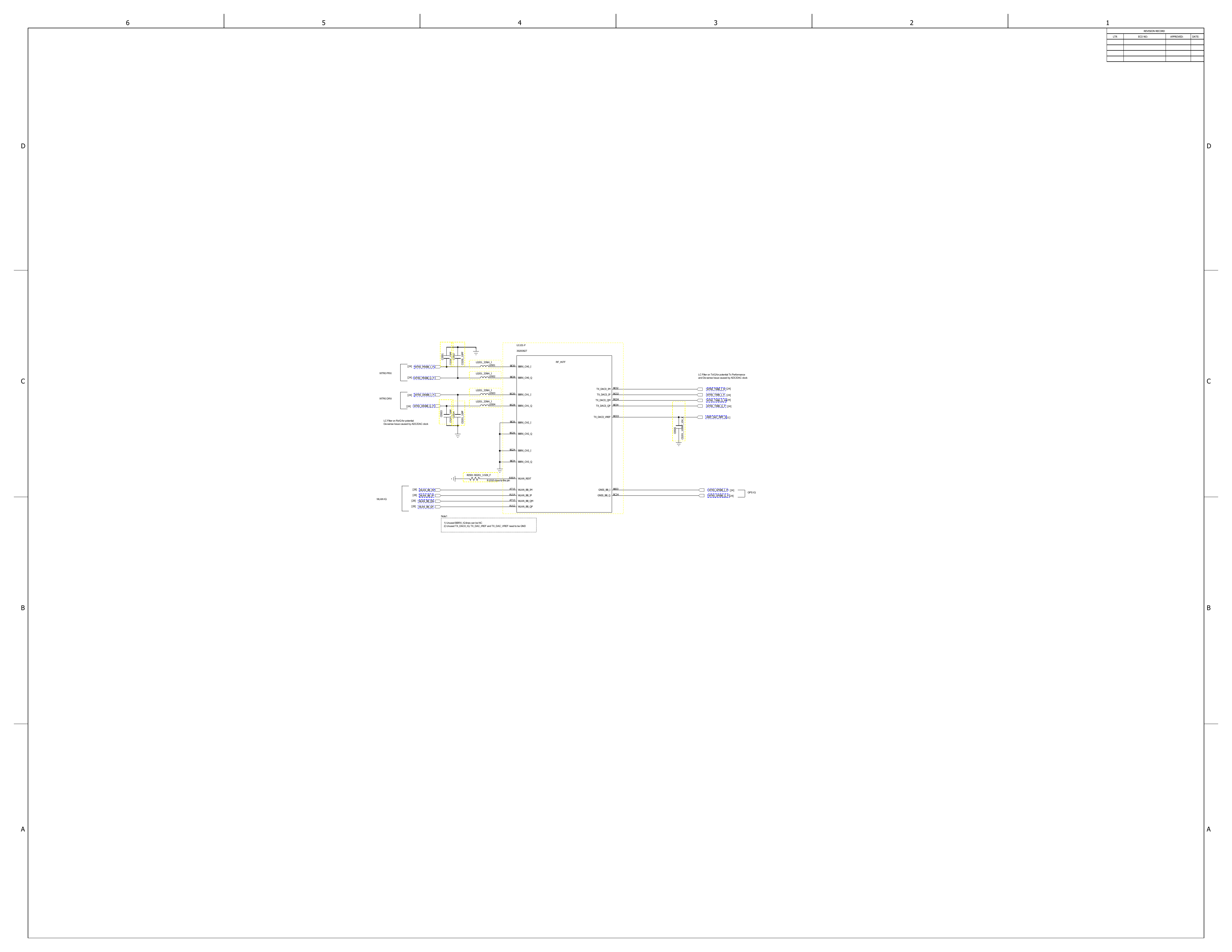

MIPI_CSI0_CLK_N

MIPI_CSI0_CLK_P

MIPI_CSI0_LANE0_N

MIPI_CSI0_LANE0_P

MIPI_CSI0_LANE1_N

MIPI_CSI0_LANE1_P

MIPI_CSI0_LANE2_N

MIPI_CSI0_LANE2_P

MIPI_CSI0_LANE3_N

MIPI_CSI0_LANE3_P

MIPI_CSI1_CLK_N

MIPI_CSI1_CLK_P

MIPI_CSI1_LANE0_N

MIPI_CSI1_LANE0_P

MIPI_CSI1_LANE1_N

MIPI_CSI1_LANE1_P

MIPI

U1101-E

39200827

AE2

AF1

AG2

AH1

AC4

AD3

AE4

AF3

AJ2

AK1

AG4

AH3

AE6

AF5

AL2

AM1

AJ4

AK3

AP1

AN2

MIPI_CSI0_LN0_N

MIPI_CSI0_LN0_P

MIPI_CSI0_LN1_N

MIPI_CSI0_LN1_P

MIPI_CSI0_LN2_N

MIPI_CSI0_LN2_P

MIPI_CSI0_LN3_N

MIPI_CSI0_LN3_P

MIPI_CSI0_LN4_N

MIPI_CSI0_LN4_P

MIPI_CSI1_LN0_N

MIPI_CSI1_LN0_P

MIPI_CSI1_LN1_N

MIPI_CSI1_LN1_P

MIPI_CSI1_LN2_N

MIPI_CSI1_LN2_P

MIPI_CSI1_LN3_N

MIPI_CSI1_LN3_P

MIPI_CSI1_LN4_N

MIPI_CSI1_LN4_P

MIPI_DSI0_CLK_N

MIPI_DSI0_CLK_P

MIPI_DSI0_LN0_N

MIPI_DSI0_LN0_P

MIPI_DSI0_LN1_N

MIPI_DSI0_LN1_P

MIPI_DSI0_LN2_N

MIPI_DSI0_LN2_P

MIPI_DSI0_LN3_N

MIPI_DSI0_LN3_P

MIPI_DSI1_CLK_N

MIPI_DSI1_CLK_P

MIPI_DSI1_LN0_N

MIPI_DSI1_LN0_P

MIPI_DSI1_LN1_N

MIPI_DSI1_LN1_P

MIPI_DSI1_LN2_N

MIPI_DSI1_LN2_P

MIPI_DSI1_LN3_N

MIPI_DSI1_LN3_P

AN4

AP3

AL4

AM3

AR2

AT1

AU2

AV1

AR4

AT3

AU4

AV3

AW2

AY1

AR6

AT5

BA2

BB1

AW4

AY3

MIPI_DSI0_CLK_N

MIPI_DSI0_CLK_P

MIPI_DSI0_LANE0_N

MIPI_DSI0_LANE0_P

MIPI_DSI0_LANE1_N

MIPI_DSI0_LANE1_P

MIPI_DSI0_LANE2_N

MIPI_DSI0_LANE2_P

MIPI_DSI0_LANE3_N

MIPI_DSI0_LANE3_P

[18]

[18]

[18]

[18]

[18]

[18]

[18]

[18]

[18]

[18]

LCD_DISPLAY

Note: If best EMI practices are followed for MIPI CSI/DSI signals, there is no need

for common mode choke filters. You may choose to have placeholders for

common mode depending upon your design constraints.

Extreme care must be taken that no stubs are created by doing so.

10_CAM_FLASH

�

6

5

4

3

2

1

REVISION RECORD

LTR

ECO NO:

APPROVED:

DATE:

WTR0 PRX

WTR0 DRX

[24]

WTR0_PRXBB_I_P

[24]

WTR0_PRXBB_Q_P

[24]

WTR0_DRXBB_I_P

[24]

WTR0_DRXBB_Q_P

1

0

5

0

C

2

0

5

0

C

F

P

0

1

_

1

0

2

0

C

F

P

0

1

_

1

0

2

0

C

L0201_33NH_J

L0501

L0201_33NH_J

L0502

L0201_33NH_J

L0503

L0201_33NH_J

L0504

LC Filter on RxIQ for potential

De-sense Issue caused by ADC/DAC clock

3

0

5

0

C

4

0

5

0

C

F

P

0

1

_

1

0

2

0

C

F

P

0

1

_

1

0

2

0

C

RF_INTF

TX_DAC0_IM

TX_DAC0_IP

TX_DAC0_QM

TX_DAC0_QP

TX_DAC0_VREF

BE32

BG32

BG34

BE34

BD33

U1101-F

39200827

BE30

BBRX_CH0_I

BE28

BBRX_CH0_Q

BG30

BBRX_CH1_I

BG28

BBRX_CH1_Q

BE26

BBRX_CH2_I

BG26

BBRX_CH2_Q

BG24

BBRX_CH3_I

BE24

BBRX_CH3_Q

LC Filter on TxIQ for potential Tx Performance

and De-sense Issue caused by ADC/DAC clock

WTR0_TXBB_I_M

WTR0_TXBB_I_P

WTR0_TXBB_Q_M

WTR0_TXBB_Q_P

[24]

[24]

[24]

[24]

VREF_DAC_MPP_3

[11]

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

5

0

5

0

C

R0501

R0201_3.92K_F

R1010 close to the pin

AW14

WLAN_REXT

WLAN IQ

[28]

[28]

[28]

[28]

WLAN_BB_IN

WLAN_BB_IP

WLAN_BB_QN

WLAN_BB_QP

AT15

AU14

AT13

AU12

WLAN_BB_IM

WLAN_BB_IP

WLAN_BB_QM

WLAN_BB_QP

Note1

1) Unused BBRX_IQ lines can be NC

2) Unused TX_DAC0_IQ, TX_DAC_IREF and TX_DAC_VREF need to be GND

GNSS_BB_I

GNSS_BB_Q

BB33

BC34

WTR0_GPSBB_I_P

WTR0_GPSBB_Q_P

[24]

[24]

GPS IQ

D

C

B

A

D

C

B

A

�

6

5

4

3

2

1

REVISION RECORD

LTR

ECO NO:

APPROVED:

DATE:

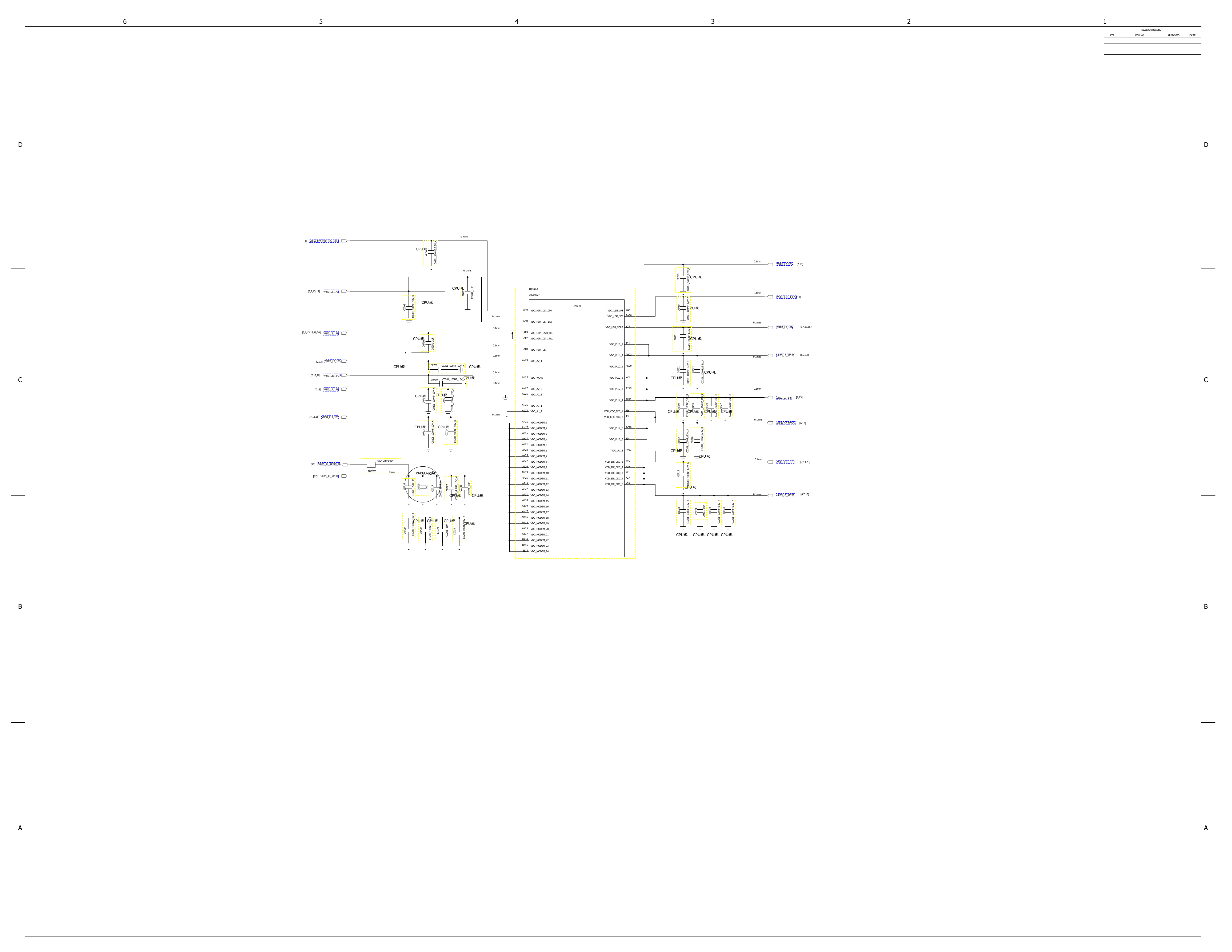

[7,13]

VREG_L3_1P225

CPU±³²¿

1.2mm

M

_

F

U

7

.

4

_

2

0

4

0

C

2

0

6

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

1

0

6

0

C

Cap depend on PDN simulation

CPU±³²¿

4

0

6

0

C

F

U

1

_

1

0

2

0

C

3

0

6

0

C

F

U

1

_

1

0

2

0

C

5

0

6

0

C

GND

F

U

1

_

1

0

2

0

C

7

1

6

0

C

6

0

6

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

8

1

6

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

U1101-G

39200827

AU30

VDD_MEM_1

J34

K9

K33

M9

P19

T11

T17

T19

U36

V13

V35

Y13

Y15

AB15

AD19

AD21

AF13

AF15

AH33

AJ32

AK29

AK31

AL30

AM33

AN34

AP9

AP17

AP21

AP25

AT9

AT21

AT33

VDD_MEM_2

VDD_MEM_3

VDD_MEM_4

VDD_MEM_5

VDD_MEM_6

VDD_MEM_7

VDD_MEM_8

VDD_MEM_9

VDD_MEM_10

VDD_MEM_11

VDD_MEM_12

VDD_MEM_13

VDD_MEM_14

VDD_MEM_15

VDD_MEM_16

VDD_MEM_17

VDD_MEM_18

VDD_MEM_19

VDD_MEM_20

VDD_MEM_21

VDD_MEM_22

VDD_MEM_23

VDD_MEM_24

VDD_MEM_25

VDD_MEM_26

VDD_MEM_27

VDD_MEM_28

VDD_MEM_29

VDD_MEM_30

VDD_MEM_31

VDD_MEM_32

VDD_MEM_33

D

C

B

A

PWR1

VDD_QFPROM_PRG

Y17

CPU±³²¿

0.1mm

VREG_L6_1P8

[3,7,13,18,19,20]

C0600

C0201_100NF_10V_K

CPU±³²¿

0.1mm£¬×ßÏß±£»¤

VDD_PX_BIAS_MPP_1

[11]

9

0

6

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

0

1

6

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

CPU±³²¿

(VDD_APC)

Cap depend on PDN simulation

0

3

6

0

C

C

N

_

2

0

4

0

C

2

3

6

0

C

F

U

1

_

1

0

2

0

C

3

3

6

0

C

CPU±³²¿

3

4

6

0

C

F

U

1

_

1

0

2

0

C

1

3

6

0

C

F

U

1

_

1

0

2

0

C

9

3

6

0

C

C

N

_

1

0

2

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

0

4

6

0

C

C

N

_

1

0

2

0

C

CPU±³²¿

M

_

F

U

2

2

_

3

0

6

0

C

6

3

6

0

C

4

3

6

0

C

M

_

F

U

2

2

_

3

0

6

0

C

5

3

6

0

C

Dedicated VIA to Main GND

M

_

F

U

2

2

_

3

0

6

0

C

7

3

6

0

C

M

_

F

U

2

2

_

3

0

6

0

C

1

4mm

2

PAD_DIFFERENT

SG0601

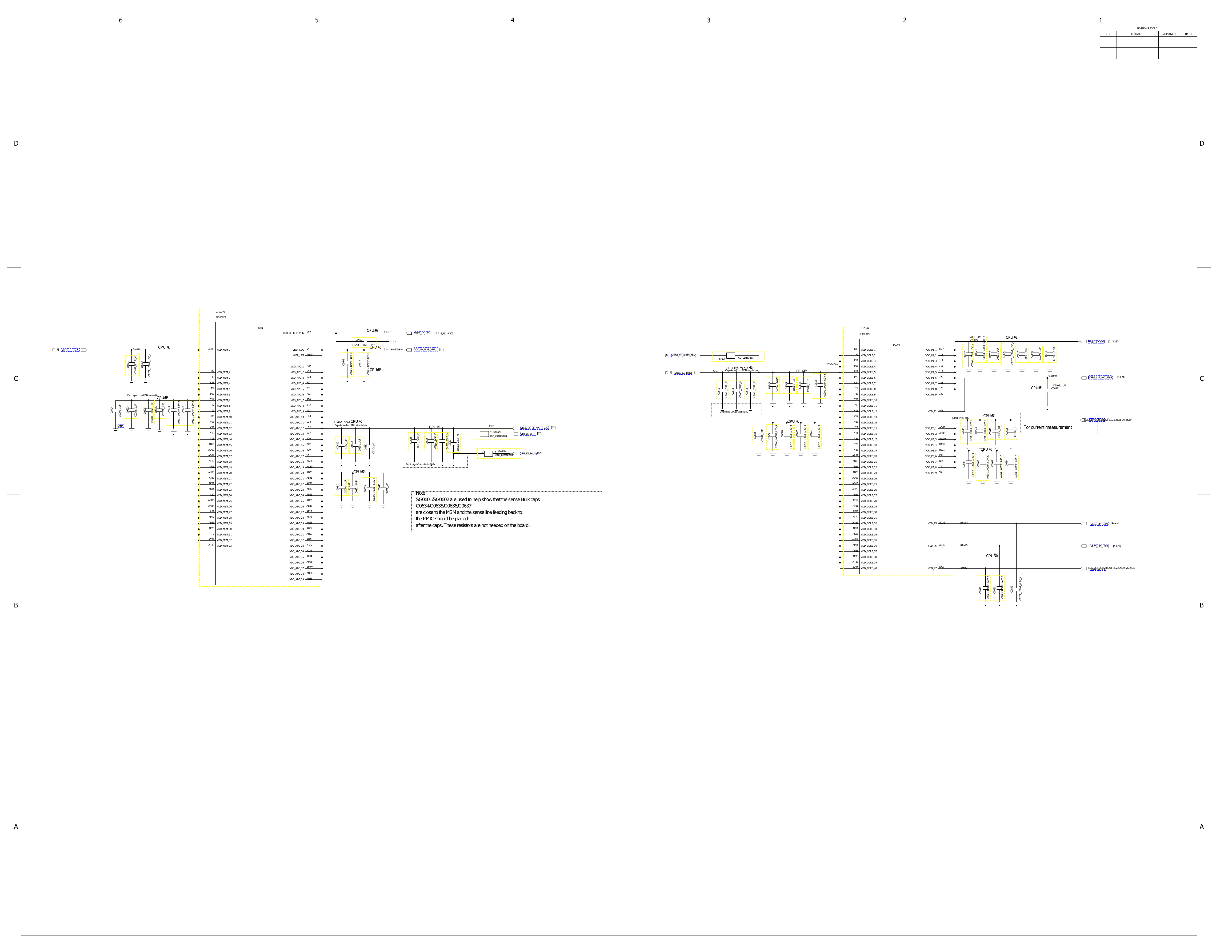

VREG_S5_S6_APC_1P225

VFB_S5_S6_P

[12]

[12]

1

SG0602

2

PAD_DIFFERENT

VFB_S5_S6_N

[12]

Note:

SG0601/SG0602 are used to help show that the sense Bulk caps

C0634/C0635/C0636/C0637

are close to the MSM and the sense line feeding back to

the PMIC should be placed

after the caps. These resistors are not needed on the board.

VREF_SDC

VREF_UIM

VDD_APC_1

VDD_APC_2

VDD_APC_3

VDD_APC_4

VDD_APC_5

VDD_APC_6

VDD_APC_7

VDD_APC_8

VDD_APC_9

VDD_APC_10

VDD_APC_11

VDD_APC_12

VDD_APC_13

VDD_APC_14

VDD_APC_15

VDD_APC_16

VDD_APC_17

VDD_APC_18

VDD_APC_19

VDD_APC_20

VDD_APC_21

VDD_APC_22

VDD_APC_23

VDD_APC_24

VDD_APC_25

VDD_APC_26

VDD_APC_27

VDD_APC_28

VDD_APC_29

VDD_APC_30

VDD_APC_31

VDD_APC_32

VDD_APC_33

VDD_APC_34

VDD_APC_35

VDD_APC_36

VDD_APC_37

VDD_APC_38

VDD_APC_39

V5

AN40

M27

N26

N28

P27

P31

P33

R26

R32

T33

U28

U30

U32

V27

V29

W30

Y29

Y31

AA26

AA30

AB25

AB31

AC26

AC32

AD25

AD31

AE28

AF27

AF29

AG28

AG32

AH27

AH31

AJ26

AJ30

AL34

AM35

AM37

AN36

AN38

[12]

VREG_S2_1P225_FB

[7,12]

VREG_S2_1P225

3mm

SG0603

PAD_DIFFERENT

CPU±³²¿/PM8937ÅÔ

Cap depend on PDN simulation

M

_

F

U

2

2

_

3

0

6

0

C

2

1

6

0

C

M

_

F

U

2

2

_

3

0

6

0

C

5

1

6

0

C

M

_

F

U

2

2

_

3

0

6

0

C

1

1

6

0

C

Dedicated VIA to Main GND

(VDD_CX)

CPU±³²¿

9

1

6

0

C

F

U

2

.

2

_

2

0

4

0

C

0

2

6

0

C

F

U

1

_

1

0

2

0

C

3

1

6

0

C

F

U

1

_

1

0

2

0

C

1

2

6

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

9

2

6

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

8

2

6

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

3

2

6

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

6

2

6

0

C

F

U

1

_

1

0

2

0

C

7

2

6

0

C

U1101-H

39200827

VDD_CORE_1

VDD_CORE_2

VDD_CORE_3

VDD_CORE_4

VDD_CORE_5

VDD_CORE_6

VDD_CORE_7

VDD_CORE_8

VDD_CORE_9

VDD_CORE_10

VDD_CORE_11

VDD_CORE_12

VDD_CORE_13

VDD_CORE_14

VDD_CORE_15

VDD_CORE_16

VDD_CORE_17

VDD_CORE_18

VDD_CORE_19

VDD_CORE_20

VDD_CORE_21

VDD_CORE_22

VDD_CORE_23

VDD_CORE_24

VDD_CORE_25

VDD_CORE_26

VDD_CORE_27

VDD_CORE_28

VDD_CORE_29

VDD_CORE_30

VDD_CORE_31

VDD_CORE_32

VDD_CORE_33

VDD_CORE_34

VDD_CORE_35

VDD_CORE_36

VDD_CORE_37

VDD_CORE_38

VDD_CORE_39

VDD_CORE_40

K35

P9

P11

P15

P17

P25

R34

T9

T23

T25

V9

V15

V17

V25

Y9

Y11

Y21

Y23

Y25

AA32

AB13

AB21

AB23

AD13

AD15

AD23

AE26

AF19

AF21

AF23

AF25

AG26

AK11

AK13

AM11

AP11

AP23

AP35

AT23

AV33

(VDD_PX1)

(LPDDR)

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

2

2

6

0

C

F

U

1

_

1

0

2

0

C

5

2

6

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

6

1

6

0

C

F

U

1

_

1

0

2

0

C

2

4

6

0

C

F

U

1

_

1

0

2

0

C

3

5

6

0

C

F

U

2

.

2

_

2

0

4

0

C

VREG_L2_1P2

[7,13,15]

0.15mm

C0402_1UF

C0638

CPU±³²¿

VREG_L12_PX2_2P95

[13,21]

CPU±³²¿

6

4

6

0

C

F

U

1

_

2

0

4

0

C

8

0

6

0

C

F

U

1

_

2

0

4

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

For current measurement

[3,6,9,13,14,15,18,20][21,22,23,25,26,28,30]

VREG_L5_1P8

7

0

6

0

C

4

2

6

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

(VDD_PX3)

(IO)

4

4

6

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

5

4

6

0

C

PWR2

VDD_P1_1

VDD_P1_2

VDD_P1_3

VDD_P1_4

VDD_P1_5

VDD_P1_6

VDD_P1_7

VDD_P1_8

VDD_P1_9

H27

J12

J14

J16

J18

J20

J22

J28

J30

VDD_P2

W6

VDD_P3_1

VDD_P3_2

VDD_P3_3

VDD_P3_4

VDD_P3_5

VDD_P3_6

VDD_P3_7

VDD_P3_8

VDD_P3_9

AD35

AH35

AW10

BA36

BB21

K11

K31

T7

V7

7

4

6

0

C

8

4

6

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

4

5

6

0

C

9

4

6

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

VDD_P5

AC36

VDD_P6

AE36

VDD_P7

N34

(UIM1)

(UIM2)

(eMMC)

CPUÕýÃæ

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

1

5

6

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

0

5

6

0

C

2

5

6

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

VREG_L14_UIM1

[13,21]

VREG_L15_UIM2

[13,21]

[3,6,9,13,14,15,18,20][21,22,23,25,26,28,30]

VREG_L5_1P8

D

C

B

A

�

6

5

4

3

2

1

REVISION RECORD

LTR

ECO NO:

APPROVED:

DATE:

D

C

B

A

[1]

VDDA_0P4_MIPI_DSI_REG

[6,7,13,15]

VREG_L2_1P2

[3,6,13,18,19,20]

VREG_L6_1P8

[7,13]

VREG_L7_1P8

[7,13,28]

VREG_L19_1P3

[7,13]

VREG_L7_1P8

[7,13,28]

VREG_L19_1P3

0.2mm

0.1mm

CPU±³²¿

3

0

7

0

C

F

U

1

_

1

0

2

0

C

CPU±³²¿

1

0

7

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

2

0

7

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

0

0

7

0

C

F

U

1

_

1

0

2

0

C

CPU±³²¿

C0708

C0201_100NF_10V_K

CPU±³²¿

CPU±³²¿

C0201_100NF_10V_K

C0710

CPU±³²¿

7

0

7

0

C

CPU±³²¿

1

1

7

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

3

1

7

0

C

CPU±³²¿

4

1

7

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

0.1mm

0.1mm

0.1mm

0.1mm

0.1mm

0.1mm

0.1mm

[12]

VREG_S1_1P225_FB

[12]

VREG_S1_1P225

PAD_DIFFERENT

SH0700

2mm

PM8937µç¸ÐÅÔ±ß

6

1

7

0

C

M

_

F

U

2

2

_

3

0

6

0

C

5

2

7

0

C

C

N

7

1

7

0

C

7

2

7

0

C

M

_

F

U

2

2

_

3

0

6

0

C

M

_

V

0

1

_

F

U

7

.

4

_

2

0

4

0

C

CPU±³²¿

6

2

7

0

C

F

U

1

_

1

0

2

0

C

CPU±³²¿

CPU±³²¿

CPU±³²¿

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

9

1

7

0

C

0

2

7

0

C

1

2

7

0

C

CPU±³²¿

F

U

1

_

1

0

2

0

C

8

1

7

0

C

CPU±³²¿

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

PWR3

VDD_USB_1P8

VDD_USB_3P3

W34

AA38

VDD_USB_CORE

Y37

VDD_PLL1_1

T21

VDD_PLL1_2

AH23

VDD_PLL2_1

AD29

VDD_PLL2_2

V21

VDD_PLL2_3

AT29

VDD_PLL2_4

AP13

VDD_CDC_SDC_1

VDD_CDC_SDC_2

J36

T3

VDD_PLL2_5

AC28

VDD_PLL2_6

J24

VDD_A1_3

AV31

VDD_EBI_CDC_1

VDD_EBI_CDC_2

VDD_EBI_CDC_3

VDD_EBI_CDC_4

VDD_EBI_CDC_5

K15

K19

K21

K27

K29

U1101-I

39200827

AH9

AM9

AK9

AP7

AB9

VDD_MIPI_DSI_0P4

VDD_MIPI_DSI_1P2

VDD_MIPI_DSI0_PLL

VDD_MIPI_DSI1_PLL

VDD_MIPI_CSI

AV29

VDD_A2_1

AR14

VDD_WLAN

AV27

AV25

AU26

AV23

AH15

AH17

AK15

AK17

AK21

AK23

AK25

AK27

AL26

AM19

AM25

AP19

AP27

AP31

AP33

AT19

AV17

AW16

AW18

AY15

AY17

BA14

BA16

BB15

VDD_A2_2

VDD_A2_3

VDD_A1_1

VDD_A1_2

VDD_MODEM_1

VDD_MODEM_2

VDD_MODEM_3

VDD_MODEM_4

VDD_MODEM_5

VDD_MODEM_6

VDD_MODEM_7

VDD_MODEM_8

VDD_MODEM_9

VDD_MODEM_10

VDD_MODEM_11

VDD_MODEM_12

VDD_MODEM_13

VDD_MODEM_14

VDD_MODEM_15

VDD_MODEM_16

VDD_MODEM_17

VDD_MODEM_18

VDD_MODEM_19

VDD_MODEM_20

VDD_MODEM_21

VDD_MODEM_22

VDD_MODEM_23

VDD_MODEM_24

9

2

7

0

C

0

3

7

0

C

1

3

7

0

C

CPU±³²¿

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

2

3

7

0

C

CPU±³²¿

4

0

7

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

5

3

7

0

C

CPU±³²¿

9

0

7

0

C

CPU±³²¿

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

0

1

_

F

N

0

0

1

_

1

0

2

0

C

7

3

7

0

C

CPU±³²¿

6

3

7

0

C

CPU±³²¿

8

3

7

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

2

1

7

0

C

CPU±³²¿

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

5

1

7

0

C

3

2

7

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

4

2

7

0

C

F

U

1

_

1

0

2

0

C

4

3

7

0

C

3

3

7

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

K

_

V

3

.

6

_

F

N

0

0

1

_

1

0

2

0

C

CPU±³²¿

CPU±³²¿

CPU±³²¿

CPU±³²¿

0.1mm

0.1mm

0.1mm

VREG_L7_1P8

[7,13]

VREG_L13_3P075

[13]

VREG_L2_1P2

[6,7,13,15]

0.1mm

VREG_L3_1P225

[6,7,13]

0.1mm

0.1mm

VREG_L7_1P8

[7,13]

VREG_S2_1P225

[6,12]

0.1mm

VREG_L19_1P3

[7,13,28]

0.1mm

VREG_L3_1P225

[6,7,13]

D

C

B

A

�

6

5

4

3

2

1

REVISION RECORD

LTR

ECO NO:

APPROVED:

DATE:

GND3

GND_204

GND_205

GND_206

GND_207

GND_208

GND_209

GND_210

GND_211

GND_212

GND_213

GND_214

GND_215

GND_216

GND_217

GND_218

GND_219

GND_220

GND_221

GND_222

GND_223

GND_224

GND_225

GND_226

GND_227

GND_228

GND_229

GND_230

GND_231

GND_232

GND_233

GND_234

GND_235

GND_236

GND_237

AW8

AW12

AW20

AW22

AW34

AY5

AY7

AY9

AY11

AY13

AY19

AY21

AY23

AY33

AY35

BA8

BA10

BA12

BA18

BA20

BA22

BB7

BB9

BB11

BB13

BB35

BC6

BC14

BD23

BF1

BF23

BG2

BG22

BG40

U1101-L

39200827

GND_154

GND_155

GND_156

GND_157

GND_158

GND_159

GND_160

GND_161

GND_162

GND_163

GND_164

GND_165

GND_166

GND_167

GND_168

GND_169

GND_170

GND_171

GND_172

GND_173

GND_174

GND_175

GND_176

GND_177

GND_178

GND_179

GND_180

GND_181

GND_182

GND_183

GND_184

GND_185

GND_186

GND_187

GND_188

GND_189

GND_190

GND_191

GND_192

GND_193

GND_194

GND_195

GND_196

GND_197

GND_198

GND_199

GND_200

GND_201

GND_202

GND_203

AB5

AB17

AB19

AB33

AC6

AC8

AD5

AD17

AD33

AE30

AE32

AF17

AF31

AF33

AG30

AH5

AH11

AH13

AH19

AH25

AH29

AJ28

AJ34

AJ36

AK19

AK33

AK35

AK37

AL28

AL36

AL38

AM15

AM17

AM21

AM23

AM27

AM29

AP15

AT7

AT25

AT35

AU6

AU32

AV5

AV7

AV9

AV11

AV19

AV21

AV35

GND1

U1101-J

39200827

AK7

AN8

AH7

AK5

AM5

AM7

AP5

GND_2

GND_3

GND_4

GND_5

GND_6

GND_7

GND_8

AW30

AY29

BB31

BC32

BD31

BF31

BF33

BF35

GND_9

GND_10

GND_11

GND_12

GND_13

GND_14

GND_15

GND_16

AV13

GND_17

AW28

AY27

BC28

BC30

BD27

BD29

BF27

BF29

AY25

BC24

BC26

BD25

BF25

GND_18

GND_19

GND_20

GND_21

GND_22

GND_23

GND_24

GND_25

GND_26

GND_27

GND_28

GND_29

GND_30

AT27

GND_31

GND_32

GND_33

GND_34

GND_35

AA34

AB37

AD27

AB27

GND_36

GND_37

U20

V19

GND_38

GND_39

GND_40

GND_41

AJ22

AH21

AC30

AB29

GND_42

GND_43

V23

U22

GND_44

GND_45

GND_46

GND_47

AR28

AP29

AN14

AM13

GND_48

GND_49

K23

H23

GND_50

M23

GND_51

GND_52

GND_53

AW32

BD35

AT31

GND2

U1101-K

39200827

GND_54

GND_55

GND_56

GND_57

GND_58

GND_59

GND_60

GND_61

GND_62

GND_63

GND_64

GND_65

GND_66

GND_67

GND_68

GND_69

GND_70

GND_71

GND_72

GND_73

GND_74

GND_75

GND_76

GND_77

GND_78

GND_79

GND_80

GND_81

GND_82

GND_83

GND_84

GND_85

GND_86

GND_87

GND_88

GND_89

GND_90

GND_91

GND_92

GND_93

GND_94

GND_95

GND_96

GND_97

GND_98

GND_99

GND_100

GND_101

GND_102

GND_103

A2

A40

B1

B7

B9

B11

B13

B15

B17

B19

B21

B23

B25

B27

B29

B31

B33

B35

B37

C6

C14

C20

C24

C32

D7

D9

D11

D13

D17

D21

D23

D27

D29

D33

D35

D37

E8

E18

E22

E24

E26

E28

E30

E34

E36

F7

F13

F23

G2

G6

GND_104

GND_105

GND_106

GND_107

GND_108

GND_109

GND_110

GND_111

GND_112

GND_113

GND_114

GND_115

GND_116

GND_117

GND_118

GND_119

GND_120

GND_121

GND_122

GND_123

GND_124

GND_125

GND_126

GND_127

GND_128

GND_129

GND_130

GND_131

GND_132

GND_133

GND_134

GND_135

GND_136

GND_137

GND_138

GND_139

GND_140

GND_141

GND_142

GND_143

GND_144

GND_145

GND_146

GND_147

GND_148

GND_149

GND_150

GND_151

GND_152

GND_153

G8

G12

G28

G36

H11

H13

H19

H29

H31

H35

J8

J10

J26

J32

K5

K7

K25

L36

M7

M29

M33

N30

N32

P13

P21

P23

P29

R28

R30

T13

T15

T27

T29

T31

T35

U26

U34

V31

V33

W20

W22

W26

W28

W32

Y7

Y19

Y27

AA4

AA6

AA28

D

C

B

A

D

C

B

A

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc