Cover

Title Page

Copyright Page

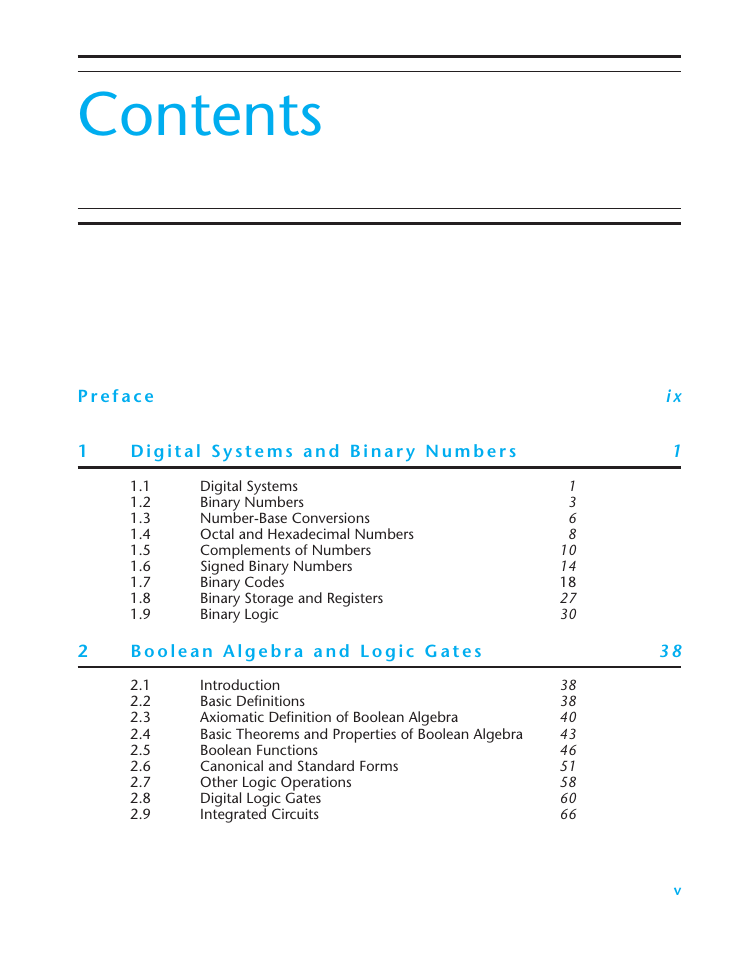

Contents

Preface

1 Digital Systems and Binary Numbers

1.1 Digital Systems

1.2 Binary Numbers

1.3 Number-Base Conversions

1.4 Octal and Hexadecimal Numbers

1.5 Complements of Numbers

1.6 Signed Binary Numbers

1.7 Binary Codes

1.8 Binary Storage and Registers

1.9 Binary Logic

2 Boolean Algebra and Logic Gates

2.1 Introduction

2.2 Basic Definitions

2.3 Axiomatic Definition of Boolean Algebra

2.4 Basic Theorems and Properties of Boolean Algebra

2.5 Boolean Functions

2.6 Canonical and Standard Forms

2.7 Other Logic Operations

2.8 Digital Logic Gates

2.9 Integrated Circuits

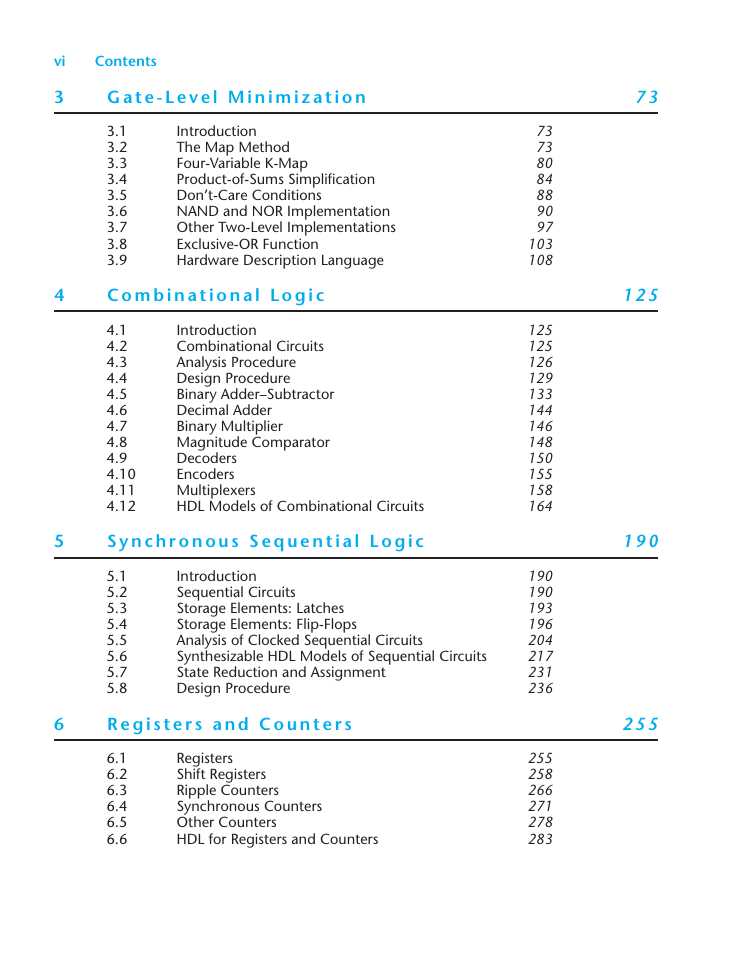

3 Gate-Level Minimization

3.1 Introduction

3.2 The Map Method

3.3 Four-Variable K-Map

3.4 Product-of-Sums Simplification

3.5 Don't-Care Conditions

3.6 NAND and NOR Implementation

3.7 Other Two-Level Implementations

3.8 Exclusive-OR Function

3.9 Hardware Description Language

4 Combinational Logic

4.1 Introduction

4.2 Combinational Circuits

4.3 Analysis Procedure

4.4 Design Procedure

4.5 Binary Adder–Subtractor

4.6 Decimal Adder

4.7 Binary Multiplier

4.8 Magnitude Comparator

4.9 Decoders

4.10 Encoders

4.11 Multiplexers

4.12 HDL Models of Combinational Circuits

5 Synchronous Sequential Logic

5.1 Introduction

5.2 Sequential Circuits

5.3 Storage Elements: Latches

5.4 Storage Elements: Flip-Flops

5.5 Analysis of Clocked Sequential Circuits

5.6 Synthesizable HDL Models of Sequential Circuits

5.7 State Reduction and Assignment

5.8 Design Procedure

6 Registers and Counters

6.1 Registers

6.2 Shift Registers

6.3 Ripple Counters

6.4 Synchronous Counters

6.5 Other Counters

6.6 HDL for Registers and Counters

7 Memory and Programmable Logic

7.1 Introduction

7.2 Random-Access Memory

7.3 Memory Decoding

7.4 Error Detection and Correction

7.5 Read-Only Memory

7.6 Programmable Logic Array

7.7 Programmable Array Logic

7.8 Sequential Programmable Devices

8 Design at the Register Transfer Level

8.1 Introduction

8.2 Register Transfer Level Notation

8.3 Register Transfer Level in HDL

8.4 Algorithmic State Machines (ASMs)

8.5 Design Example (ASMD Chart)

8.6 HDL Description of Design Example

8.7 Sequential Binary Multiplier

8.8 Control Logic

8.9 HDL Description of Binary Multiplier

8.10 Design with Multiplexers

8.11 Race-Free Design (Software Race Conditions)

8.12 Latch-Free Design (Why Waste Silicon?)

8.13 Other Language Features

9 Laboratory Experiments with Standard ICs and FPGAs

9.1 Introduction to Experiments

9.2 Experiment 1: Binary and Decimal Numbers

9.3 Experiment 2: Digital Logic Gates

9.4 Experiment 3: Simplification of Boolean Functions

9.5 Experiment 4: Combinational Circuits

9.6 Experiment 5: Code Converters

9.7 Experiment 6: Design with Multiplexers

9.8 Experiment 7: Adders and Subtractors

9.9 Experiment 8: Flip-Flops

9.10 Experiment 9: Sequential Circuits

9.11 Experiment 10: Counters

9.12 Experiment 11: Shift Registers

9.13 Experiment 12: Serial Addition

9.14 Experiment 13: Memory Unit

9.15 Experiment 14: Lamp Handball

9.16 Experiment 15: Clock-Pulse Generator

9.17 Experiment 16: Parallel Adder and Accumulator

9.18 Experiment 17: Binary Multiplier

9.19 Verilog HDL Simulation Experiments and Rapid Prototyping with FPGAs

10 Standard Graphic Symbols

10.1 Rectangular-Shape Symbols

10.2 Qualifying Symbols

10.3 Dependency Notation

10.4 Symbols for Combinational Elements

10.5 Symbols for Flip-Flops

10.6 Symbols for Registers

10.7 Symbols for Counters

10.8 Symbol for RAM

Appendix

Answers to Selected Problems

Index

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

R

S

T

U

V

W

X

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc