课程设计任务书

学生姓名:

指导教师:

专业班级:

工作单位:

题 目: 设计一简单信号发生器

初始条件:

1.选用 8088 CPU 最小工作模式;

2.选择 DAC0832 芯片完成模拟信号输出,确定芯片地址范围;

3.输出三角波的电压范围为 0~+2.5V,能够实现频率调节功能。

要求完成的主要任务: (包括课程设计工作量及其技术要求,以及说明书撰写等具体要

求)

1.查阅参考资料,自学相关可编程接口芯片的内部结构、工作方式和初始化编程

过程;

2.根据设计系统的具体功能和性能参数,明确设计目标;

3.微机基本系统及其扩展接口电路设计,绘制微机系统硬件原理图;

4.编制扩展接口电路工作的汇编源程序,绘制汇编源程序流程图,包括初始化和

监控工作程序;

5.撰写设计说明书(包括参考资料目录,字数不少于 5000 字)

时间安排:

序号

内

容

所用时间(天)

1

2

3

4

5

查阅资料,学习相关芯片知识

系统及扩展电路硬件设计

初始化程序和应用程序设计

相关硬件电路和程序调试

编写课程设计说明书和答辩

合计

1.5

3

2

2

1.5

10

指导教师签名:

2010 年 12 月 12 日

系主任(或责任教师)签名:

年

月

日

�

(一)

概述

设计内容及要求

本设计综合应用 8088CPU、D/A 转换器、定时器/计数器电路,中断技术:通过 PC

机定时,产生三角波模拟信号输出,信号频率可通过 PC 机键盘调节。输出电压范围在

0~2.5V 之间。

课程设计要求

设计要求画出电路原理图,说明工作原理,编写程序及程序流程图。

设计目的

通过该课程的学习使学生对微机系统有一个全面的了解、掌握常规芯片的使用方

法、掌握简单微型计算机应用系统软硬的设计方法,进一步锻炼同学们在微型计算机应

用方面的实际工作能力。

本设计主要能够完成对制定波形的形成,可以通过输入来改变频率。此信号发生器

可以很好的运用于有需要的场合。

(二)

系统总体设计

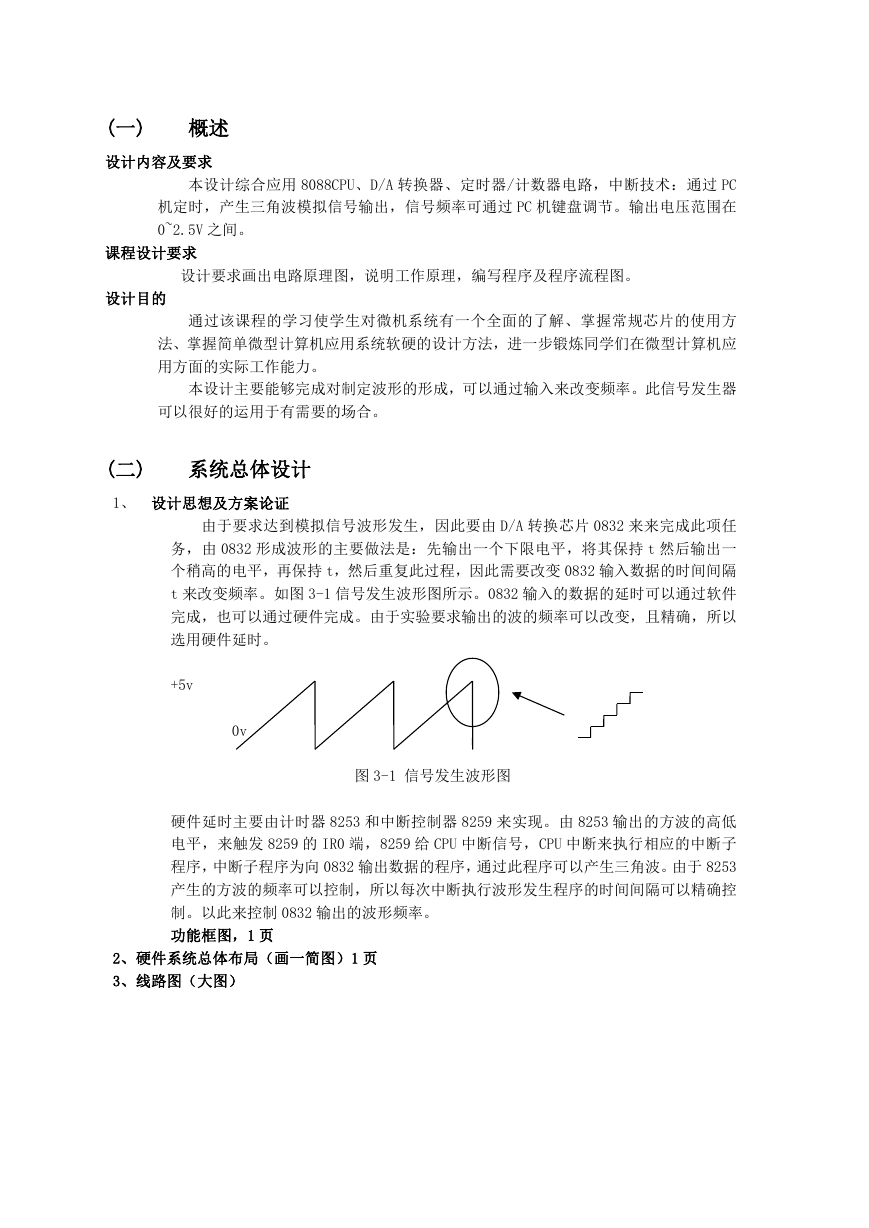

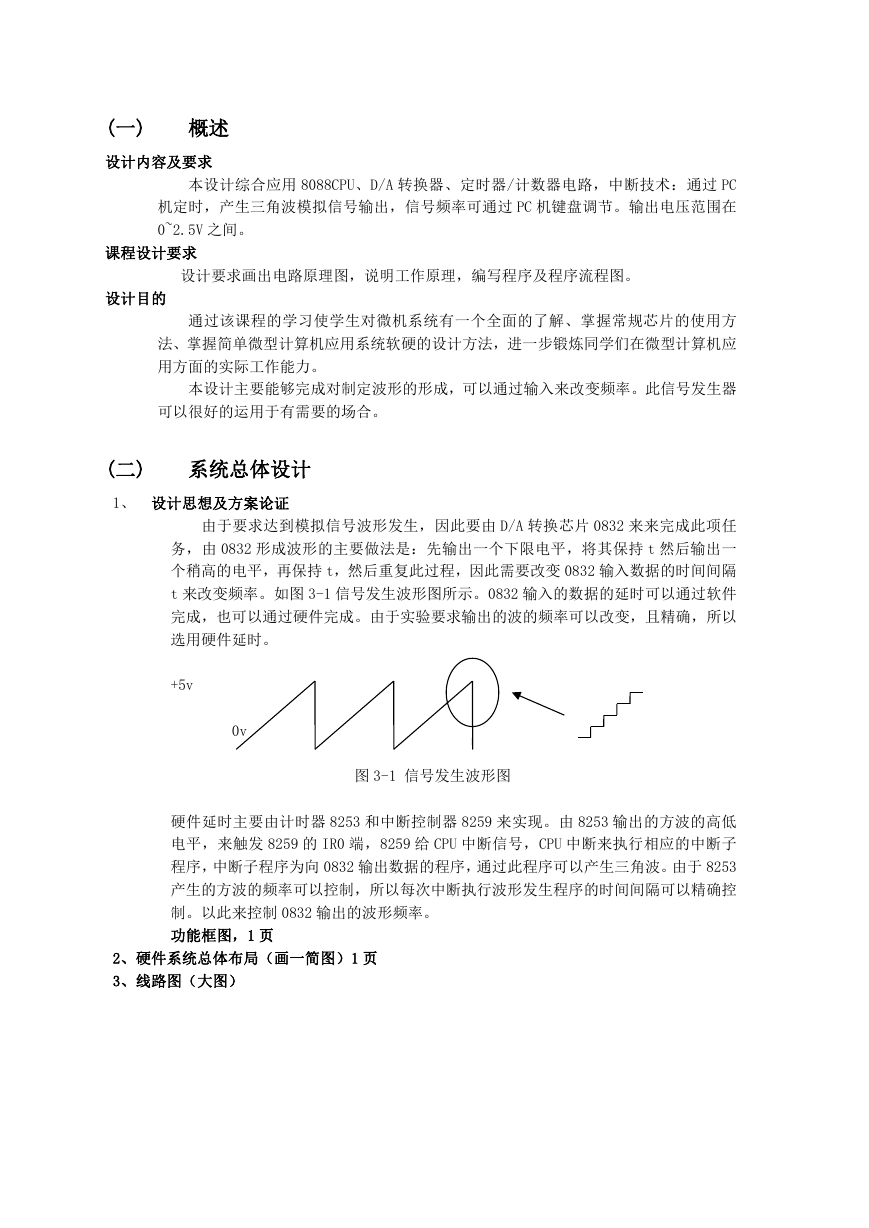

1、 设计思想及方案论证

由于要求达到模拟信号波形发生,因此要由 D/A 转换芯片 0832 来来完成此项任

务,由 0832 形成波形的主要做法是:先输出一个下限电平,将其保持 t 然后输出一

个稍高的电平,再保持 t,然后重复此过程,因此需要改变 0832 输入数据的时间间隔

t 来改变频率。如图 3-1 信号发生波形图所示。0832 输入的数据的延时可以通过软件

完成,也可以通过硬件完成。由于实验要求输出的波的频率可以改变,且精确,所以

选用硬件延时。

+5v

0v

图 3-1 信号发生波形图

硬件延时主要由计时器 8253 和中断控制器 8259 来实现。由 8253 输出的方波的高低

电平,来触发 8259 的 IR0 端,8259 给 CPU 中断信号,CPU 中断来执行相应的中断子

程序,中断子程序为向 0832 输出数据的程序,通过此程序可以产生三角波。由于 8253

产生的方波的频率可以控制,所以每次中断执行波形发生程序的时间间隔可以精确控

制。以此来控制 0832 输出的波形频率。

功能框图,1 页

2、硬件系统总体布局(画一简图)1 页

3、线路图(大图)

�

1

2

VCC

13

13

14

14

1

1

15

15

17

17

16

16

Y?

1.000MHZ

11

11

U?

U1

F/C

F/C

EFI

EFI

CSYNC

CSYNC

ASYNC

ASYNC

X1

X1

X2

X2

RES

RES

8284

8284

READY

READY

CLK

CLK

PCLK

PCLK

OSC

OSC

RESET

RESET

RDY1

RDY1

RDY2

RDY2

AEN1

AEN1

AEN2

AEN2

5

5

8

8

2

2

12

12

10

10

4

4

6

6

3

3

7

7

3

11

9

8

7

6

5

4

3

2

1

T

OE

A7

A6

A5

A4

A3

A2

A1

A0

U2

B7

B6

B5

B4

B3

B2

B1

B0

8286

12

13

14

15

16

17

18

19

D0

D1

D2

D3

D4

D5

D6

D7

11

12

13

15

16

17

18

19

10

9

8

7

6

5

4

3

25

24

21

23

2

20

22

27

1

U9

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

CE

OE

PGM

VPP

2764

1

2

3

4

5

6

7

8

9

11

U3

DI0

DI1

DI2

DI3

DI4

DI5

DI6

DI7

U4

OE

STB

8282

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

NMI

INTR

RD

WR/LOC

HOLD

HLDA

MN/MX

SSO

TEST

READY

8088

U8

D0

D1

D2

D3

D4

D5

D6

D7

CS

RD

WR

A0

A1

8253

16

15

14

13

12

11

10

9

17

18

32

29

31

30

33

34

23

22

8

7

6

5

4

3

2

1

21

22

23

19

20

DO0

DO1

DO2

DO3

DO4

DO5

DO6

DO7

19

18

17

16

15

14

13

12

A8

A9

A10

A11

A12

A13

A14

A15

A16/S3

A17/S4

A18/S5

A19/S6

S0/DEN

S1DT/R

S2IO/M

ALEQS0

INAQS1

CLK

RESET

OUT0

GATE0

CLK0

OUT1

GATE1

CLK1

OUT2

GATE2

CLK2

8

7

6

5

4

3

2

39

38

37

36

35

26

27

28

25

24

19

21

10

11

9

13

14

15

17

16

18

D

C

B

A

1

2

3

4

4、芯片选择

4

5

6

1

5

1

4

1

3

1

2

1

1

1

0

9

7

U5

74LS138

Y

0

Y

1

Y

2

Y

3

Y

4

Y

5

Y

6

Y

7

A

B

C

E

1

E

2

E

3

1

2

3

4

5

6

D

C

B

A

U6

DAC0832

Xfer

CS

msbDI7

DI6

DI5

DI4

DI3

DI2

DI1

lsbDI0

17

1

13

14

15

16

4

5

6

7

WR1

WR2

ILE

Vref

Rfb

Iout2

Iout1

2

18

19

8

9

12

11

V

c

c

2

0

5v

U?A

LM324A

1

参考电压

3

2

4

1

1

11

10

9

8

7

6

5

4

17

26

1

3

2

27

U7

D0

D1

D2

D3

D4

D5

D6

D7

INT

INTA

CS

RD

WR

A0

8259

Title

Size

B

Date:

File:

5

IR0

IR1

IR2

IR3

IR4

IR5

IR6

IR7

SP/EN

CAS0

CAS1

CAS2

18

19

20

21

22

23

24

25

16

12

13

15

Number

Revision

16-Dec-2005

E:\王少游\MyDesign1.ddb

Sheet of

Drawn By:

6

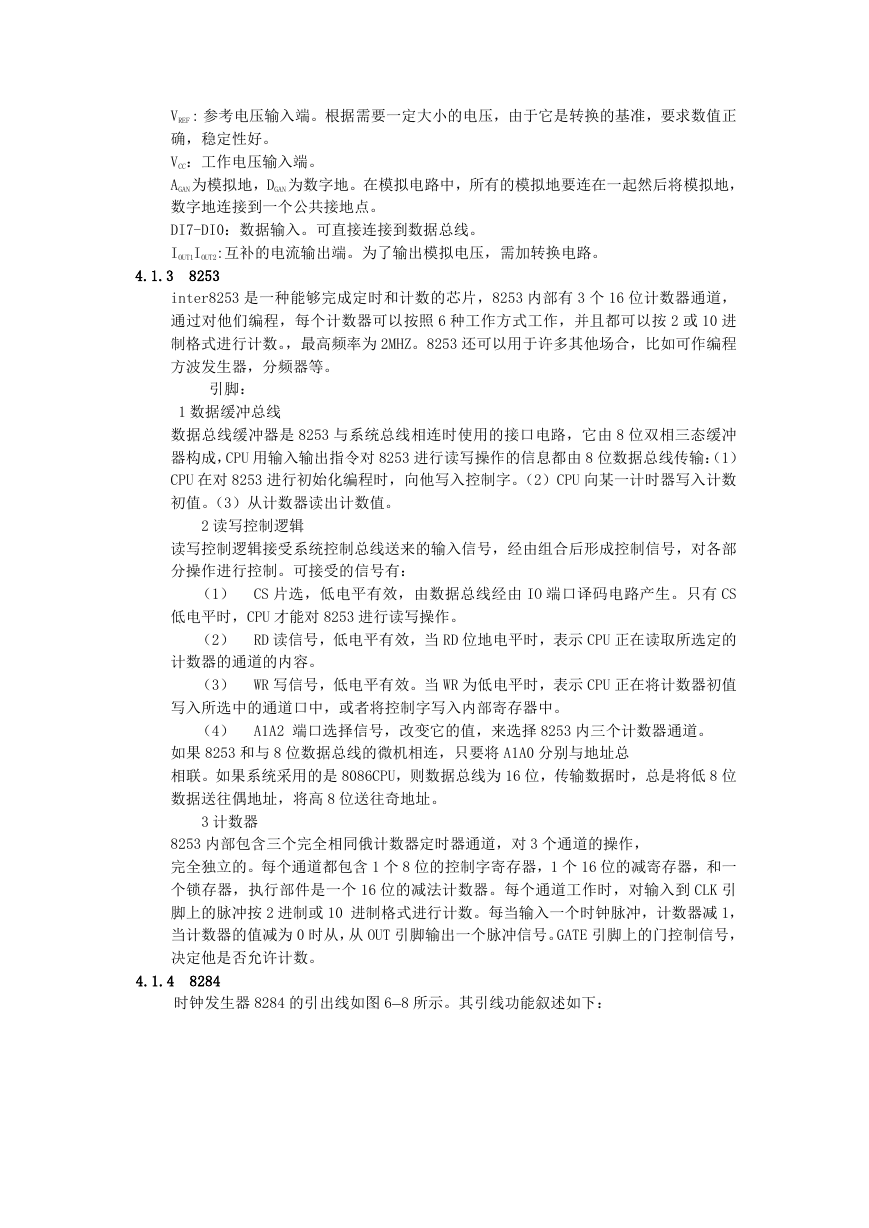

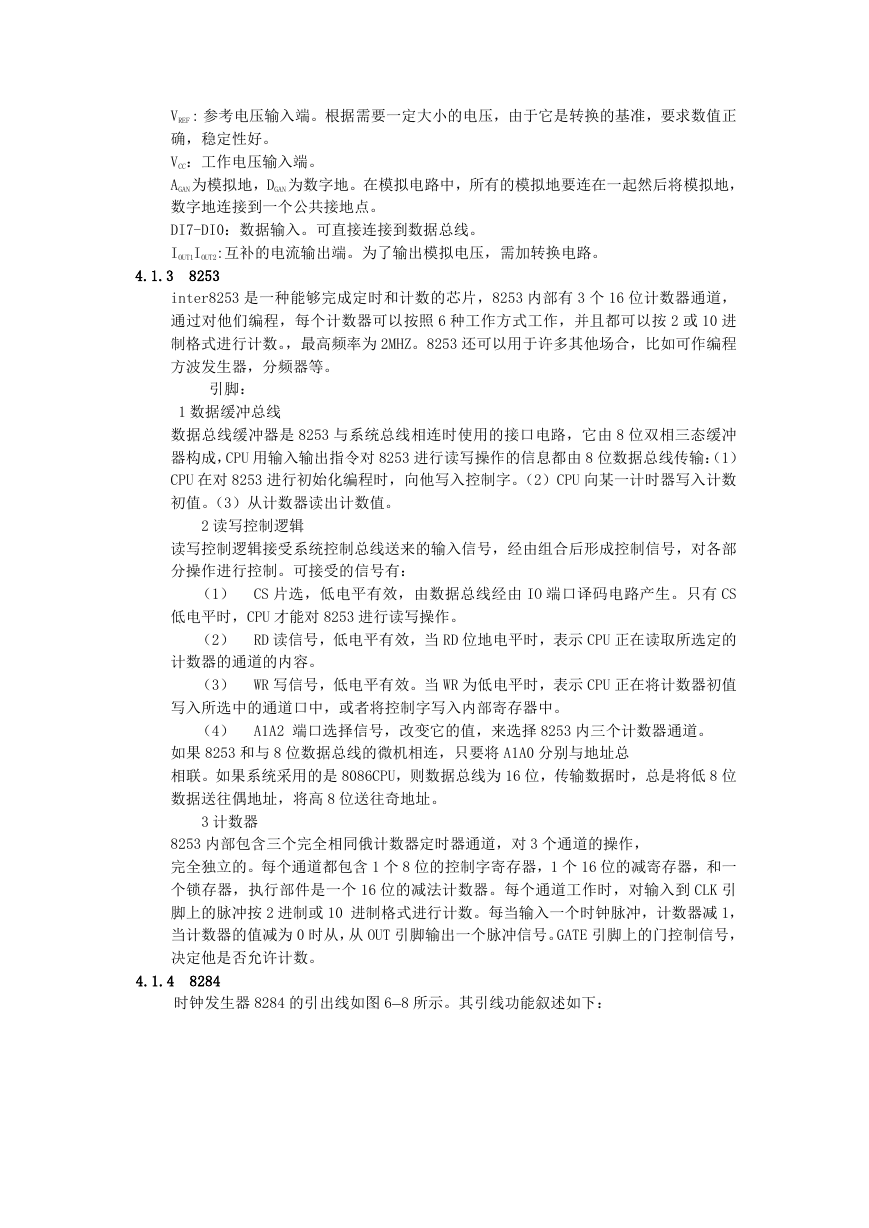

根据需要,选择了 8088CPU,时钟发生器 8284*1,总线控制器 8286*1,总线地

址锁存器 8282*3,RAM6264*1,ROM2764*1,计时器 8253*1,中断控制器 8259*1,D/A

转换器 0832*1,地址译码器 74L138*2

4.1.1 可编程中断控制器 8259a

8259a 是 8086/8088 系列的可编程中断控制器,8259a 为 28 个引脚的双列直插芯片。

它的主要功能是:

(1)据 8 级优先级控制,通过联级可以扩展到 64 级优先控制。

(2)每一级中断可由程序单独屏蔽或允许。

(3)可提供中断类型号传送给 CPU。

(4)可以通过编程选择多种不同工作方式。

引脚功能:

D7-D0:双向数据线,三态,与数据总线相连。

IR7-IR0:外设的中断请求信号输入端,输入,中断请求:可以是电平触发,或者边缘

触发。

RD:读命令信号,输入,低电平有效,用来控制数据由 8259A 读

WR:写命令信号,输入,地点平有效,用来控制写到 8259

CS:片选信号,输入,通过译码器与地址总线相连

INT:向 CPU 发出中断请求信号,输出,与 CPU 的 INTR 相连

INTA:CPU 给 8259 的中断响应信号,输入。

4.1.2DAC0832:

NSC 公司生产的 DAC0832 ,是一种内部带有数据输入寄存器的 8 位 D/A 转化器,采用

CMOS 工艺制成,芯片内部 R-2R 梯形电阻网络,用于对参考电压产生的电压进行分流,

完成模数转换,转换结果以一组差动电流 IOUT1IOUT2 输出。

0832 具有 8 位分辨率,如果输出电压范围在 0~5V 间的话,当输入数字量为 0 时,

输出电压为 0V;输入数字量为 255(0FFH)时,输出电压为 5V。

各引脚的功能分述如下:

�

VREF : 参考电压输入端。根据需要一定大小的电压,由于它是转换的基准,要求数值正

确,稳定性好。

VCC:工作电压输入端。

AGAN 为模拟地,DGAN 为数字地。在模拟电路中,所有的模拟地要连在一起然后将模拟地,

数字地连接到一个公共接地点。

DI7-DI0:数据输入。可直接连接到数据总线。

IOUT1IOUT2:互补的电流输出端。为了输出模拟电压,需加转换电路。

4.1.3

8253

inter8253 是一种能够完成定时和计数的芯片,8253 内部有 3 个 16 位计数器通道,

通过对他们编程,每个计数器可以按照 6 种工作方式工作,并且都可以按 2 或 10 进

制格式进行计数。,最高频率为 2MHZ。8253 还可以用于许多其他场合,比如可作编程

方波发生器,分频器等。

引脚:

1 数据缓冲总线

数据总线缓冲器是 8253 与系统总线相连时使用的接口电路,它由 8 位双相三态缓冲

器构成,CPU 用输入输出指令对 8253 进行读写操作的信息都由 8 位数据总线传输:(1)

CPU 在对 8253 进行初始化编程时,向他写入控制字。(2)CPU 向某一计时器写入计数

初值。(3)从计数器读出计数值。

2 读写控制逻辑

读写控制逻辑接受系统控制总线送来的输入信号,经由组合后形成控制信号,对各部

分操作进行控制。可接受的信号有:

(1) CS 片选,低电平有效,由数据总线经由 IO 端口译码电路产生。只有 CS

低电平时,CPU 才能对 8253 进行读写操作。

(2) RD 读信号,低电平有效,当 RD 位地电平时,表示 CPU 正在读取所选定的

计数器的通道的内容。

(3) WR 写信号,低电平有效。当 WR 为低电平时,表示 CPU 正在将计数器初值

写入所选中的通道口中,或者将控制字写入内部寄存器中。

(4) A1A2 端口选择信号,改变它的值,来选择 8253 内三个计数器通道。

如果 8253 和与 8 位数据总线的微机相连,只要将 A1A0 分别与地址总

相联。如果系统采用的是 8086CPU,则数据总线为 16 位,传输数据时,总是将低 8 位

数据送往偶地址,将高 8 位送往奇地址。

3 计数器

8253 内部包含三个完全相同俄计数器定时器通道,对 3 个通道的操作,

完全独立的。每个通道都包含 1 个 8 位的控制字寄存器,1 个 16 位的减寄存器,和一

个锁存器,执行部件是一个 16 位的减法计数器。每个通道工作时,对输入到 CLK 引

脚上的脉冲按 2 进制或 10 进制格式进行计数。每当输入一个时钟脉冲,计数器减 1,

当计数器的值减为 0 时从,从 OUT 引脚输出一个脉冲信号。GATE 引脚上的门控制信号,

决定他是否允许计数。

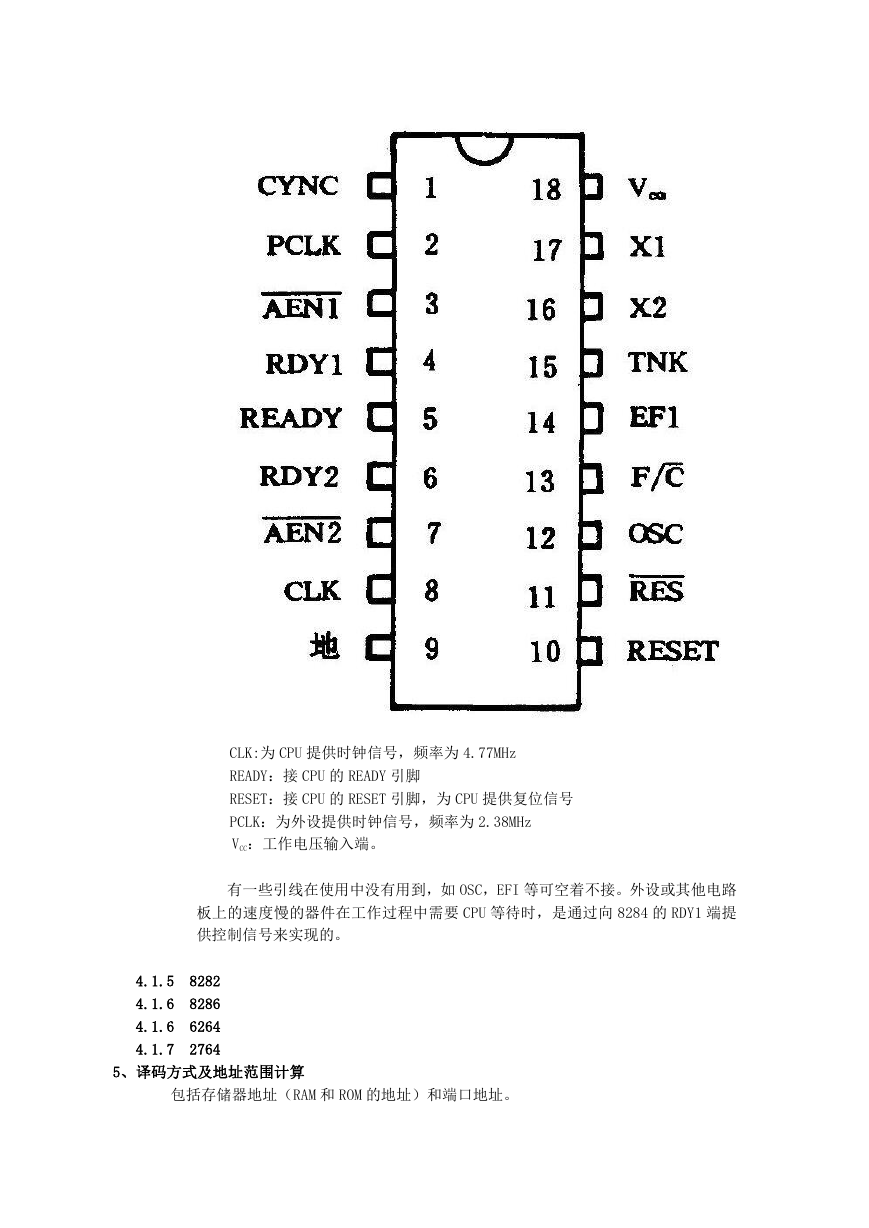

4.1.4

8284

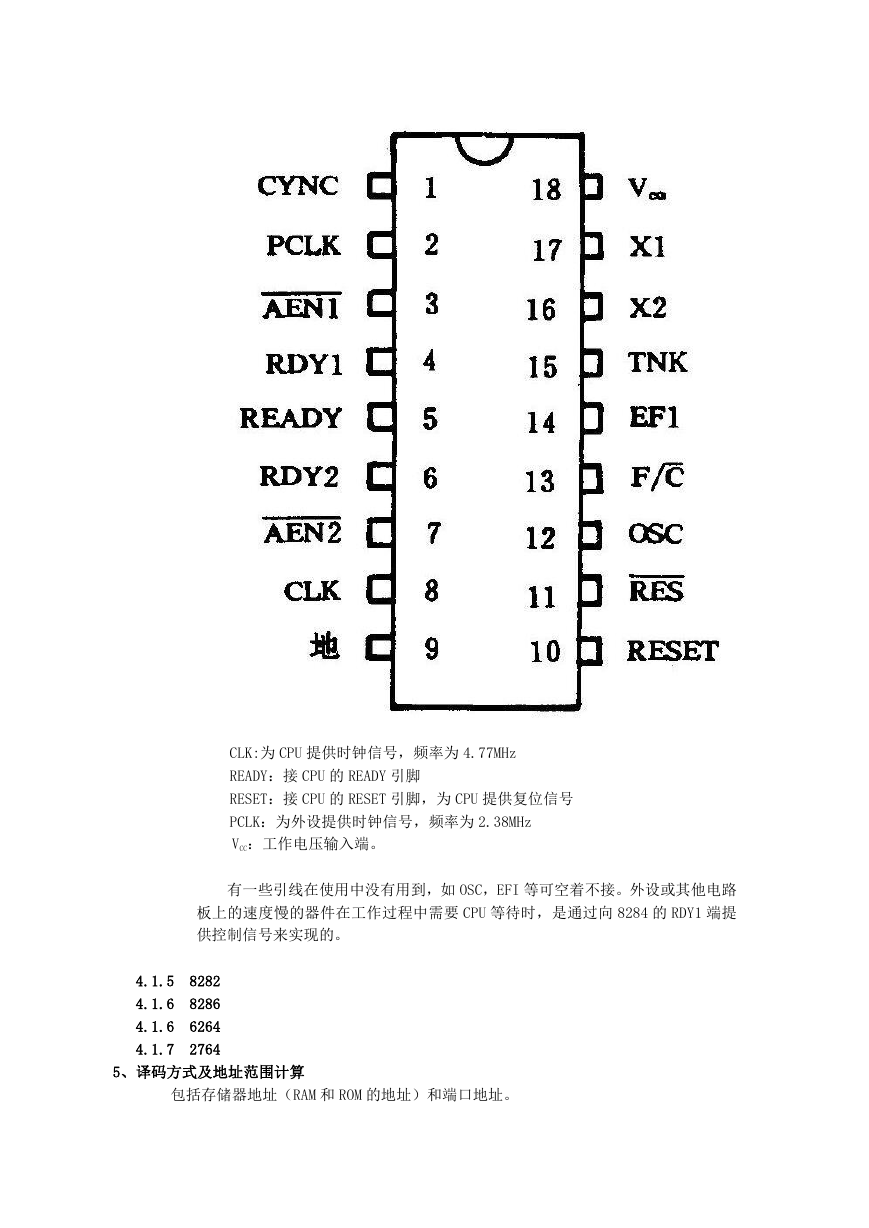

时钟发生器 8284 的引出线如图 6—8 所示。其引线功能叙述如下:

�

CLK:为 CPU 提供时钟信号,频率为 4.77MHz

READY:接 CPU 的 READY 引脚

RESET:接 CPU 的 RESET 引脚,为 CPU 提供复位信号

PCLK:为外设提供时钟信号,频率为 2.38MHz

VCC:工作电压输入端。

有一些引线在使用中没有用到,如 OSC,EFI 等可空着不接。外设或其他电路

板上的速度慢的器件在工作过程中需要 CPU 等待时,是通过向 8284 的 RDY1 端提

供控制信号来实现的。

4.1.5

4.1.6

4.1.6

4.1.7

8282

8286

6264

2764

5、译码方式及地址范围计算

包括存储器地址(RAM 和 ROM 的地址)和端口地址。

�

端口地址有 8259(两个地址),8253(四个地址),0832(一个地址?)均需译码器译

码分配 CS。

(三)

接口扩展电路设计

接口电路的设计、原理和工作方式

使用 8253 产生定时中断,故 8253 使用方式 3 以产生方波信号,以方波信号的上升沿触发中断

达到定时目的。8253 的计数初值根据所需输出地三角波频率计算得到。8253 的输入时钟频率来

自 8284 芯片的 PCLK 引脚,频率为 2.38MHz。

8259 芯片在此次应用中只负责产生定时中,没有设置从片及,所以使用一般嵌套,根据 8253

的输入波形,选择上升沿触发方式。

列写端口地址表

8259 的工作方式及初始化程序

;初始化 8259,设置为单片,上升沿触发,完全

;非自动 EOI 方式,03H

MOV DX,8259AD0

MOV AL,00010011B

OUT DX,AL

MOV DX,8259AD1

MOV AL,10000000B…………..ICW2,10H,中断向量码 IR0——10H

OUT DX,AL

MOV AL,00000001B…………..ICW4,01H,

OUT DX,AL

8253 的工作方式及初始化程序

;通道 1 方式字,方式 3,二进制记数

方波发生器,用以产生中断

OUT DX,AL MOV DX,316H……………初始化 8253,计数器地址,写计数器 1

MOV AL,01110110B

OUT DX,AL

MOV DX,312H……………………写计数值

POP CX……………………………..计数值弹到 CX

MOV AL,CL ………………………..写低八位

OUT DX,AL

MOV AL,CH…………………………写高八位

OUT DX,AL

0832 的工作方式及初始化程序

工作方式单缓冲模式,没有初始化程序

(四)

系统程序设计

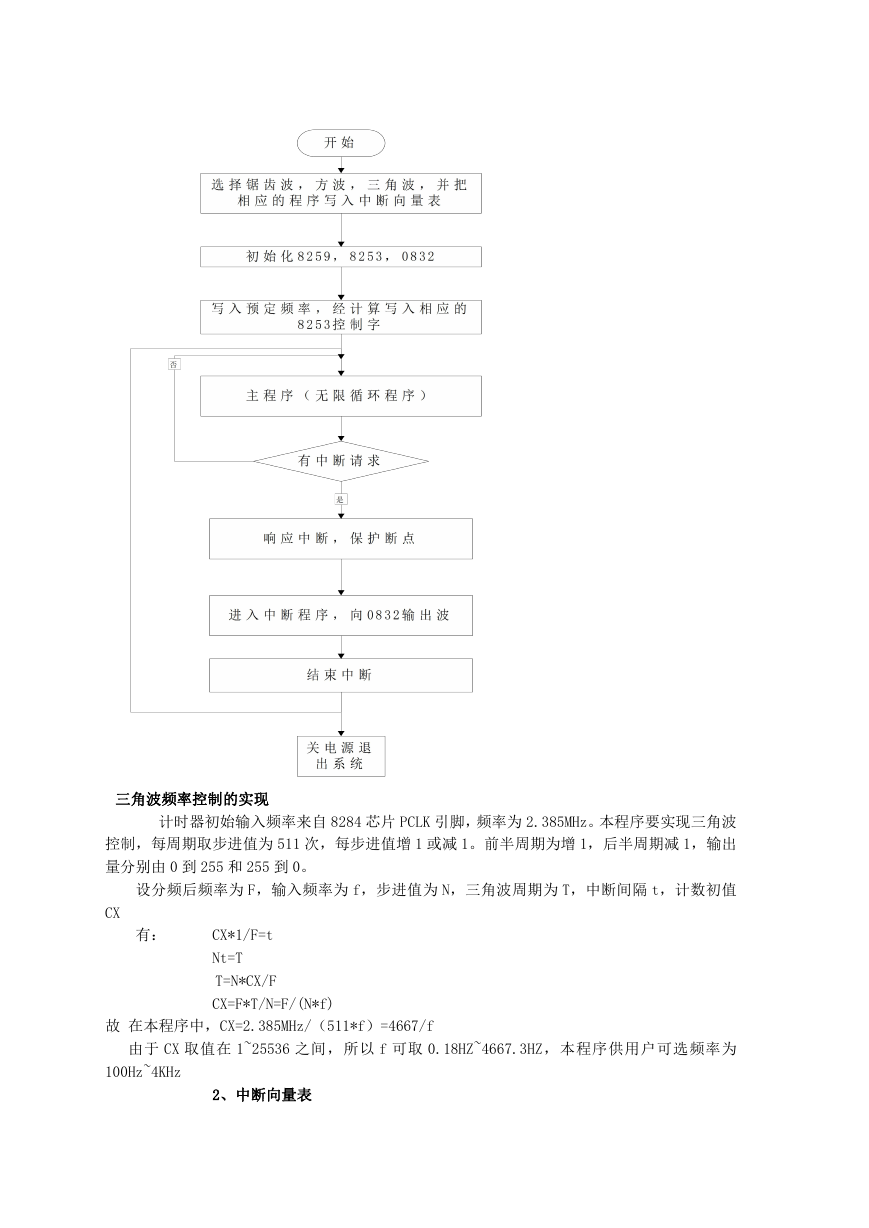

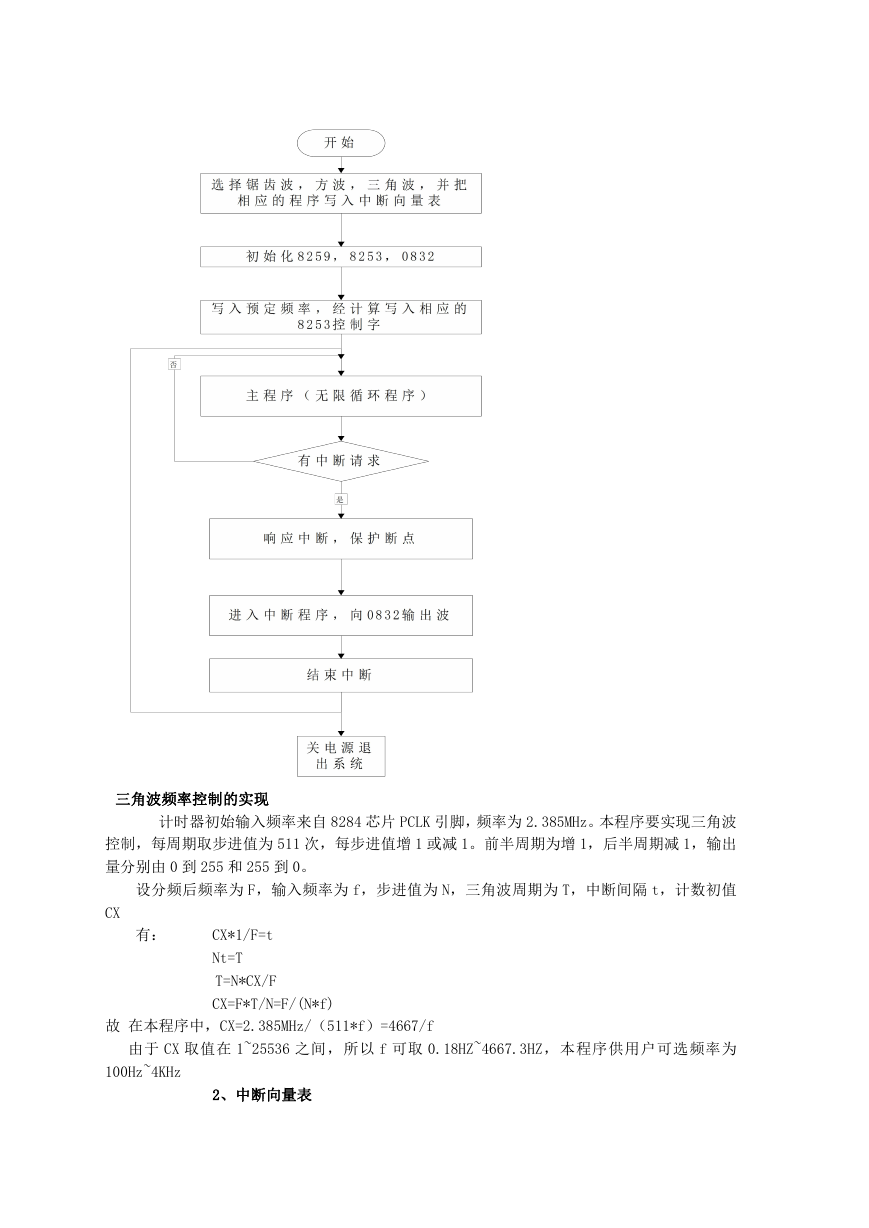

1 流程图主要进行系统初始化和外围接口芯片初始化,及开中断,等待中断产生,

其流程图所示。

�

三角波频率控制的实现

计时器初始输入频率来自 8284 芯片 PCLK 引脚,频率为 2.385MHz。本程序要实现三角波

控制,每周期取步进值为 511 次,每步进值增 1 或减 1。前半周期为增 1,后半周期减 1,输出

量分别由 0 到 255 和 255 到 0。

设分频后频率为 F,输入频率为 f,步进值为 N,三角波周期为 T,中断间隔 t,计数初值

CX

有:

CX*1/F=t

Nt=T

T=N*CX/F

CX=F*T/N=F/(N*f)

故 在本程序中,CX=2.385MHz/(511*f)=4667/f

由于 CX 取值在 1~25536 之间,所以 f 可取 0.18HZ~4667.3HZ,本程序供用户可选频率为

100Hz~4KHz

2、中断向量表

�

中断向量地址指

针

8259A 引脚

中断类型号

优先级

中断源

00020H

00024H

主片 IR0

主片 IR1

08H

09H

0

1

定时器

键盘

3、程序清单

DATA SEGMENT

定义数据段

MESS DB'输入发生频率(100Hz~4000Hz)',0DH,0AH,'$' …………………….提示信息

CUNCHU DB ? …………………………………………………暂存量存储位置

JISHU DW 0

PINLV DW ?

DATA ENDS

STACK SEGMENT STACK……………………………………………堆栈段定义

ST DW 20 DUP(?)…………………………………………………..堆栈空间大小为 20 字节

TOP LABEL WORD………………………………………………...定义栈顶指针为 TOP

STACK ENDS……………………………………………………………堆栈段结束

CODE SEGMENT………………………………………………………..定义指令段

ASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATA……………初始化段基地址

MAIN PROC FAR…………………………………………………………定义远调用 MAIN 函数

MOV AX,DATA……………………………………………………..初始化段基地址

MOV DS,AX

MOV AX,STACK

MOV SS,AX

MOV AX,CODE

MOV CS,AX

;初始化 8259,设置为单片,上升沿触发,完全

;非自动 EOI 方式,03H

MOV DX,8259AD0

MOV AL,00010011B

OUT DX,AL

MOV DX,8259AD1

MOV AL,10000000B…………..ICW2,10H,中断向量码 IR0——10H

OUT DX,AL

MOV AL,00000001B…………..ICW4,01H,

OUT DX,AL

;输入频率

LEA DX,MESS

MOV AH,09H

INT 21H

LEA DX,PINLV…………………将输入频率存到 PINLV 中

MOV AH,01H

INT 21H

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc