A

B

C

D

1

2

3

4

5

6

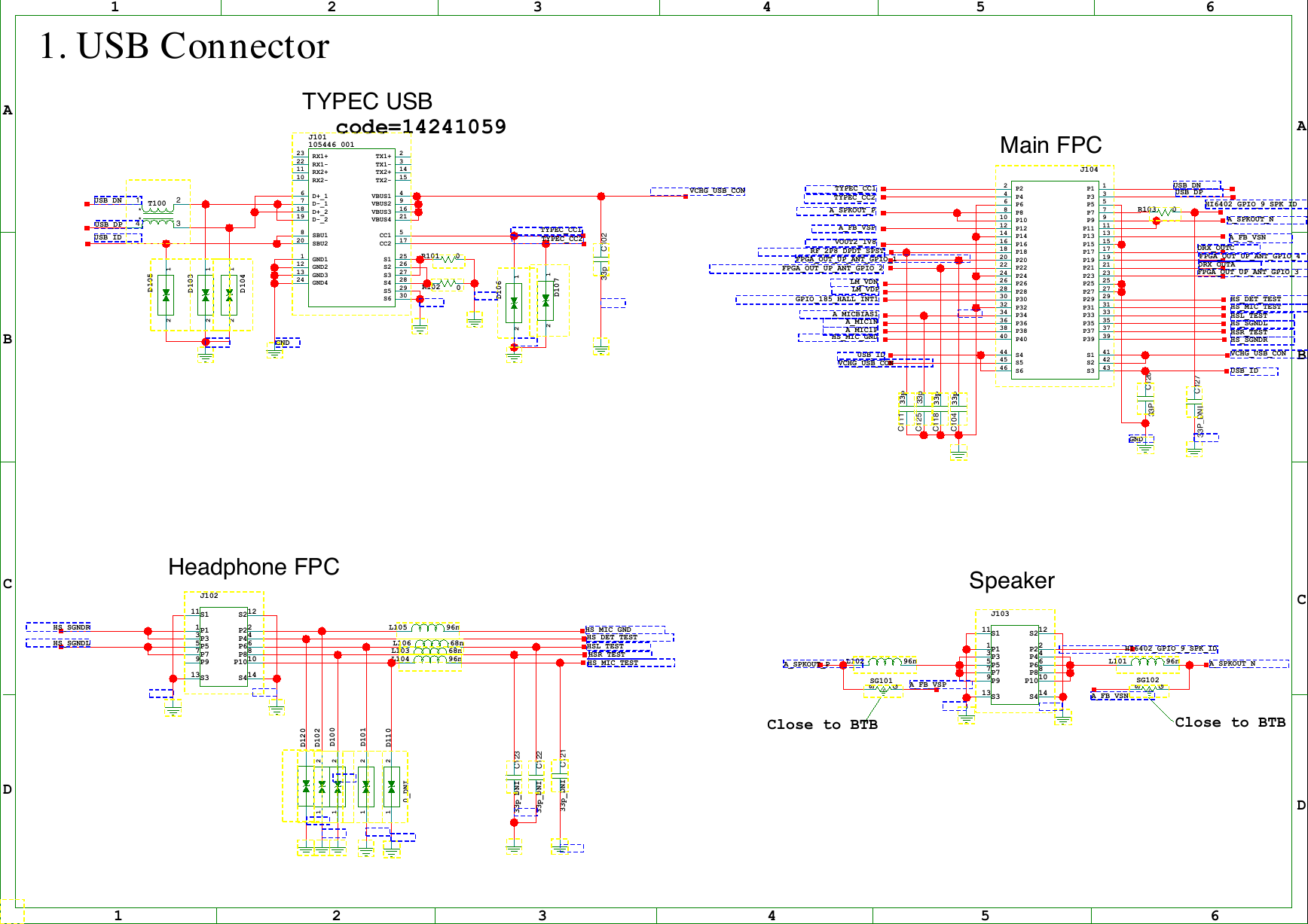

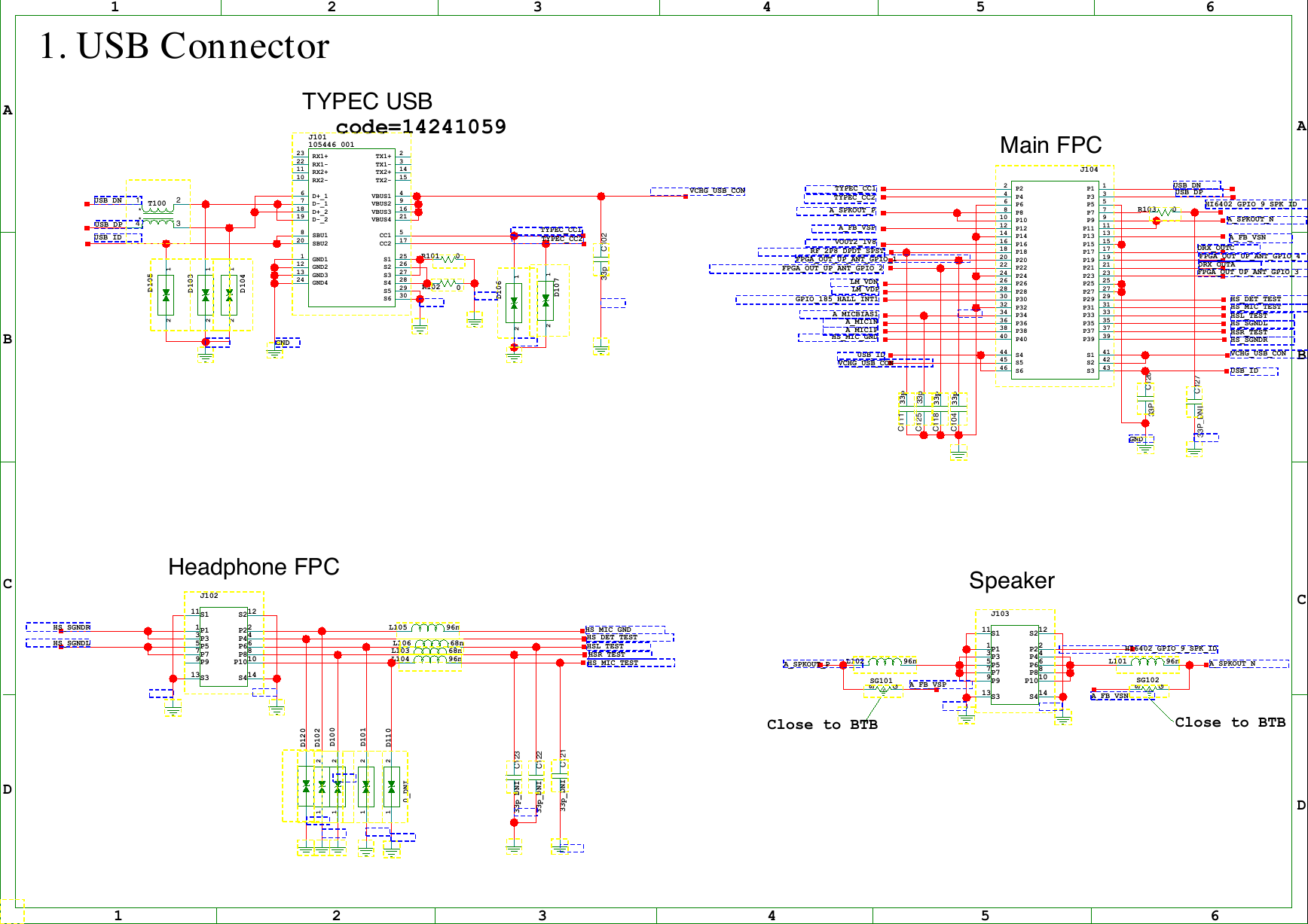

1. USB Connector

TYPEC USB

code=14241059

J101

105446_001

RX1+

RX1-

RX2+

RX2-

T100

1

*

*

4

2

3

USB_DN

USB_DP

USB_ID

1

1

1

5

0

1

D

3

0

1

D

4

0

1

D

2

2

2

23

22

11

10

6

7

18

19

8

20

1

12

13

24

GND

D+_1

D-_1

D+_2

D-_2

SBU1

SBU2

GND1

GND2

GND3

GND4

TX1+

TX1-

TX2+

TX2-

VBUS1

VBUS2

VBUS3

VBUS4

CC1

CC2

S1

S2

S3

S4

S5

S6

2

3

14

15

4

9

16

21

5

17

25

26

27

28

29

30

R101

0

R102

0

2

0

1

C

p

3

3

TYPEC_CC1

TYPEC_CC2

1

1

7

0

1

D

6

0

1

D

2

2

VCHG_USB_CON

TYPEC_CC1

TYPEC_CC2

A_SPKOUT_P

A_FB_VSP

VOUT2_1V8

RF_2P8_DPDT_SPST

FPGA_OUT_UP_ANT_GPIO_1

FPGA_OUT_UP_ANT_GPIO_2

LM_VDN

LM_VDP

GPIO_185_HALL_INT1

A_MICBIAS1

A_MIC1N

A_MIC1P

HS_MIC_GND

USB_ID

VCHG_USB_CON

p

3

3

1

1

1

C

p

3

3

5

2

1

C

p

3

3

8

1

1

C

p

3

3

4

0

1

C

Main FPC

J104

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

44

45

46

P2

P4

P6

P8

P10

P12

P14

P16

P18

P20

P22

P24

P26

P28

P30

P32

P34

P36

P38

P40

S4

S5

S6

P1

P3

P5

P7

P9

P11

P13

P15

P17

P19

P21

P23

P25

P27

P29

P31

P33

P35

P37

P39

S1

S2

S3

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

42

43

A

USB_DN

USB_DP

R103

0

HI6402_GPIO_9_SPK_ID

A_SPKOUT_N

A_FB_VSN

DRX_OUTC

FPGA_OUT_UP_ANT_GPIO_4

DRX_OUTA

FPGA_OUT_UP_ANT_GPIO_3

HS_DET_TEST

HS_MIC_TEST

HSL_TEST

HS_SGNDL

HSR_TEST

HS_SGNDR

VCHG_USB_CON

USB_ID

B

6

2

1

C

P

3

3

GND

7

2

1

C

I

N

D

_

P

3

3

HS_SGNDR

HS_SGNDL

Headphone FPC

J102

11S1

1

3

5

7

9

P1

P3

P5

P7

P9

13

S3

12

S2

2

4

6

8

10

P2

P4

P6

P8

P10

14

S4

L105

L106

L103

L104

96n

68n

68n

96n

HS_MIC_GND

HS_DET_TEST

HSL_TEST

HSR_TEST

HS_MIC_TEST

0

2

1

D

2

0

1

D

0

0

1

D

1

0

1

D

0

1

1

D

2

2

2

2

I

N

D

_

0

1

1

1

1

3

2

1

C

I

N

D

_

p

3

3

2

2

1

C

I

N

D

_

p

3

3

1

2

1

C

I

N

D

_

p

3

3

Speaker

J103

11S1

1

3

5

7

9

P1

P3

P5

P7

P9

13

S3

12

S2

2

4

6

8

10

P2

P4

P6

P8

P10

14

S4

A_SPKOUT_P

L102

96n

SG101

S G

S

A_FB_VSP

Close to BTB

HI6402_GPIO_9_SPK_ID

L101

96n

A_SPKOUT_N

SG102

S G

S

A_FB_VSN

Close to BTB

C

D

1

2

3

4

5

6

�

1

2

3

4

5

6

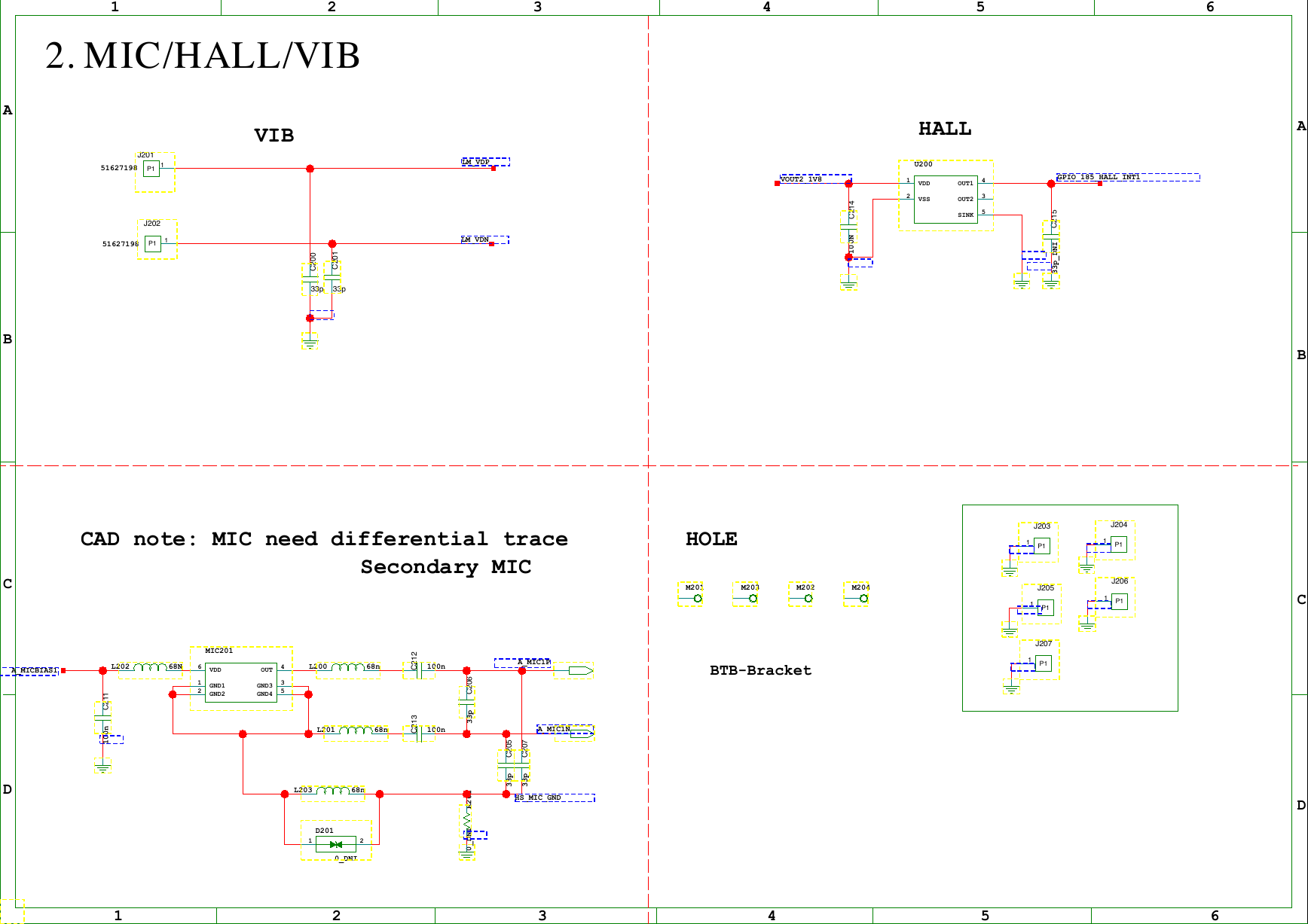

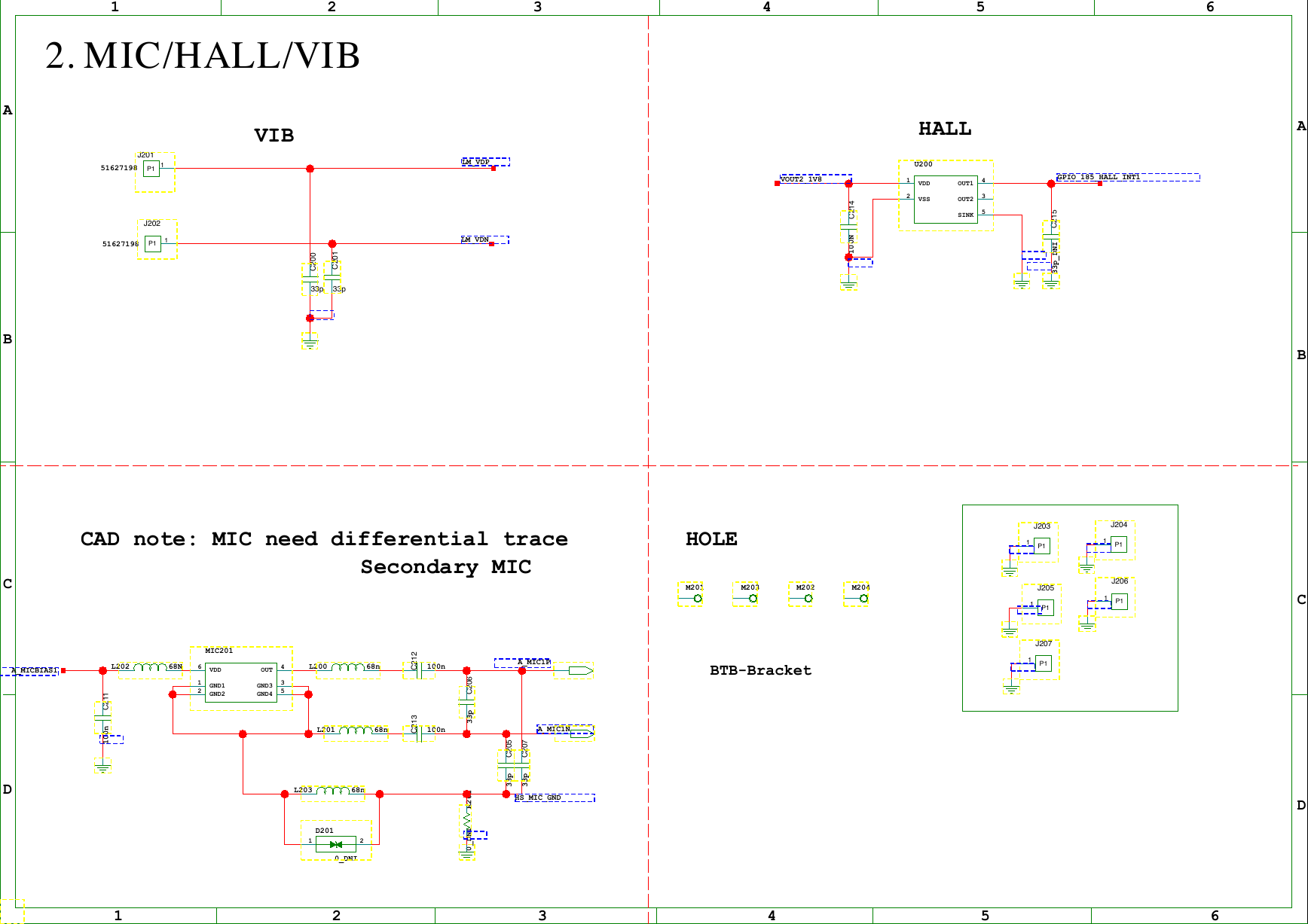

2. MIC/HALL/VIB

J201

51627198

1

P1

J202

51627198

P1

1

VIB

0

0

2

C

1

0

2

C

33p

33p

LM_VDP

LM_VDN

HALL

U200

1 VDD

2

VSS

OUT1

OUT2

SINK

4

3

5

VOUT2_1V8

4

1

2

C

N

0

0

1

GPIO_185_HALL_INT1

5

1

2

C

I

N

D

_

p

3

3

A

B

C

A

B

C

D

J204

1 P1

J206

1 P1

J203

1 P1

J205

1 P1

J207

1 P1

CAD note: MIC need differential trace

HOLE

Secondary MIC

M201

M203

M202

M204

MIC201

6

VDD

1 GND1

2

GND2

OUT

GND3

GND4

4

3

5

A_MICBIAS1

L202

68N

1

1

2

C

n

0

0

1

D

L200

68n

2

1

2

C

100n

A_MIC1P

L201

68n

3

1

2

C

100n

L203

68n

D201

1

2

0_DNI

6

0

2

C

p

3

3

1

0

2

R

I

N

D

_

0

A_MIC1N

5

0

2

C

7

0

2

C

p

3

3

p

3

3

HS_MIC_GND

BTB-Bracket

1

2

3

4

5

6

�

1

2

3

4

5

6

3.Reserved

A

B

C

D

A

B

C

D

1

2

3

4

5

6

�

1

2

3

4

5

6

4. Reserved

A

B

C

D

A

B

C

D

1

2

3

4

5

6

�

1

2

3

4

5

6

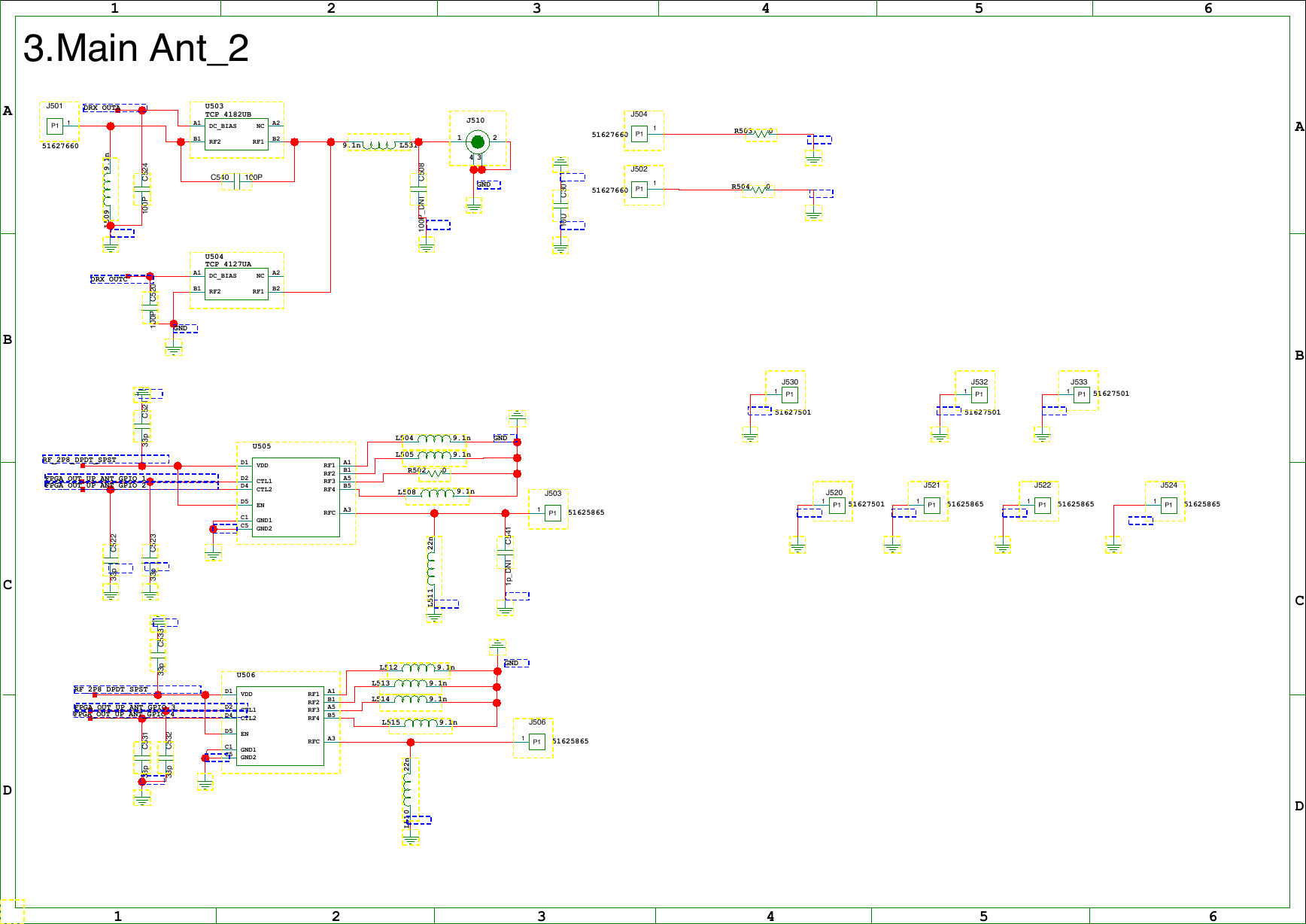

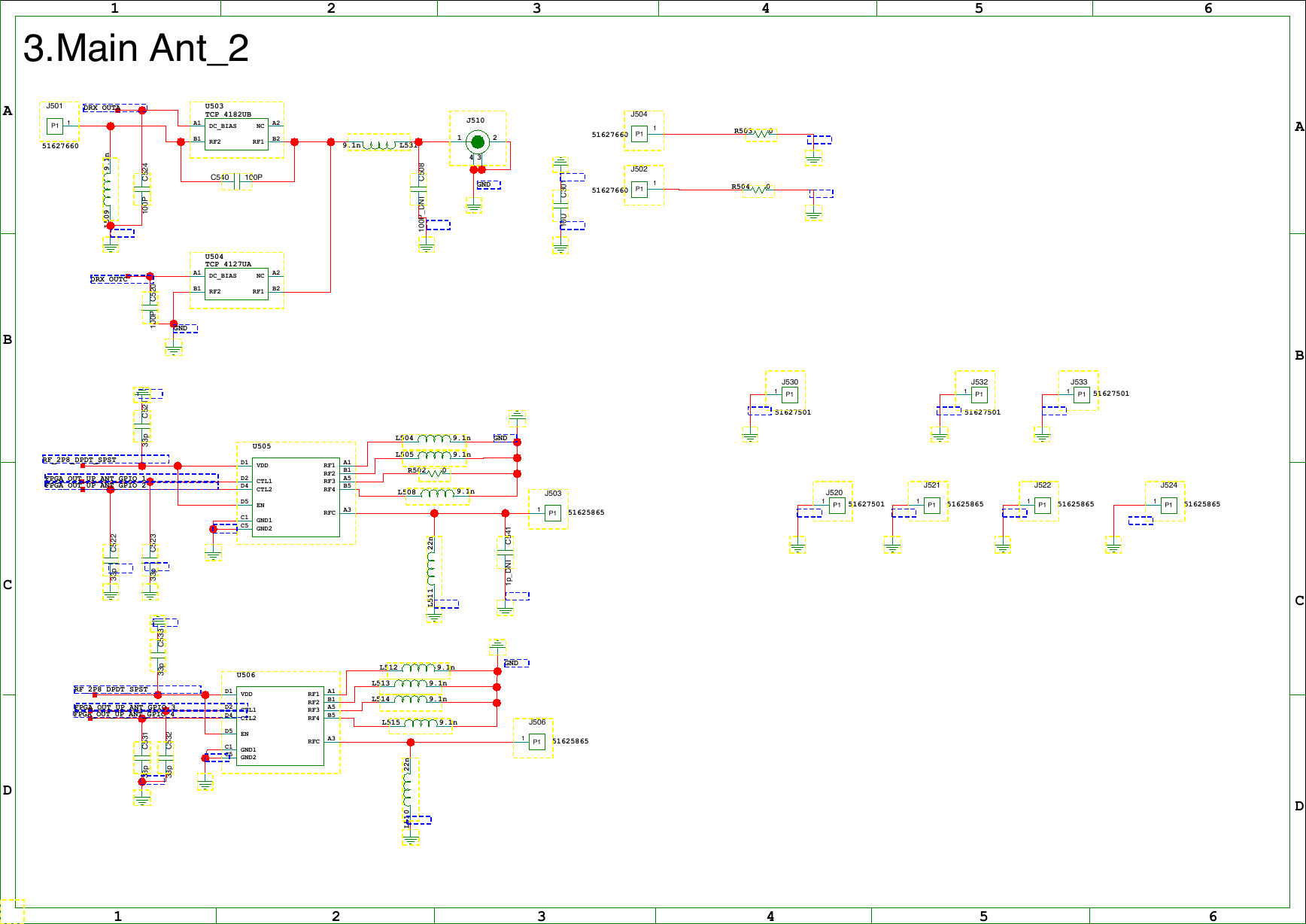

3.Main Ant_2

A

DRX_OUTA

J501

1

P1

51627660

n

1

.

9

9

0

5

L

4

2

5

C

P

0

0

1

U503

TCP_4182UB

A1 DC_BIAS

B1

RF2

NC

RF1

A2

B2

C540

100P

J510

1

2

4 3

GND

9.1n

L531

8

0

5

C

I

N

D

_

P

0

0

1

J504

51627660

P1

J502

51627660

P1

1

1

1

0

3

C

U

0

1

R503

0

R504

0

U504

TCP_4127UA

A1 DC_BIAS

B1

RF2

NC

RF1

A2

B2

DRX_OUTC

0

2

5

C

P

0

0

1

GND

1

2

5

C

p

3

3

RF_2P8_DPDT_SPST

FPGA_OUT_UP_ANT_GPIO_1

FPGA_OUT_UP_ANT_GPIO_2

2

2

5

C

p

3

3

3

2

5

C

p

3

3

3

3

5

C

p

3

3

RF_2P8_DPDT_SPST

FPGA_OUT_UP_ANT_GPIO_3

FPGA_OUT_UP_ANT_GPIO_4

1

3

5

C

p

3

3

2

3

5

C

p

3

3

U505

VDD

CTL1

CTL2

EN

GND1

GND2

D1

D2

D4

D5

C1

C5

RF1

RF2

RF3

RF4

RFC

A1

B1

A5

B5

A3

U506

D1

VDD

D2 CTL1

D4

CTL2

D5

C1

C5

EN

GND1

GND2

RF1

RF2

RF3

RF4

RFC

A1

B1

A5

B5

A3

L504

L505

GND

9.1n

9.1n

R502

0

L508

9.1n

J503

1 P1

51625865

1

4

5

C

I

N

D

_

p

1

GND

n

2

2

1

1

5

L

L512

9.1n

L513

L514

9.1n

9.1n

L515

9.1n

J506

1 P1

51625865

n

2

2

0

1

5

L

B

C

D

J530

1 P1

51627501

J532

1 P1

51627501

J533

1 P1

51627501

J520

1 P1

J521

J522

J524

51627501

1 P1

51625865

1 P1

51625865

1 P1

51625865

A

B

C

D

1

2

3

4

5

6

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc