ALINT-PRO使用教程�

目录一、软件窗口..............................................................................................................3二、工程Project.........................................................................................................92.1workspace和project......................................................................................102.2创建工程........................................................................................................102.3添加被测文件.................................................................................................112.4导入工程文件.................................................................................................122.5项目设置.........................................................................................................122.6约束设置........................................................................................................142.7执行检查.........................................................................................................172.8检查结果查看.................................................................................................17三、ALDEC-CDC规则集............................................................................................19�

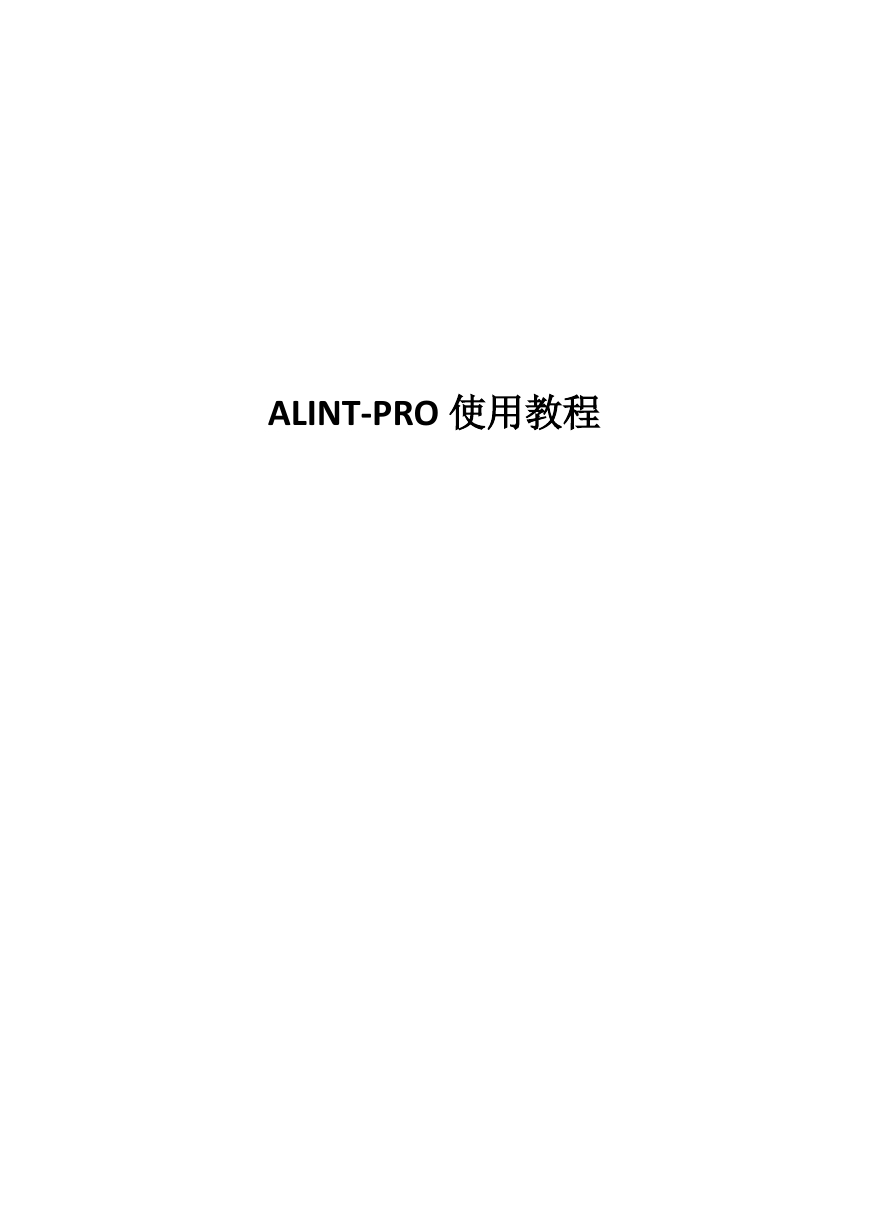

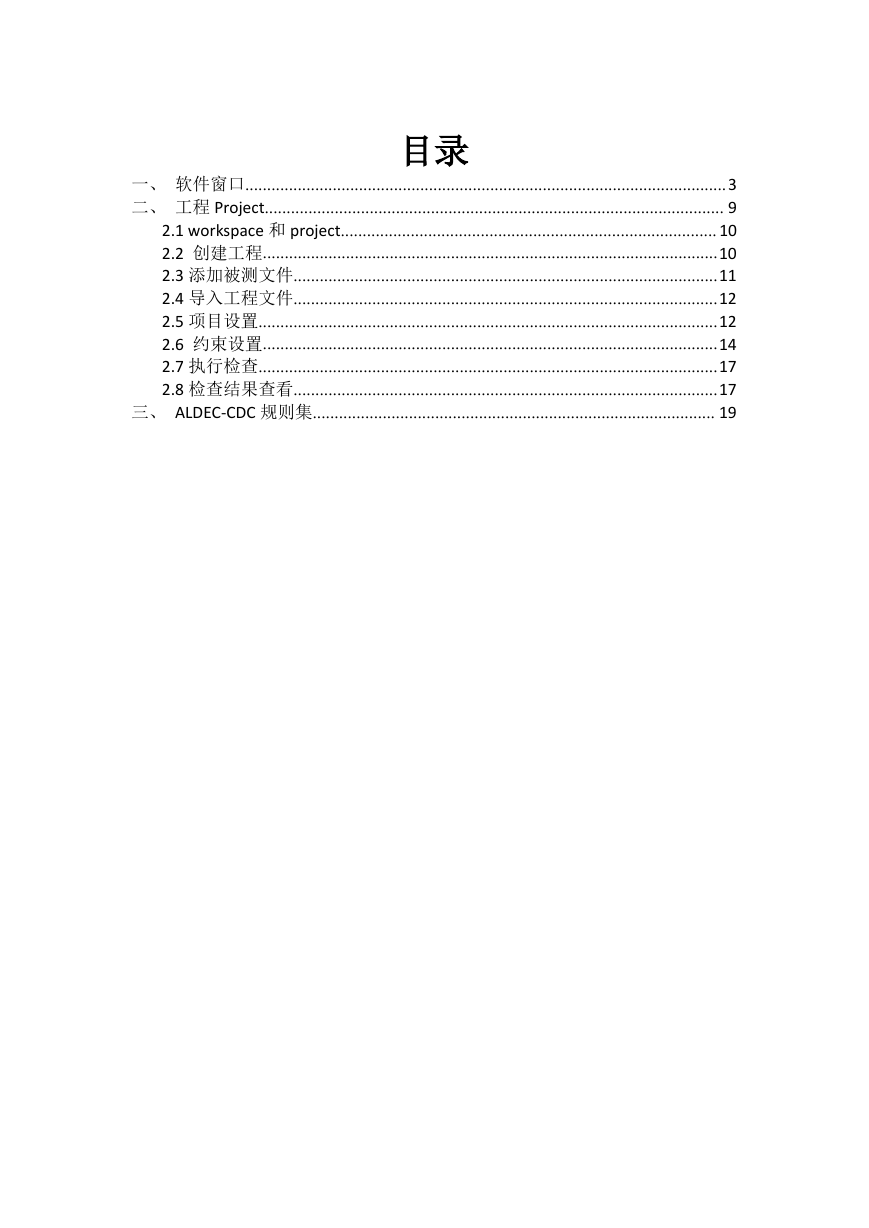

一、软件窗口工程管理窗口(view--designmanagementwindows--projectmanager)工程管理窗口是整个设计的管理窗口,有workspace、project和file三种实体,workspace下可以有多个project,project下有多个file。文件浏览器(view--designmanagementwindows--filebrowser)文件浏览器不同于工程管理器,工程管理器中的file是该工程中的子模块,文件浏览器是指当前目录下的所有文件。库观察器(view--designmanagementwindows--libraryviewer)库观察器是为厂商IP提供的检查库文件,用于识别主流FPGA厂商的IP模块,包括:xilinx,intel,lattice,microsemi等主流FPGA厂商。�

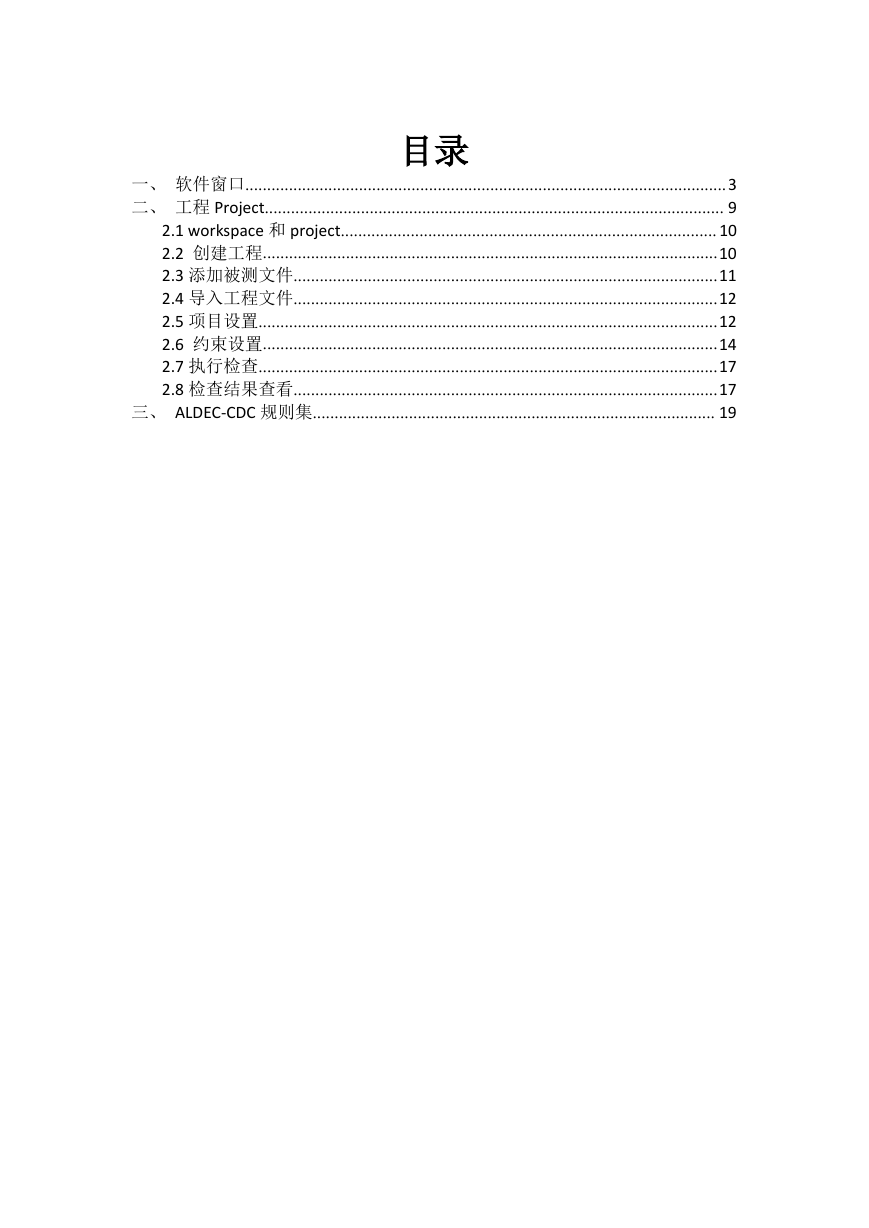

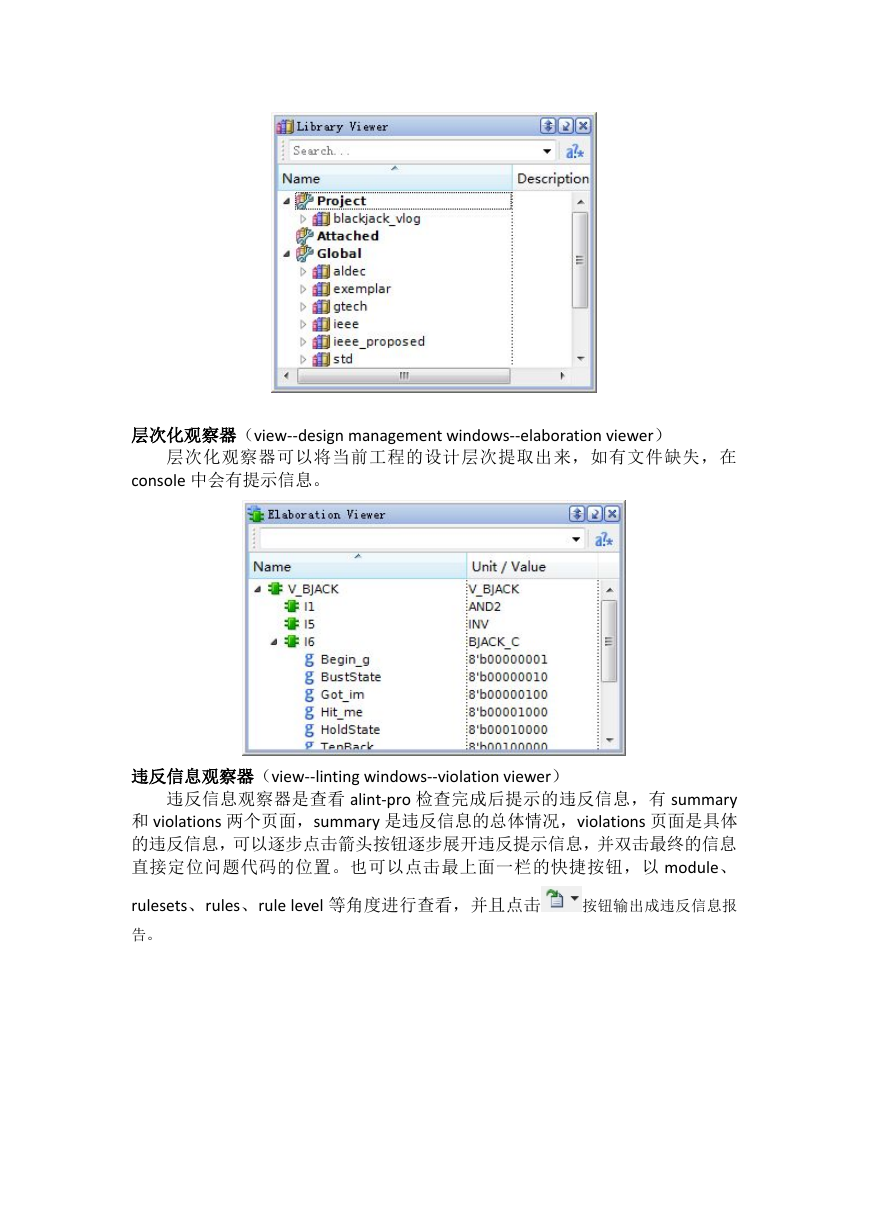

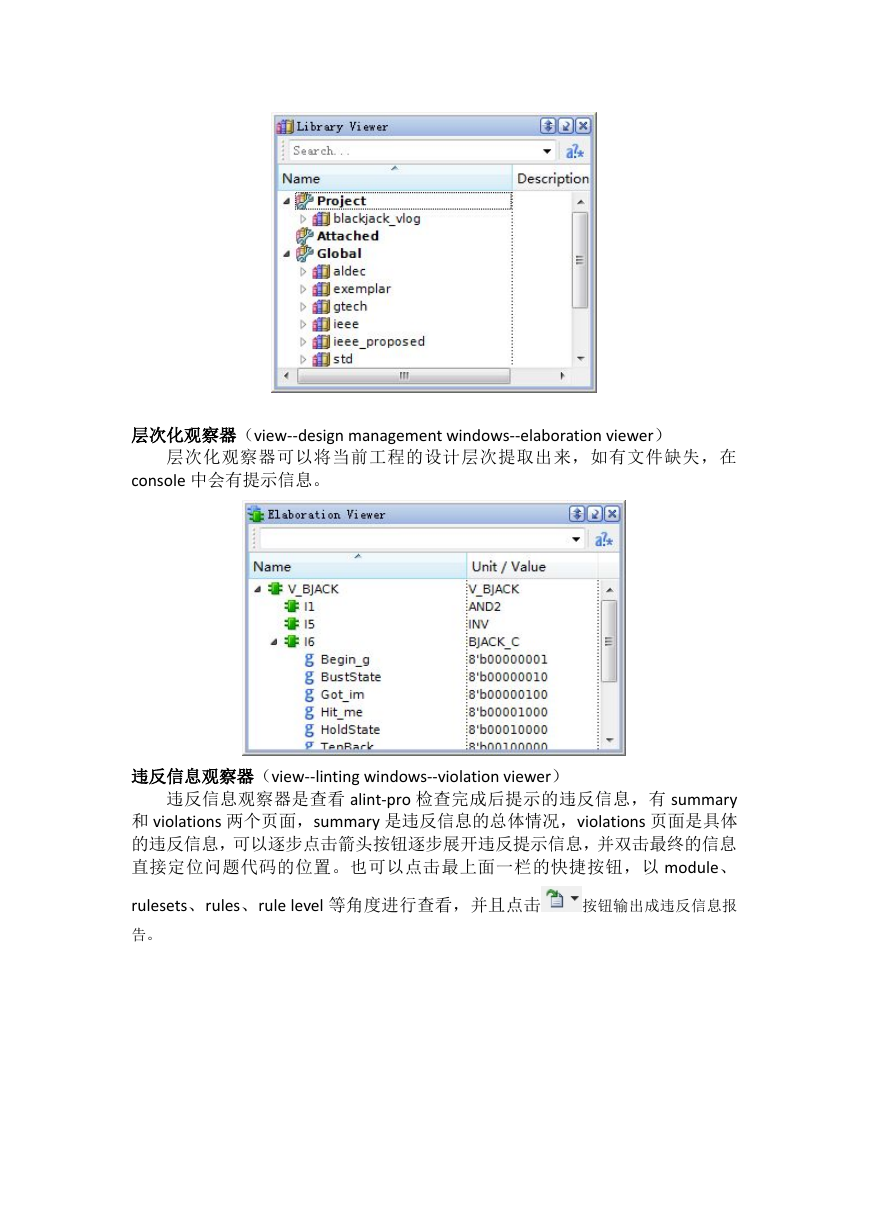

层次化观察器(view--designmanagementwindows--elaborationviewer)层次化观察器可以将当前工程的设计层次提取出来,如有文件缺失,在console中会有提示信息。违反信息观察器(view--lintingwindows--violationviewer)违反信息观察器是查看alint-pro检查完成后提示的违反信息,有summary和violations两个页面,summary是违反信息的总体情况,violations页面是具体的违反信息,可以逐步点击箭头按钮逐步展开违反提示信息,并双击最终的信息直接定位问题代码的位置。也可以点击最上面一栏的快捷按钮,以module、rulesets、rules、rulelevel等角度进行查看,并且点击按钮输出成违反信息报告。�

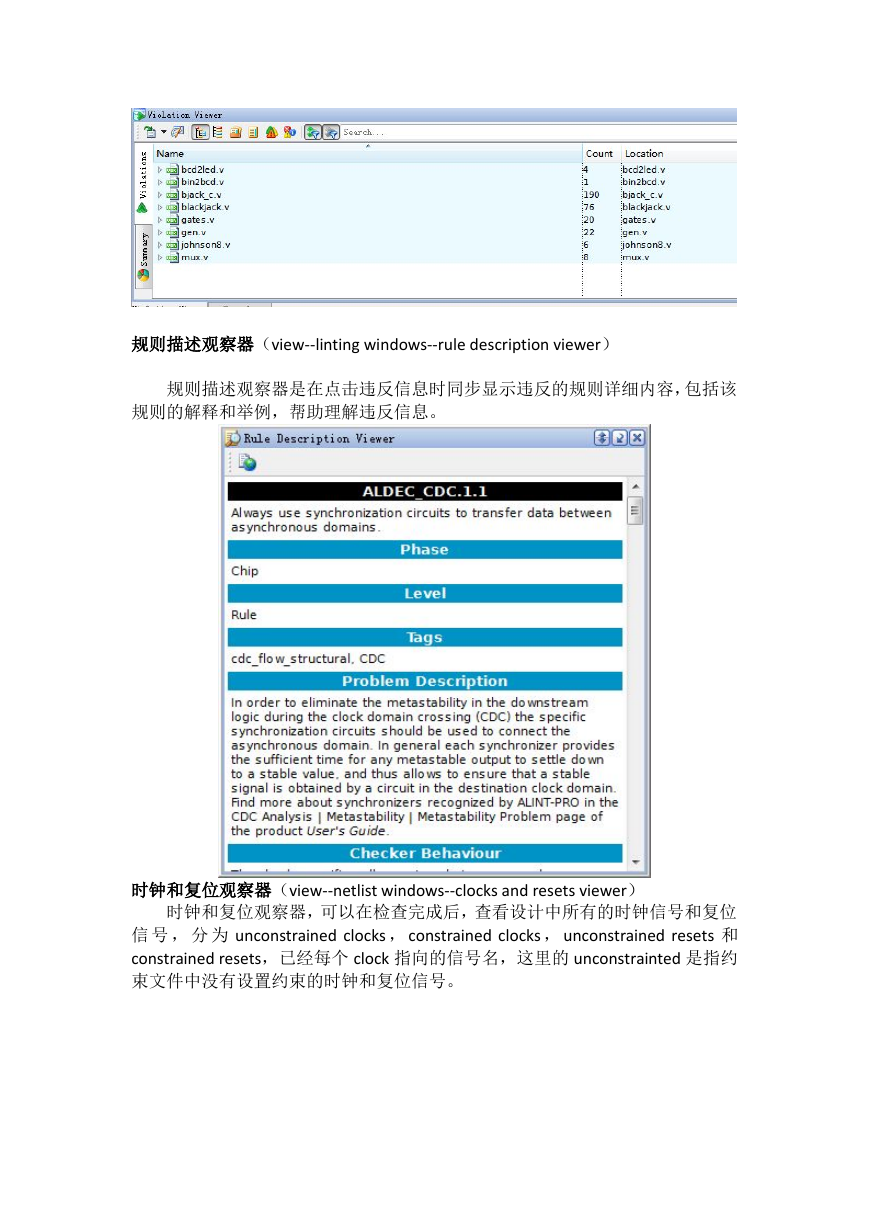

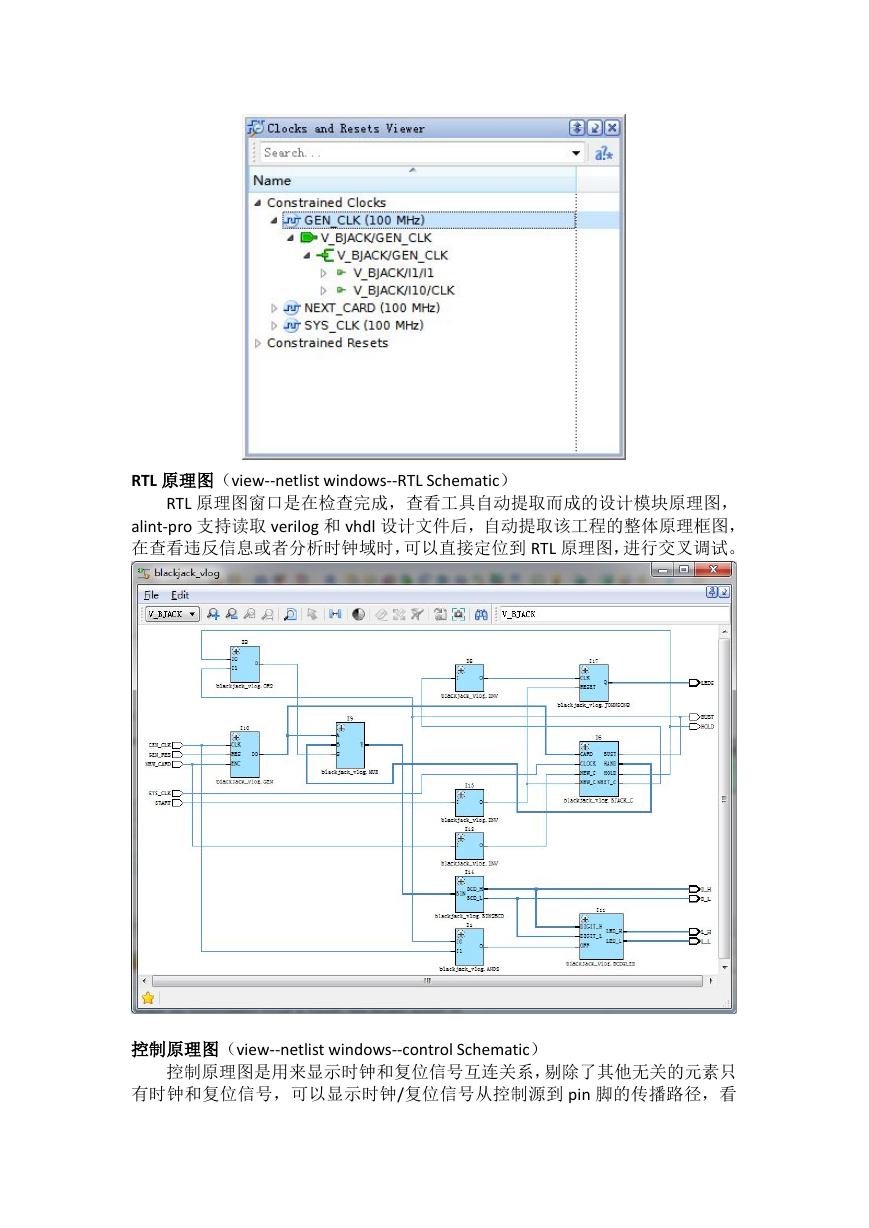

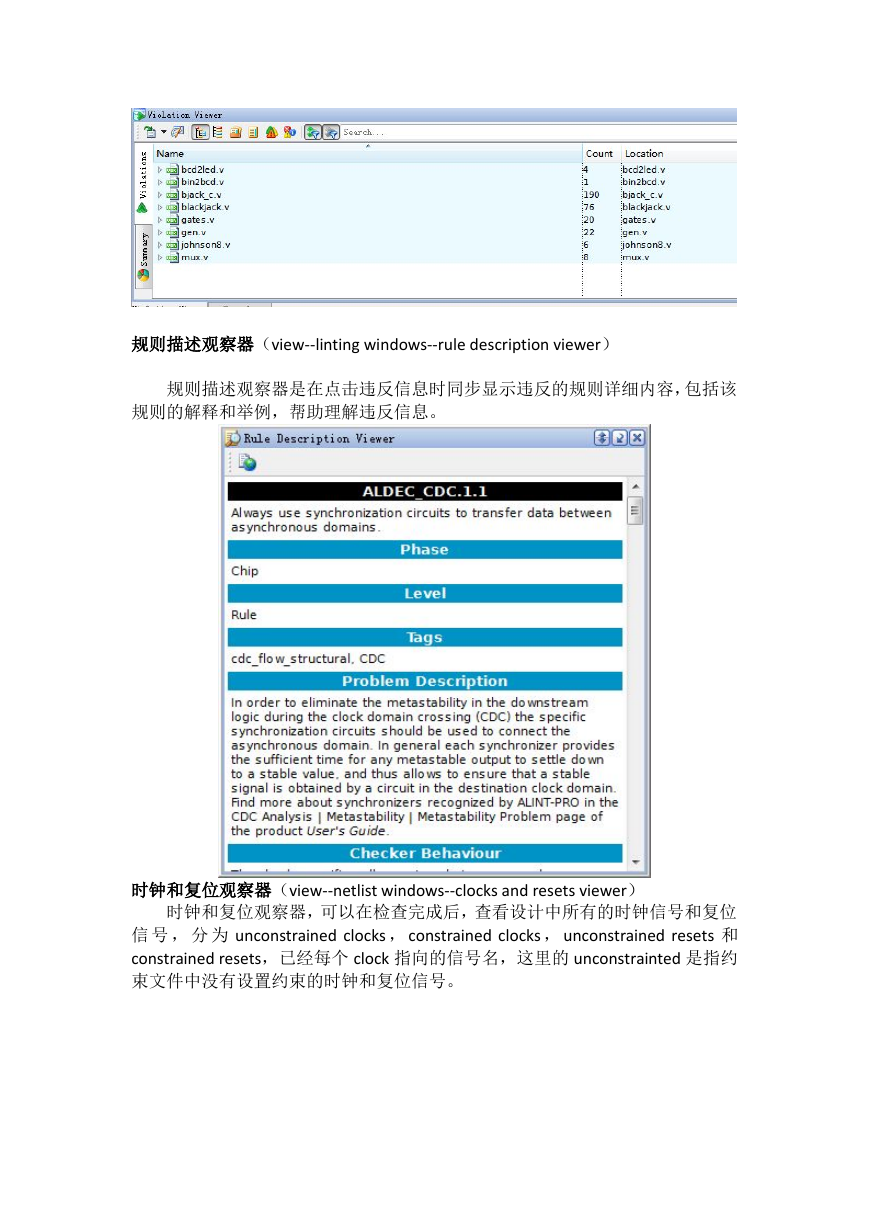

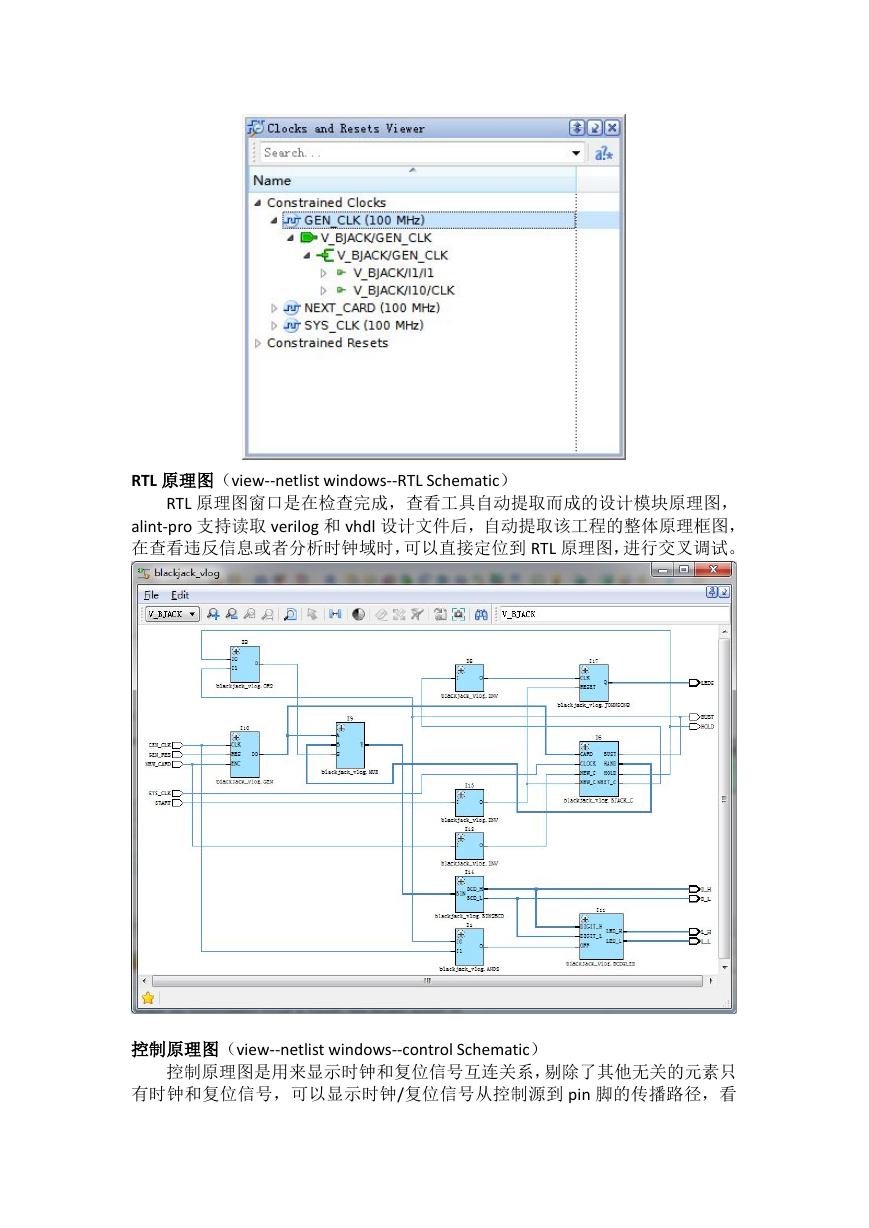

规则描述观察器(view--lintingwindows--ruledescriptionviewer)规则描述观察器是在点击违反信息时同步显示违反的规则详细内容,包括该规则的解释和举例,帮助理解违反信息。时钟和复位观察器(view--netlistwindows--clocksandresetsviewer)时钟和复位观察器,可以在检查完成后,查看设计中所有的时钟信号和复位信号,分为unconstrainedclocks,constrainedclocks,unconstrainedresets和constrainedresets,已经每个clock指向的信号名,这里的unconstrainted是指约束文件中没有设置约束的时钟和复位信号。�

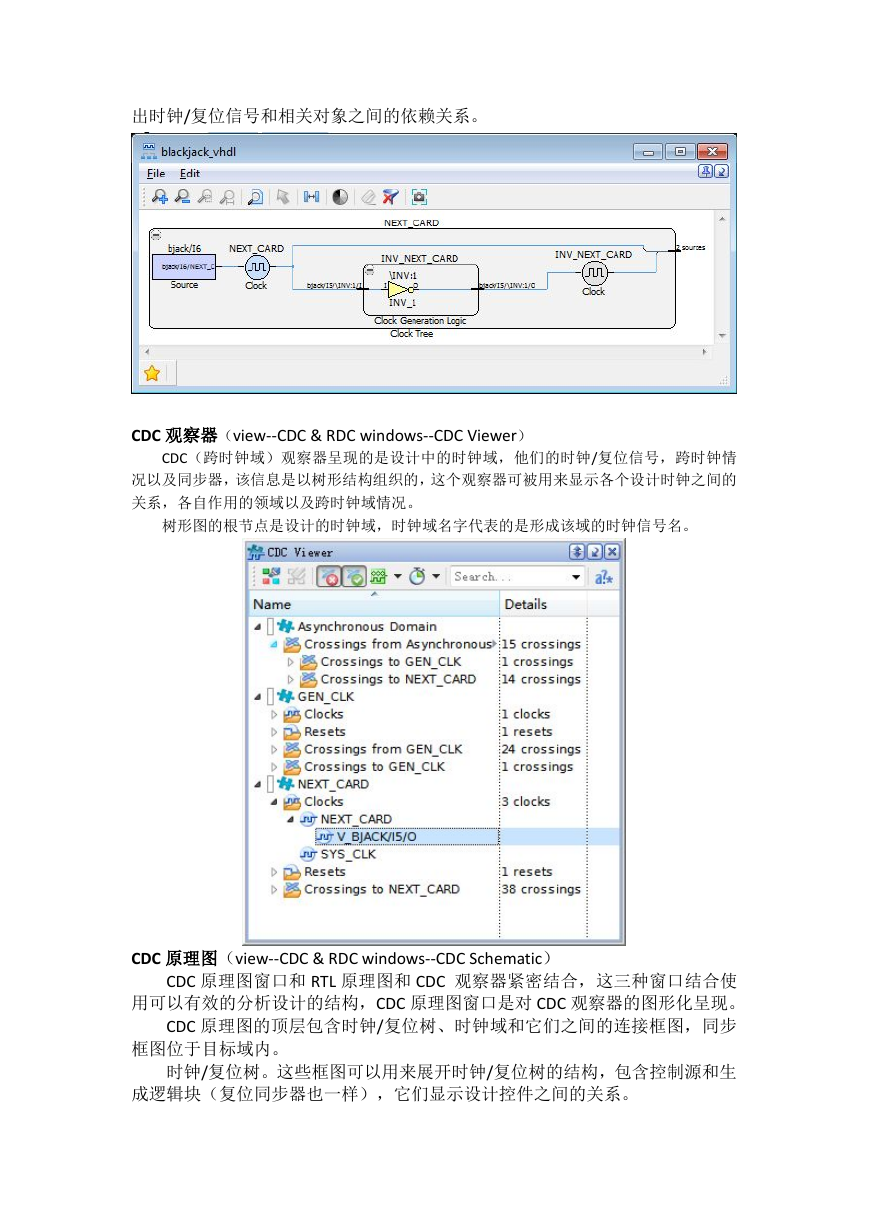

RTL原理图(view--netlistwindows--RTLSchematic)RTL原理图窗口是在检查完成,查看工具自动提取而成的设计模块原理图,alint-pro支持读取verilog和vhdl设计文件后,自动提取该工程的整体原理框图,在查看违反信息或者分析时钟域时,可以直接定位到RTL原理图,进行交叉调试。控制原理图(view--netlistwindows--controlSchematic)控制原理图是用来显示时钟和复位信号互连关系,剔除了其他无关的元素只有时钟和复位信号,可以显示时钟/复位信号从控制源到pin脚的传播路径,看�

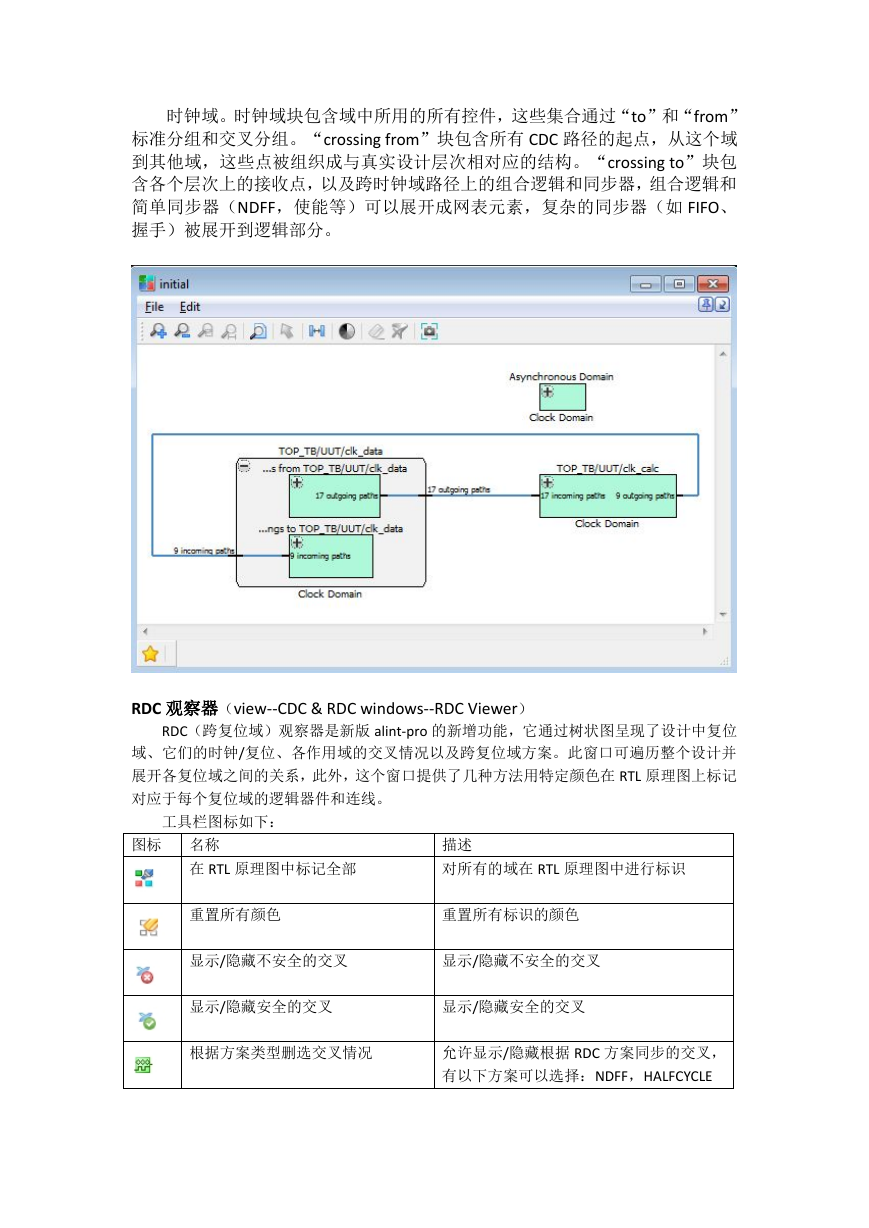

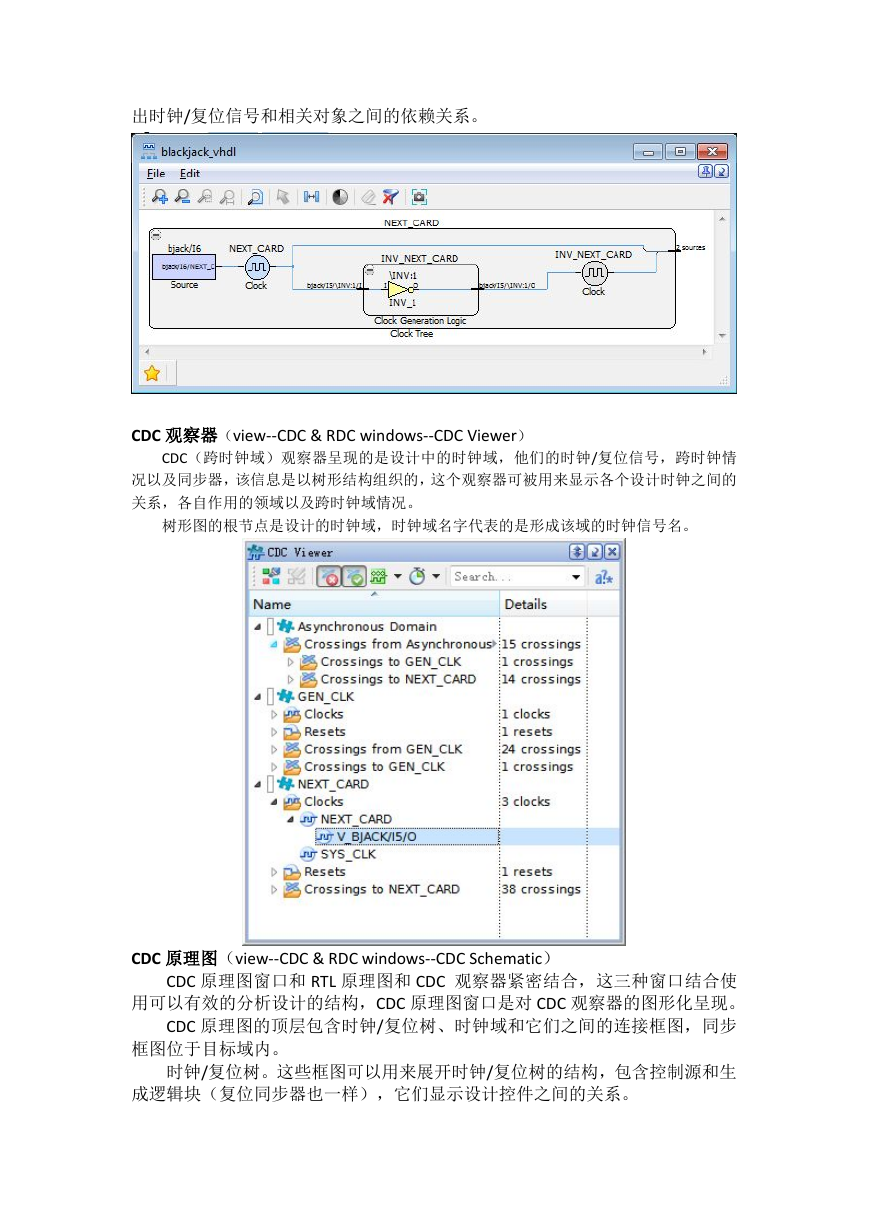

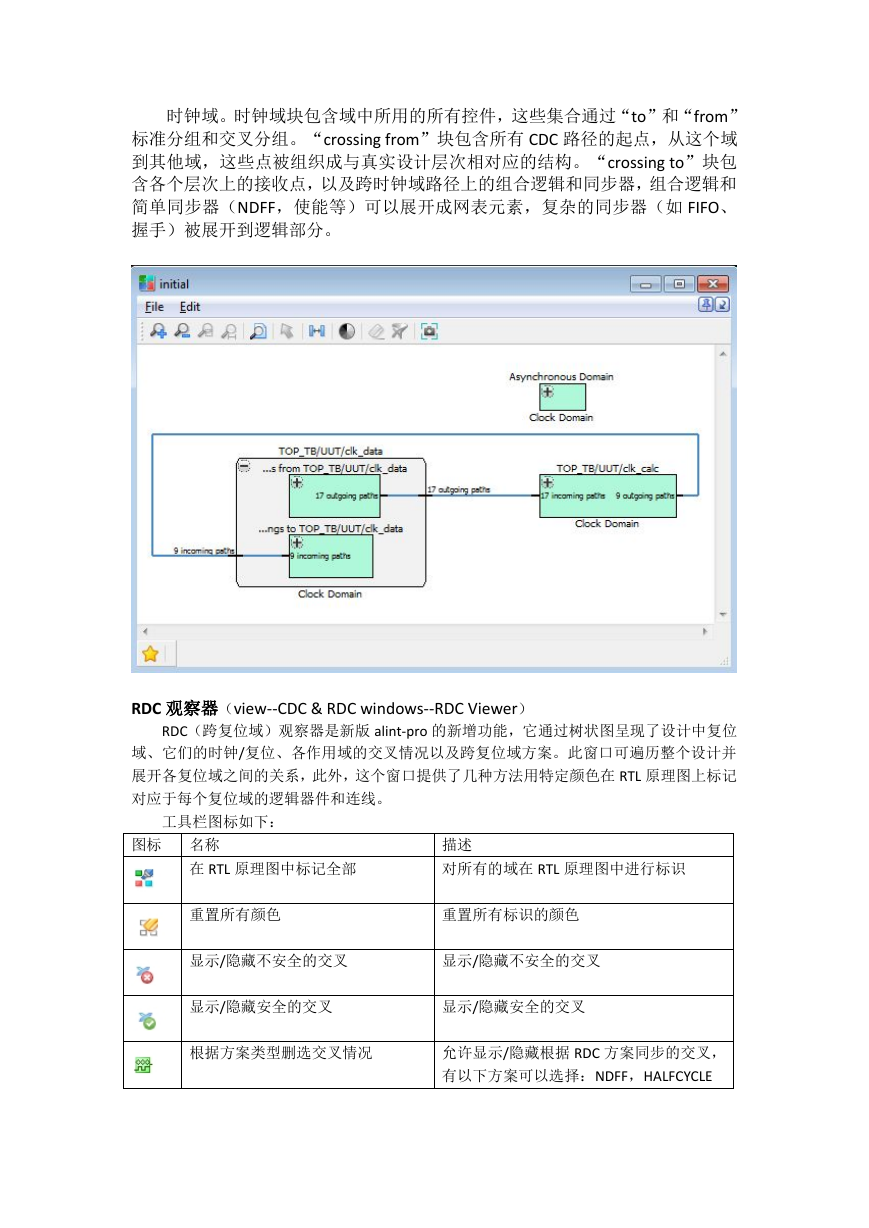

出时钟/复位信号和相关对象之间的依赖关系。CDC观察器(view--CDC&RDCwindows--CDCViewer)CDC(跨时钟域)观察器呈现的是设计中的时钟域,他们的时钟/复位信号,跨时钟情况以及同步器,该信息是以树形结构组织的,这个观察器可被用来显示各个设计时钟之间的关系,各自作用的领域以及跨时钟域情况。树形图的根节点是设计的时钟域,时钟域名字代表的是形成该域的时钟信号名。CDC原理图(view--CDC&RDCwindows--CDCSchematic)CDC原理图窗口和RTL原理图和CDC观察器紧密结合,这三种窗口结合使用可以有效的分析设计的结构,CDC原理图窗口是对CDC观察器的图形化呈现。CDC原理图的顶层包含时钟/复位树、时钟域和它们之间的连接框图,同步框图位于目标域内。时钟/复位树。这些框图可以用来展开时钟/复位树的结构,包含控制源和生成逻辑块(复位同步器也一样),它们显示设计控件之间的关系。�

时钟域。时钟域块包含域中所用的所有控件,这些集合通过“to”和“from”标准分组和交叉分组。“crossingfrom”块包含所有CDC路径的起点,从这个域到其他域,这些点被组织成与真实设计层次相对应的结构。“crossingto”块包含各个层次上的接收点,以及跨时钟域路径上的组合逻辑和同步器,组合逻辑和简单同步器(NDFF,使能等)可以展开成网表元素,复杂的同步器(如FIFO、握手)被展开到逻辑部分。RDC观察器(view--CDC&RDCwindows--RDCViewer)RDC(跨复位域)观察器是新版alint-pro的新增功能,它通过树状图呈现了设计中复位域、它们的时钟/复位、各作用域的交叉情况以及跨复位域方案。此窗口可遍历整个设计并展开各复位域之间的关系,此外,这个窗口提供了几种方法用特定颜色在RTL原理图上标记对应于每个复位域的逻辑器件和连线。工具栏图标如下:图标名称描述在RTL原理图中标记全部对所有的域在RTL原理图中进行标识重置所有颜色重置所有标识的颜色显示/隐藏不安全的交叉显示/隐藏不安全的交叉显示/隐藏安全的交叉显示/隐藏安全的交叉根据方案类型删选交叉情况允许显示/隐藏根据RDC方案同步的交叉,有以下方案可以选择:NDFF,HALFCYCLE�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc