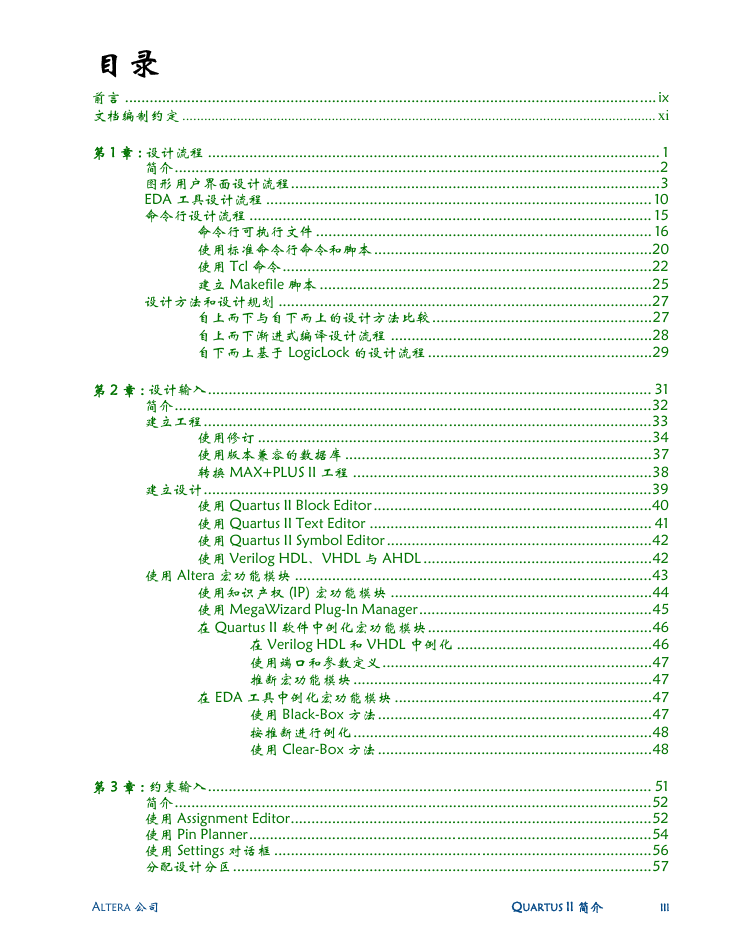

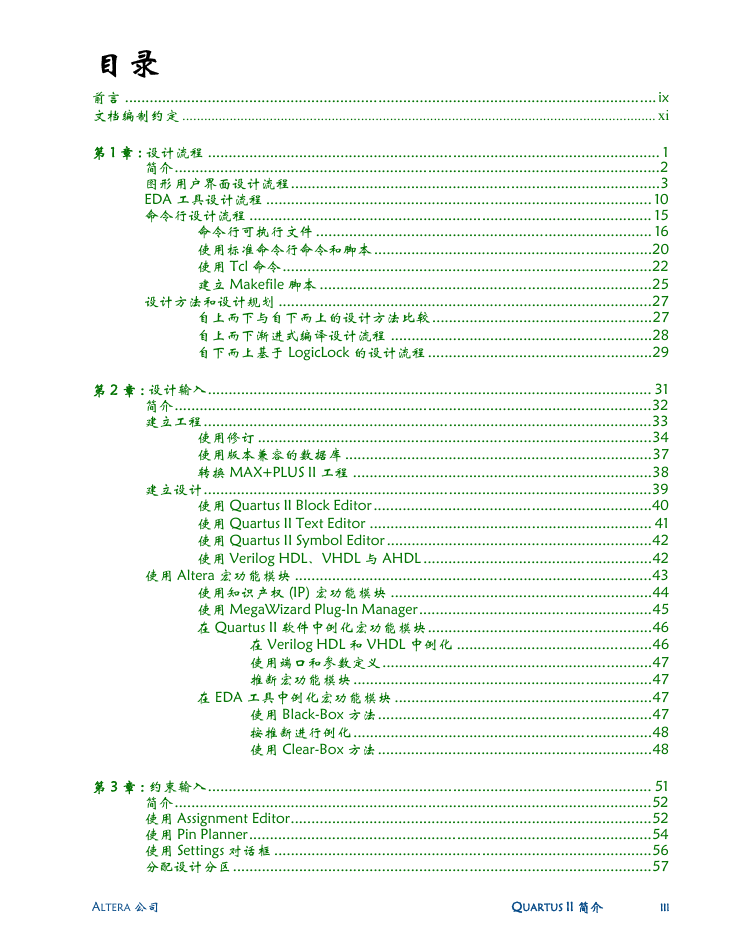

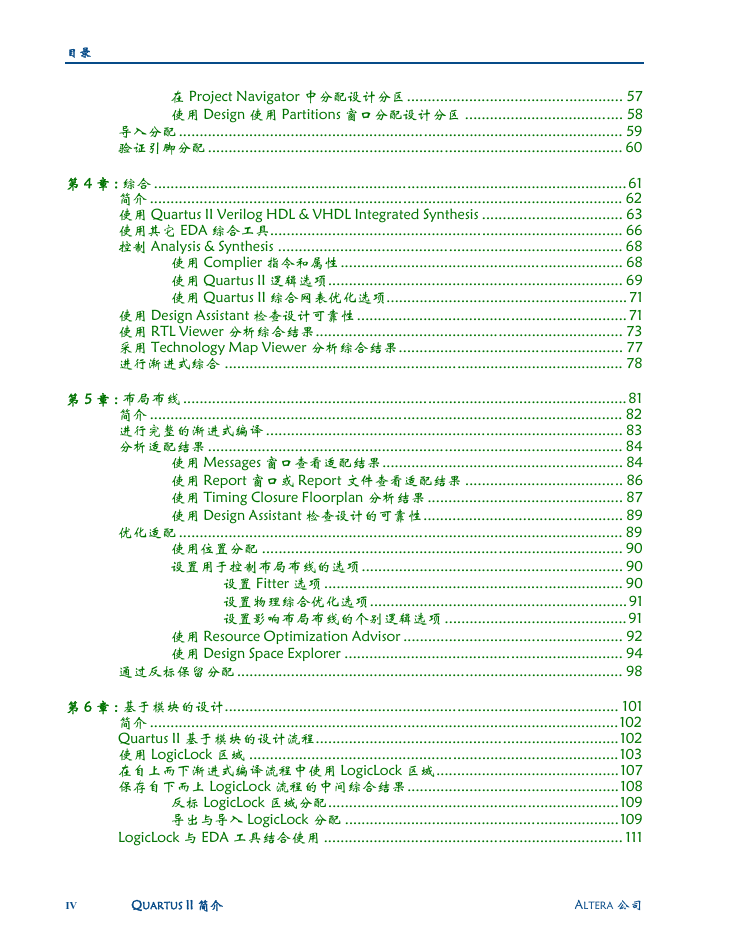

目录

前言

文档编制约定

第一章:设计流程

简介

图形用户界面设计流程

EDA工具设计流程

命令行设计流程

命令行可执行文件

使用标准命令行命令和脚本

使用Tcl 命令

建立Makefile 脚本

设计方法和设计规划

自上而下与自下而上的设计方法比较

自上而下渐进式编译设计流程

自下而上基于LogicLock的设计流程

第二章:设计输入

简介

建立工程

使用修订

使用版本兼容的数据库

转换MAX+PLUS II工程

建立设计

使用Quartus II Block Editor

使用Quartus II Text Editor

使用Quartus II Symbol Editor

使用Verilog HDL、VHDL 与AHDL

使用Altera宏功能模块

使用知识产权(IP) 宏功能模块

使用MegaWizard Plug-In Manager

在 Quartus II 软件中例化宏功能模块

在 Verilog HDL 和 VHDL 中例化

使用端口和参数定义

推断宏功能模块

在 EDA 工具中例化宏功能模块

使用Black-Box 方法

按推断进行例化

使用 Clear-Box 方法

第三章:约束输入

简介

使用 Assignment Editor

使用Pin Planner

使用Settings对话框

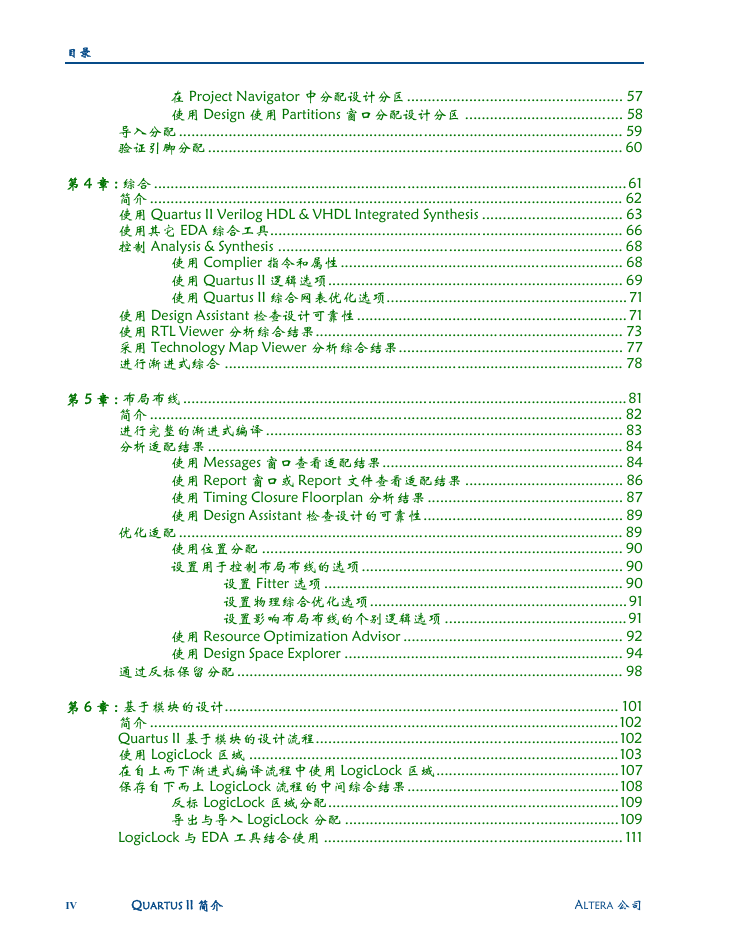

分配设计分区

在Project Navigator中分配设计分区

使用Design使用 Partitions窗口分配设计分区

导入分配

验证引脚分配

第四章:综合

简介

使用Quartus II Verilog HDL & VHDL Integrated Synthesis

使用其它EDA 综合工具

控制Analysis & Synthesis

使用Complier指令和属性

使用Quartus II 逻辑选项

使用Quartus II 综合网表优化选项

使用Design Assistant 检查设计可靠性

使用RTL Viewer 分析综合结果

采用Technology Map Viewer分析综合结果

进行渐进式综合

第五章:布局布线

简介

进行完整的渐进式编译

分析适配结果

使用Messages 窗口查看适配结果

使用Report 窗口或Report 文件查看适配结果

使用Timing Closure Floorplan分析结果

使用Design Assistant 检查设计的可靠性

优化适配

使用位置分配

设置用于控制布局布线的选项

设置Fitter选项

设置物理综合优化选项

设置影响布局布线的个别逻辑选项

使用Resource Optimization Advisor

使用Design Space Explorer

通过反标保留分配

第六章:基于模块的设计

简介

Quartus II基于模块的设计流程

使用LogicLock 区域

在自上而下渐进式编译流程中使用LogicLock 区域

保存自下而上LogicLock流程的中间综合结果

反标LogicLock区域分配

导出与导入LogicLock 分配

LogicLock 与EDA 工具结合使用

第七章:仿真

简介

使用EDA 工具进行设计仿真

进行EDA 仿真工具设置

生成仿真输出文件

EDA 仿真流程

功能仿真流程

NativeLink仿真流程

手动时序仿真流程

仿真库

使用Quartus II Simulator 进行仿真设计

建立波形文件

使用 Simulator Tool

第八章:时序分析

简介

在Quartus II 软件中进行时序分析

指定时序要求

进行工程全局范围的时序设置

进行个别时序分配

进行时序分析

进行早期时序估算

查看时序分析结果

使用报告窗口

进行分配与查看延时路径

使用Technology Map Viewer

使用EDA 工具进行时序分析

使用PrimeTime 软件

使用Tau软件

第九章:时序逼近

简介

使用Timing Closure Floorplan

查看分配与布线

进行分配

使用Timing Optimization Advisor

使用网表优化实现时序逼近

使用LogicLock 区域达到时序逼近

软LogicLock 区域

基于路径的分配

使用Design Space Explorer达到时序逼近

使用渐进式编译达到时序逼近

第十章:功耗分析

简介

使用PowerPlay Power Analyzer分析功耗

指定Power Analyzer选项

使用PowerPlay Early Power Estimator

第十一章:编程和配置

简介

使用Programmer 对一个或多个器件编程

建立辅助编程文件

建立其它编程文件格式

转换编程文件

使用Quartus II 软件通过远程JTAG 服务器进 行编程

第十二章:调试

简介

使用 SignalTap II Logic Analyzer

设置和运行 SignalTap II Logic Analyzer

渐进式编译使用SignalTap II Logic Analyzer

分析 SignalTap II 数据

使用SignalProbe

使用In-System Memory Content Editor

使用RTL Viewer和Technology Map Viewer

使用Chip Editor

第十三章:工程更改管理

简介

使用Chip Editor识别延时与关键路径

在Chip Editor中编辑基元

使用Resource Property Editor 修改资源属性

使用Change Manager 查看和管理更改

验证ECO 更改的效果

第十四章:形式验证

简介

使用EDA形式验证工具

指定其他设置

第十五章:系统级设计

简介

使用SOPC Builder建立SOPC设计

建立系统

生成系统

使用DSP Builder建立DSP设计

例化功能

生成仿真文件

生成综合文件

第十六章:软件开发

简介

在Quartus II 软件中使用Software Builder

进行软件构建设置

生成软件输出文件

生成闪存编程文件

生成被动编程文件

生成存储器初始化数据文件

第十七章:安装、许可和技术支持

安装Quartus II 软件

许可Quartus II软件

获取技术支持

第十八章:文档和其他资源

获取在线帮助

使用Quartus II 在线教程

其它Quartus II 软件文档

其他Altera文献

索引

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc