FPGA产生PWM、SPWM波

�

FPGA---PWM

v PWM是脉冲宽度调制(Pulse Width Modulation)的简称,它在自动控

制和计算机技术领域中都有广泛的应用。在电机控制、交流检测等实际

应用系统中,PWM 是整个系统的技术核心。因此,设计支持 PWM 输

出的芯片(或独立的电路功能模块)实用价值很大。

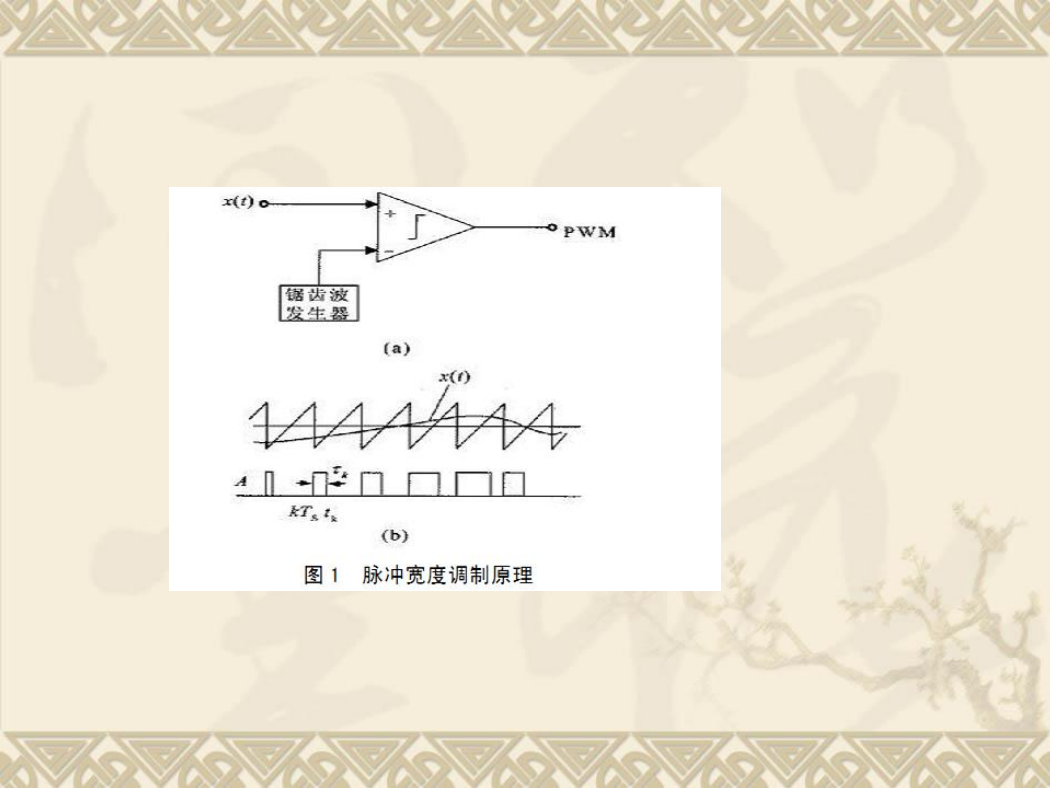

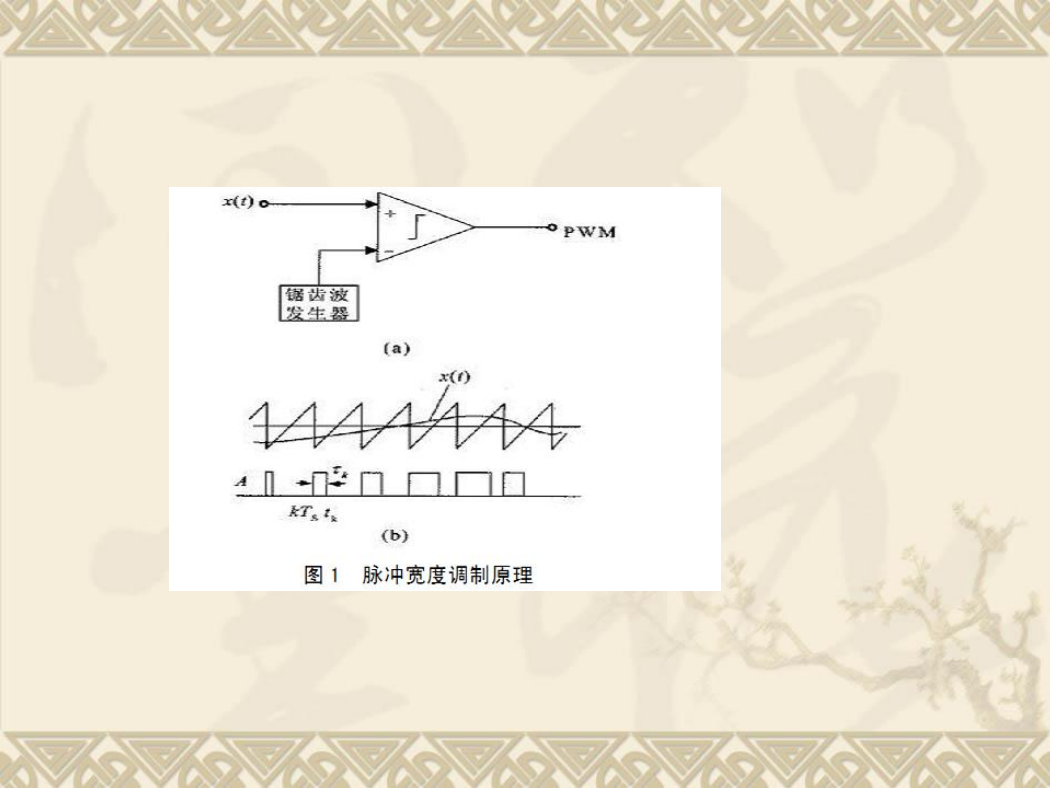

PWM调制原理

PWM 波通常由一列占空比不同的矩形脉冲构成,其占空比与信号的瞬时采样

值成比例。图 1 所示为脉冲宽度调制系统的原理框图和波形图。该系统有一个

比较器和一个周期为Ts的锯齿波发生器组成。语音信号如果大于锯齿波信号,

比较器输出正常数 A,否则输出 0。因此,从图 1 中可以看出,比较器输出一

列下降沿调制的脉冲宽度调制波。

�

�

PWM 技术最初是在无线电技术中用于信号的调制, 后来在低频大功率电路中得到

了很好的应用。 在直流伺服控制系统中,通过专用集成芯片或中小规模数字集成电

路构成的传统PWM 控制电路往往存在电路设计复杂、体积大、抗干扰能力差以及

设计困难、设计周期长等缺点,因此,PWM 控制电路的模块化、集成化已成为发

展趋势。 它不仅可以使系统体积减小、重量减轻且功耗降低,同时可使系统的可靠

性大大提高。随着电子技术的发展,特别是ASIC(专用集成电路)设计技术的日趋

完善,数字化的 EDA(电子设计自动化)工具给电子设计带来了巨大变革,在水声

和超声、电机控制等许多应用场合, 需要产生多路频率和脉冲宽度可调的PWM 波

形, 这可通过 FPGA 丰富的硬件资源和可以配置 I/O 引脚来实现。嵌入式系统中

FPGA的应用设计关键是系统软硬件功能的划分。

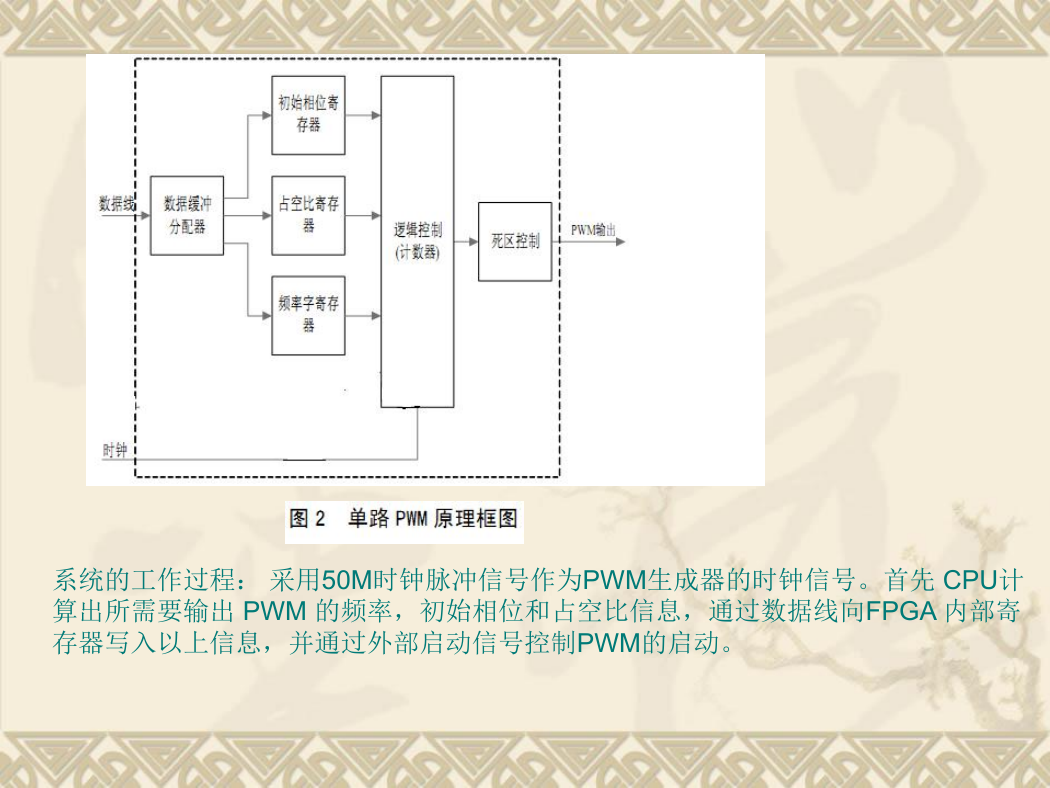

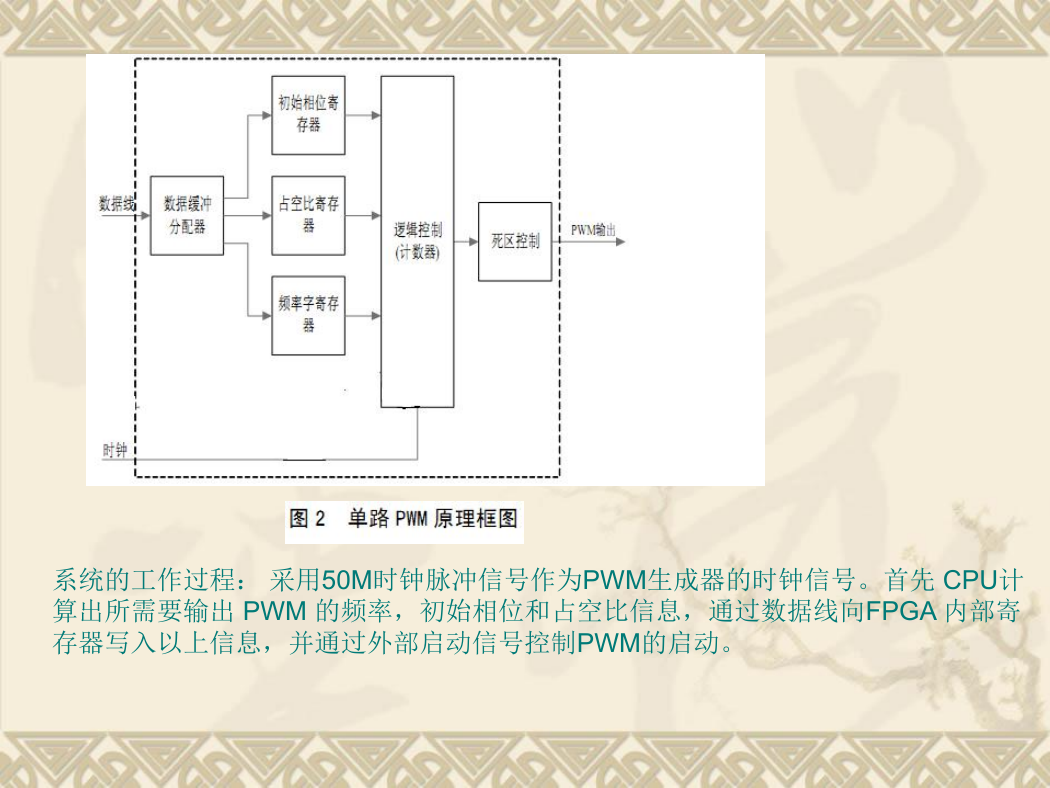

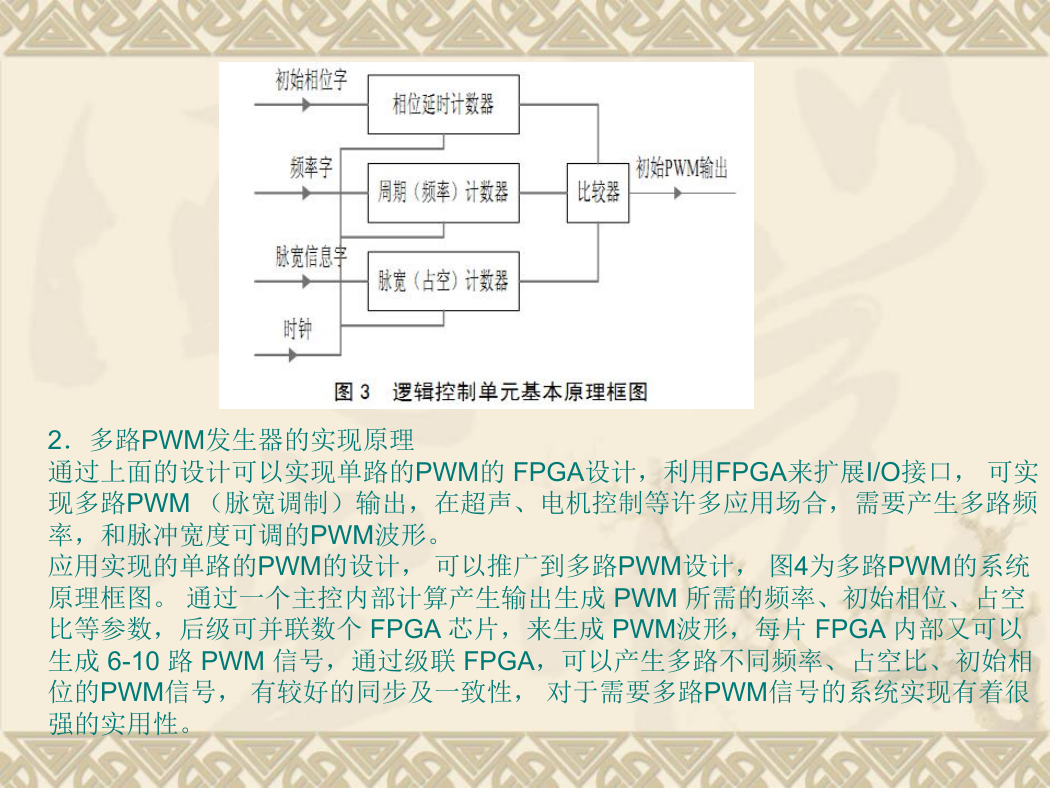

1.单路PWM发生器结构和原理

图2是实现的单路PWM硬件结构框图。 CPU通过数据线向FPGA写入定时常数控

制PWM的频率、初始相位和占空比,并通过外部启动信号控制PWM的启动。

�

系统的工作过程: 采用50M时钟脉冲信号作为PWM生成器的时钟信号。首先 CPU计

算出所需要输出 PWM 的频率,初始相位和占空比信息,通过数据线向FPGA 内部寄

存器写入以上信息,并通过外部启动信号控制PWM的启动。

�

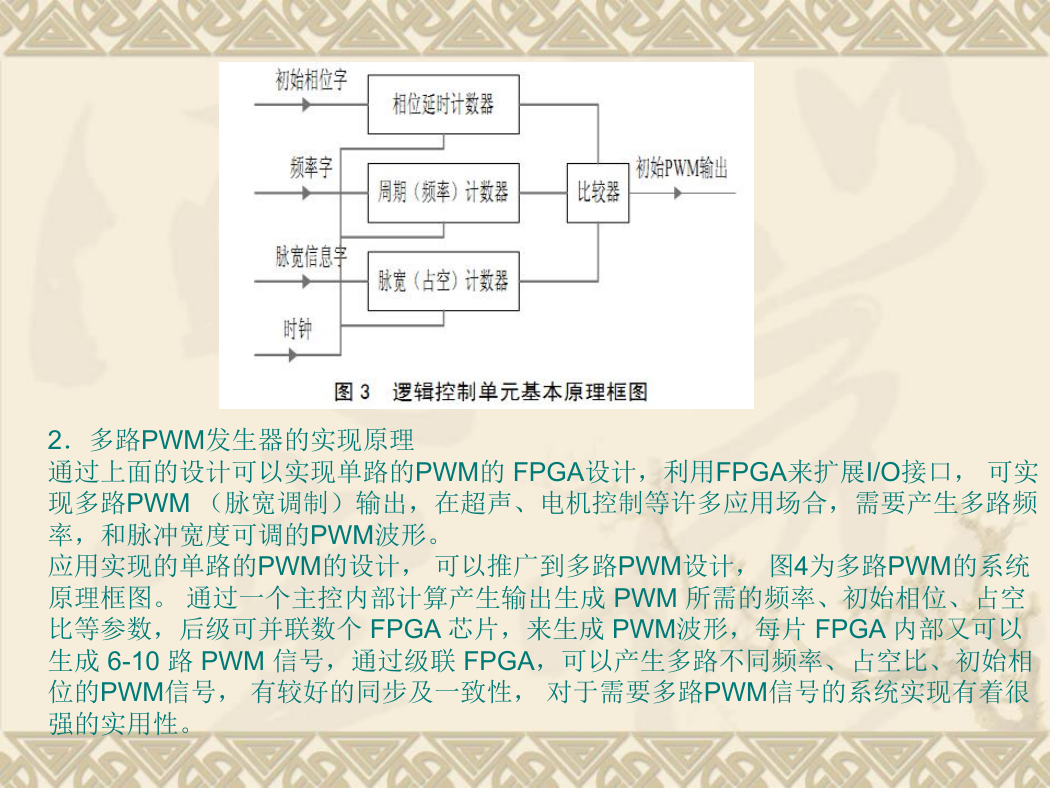

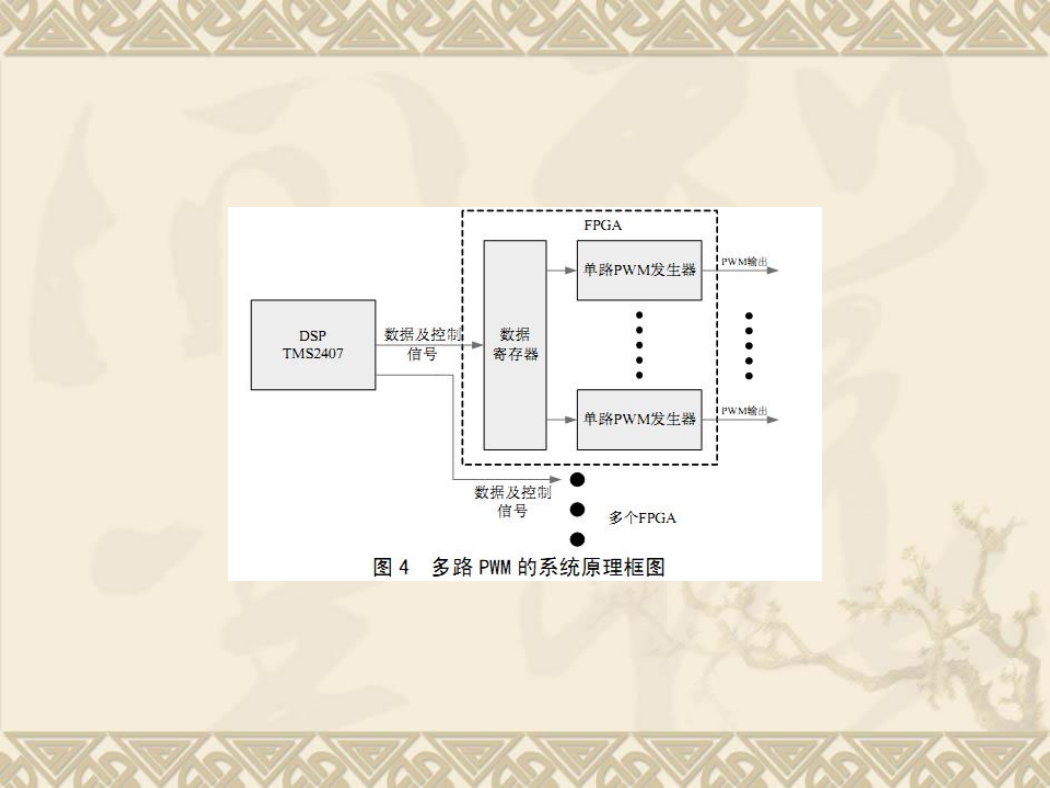

2.多路PWM发生器的实现原理

通过上面的设计可以实现单路的PWM的 FPGA设计,利用FPGA来扩展I/O接口, 可实

现多路PWM (脉宽调制)输出,在超声、电机控制等许多应用场合,需要产生多路频

率,和脉冲宽度可调的PWM波形。

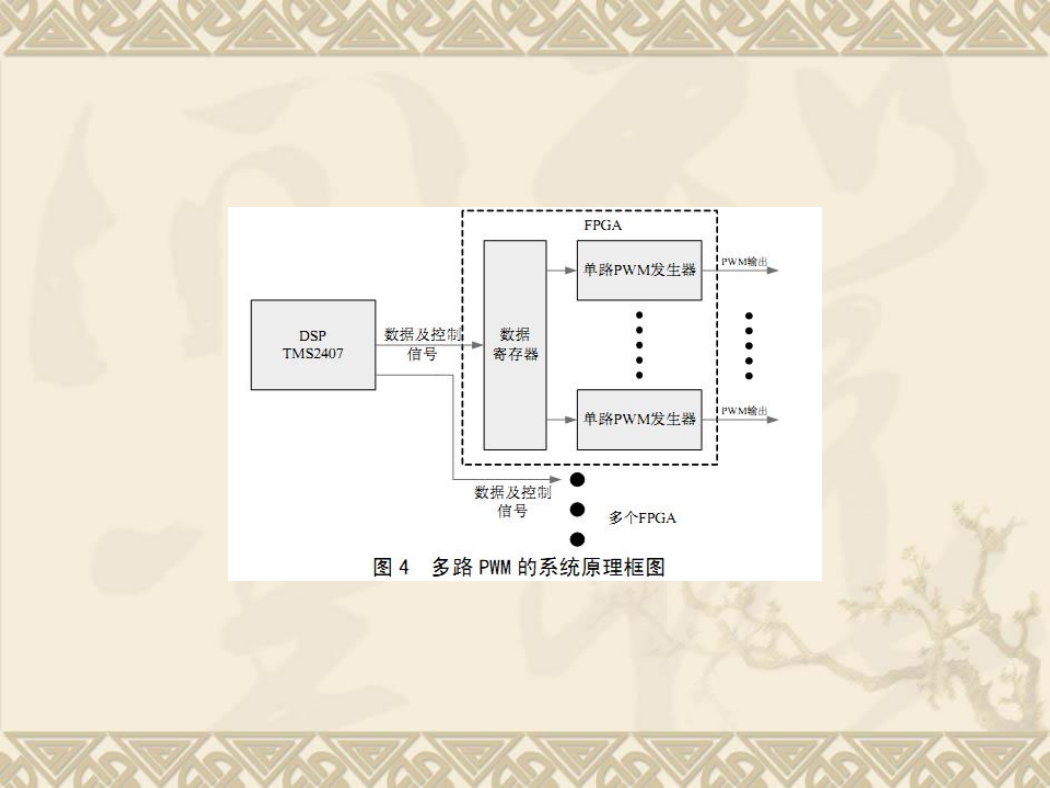

应用实现的单路的PWM的设计, 可以推广到多路PWM设计, 图4为多路PWM的系统

原理框图。 通过一个主控内部计算产生输出生成 PWM 所需的频率、初始相位、占空

比等参数,后级可并联数个 FPGA 芯片,来生成 PWM波形,每片 FPGA 内部又可以

生成 6-10 路 PWM 信号,通过级联 FPGA,可以产生多路不同频率、占空比、初始相

位的PWM信号, 有较好的同步及一致性, 对于需要多路PWM信号的系统实现有着很

强的实用性。

�

�

FPGA---SPWM

v 正弦脉宽调制(SPWM)技术在交流调速系统中得到广泛应用,

但SPWM的波形生成是应用中一个难点,目前形成SPWM的

方法有:(1)由分立元件构成,结构简单,但可靠性和精度均不能

满足要求;(2)采用计算机计算或查表方式,省却了硬件电路,但

CPU负担很重; (3)采用专用集成电路,如SLE4520、SA4828

等,但其功能固定,可扩展性差;(4)采用FPGA(现场可编门阵

列),具有速度快、精度高且可以在线编程修改等优点,是一种

较好的方案。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc