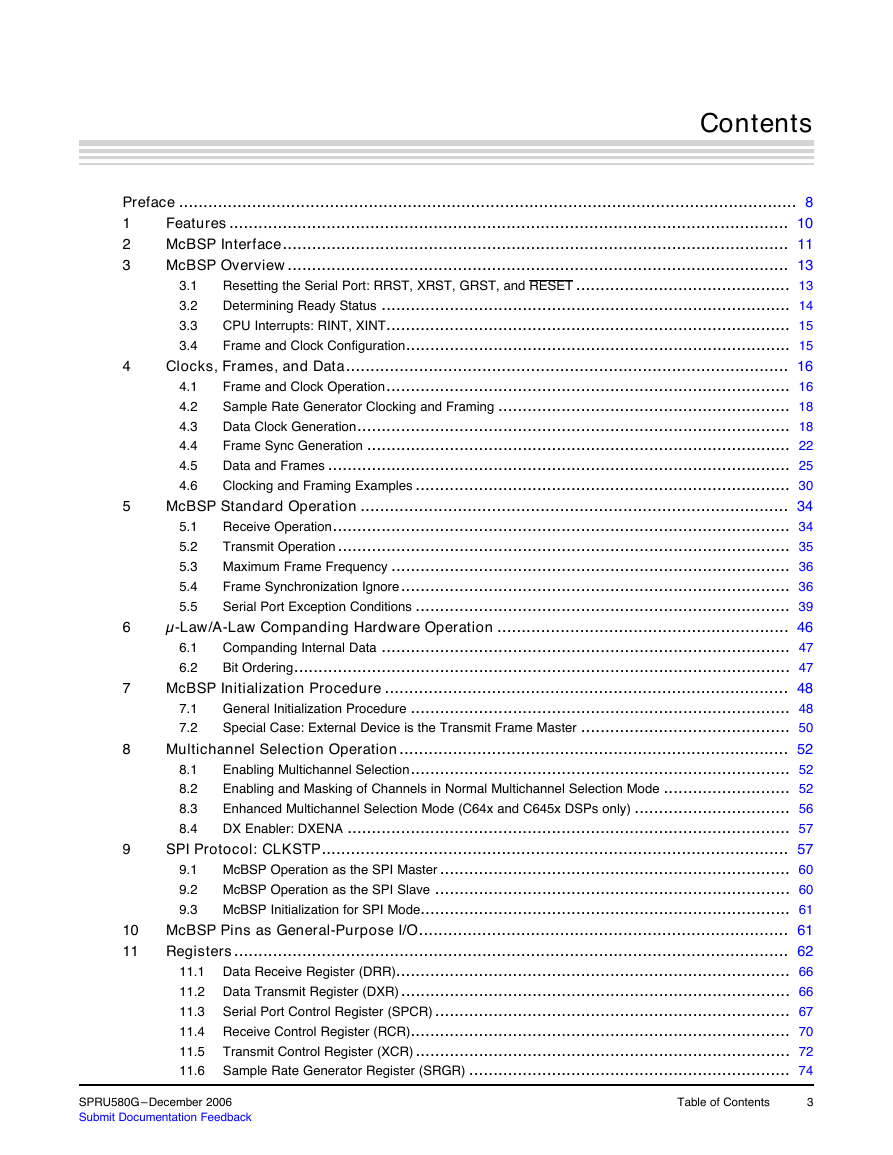

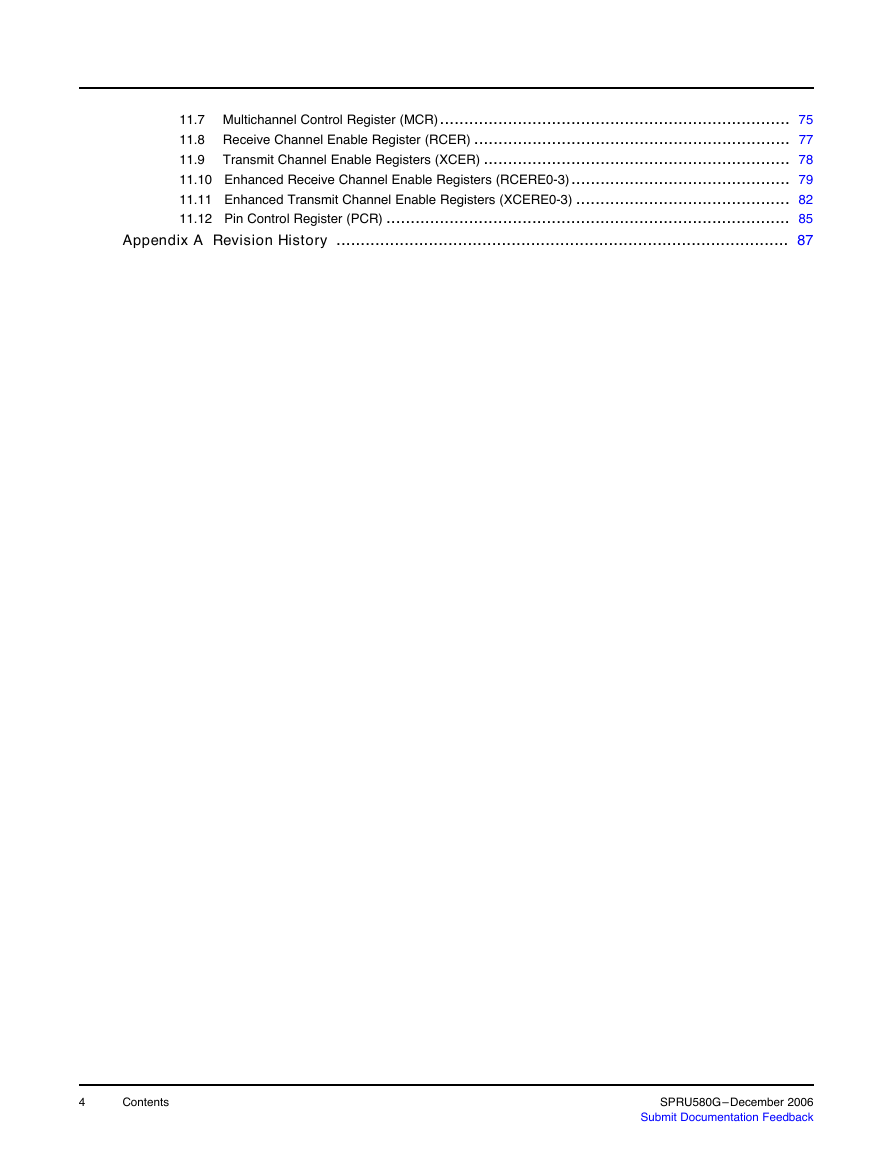

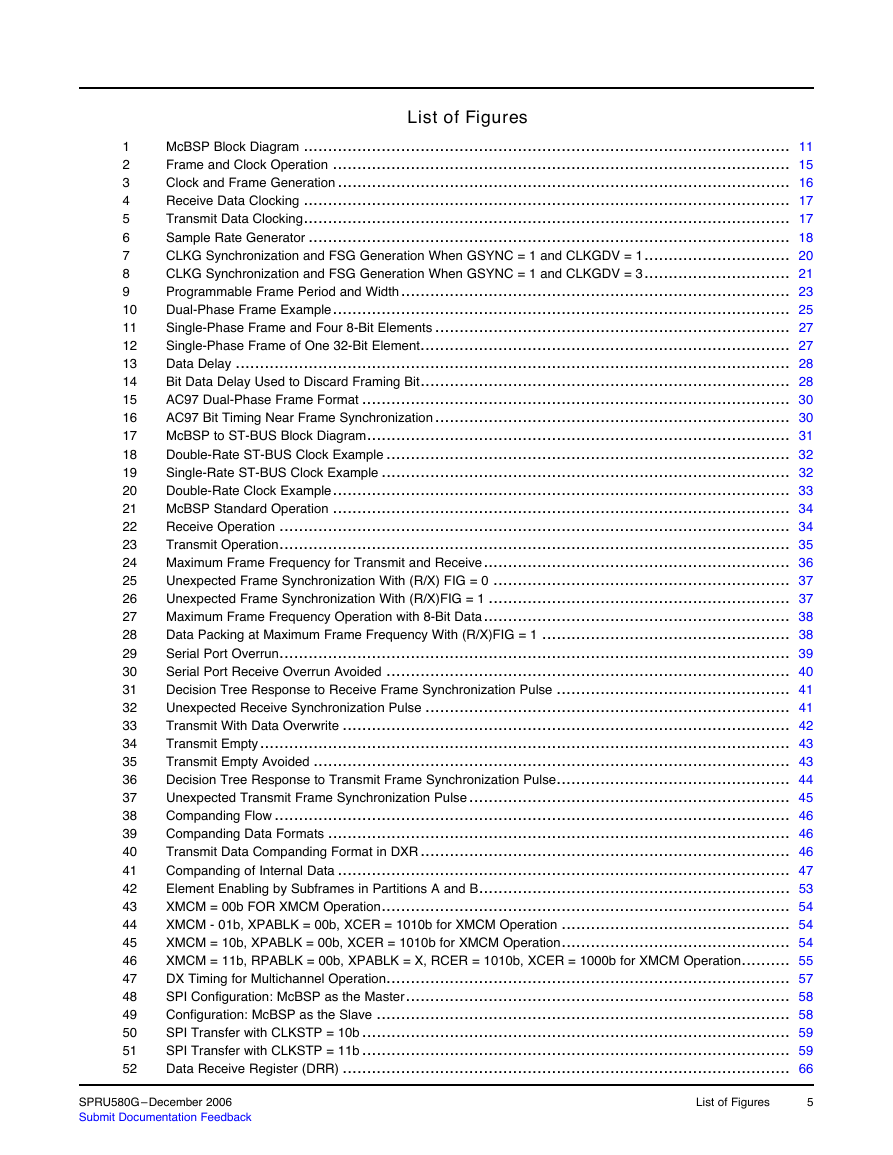

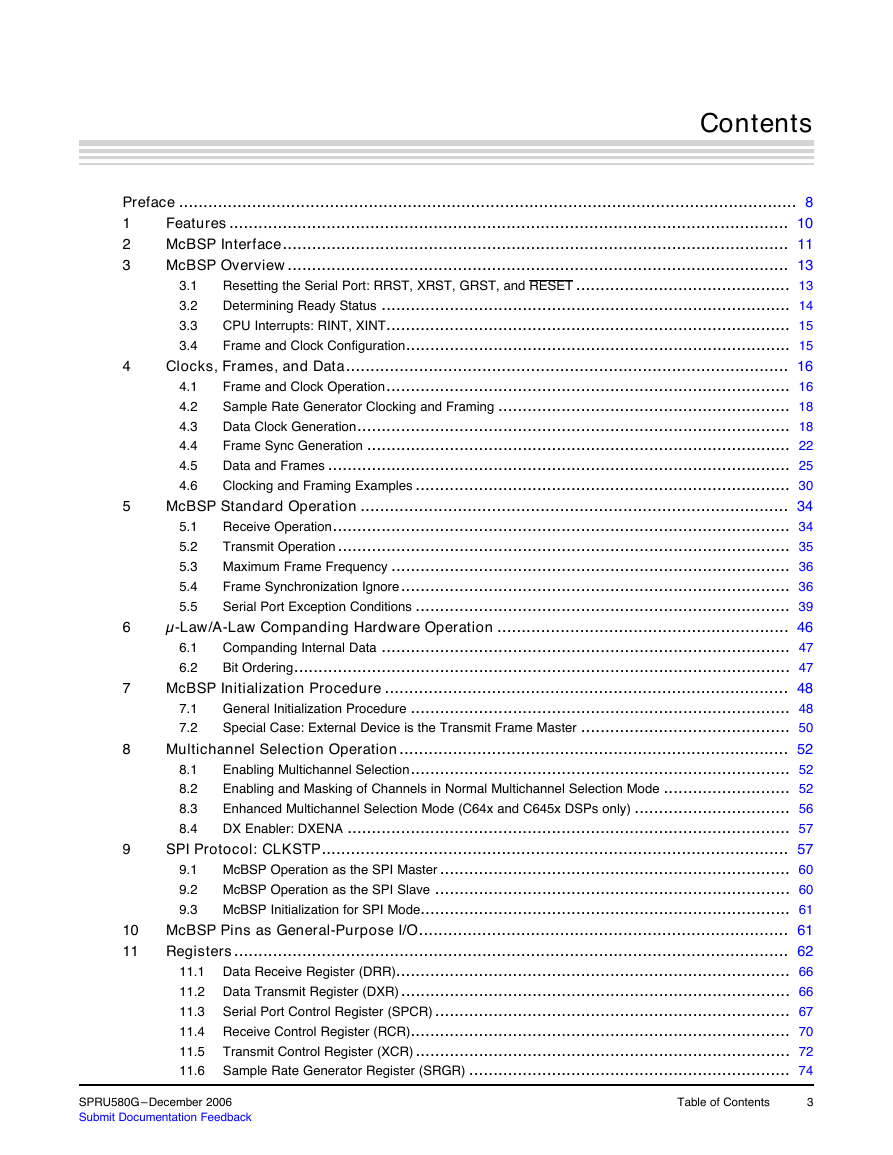

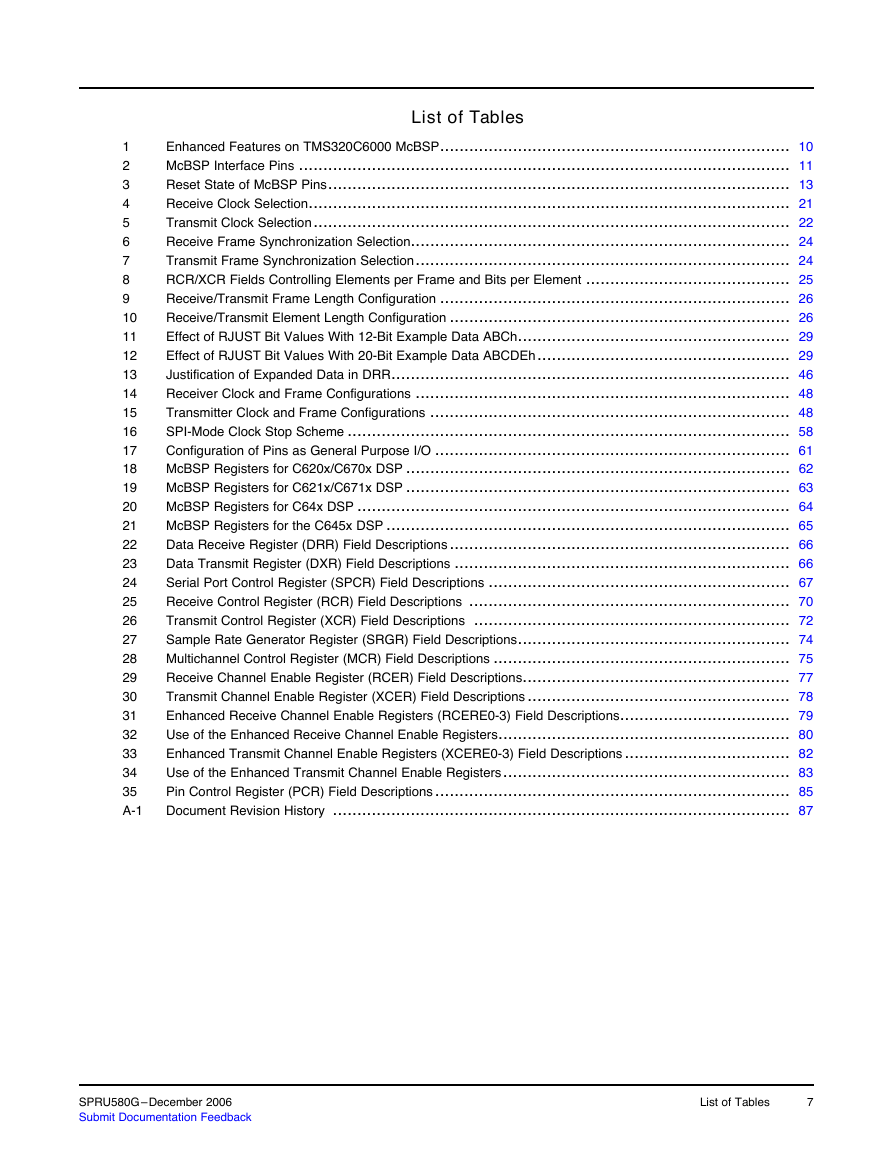

Table of Contents

Preface

1 Features

2 McBSP Interface

3 McBSP Overview

3.1 Resetting the Serial Port: RRST, XRST, GRST, and RESET

3.2 Determining Ready Status

3.2.1 Receive Ready Status: REVT, RINT, and RRDY

3.2.2 Transmit Ready Status: XEVT, XINT, and XRDY

3.3 CPU Interrupts: RINT, XINT

3.4 Frame and Clock Configuration

4 Clocks, Frames, and Data

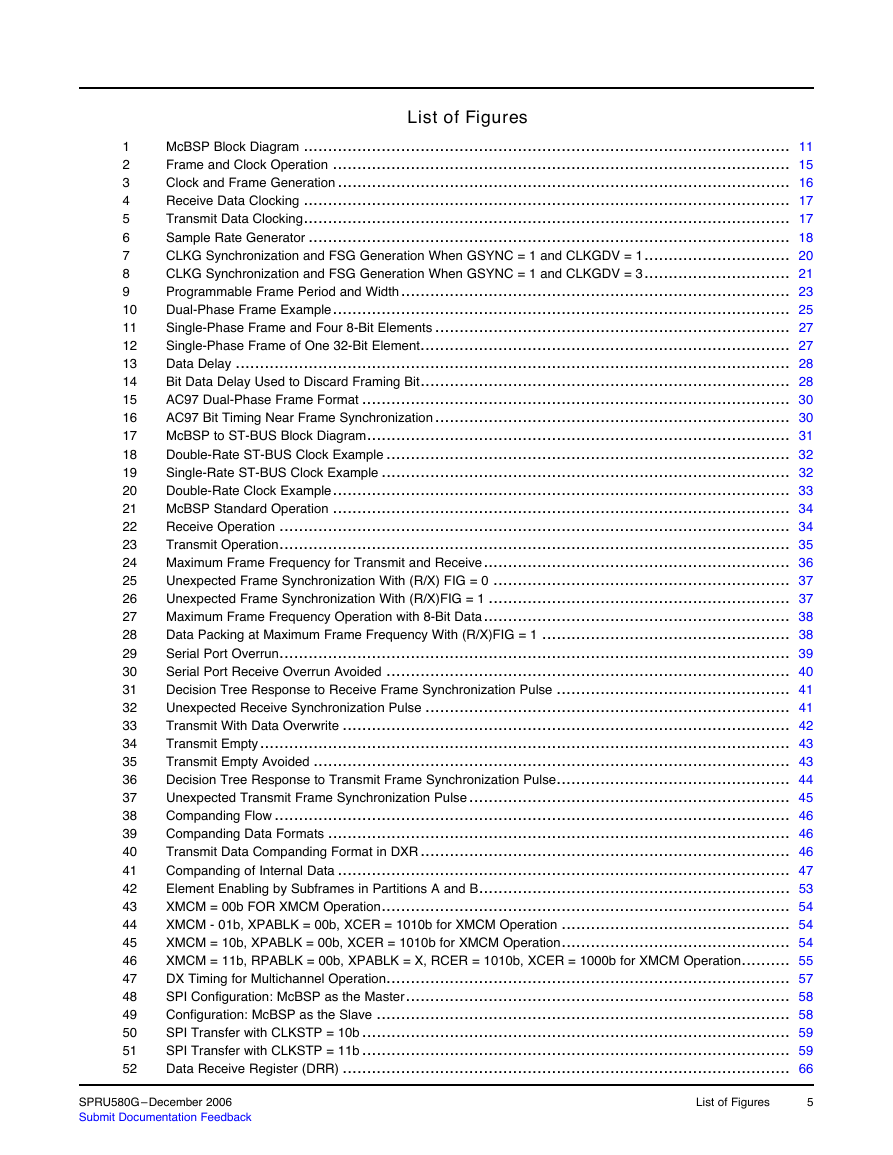

4.1 Frame and Clock Operation

4.2 Sample Rate Generator Clocking and Framing

4.3 Data Clock Generation

4.3.1 Input Clock Source Mode: CLKSM

4.3.2 Sample Rate Generator Data Bit Clock Rate: CLKGDV

4.3.3 Bit Clock Polarity: CLKSP

4.3.4 Bit Clock and Frame Synchronization

4.3.5 Digital Loopback Mode: DLB

4.3.6 Receive Clock Selection: DLB, CLKRM

4.3.7 Transmit Clock Selection: CLKXM

4.3.8 Stopping Clocks

4.4 Frame Sync Generation

4.4.1 Frame Period (FPER) and Frame Width (FWID)

4.4.2 Receive Frame Sync Selection: DLB, FSRM, GSYNC

4.4.3 Transmit Frame Sync Selection: FSXM, FSGM

4.4.4 Frame Detection for Initialization

4.5 Data and Frames

4.5.1 Frame Synchronization Phases

4.5.2 Frame Length: RFRLEN1/2, XFRLEN1/2

4.5.3 Element Length: RWDLEN1/2, XWDLEN1/2

4.5.4 Data Packing using Frame Length and Element Length

4.5.5 Data Delay: RDATDLY, XDATDLY

4.5.6 Receive Data Justification and Sign Extension: RJUST

4.5.7 32-Bit Bit Reversal: RWDREVRS, XWDREVRS

4.6 Clocking and Framing Examples

4.6.1 Multiphase Frame Example: AC97

4.6.2 Double-Rate ST-BUS Clock

4.6.3 Single-Rate ST-BUS Clock

4.6.4 Double-Rate Clock

5 McBSP Standard Operation

5.1 Receive Operation

5.2 Transmit Operation

5.3 Maximum Frame Frequency

5.4 Frame Synchronization Ignore

5.4.1 Frame Sync Ignore and Unexpected Frame Sync Pulses

5.4.2 Data Packing using Frame Sync Ignore Bits

5.5 Serial Port Exception Conditions

5.5.1 Receive Overrun: RFULL

5.5.2 Unexpected Receive Frame Synchronization: RSYNCERR

5.5.3 Transmit With Data Overwrite

5.5.4 Transmit Empty: XEMPTY

5.5.5 Unexpected Transmit Frame Synchronization: XSYNCERR

6 µ-Law/A-Law Companding Hardware Operation

6.1 Companding Internal Data

6.2 Bit Ordering

7 McBSP Initialization Procedure

7.1 General Initialization Procedure

7.2 Special Case: External Device is the Transmit Frame Master

8 Multichannel Selection Operation

8.1 Enabling Multichannel Selection

8.2 Enabling and Masking of Channels in Normal Multichannel Selection Mode

8.2.1 Changing Element Selection

8.2.2 End-of-Subframe Interrupt

8.3 Enhanced Multichannel Selection Mode (C64x and C645x DSPs only)

8.4 DX Enabler: DXENA

9 SPI Protocol: CLKSTP

9.1 McBSP Operation as the SPI Master

9.2 McBSP Operation as the SPI Slave

9.3 McBSP Initialization for SPI Mode

10 McBSP Pins as General-Purpose I/O

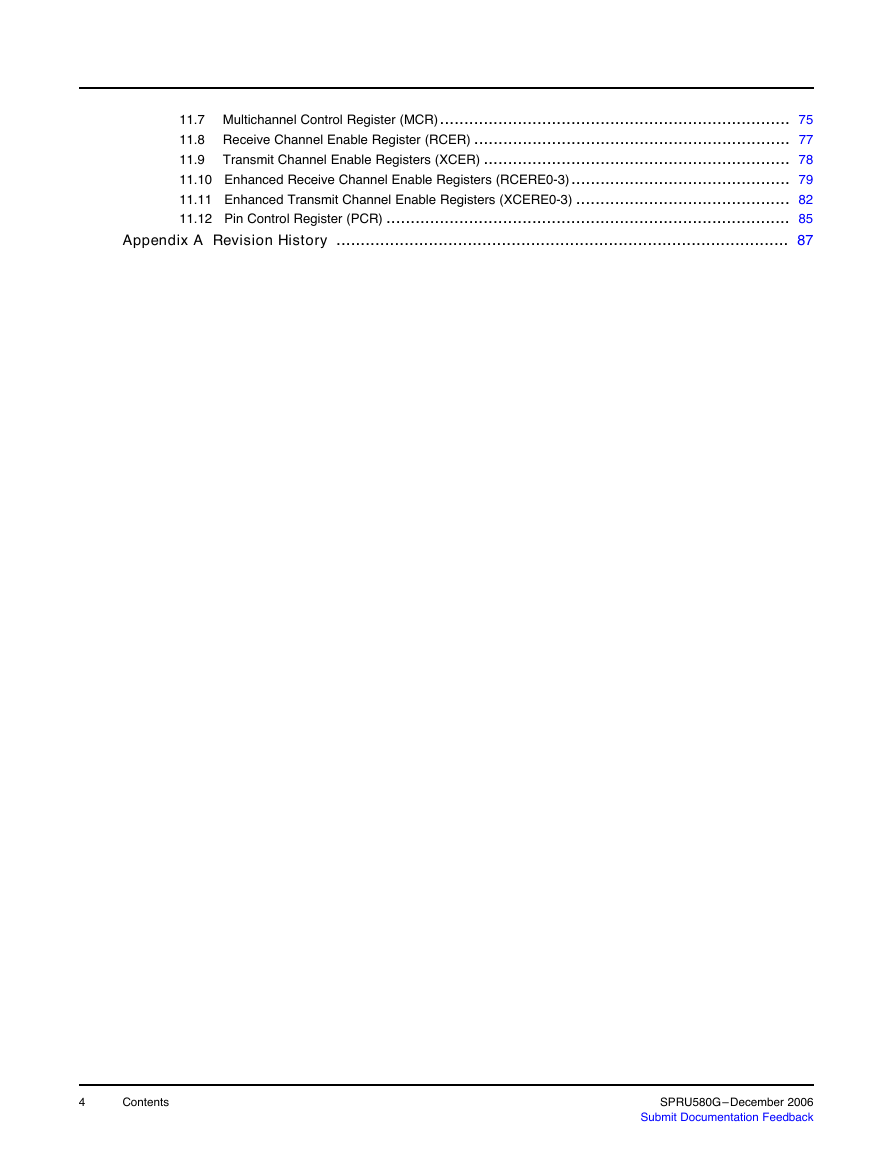

11 Registers

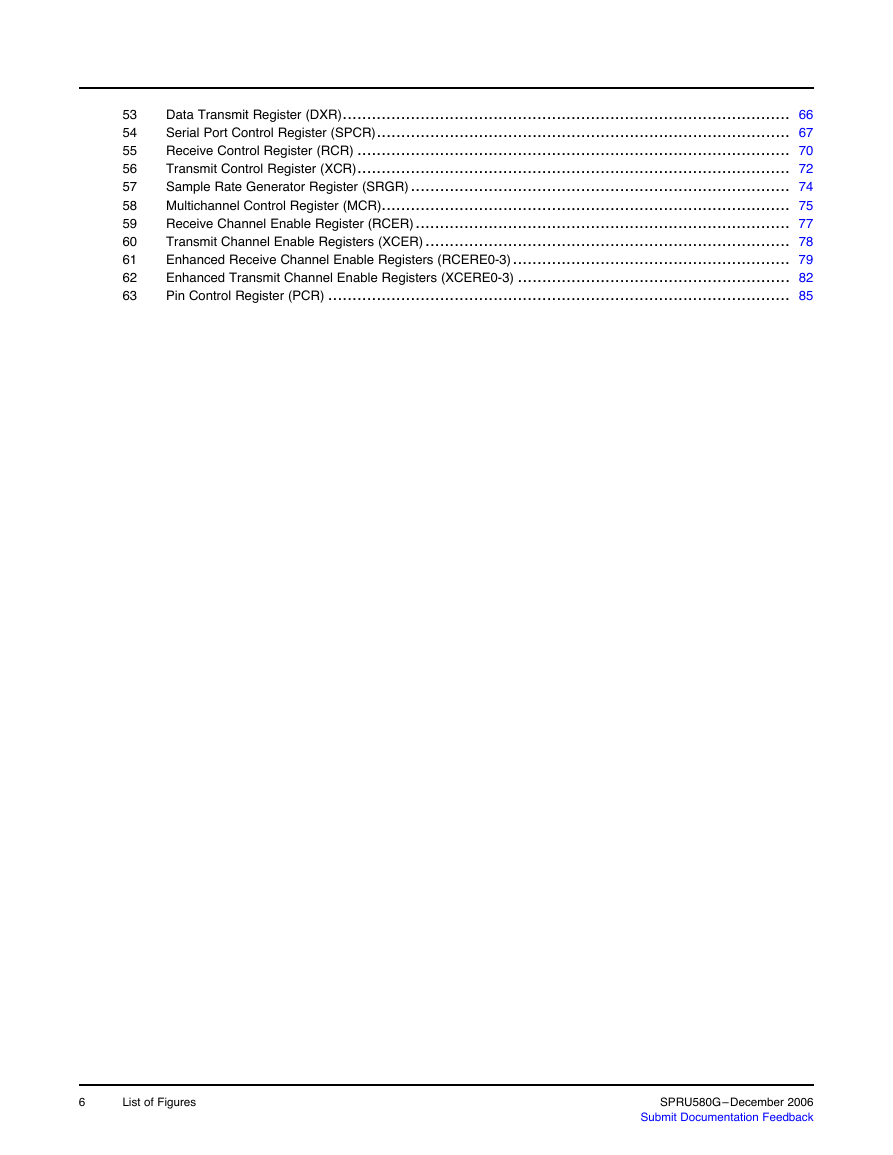

11.1 Data Receive Register (DRR)

11.2 Data Transmit Register (DXR)

11.3 Serial Port Control Register (SPCR)

11.4 Receive Control Register (RCR)

11.5 Transmit Control Register (XCR)

11.6 Sample Rate Generator Register (SRGR)

11.7 Multichannel Control Register (MCR)

11.8 Receive Channel Enable Register (RCER)

11.9 Transmit Channel Enable Registers (XCER)

11.10 Enhanced Receive Channel Enable Registers (RCERE0-3)

11.10.1 RCEREs Used in the Receive Multichannel Selection Mode

11.11 Enhanced Transmit Channel Enable Registers (XCERE0-3)

11.11.1 XCEREs Used in a Transmit Multichannel Selection Mode

11.12 Pin Control Register (PCR)

Appendix A Revision History

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc