FPGA MicroBlaze 配置与程序烧录指导

前言

MicroBlaze 嵌入式软核是一个被 Xilinx 公司优化过的可以嵌入在 FPGA 中的 RISC 处

理器软核,具有运行速度快、占用资源少、可配置性强等优点,广泛应用于通信、军事、高

端消费市场等领域。本指导手册旨在指导在 FPGA 工程中配置 microblaze 软核并生成 mcs

文件烧录到 FPGA 中成功固化运行。

硬件平台:spartan-6 AX545

软件平台:Xilinx Platform Stdio + SDK

实验项目:硬件 microblaze 配置 + VGA project

�

目录

目录

1. 硬件配置 ....................................................................................................................................... 3

2. 软核配置 ..................................................................................................................................... 14

3. SDK 编程 ....................................................................................................................................... 23

4. 程序 flash 固化 ............................................................................................................................33

4.1 生成比特流文件............................................................................................................... 34

4.2 生成 SPI FLASH 的 MCS 文件 .........................................................................................35

4.3 下载 MCS 文件到 SPI FLASH ...........................................................................................38

�

1. 硬件配置

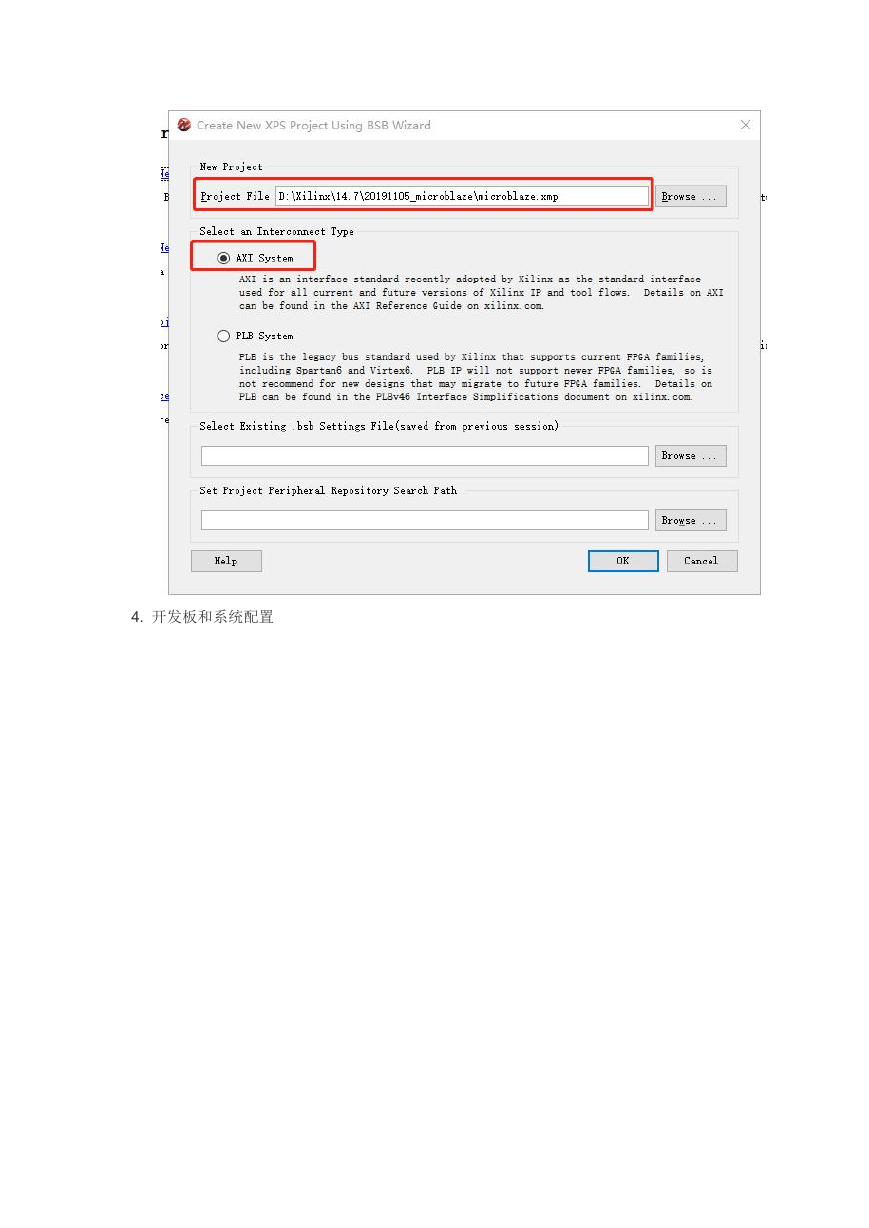

1. 打开 ISE 14.7 中 Xlinx Platform Studio

2. 打开工程向导 Create New Project Using Base System Builder

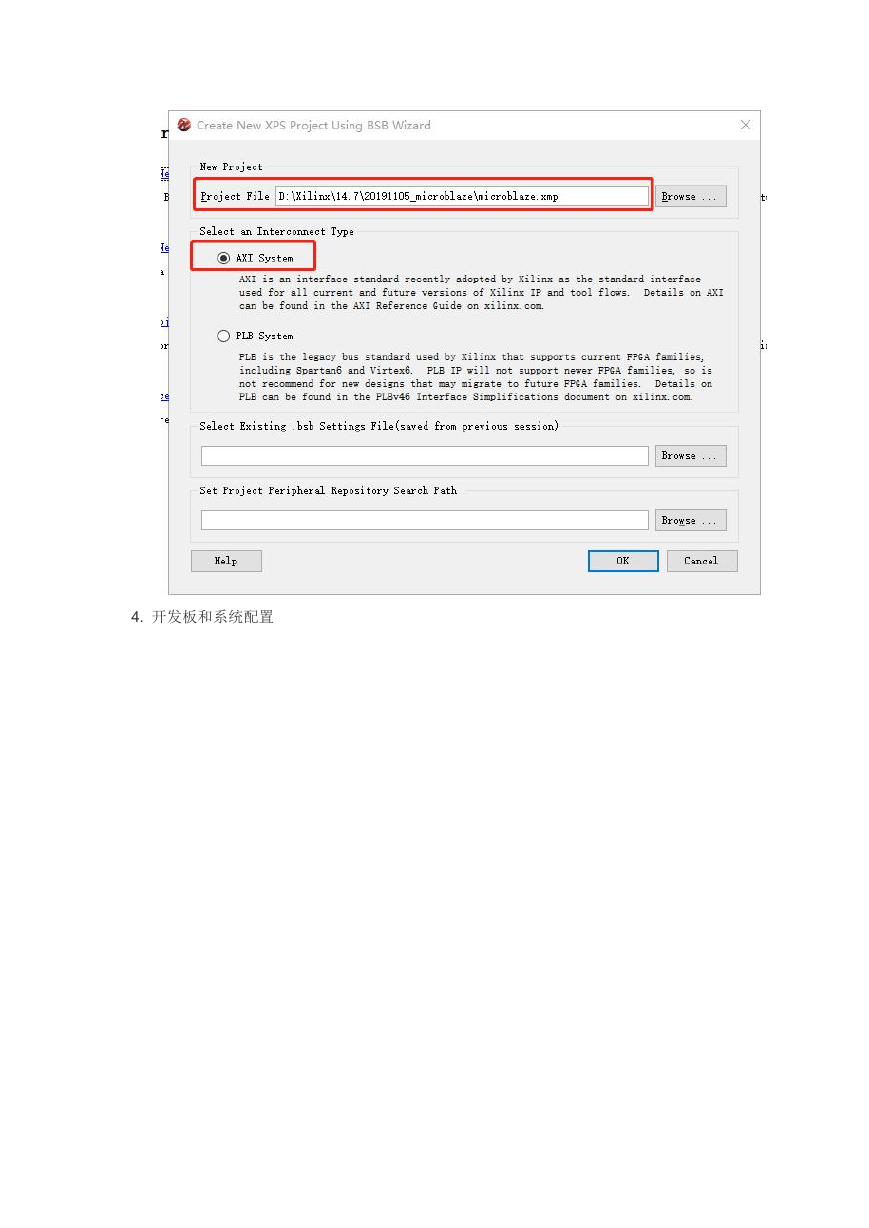

3. 配置工程路径和总线类型

�

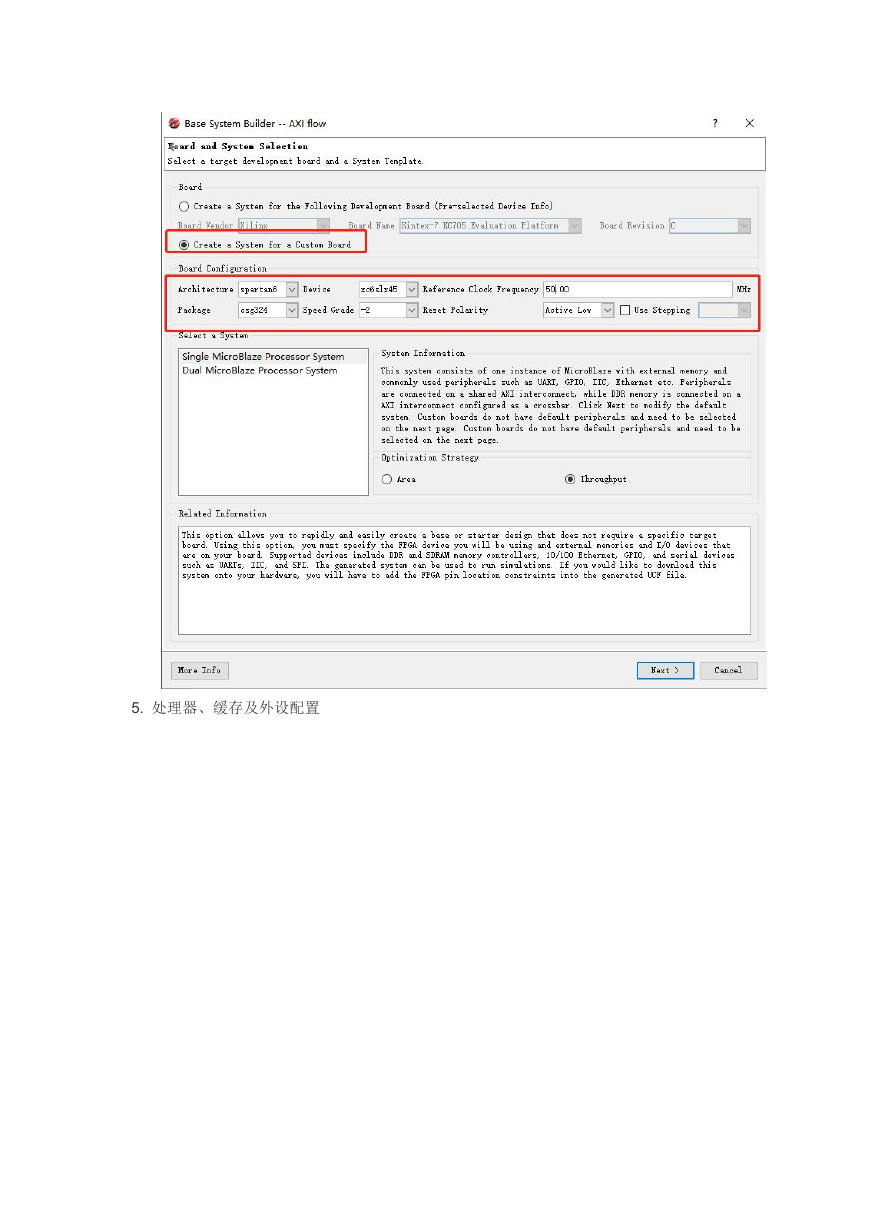

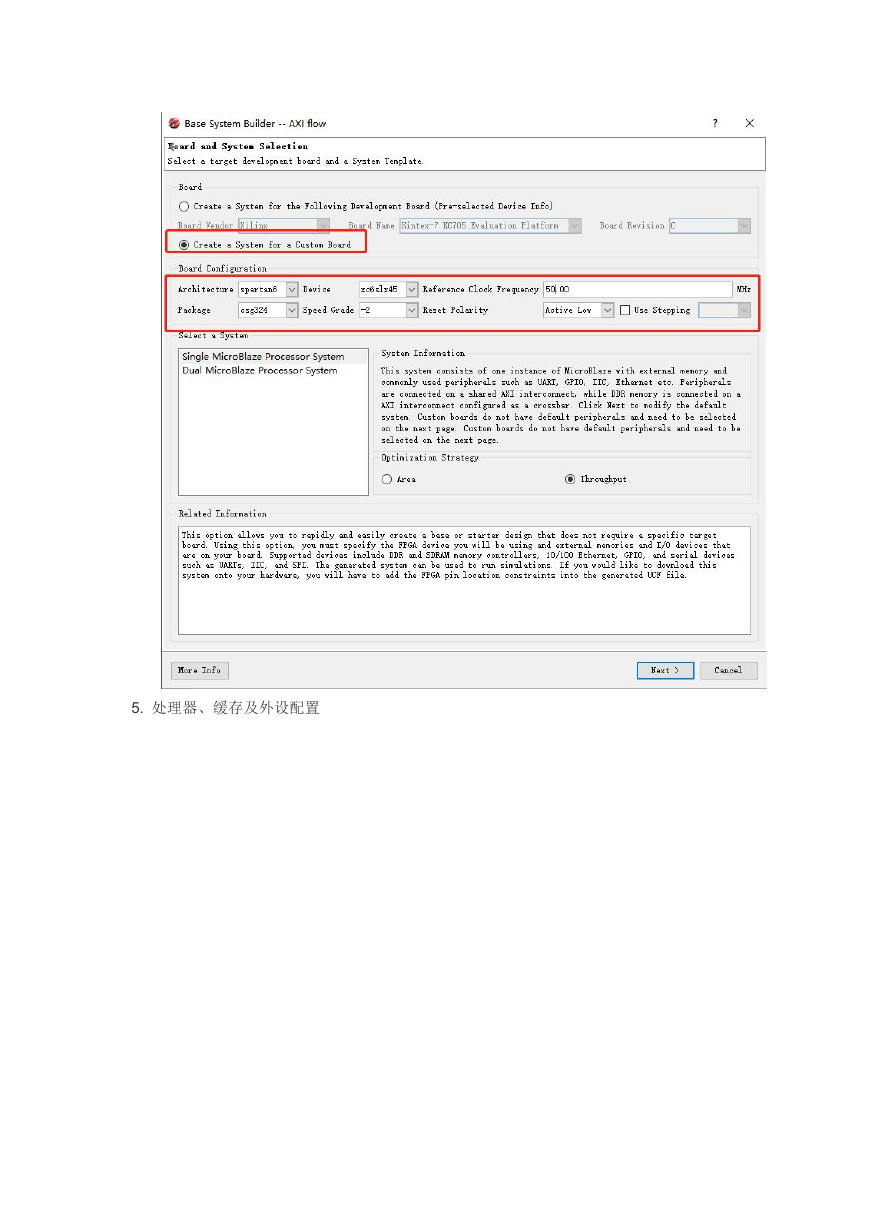

4. 开发板和系统配置

�

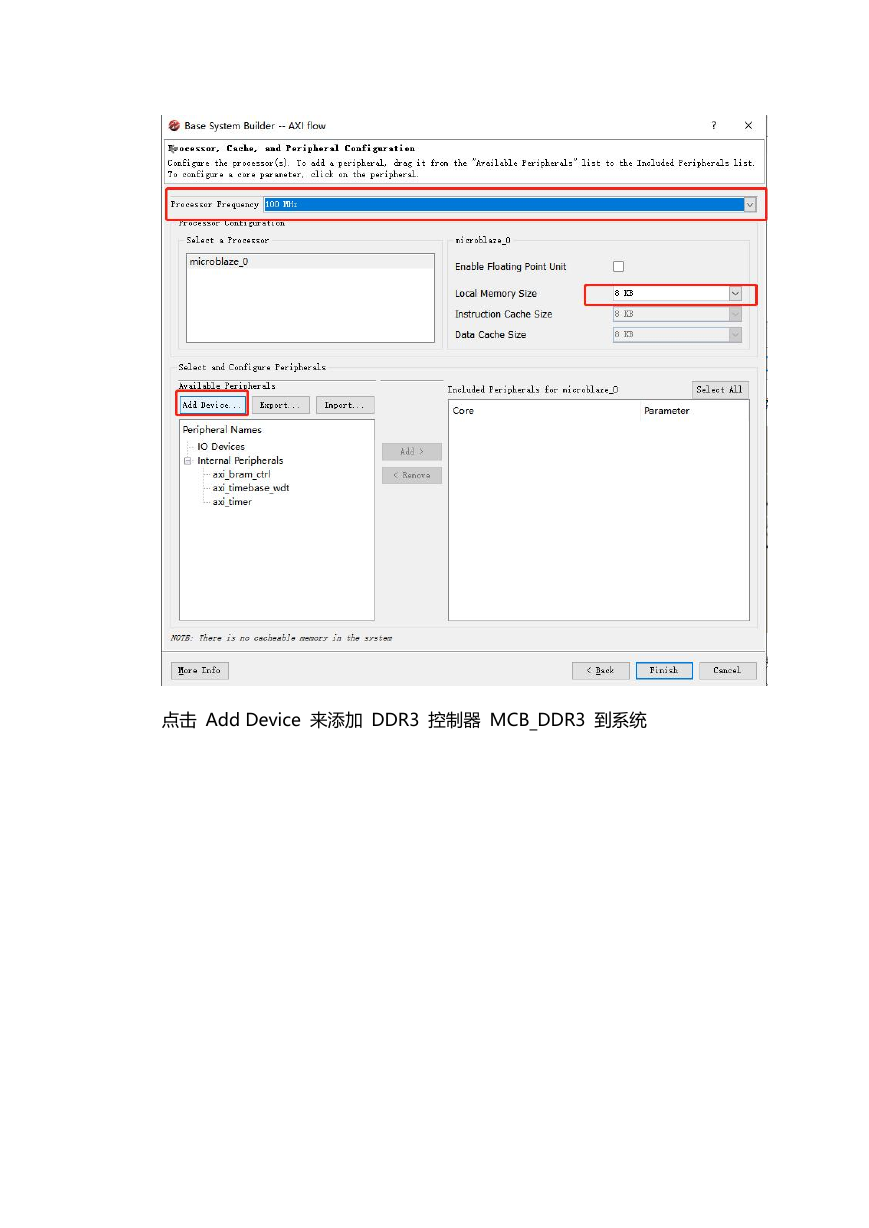

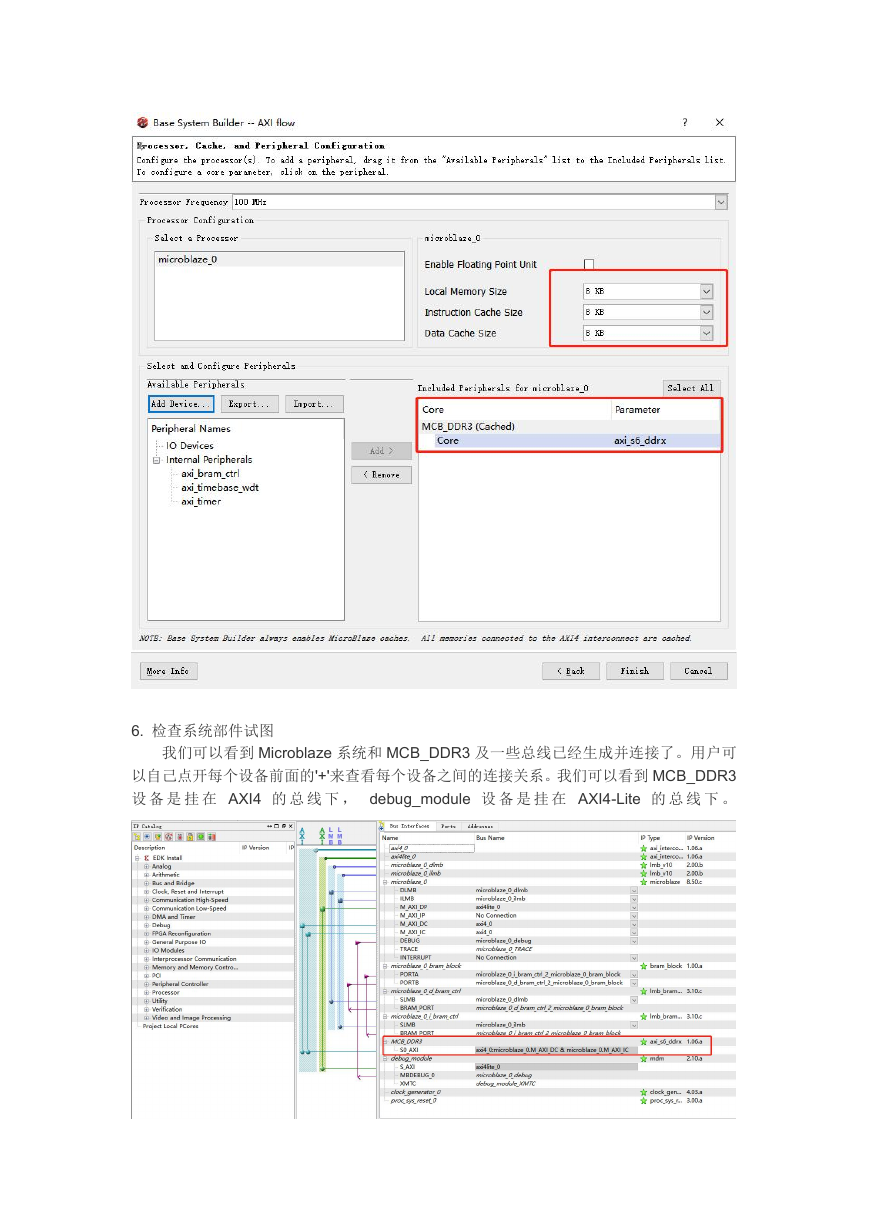

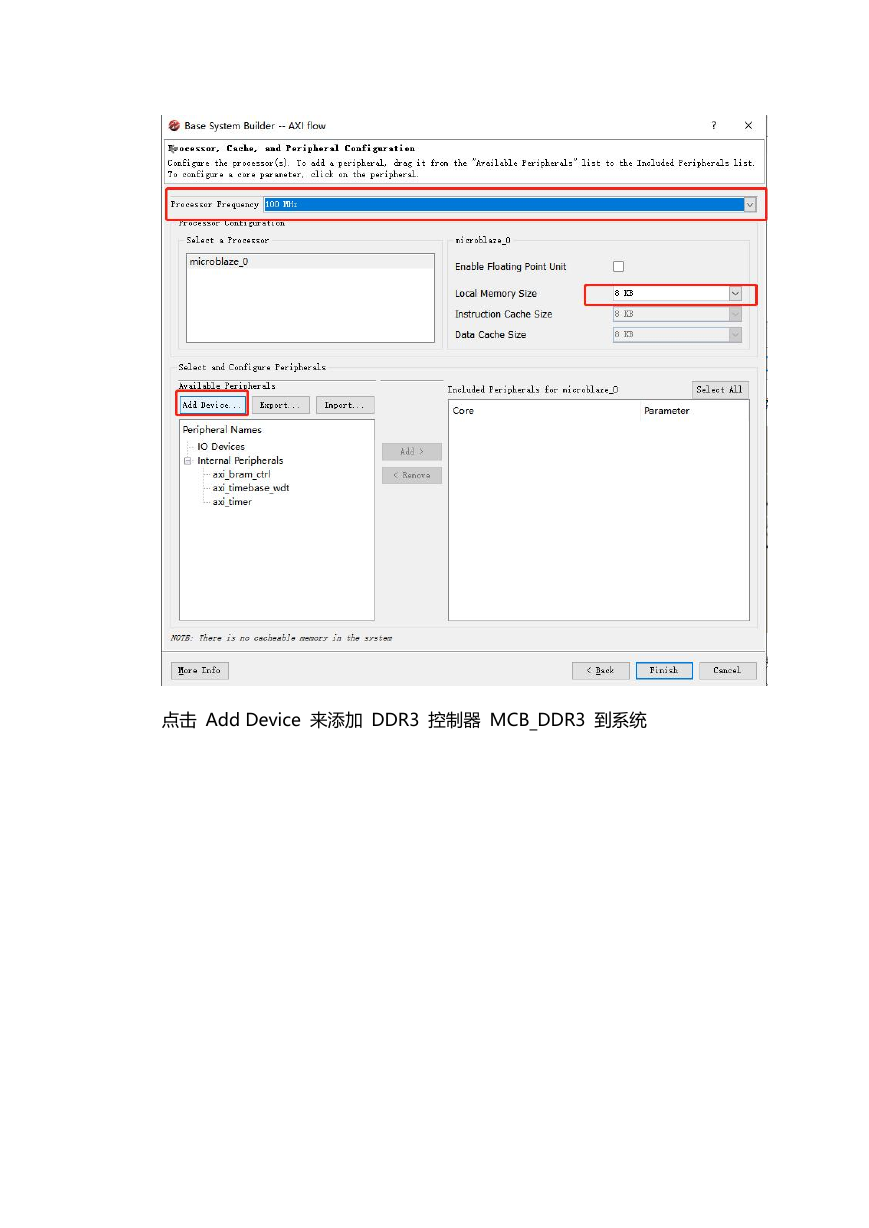

5. 处理器、缓存及外设配置

�

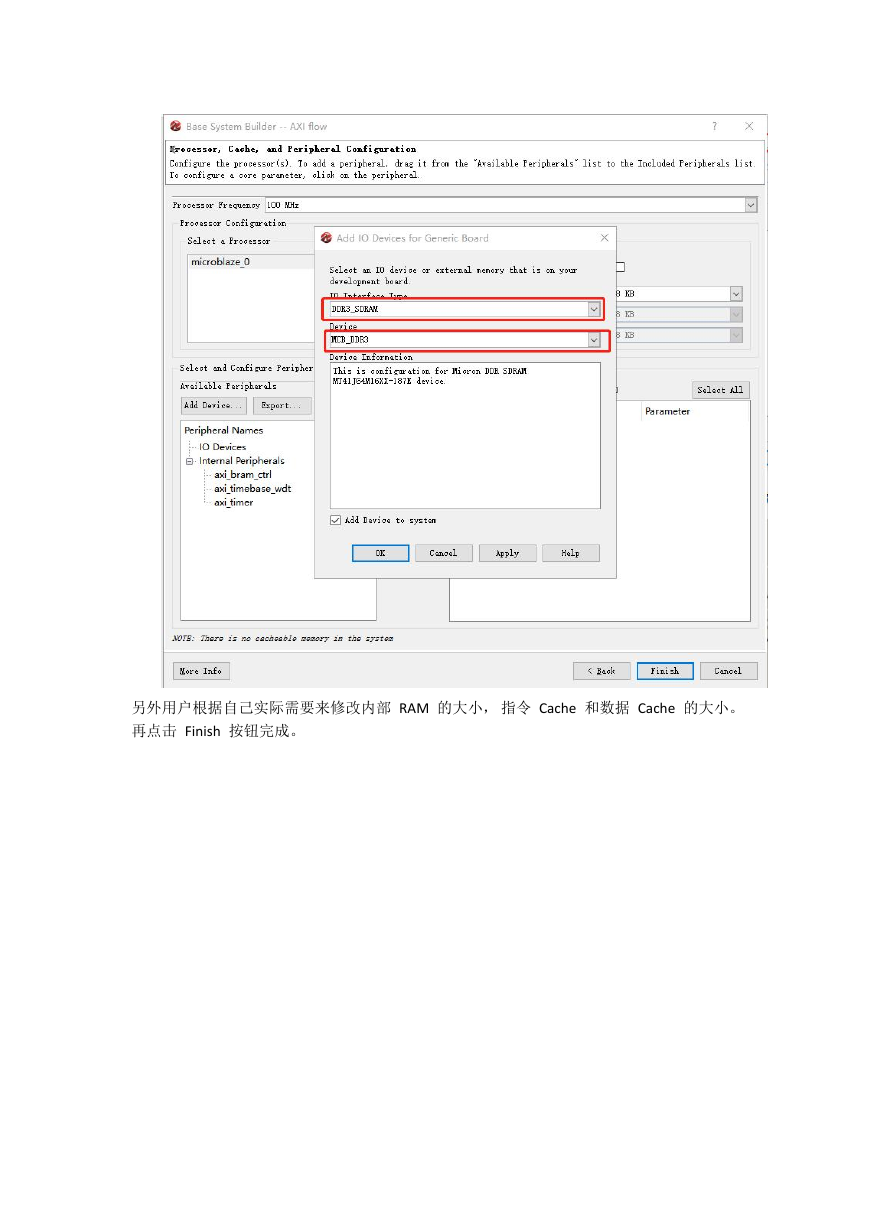

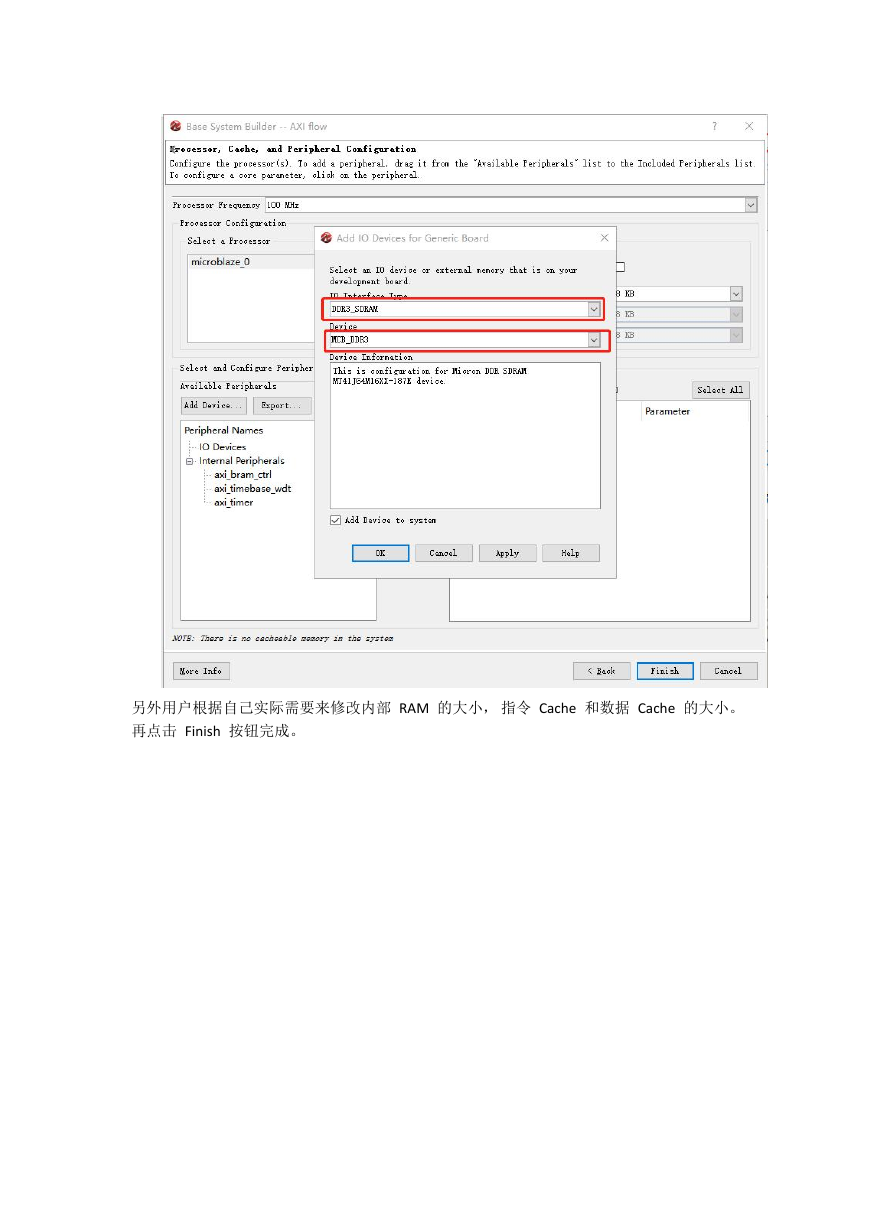

点击 Add Device 来添加 DDR3 控制器 MCB_DDR3 到系统

�

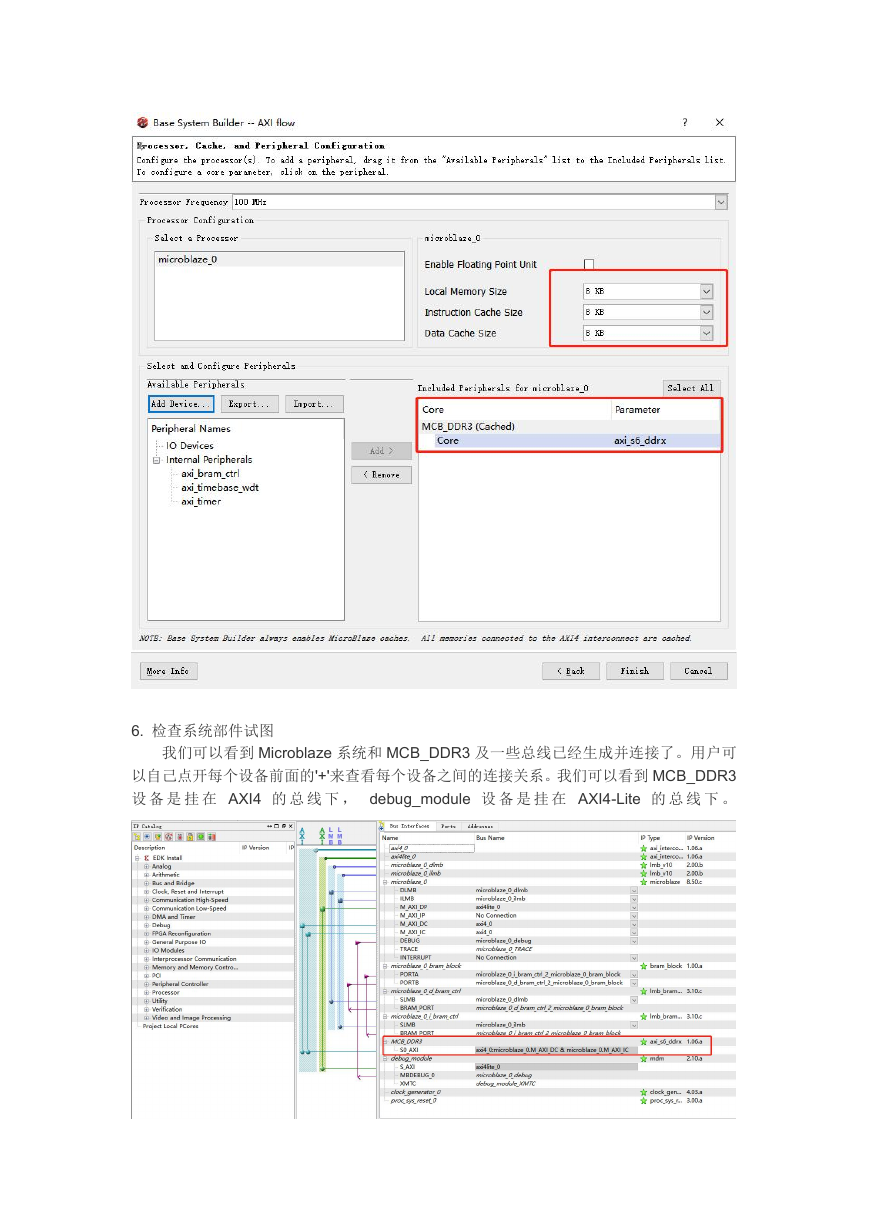

另外用户根据自己实际需要来修改内部 RAM 的大小, 指令 Cache 和数据 Cache 的大小。

再点击 Finish 按钮完成。

�

6. 检查系统部件试图

我们可以看到 Microblaze 系统和 MCB_DDR3 及一些总线已经生成并连接了。用户可

以自己点开每个设备前面的'+'来查看每个设备之间的连接关系。我们可以看到 MCB_DDR3

设 备 是 挂 在 AXI4 的 总 线 下 , debug_module 设 备 是 挂 在 AXI4-Lite 的 总 线 下 。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc