Flash and OTP Registers.pdf

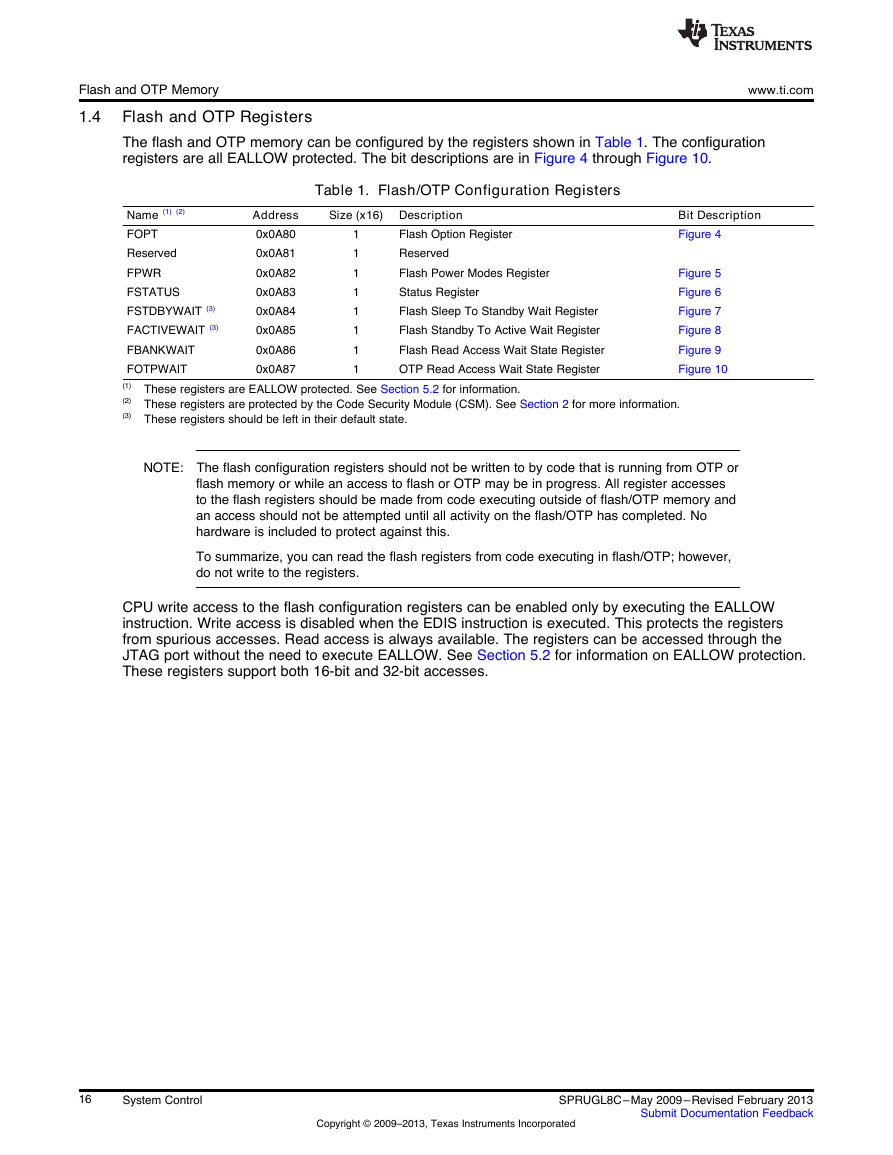

Flash and OTP Registers

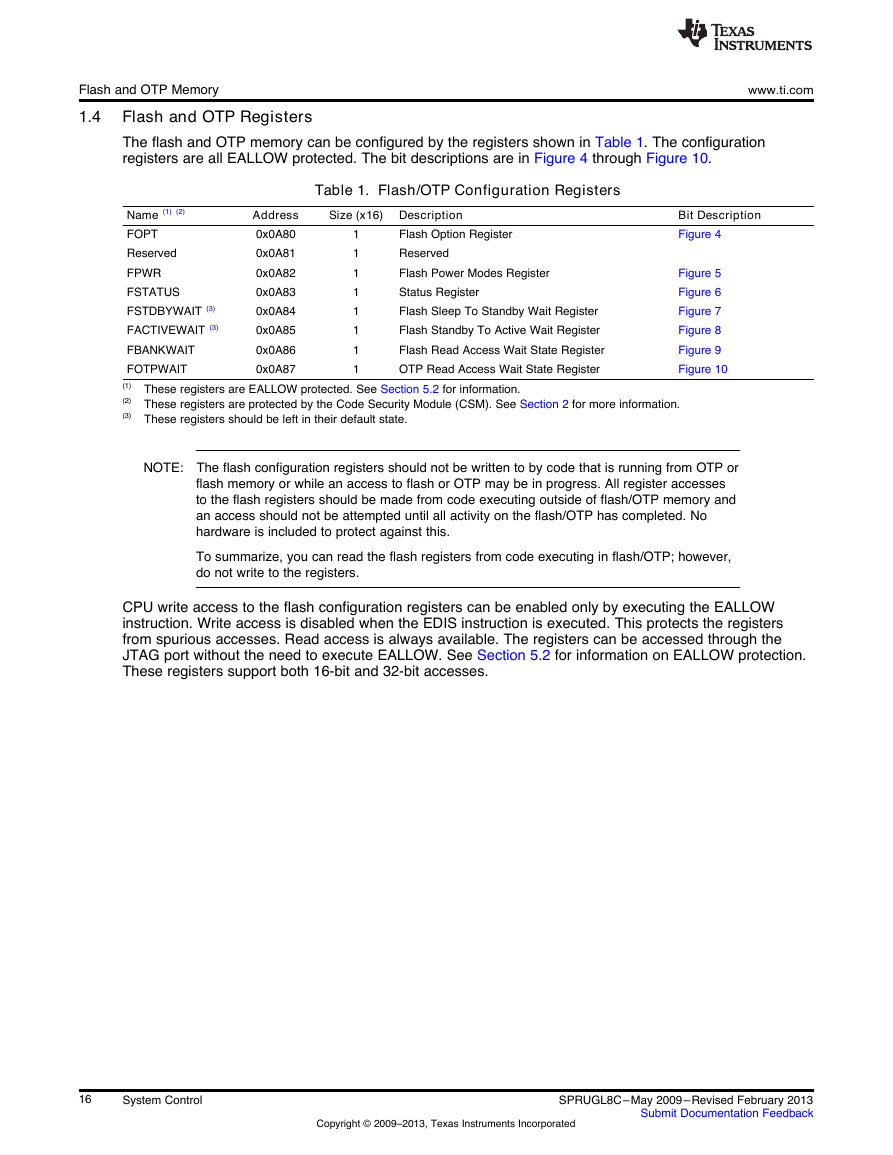

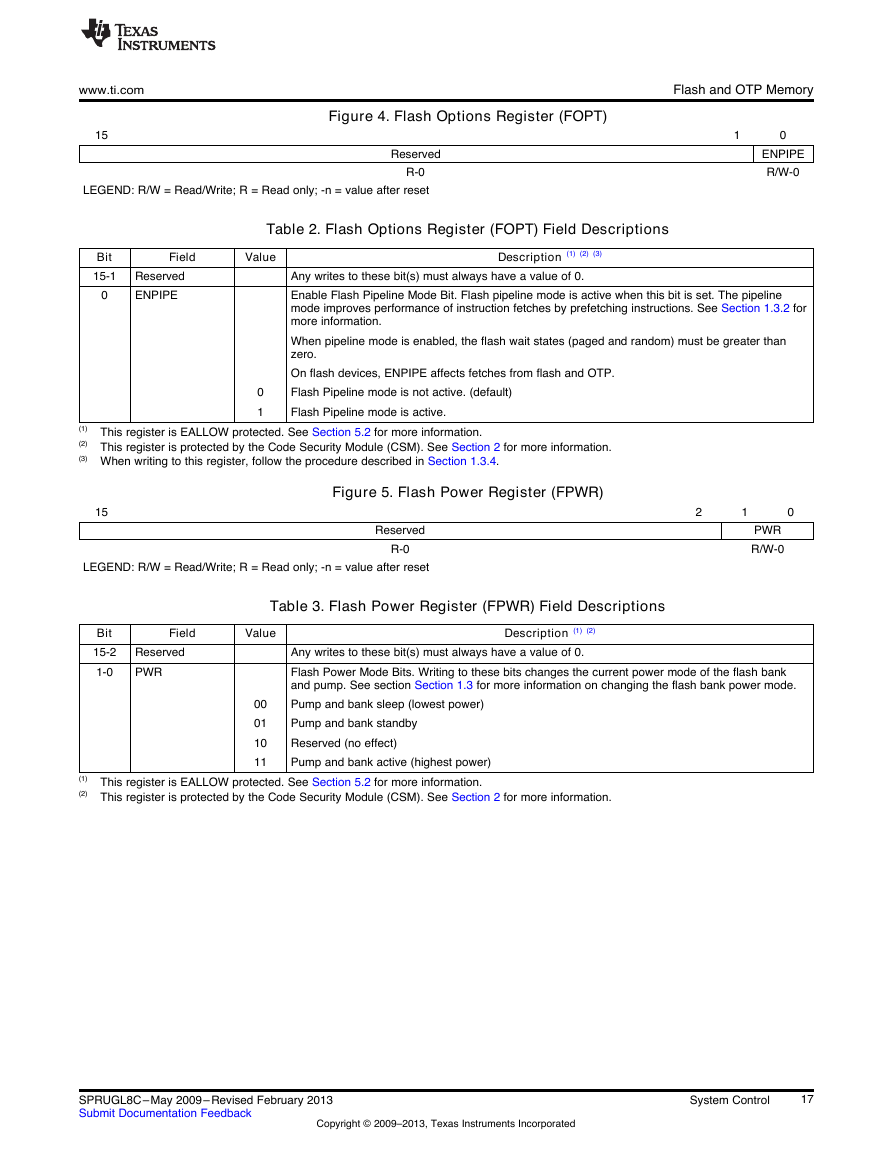

Figure 4. Flash Options Register (FOPT)

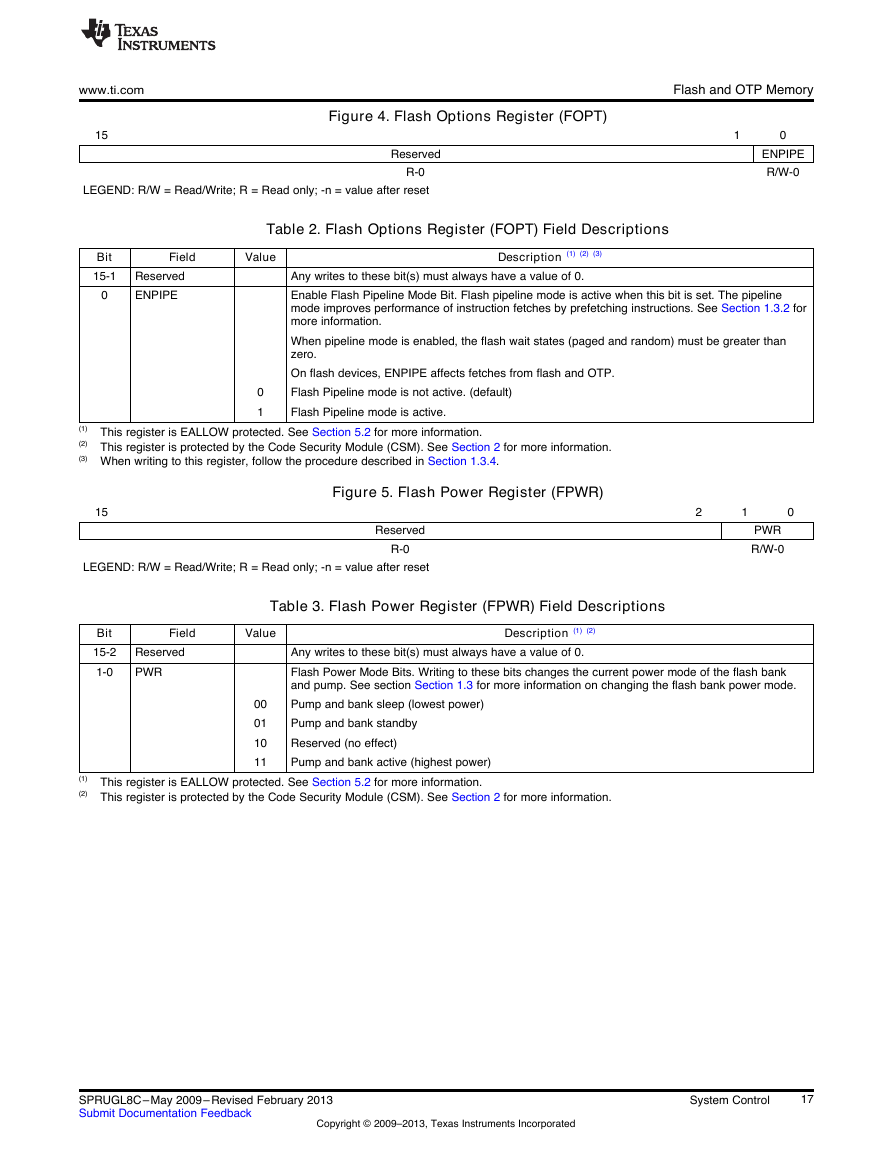

Figure 5. Flash Power Register (FPWR)

Figure 6. Flash Status Register (FSTATUS)

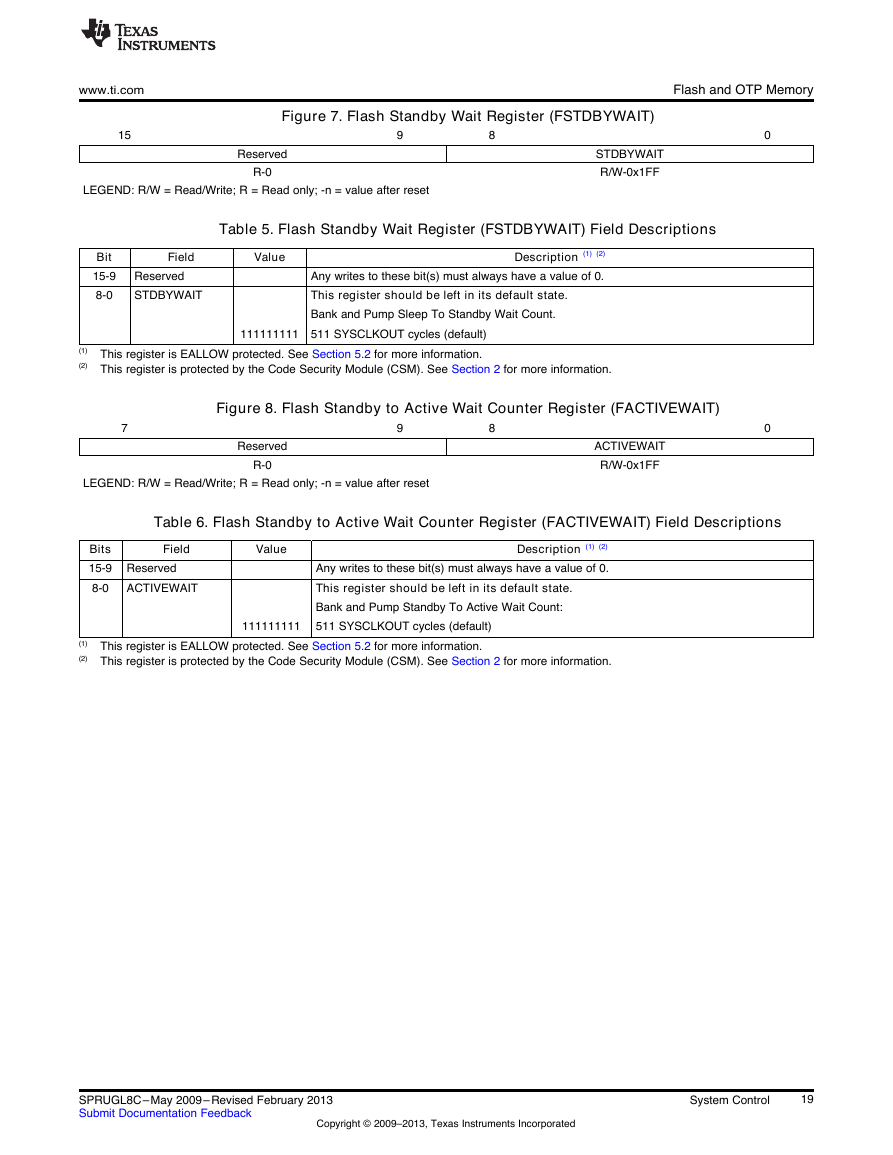

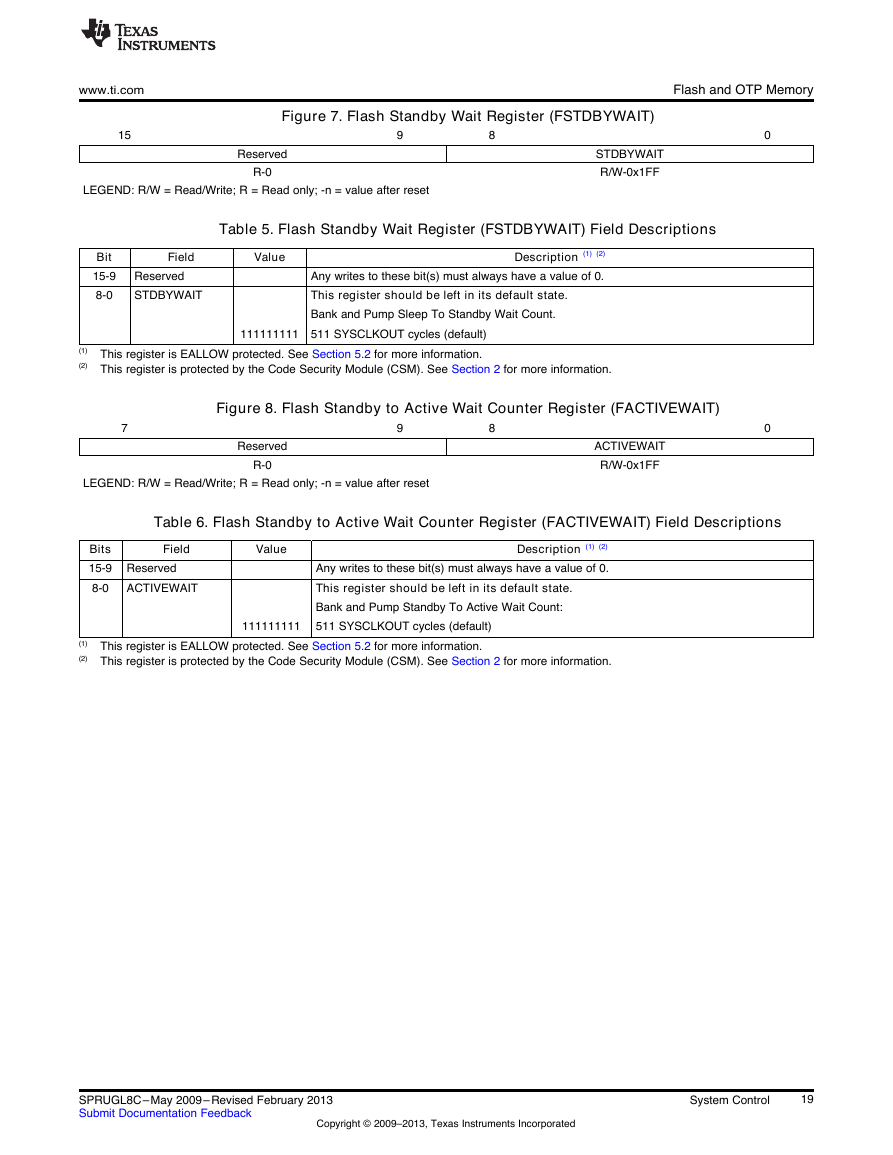

Figure 7. Flash Standby Wait Register (FSTDBYWAIT)

Figure 8. Flash Standby to Active Wait Counter Register (FACTIVEWAIT)

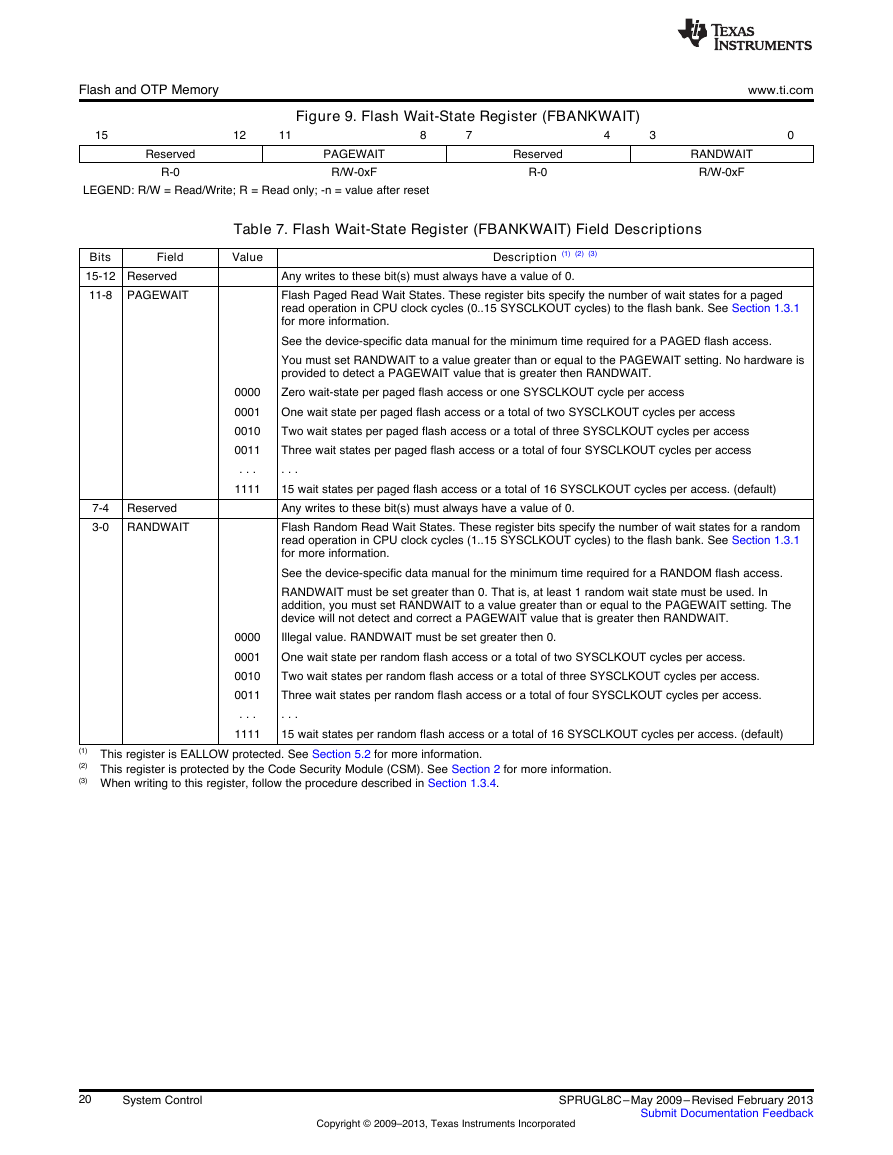

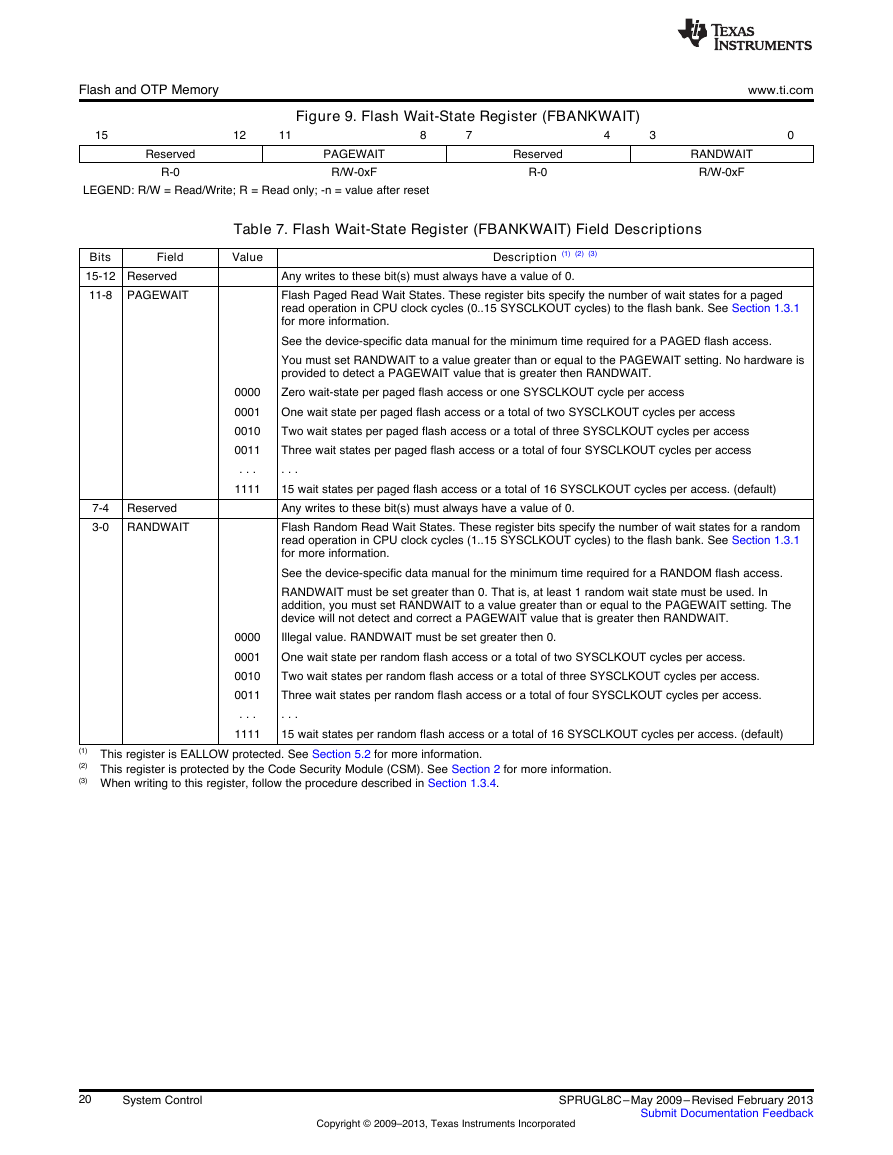

Figure 9. Flash Wait-State Register (FBANKWAIT)

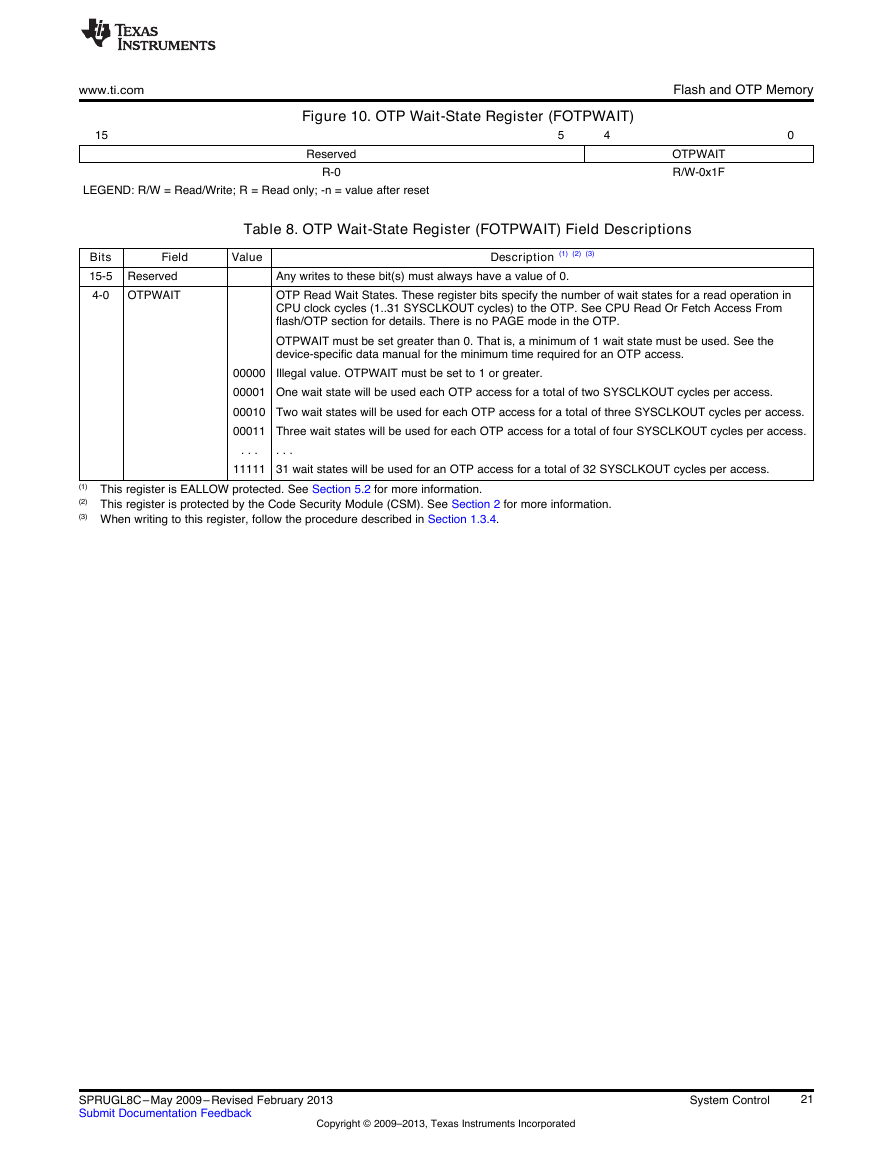

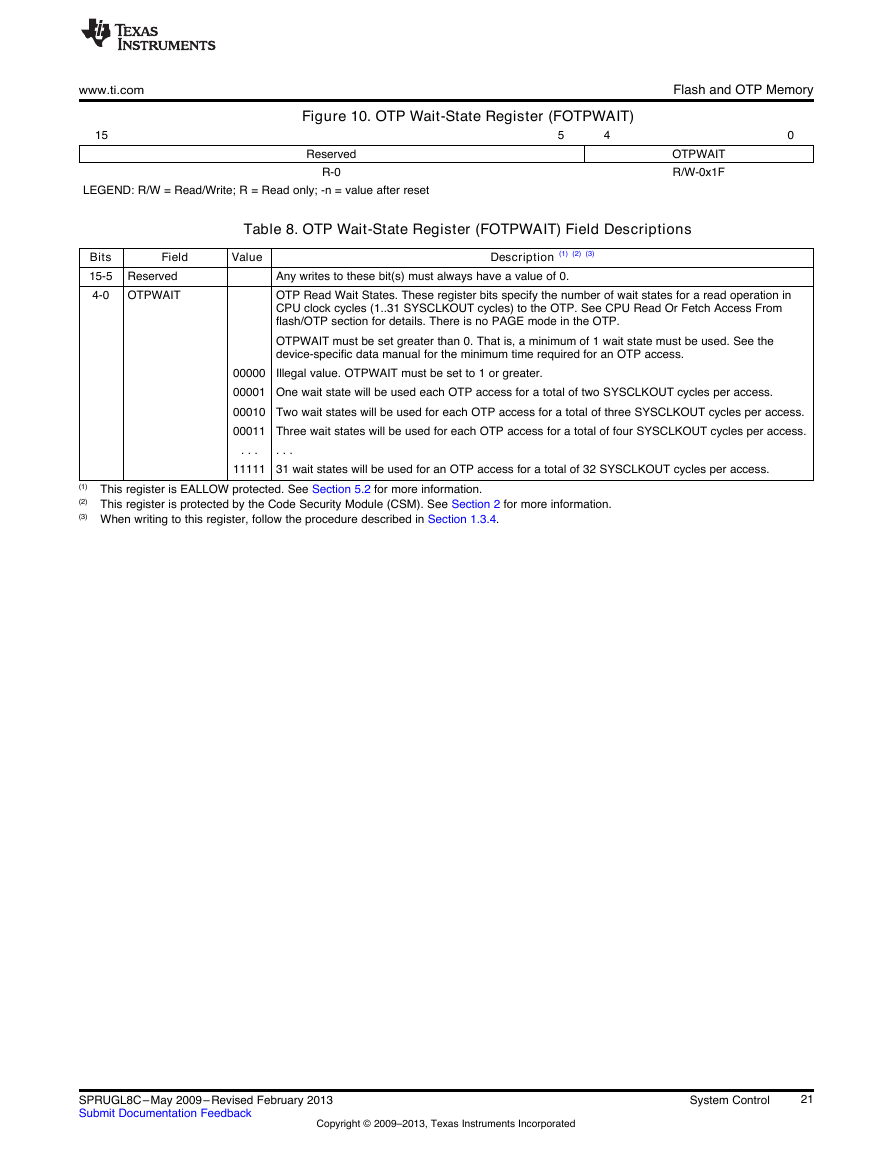

Figure 10. OTP Wait-State Register (FOTPWAIT)

CPU Timers Register.pdf

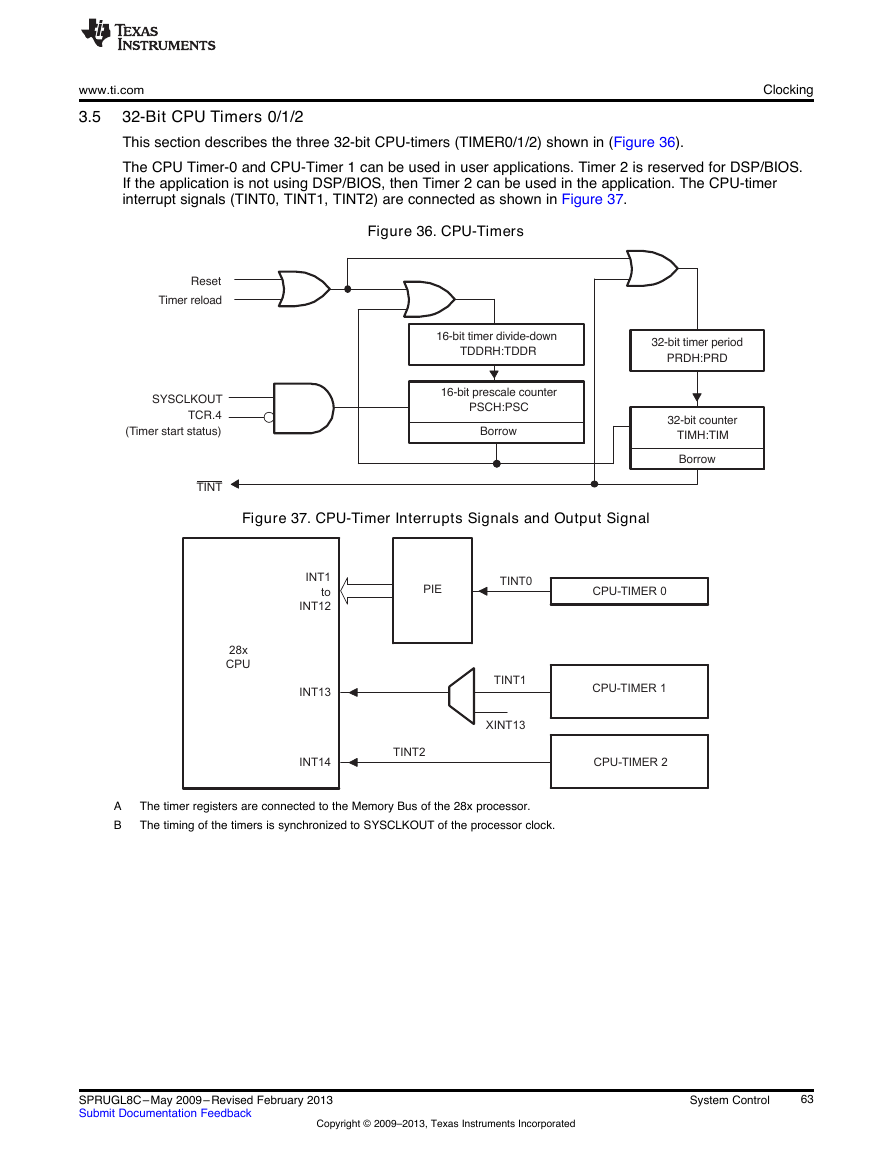

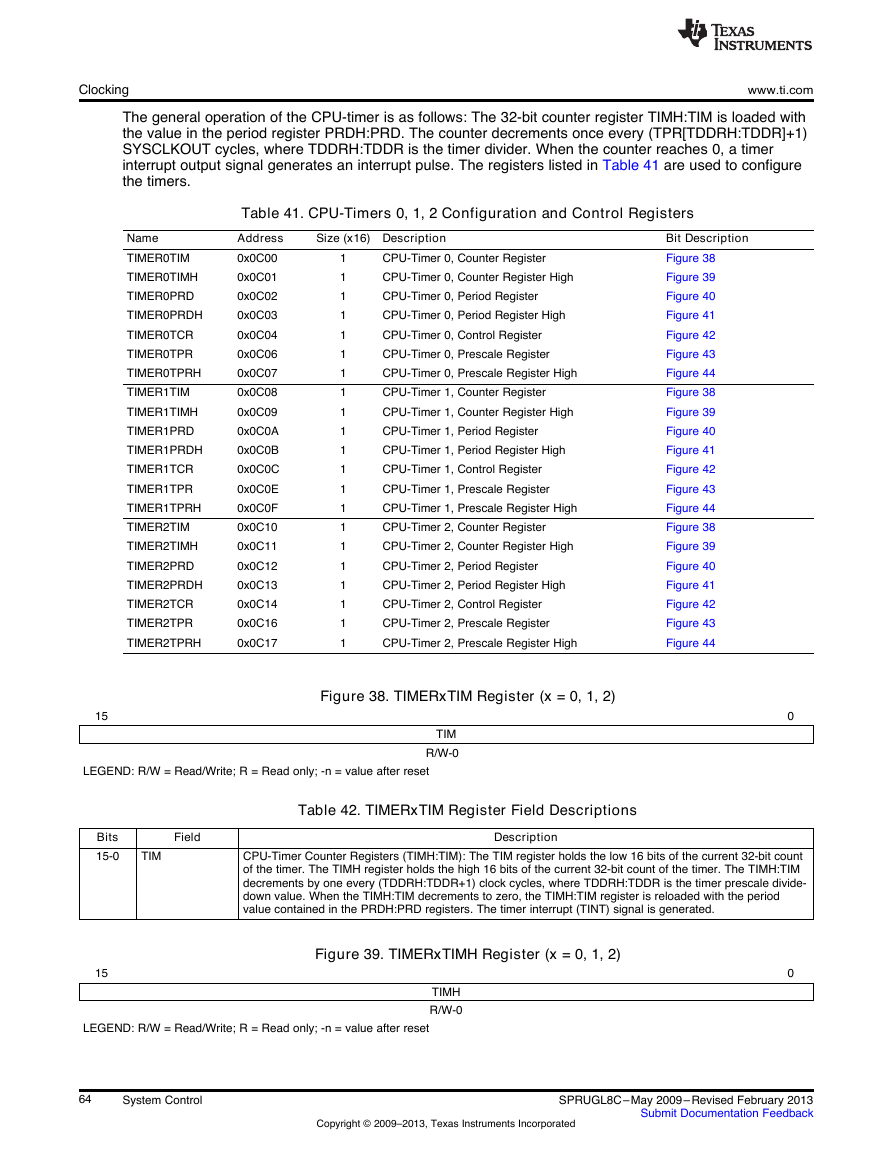

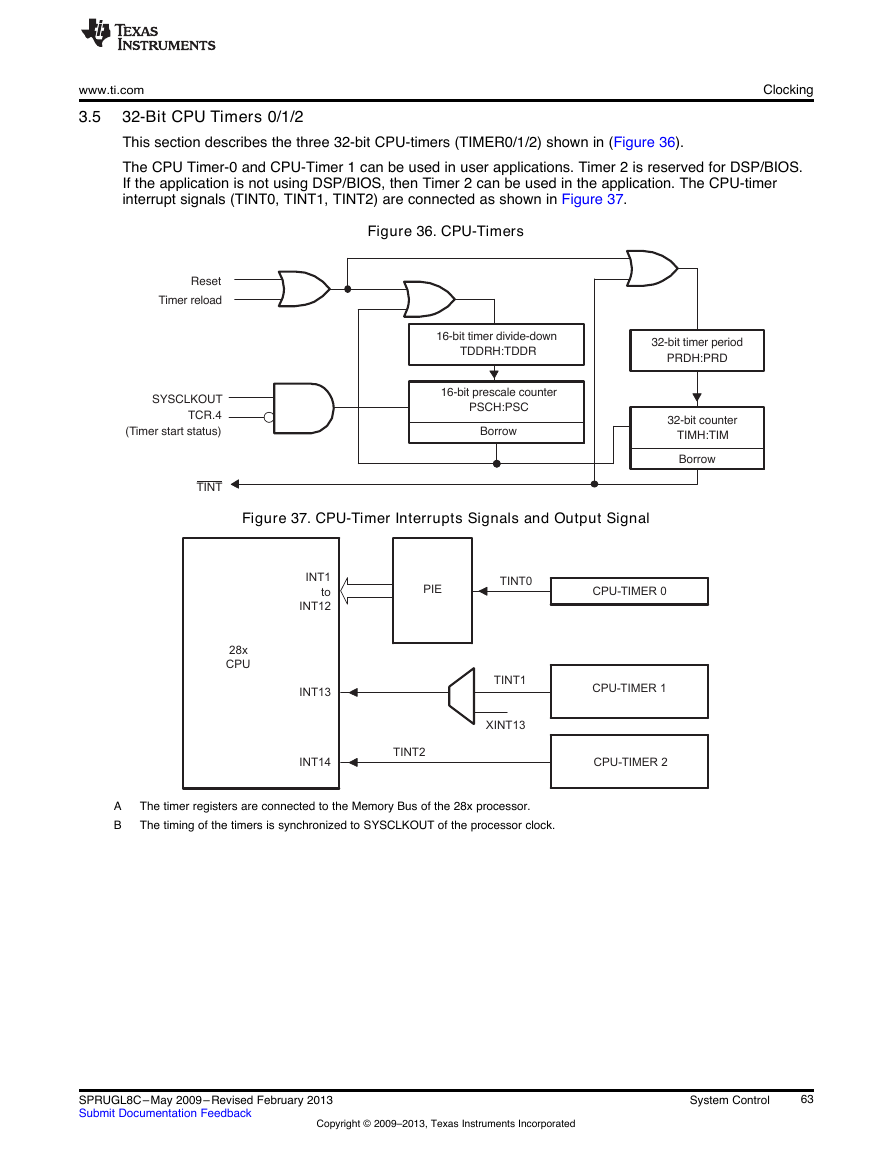

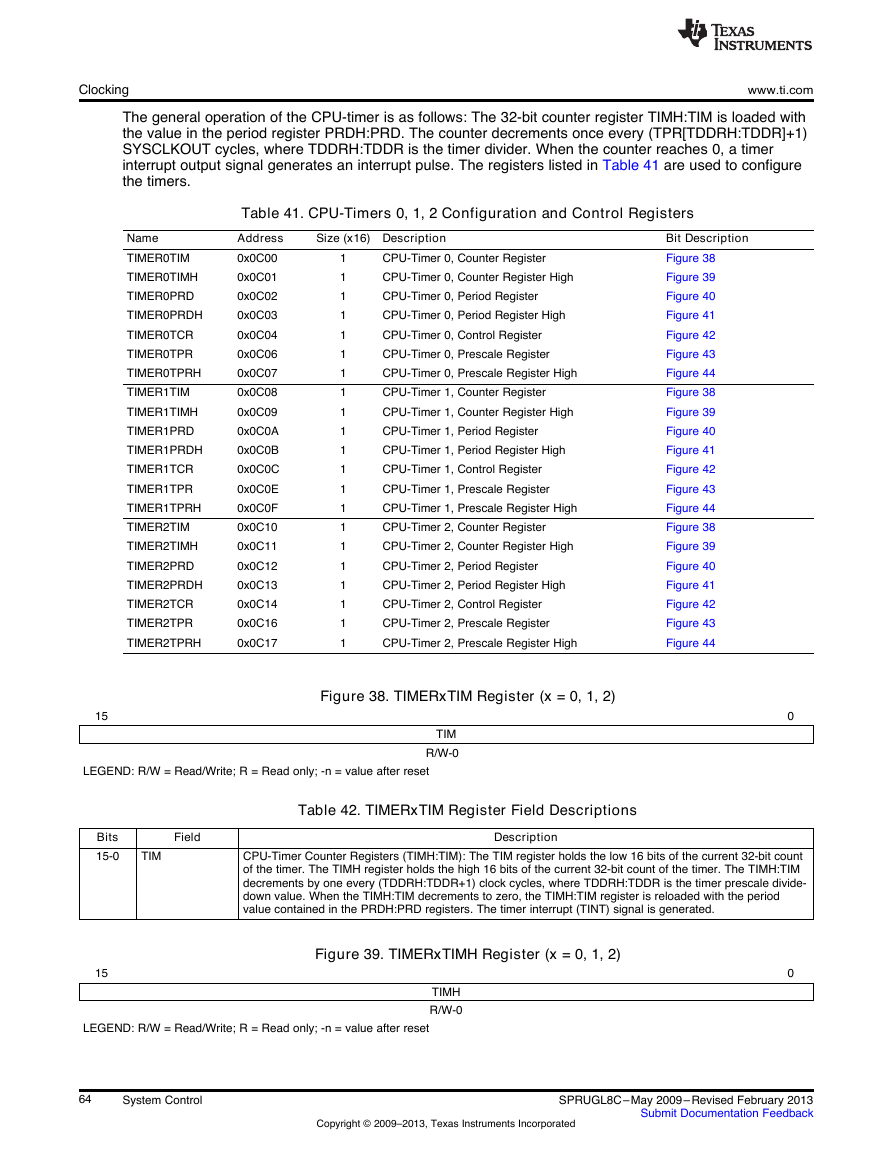

32-Bit CPU Timers 0/1/2

Figure 38. TIMERxTIM Register (x = 0, 1, 2)

Figure 39. TIMERxTIMH Register (x = 0, 1, 2)

Figure 40. TIMERxPRD Register (x = 0, 1, 2)

Figure 41. TIMERxPRDH Register (x = 0, 1, 2)

Figure 42. TIMERxTCR Register (x = 0, 1, 2)

Figure 43. TIMERxTPR Register (x = 0, 1, 2)

Figure 44. TIMERxTPRH Register (x = 0, 1, 2)

Clocking and System Control Register.pdf

Enabling/Disabling Clocks to the Peripheral Modules

Figure 14. Peripheral Clock Control 0 Register (PCLKCR0)

Figure 15. Peripheral Clock Control 1 Register (PCLKCR1)

Figure 16. Peripheral Clock Control 3 Register (PCLKCR3)

Figure 17. Low-Speed Peripheral Clock Prescaler Register (LOSPCP)

PLL and XCLKOUT Register.pdf

PLL Control, Status and XCLKOUT Register Descriptions

Figure 28. PLL Status Register (PLLSTS)

Figure 29. PLL Lock Period (PLLLOCKPRD) Register

PIE Interrupt Registers.pdf

PIE Interrupt Registers

Figure 81. PIECTRL Register (Address 0xCE0)

Figure 82. PIE Interrupt Acknowledge Register (PIEACK) Register (Address 0xCE1)

Figure 83. PIEIFRx Register (x = 1 to 12)

Figure 84. PIEIERx Register (x = 1 to 12)

Figure 85. Interrupt Flag Register (IFR) — CPU Register

Figure 86. Interrupt Enable Register (IER) — CPU Register

Figure 87. Debug Interrupt Enable Register (DBGIER) — CPU Register

The PIE Vector Table.pdf

Watchdog Registers.pdf

Watchdog Registers

Figure 32. System Control and Status Register (SCSR)

Figure 33. Watchdog Counter Register (WDCNTR)

Figure 34. Watchdog Reset Key Register (WDKEY)

Figure 35. Watchdog Control Register (WDCR)

External Interrupt Control Registers.pdf

External Interrupt Control Registers

Figure 88. External Interrupt n Control Register (XINTnCR)

Figure 89. External Interrupt n Counter (XINTnCTR) (Address 7078h)

GPIO Register.pdf

GPIO Register Bit Definitions

Figure 51. GPIO Port A MUX 1 (GPAMUX1) Register

Figure 52. GPIO Port A MUX 2 (GPAMUX2) Register

Figure 53. GPIO Port B MUX 1 (GPBMUX1) Register

Figure 54. Analog I/O MUX (AIOMUX1) Register

Figure 55. GPIO Port A Qualification Control (GPACTRL) Register

Figure 56. GPIO Port B Qualification Control (GPBCTRL) Register

Figure 57. GPIO Port A Qualification Select 1 (GPAQSEL1) Register

Figure 58. GPIO Port A Qualification Select 2 (GPAQSEL2) Register

Figure 59. GPIO Port B Qualification Select 1 (GPBQSEL1) Register

Figure 60. GPIO Port A Direction (GPADIR) Register

Figure 61. GPIO Port B Direction (GPBDIR) Register

Figure 62. Analog I/O DIR (AIODIR) Register

Figure 63. GPIO Port A Pullup Disable (GPAPUD) Registers

Figure 64. GPIO Port B Pullup Disable (GPBPUD) Registers

Figure 65. GPIO Port A Data (GPADAT) Register

Figure 66. GPIO Port B Data (GPBDAT) Register

Figure 67. Analog I/O DAT (AIODAT) Register

Figure 68. GPIO Port A Set, Clear and Toggle (GPASET, GPACLEAR, GPATOGGLE) Registers

Figure 69. GPIO Port B Set, Clear and Toggle (GPBSET, GPBCLEAR, GPBTOGGLE) Registers

Figure 70. Analog I/O Toggle (AIOSET, AIOCLEAR, AIOTOGGLE) Register

Figure 71. GPIO XINTn Interrupt Select (GPIOXINTnSEL) Registers

Figure 72. GPIO Low Power Mode Wakeup Select (GPIOLPMSEL) Register

EPWM Registers.pdf

4.1 Time-Base Submodule Registers

Time-Base Period Register (TBPRD)

Time Base Period High Resolution Register (TBPRDHR)

Time Base Period Mirror Register (TBPRDM)

Time-Base Period High Resolution Mirror Register (TBPRDHRM)

Time-Base Phase Register (TBPHS)

Time-Base Phase High Resolution Register (TBPHSHR)

Time-Base Counter Register (TBCTR)

Time-Base Control Register (TBCTL)

Time-Base Status Register (TBSTS)

High Resolution Period Control Register (HRPCTL)

4.2 Counter-Compare Submodule Registers

Counter-Compare A Register (CMPA)

Counter-Compare B Register (CMPB)

Counter-Compare Control Register (CMPCTL)

Counter-Compare A Mirror Register (CMPAM)

Compare A High Resolution Mirror Register(CMPAHRM)

4.3 Action-Qualifier Submodule Registers

Action-Qualifier Output A Control Register (AQCTLA)

Action-Qualifier Output B Control Register (AQCTLB)

Action-Qualifier Software Force Register (AQSFRC)

Action-Qualifier Continuous Software Force Register (AQCSFRC)

4.4 Dead-Band Submodule Registers

Dead-Band Generator Control Register (DBCTL)

Dead-Band Generator Rising Edge Delay Register (DBRED)

Dead-Band Generator Falling Edge Delay Register (DBFED

4.5 PWM-Chopper Submodule Control Register

PWM-Chopper Control Register (PCCTL)

4.6 Trip-Zone Submodule Control and Status Registers

Trip-Zone Select Register (TZSEL)

Trip-Zone Control Register (TZCTL)

Trip-Zone Enable Interrupt Register (TZEINT)

Trip-Zone Flag Register (TZFLG)

Trip-Zone Clear Register (TZCLR)

Trip-Zone Force Register (TZFRC)

Trip Zone Digital Compare Event Select Register (TZDCSEL)

4.7 Digital Compare Submodule Registers

Digital Compare Trip Select (DCTRIPSEL)

Digital Compare A Control Register (DCACTL)

Digital Compare B Control Register (DCBCTL)

Digital Compare Filter Control Register (DCFCTL)

Digital Compare Capture Control Register (DCCAPCTL)

Digital Compare Counter Capture Register (DCCAP)

Digital Compare Filter Offset Register (DCFOFFSET)

Digital Compare Filter Offset Counter Register (DCFOFFSETCNT)

Digital Compare Filter Window Register (DCFWINDOW)

Digital Compare Filter Window Counter Register (DCFWINDOWCNT)

4.8 Event-Trigger Submodule Registers

Event-Trigger Selection Register (ETSEL)

Event-Trigger Prescale Register (ETPS)

Event-Trigger Flag Register (ETFLG)15

Event-Trigger Clear Register (ETCLR)

Event-Trigger Force Register (ETFRC)

HRPWM Register.pdf

HRPWM Register

Figure 15. HRPWM Configuration Register (HRCNFG)

Figure 16. Counter Compare A High Resolution Register (CMPAHR)

Figure 17. TB Phase High Resolution Register (TBPHSHR)

Figure 18. Time Base Period High Resolution Register

Figure 19. Compare A High Resolution Mirror Register

Figure 20. Time-Base Period High Resolution Mirror Register15

Figure 21. High Resolution Period Control Register (HRPCTL)

Figure 22. High Resolution Micro Step Register (HRMSTEP) (EALLOW protected)

Figure 23. High Resolution Power Register (HRPWR) (EALLOW protected)

ECap Registers.pdf

Capture Module - Control and Status Registers

Figure 9. Time-Stamp Counter Register (TSCTR)

Figure 10. Counter Phase Control Register (CTRPHS)

Figure 11. Capture-1 Register (CAP1)

Figure 12. Capture-2 Register (CAP2)31

Figure 13. Capture-3 Register (CAP3)

Figure 14. Capture-4 Register (CAP4)

Figure 15. ECAP Control Register 1 (ECCTL1)

Figure 16. ECAP Control Register 2 (ECCTL2)

Figure 17. ECAP Interrupt Enable Register (ECEINT)

Figure 18. ECAP Interrupt Flag Register (ECFLG)

Figure 19. ECAP Interrupt Clear Register (ECCLR)

Figure 20. ECAP Interrupt Forcing Register (ECFRC)

Register Mapping

EQEP Registers.pdf

eQEP Registers

Figure 21. QEP Decoder Control (QDECCTL) Register

Figure 22. eQEP Control (QEPCTL) Register

Figure 23. eQEP Position-compare Control (QPOSCTL) Register

Figure 24. eQEP Capture Control (QCAPCTL) Register

Figure 25. eQEP Position Counter (QPOSCNT) Register

Figure 26. eQEP Position Counter Initialization (QPOSINIT) Register

Figure 27. eQEP Maximum Position Count Register (QPOSMAX) Register

Figure 28. eQEP Position-compare (QPOSCMP) Register

Figure 29. eQEP Index Position Latch (QPOSILAT) Register

Figure 30. eQEP Strobe Position Latch (QPOSSLAT) Register

Figure 31. eQEP Position Counter Latch (QPOSLAT) Register

Figure 32. eQEP Unit Timer (QUTMR) Register

Figure 33. eQEP Register Unit Period (QUPRD) Register

Figure 34. eQEP Watchdog Timer (QWDTMR) Register

Figure 35. eQEP Watchdog Period (QWDPRD) Register

Figure 36. eQEP Interrupt Enable (QEINT) Register

Figure 37. eQEP Interrupt Flag (QFLG) Register

Figure 38. eQEP Interrupt Clear (QCLR) Register

Figure 39. eQEP Interrupt Force (QFRC) Register

Figure 40. eQEP Status (QEPSTS) Register

Figure 41. eQEP Capture Timer (QCTMR) Register

Figure 42. eQEP Capture Period (QCPRD) Register

Figure 43. eQEP Capture Timer Latch (QCTMRLAT) Register

Figure 44. eQEP Capture Period Latch (QCPRDLAT) Register

ADC Registers.pdf

ADC Registers

ADC Control Register 1 (ADCCTL1)

Figure 8. ADC Control Register 1 (ADCCTL1)

ADC Control Register 2 (ADCCTL2)

Figure 9. ADC Control Register 2 (ADCCTL2)

ADC Interrupt Registers

Figure 10. ADC Interrupt Flag Register (ADCINTFLG)

Figure 11. ADC Interrupt Flag Clear Register (ADCINTFLGCLR)

Figure 12. ADC Interrupt Overflow Register (ADCINTOVF)

Figure 13. ADC Interrupt Overflow Clear Register (ADCINTOVFCLR)

Figure 14. Interrupt Select 1 And 2 Register (INTSEL1N2)

Figure 15. Interrupt Select 3 And 4 Register (INTSEL3N4)

Figure 16. Interrupt Select 5 And 6 Register (INTSEL5N6)

Figure 17. Interrupt Select 7 And 8 Register (INTSEL7N8)

Figure 18. Interrupt Select 9 And 10 Register (INTSEL9N10)

Table 9. INTSELxNy Register Field Descriptions

ADC Priority Register

Figure 19. ADC Start of Conversion Priority Control Register (SOCPRICTL)

ADC SOC Registers

Figure 20. ADC Sample Mode Register (ADCSAMPLEMODE)

Figure 21. ADC Interrupt Trigger SOC Select 1 Register (ADCINTSOCSEL1)

Figure 22. ADC Interrupt Trigger SOC Select 2 Register (ADCINTSOCSEL2)

Figure 23. ADC SOC Flag 1 Register (ADCSOCFLG1)

Figure 24. ADC SOC Force 1 Register (ADCSOCFRC1)

Figure 25. ADC SOC Overflow 1 Register (ADCSOCOVF1)

Figure 26. ADC SOC Overflow Clear 1 Register (ADCSOCOVFCLR1)

Figure 27. ADC SOC0 - SOC15 Control Registers (ADCSOCxCTL)

ADC Calibration Registers

Figure 28. ADC Reference/Gain Trim Register (ADCREFTRIM)

Figure 29. ADC Offset Trim Register (ADCOFFTRIM)

Comparator Hysteresis Control Register

Figure 30. Comparator Hysteresis Control Register (COMPHYSTCTL)

ADC Revision Register

Figure 31. ADC Revision Register (ADCREV)

ADC Result Registers

Figure 32. ADC RESULT0 - RESULT15 Registers (ADCRESULTx)

Comparator Registers.pdf

Comparator Registers

Comparator Control (COMPCTL) Register

Compare Output Status (COMPSTS) Register

DAC Control (DACCTL) Register

DAC Value (DACVAL) Register

Ramp Generator Maximum Reference Active (RAMPMAXREF_ACTIVE) Register

Ramp Generator Maximum Reference Shadow (RAMPMAXREF_SHDW) Register

Ramp Generator Decrement Value Active (RAMPDECVAL_ACTIVE) Register

Ramp Generator Decrement Value Shadow (RAMPDECVAL_SHDW) Register

Ramp Generator Status (RAMPSTS) Register

SPI Registers.pdf

SPI Control Registers

SPI Configuration Control Register (SPICCR)

SPI Operation Control Register (SPICTL)

SPI Status Register (SPIST)

SPI Baud Rate Register (SPIBRR)

SPI Emulation Buffer Register (SPIRXEMU)

SPI Serial Receive Buffer Register (SPIRXBUF)

SPI Serial Transmit Buffer Register (SPITXBUF)

SPI Serial Data Register (SPIDAT)

SPI FIFO Transmit, Receive, and Control Registers

SPI Priority Control Register (SPIPRI)

SCI Registers.pdf

SCI Registers

SCI Communication Control Register (SCICCR)

SCI Control Register 1 (SCICTL1)

SCI Baud-Select Registers (SCIHBAUD, SCILBAUD)

SCI Control Register 2 (SCICTL2)

SCI Receiver Status Register (SCIRXST)

Receiver Data Buffer Registers (SCIRXEMU, SCIRXBUF)

SCI Transmit Data Buffer Register (SCITXBUF)

SCI FIFO Registers (SCIFFTX, SCIFFRX, SCIFFCT)

Priority Control Register (SCIPRI)

I2C Module Registers.pdf

I2C Module Registers

I2C Mode Register (I2CMDR)

I2C Extended Mode Register (I2CEMDR)

I2C Interrupt Enable Register (I2CIER)

I2C Status Register (I2CSTR)

I2C Interrupt Source Register (I2CISRC)

I2C Prescaler Register (I2CPSC)

I2C Clock Divider Registers (I2CCLKL and I2CCLKH)

I2C Slave Address Register (I2CSAR)

I2C Own Address Register (I2COAR)

I2C Data Count Register (I2CCNT)

I2C Data Receive Register (I2CDRR)

I2C Data Transmit Register (I2CDXR)

I2C Transmit FIFO Register (I2CFFTX)

I2C Receive FIFO Register (I2CFFRX)

ECAN Registers.pdf

eCAN Registers

Mailbox Enable Register (CANME)

Mailbox-Direction Register (CANMD)

Transmission-Request Set Register (CANTRS

Transmission-Request-Reset Register (CANTRR)

Transmission-Acknowledge Register (CANTA)

Abort-Acknowledge Register (CANAA)

Received-Message-Pending Register (CANRMP)

Received-Message-Lost Register (CANRML)

Remote-Frame-Pending Register (CANRFP)

Global Acceptance Mask Register (CANGAM)

Master Control Register (CANMC)

Bit-Timing Configuration Register (CANBTC)

Error and Status Register (CANES)

CAN Error Counter Registers (CANTEC/CANREC)

Figure 18. Transmit-Error-Counter Register (CANTEC)

Figure 19. Receive-Error-Counter Register (CANREC

Interrupt Registers

Global Interrupt Flag Registers (CANGIF0/CANGIF1)

Figure 20. Global Interrupt Flag 0 Register (CANGIF0)

Figure 21. Global Interrupt Flag 1 Register (CANGIF1)

Global Interrupt Mask Register (CANGIM)

Mailbox Interrupt Mask Register (CANMIM)

Mailbox Interrupt Level Register (CANMIL)

Overwrite Protection Control Register (CANOPC)

eCAN I/O Control Registers (CANTIOC, CANRIOC)

Figure 26. TX I/O Control Register (CANTIOC)

Figure 27. RX I/O Control Register (CANRIOC)

Timer Management Unit

Time-Stamp Counter Register (CANTSC)

Message Object Time Stamp Registers (MOTS)

Message-Object Time-Out Registers (MOTO)

Time-Out Control Register (CANTOC)

Time-Out Status Register (CANTOS)

Mailbox Layout

Message Identifier Register (MSGID)

Message-Control Register (MSGCTRL)

Message Data Registers (CANMDL, CANMDH)

CLA register.pdf

CLA Register

Task Interrupt Vector Registers

Figure 2. Task Interrupt Vector (MVECT1/2/3/4/5/6/7/8) Register

Configuration Registers

Control Register (MCTL)

Memory Configuration Register (MMEMCFG)

CLA Peripheral Interrupt Source Select 1 Register (MPISRCSEL1)

Interrupt Enable Register (MIER)

Interrupt Flag Register (MIFR)

Interrupt Overflow Flag Register (MIOVF)

Interrupt Run Status Register (MIRUN)

Interrupt Force Register (MIFRC)

Interrupt Flag Clear Register (MICLR)

Interrupt Overflow Flag Clear Register (MICLROVF)

Execution Registers

MPC Register

Figure 13. Program Counter (MPC)

MSTF Register

Figure 14. CLA Status Register (MSTF)

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc