ZYNQ MPSoC 逻辑开发教程

AXU3CG

19.8.5 14:54:32

�

ALINX 黑金 ZYNQ MPSoC 开发平台配套教

版权声明

程

Copyright © 2012-2019 芯驿电子科技(上海)有限公司

公司网址:

Http://www.alinx.com

天猫旗舰店:

https://alinx.tmall.com

京东旗舰店:

http://alinx.jd.com

邮箱:

avic@alinx.com

电话:

021-67676997

传真:

021-37737073

ALINX 微信公众号:

芯驿电子科技(上海)有限公司

2 / 181

�

时间

2019/6/13

2019/7/16

2019/7/23

2019/8/5

版本

1.01

1.02

1.03

1.04

ALINX 黑金 ZYNQ MPSoC 开发平台配套教

程

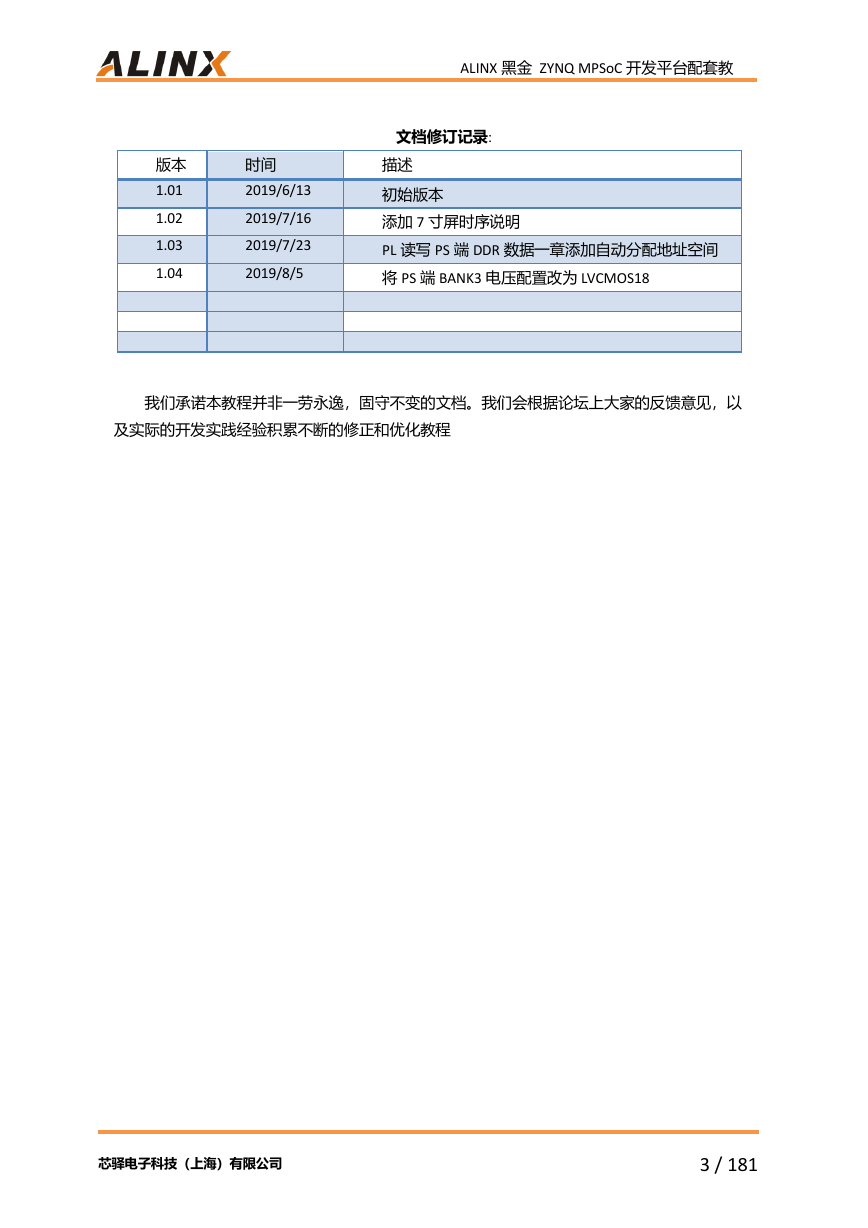

文档修订记录:

描述

初始版本

添加 7 寸屏时序说明

PL 读写 PS 端 DDR 数据一章添加自动分配地址空间

将 PS 端 BANK3 电压配置改为 LVCMOS18

我们承诺本教程并非一劳永逸,固守不变的文档。我们会根据论坛上大家的反馈意见,以

及实际的开发实践经验积累不断的修正和优化教程

芯驿电子科技(上海)有限公司

3 / 181

�

ALINX 黑金 ZYNQ MPSoC 开发平台配套教

程

前言

首先感谢大家购买芯驿电子科技(上海)有限公司出品的 ZYNQ MPSoC 的开发板!您对

我们和我们产品的支持和信任,给我们增添了勇往直前的信心和勇气。“播下一粒种子,收获

一片森林”,更是芯驿电子科技(上海)有限公司的美好愿望。

本文档主要介绍 ZYNQ MPSoC 下的硬件工程创建过程。

芯驿电子科技(上海)有限公司只能抛砖引玉,把最常用的知识点收集分享给大家。

芯驿电子科技(上海)有限公司

4 / 181

�

ALINX 黑金 ZYNQ MPSoC 开发平台配套教

程

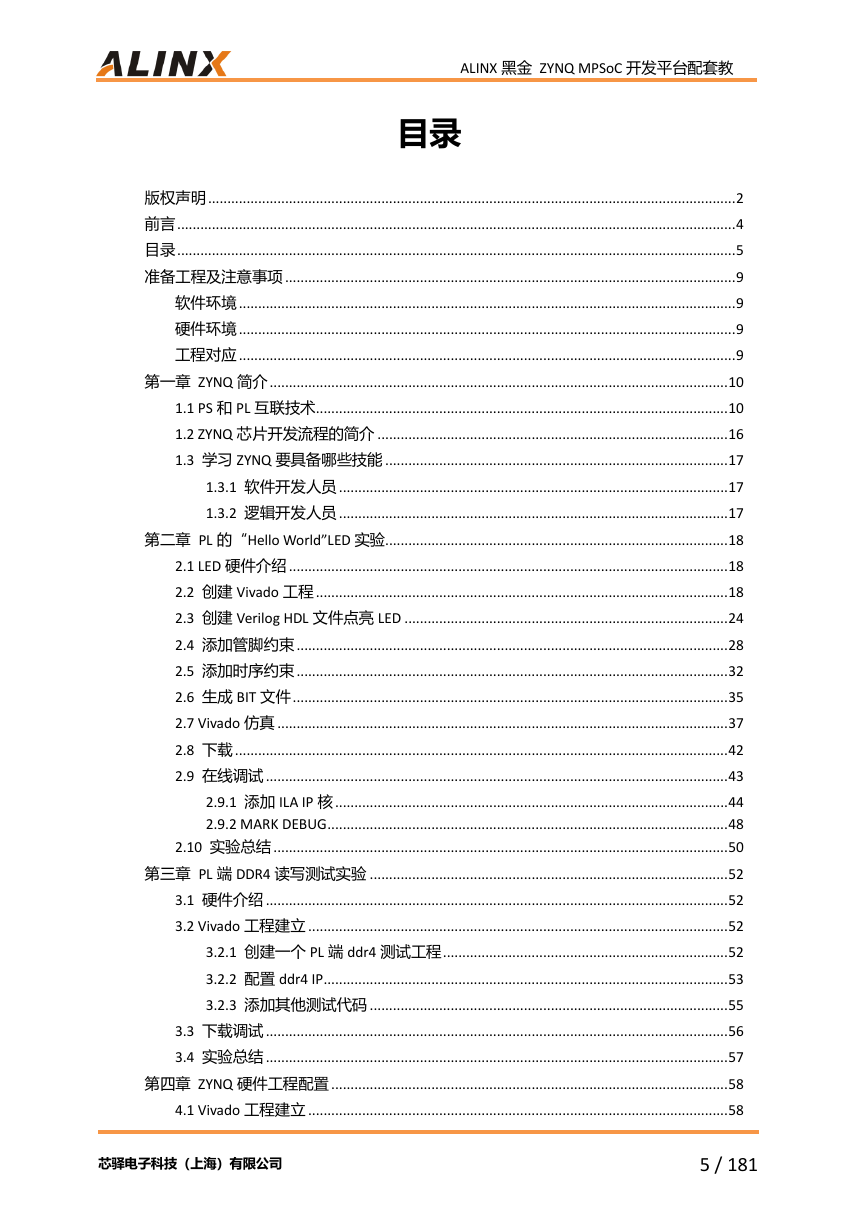

目录

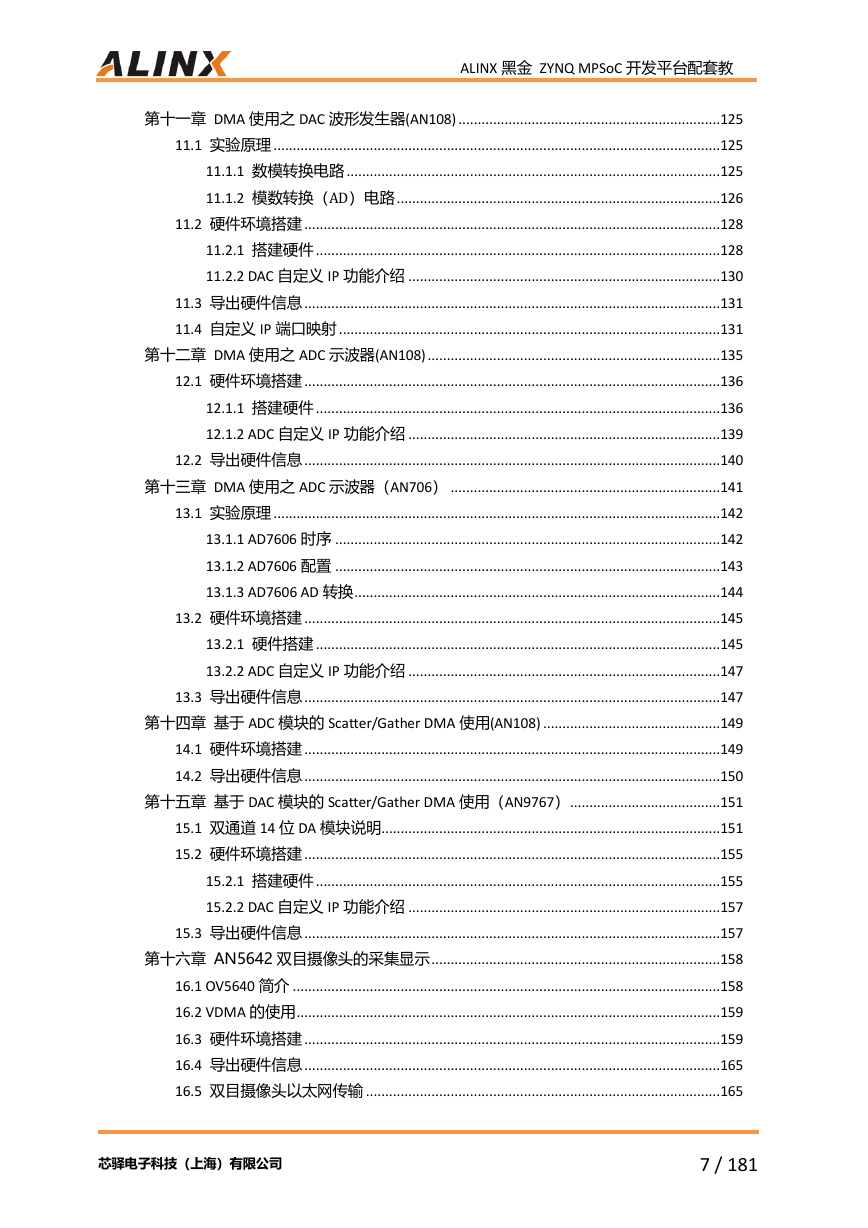

版权声明 ......................................................................................................................................... 2

前言 ................................................................................................................................................. 4

目录 ................................................................................................................................................. 5

准备工程及注意事项 ..................................................................................................................... 9

软件环境 ................................................................................................................................. 9

硬件环境 ................................................................................................................................. 9

工程对应 ................................................................................................................................. 9

第一章 ZYNQ 简介 ....................................................................................................................... 10

1.1 PS 和 PL 互联技术 ........................................................................................................... 10

1.2 ZYNQ 芯片开发流程的简介 ........................................................................................... 16

1.3 学习 ZYNQ 要具备哪些技能 ......................................................................................... 17

1.3.1 软件开发人员 ..................................................................................................... 17

1.3.2 逻辑开发人员 ..................................................................................................... 17

第二章 PL 的“Hello World”LED 实验 ......................................................................................... 18

2.1 LED 硬件介绍 .................................................................................................................. 18

2.2 创建 Vivado 工程 ........................................................................................................... 18

2.3 创建 Verilog HDL 文件点亮 LED .................................................................................... 24

2.4 添加管脚约束 ................................................................................................................ 28

2.5 添加时序约束 ................................................................................................................ 32

2.6 生成 BIT 文件 ................................................................................................................. 35

2.7 Vivado 仿真 ..................................................................................................................... 37

2.8 下载 ................................................................................................................................ 42

2.9 在线调试 ........................................................................................................................ 43

2.9.1 添加 ILA IP 核 ...................................................................................................... 44

2.9.2 MARK DEBUG ........................................................................................................ 48

2.10 实验总结 ...................................................................................................................... 50

第三章 PL 端 DDR4 读写测试实验 ............................................................................................. 52

3.1 硬件介绍 ........................................................................................................................ 52

3.2 Vivado 工程建立 ............................................................................................................. 52

3.2.1 创建一个 PL 端 ddr4 测试工程 .......................................................................... 52

3.2.2 配置 ddr4 IP......................................................................................................... 53

3.2.3 添加其他测试代码 ............................................................................................. 55

3.3 下载调试 ........................................................................................................................ 56

3.4 实验总结 ........................................................................................................................ 57

第四章 ZYNQ 硬件工程配置 ....................................................................................................... 58

4.1 Vivado 工程建立 ............................................................................................................. 58

芯驿电子科技(上海)有限公司

5 / 181

�

程

ALINX 黑金 ZYNQ MPSoC 开发平台配套教

4.1.1 Low Speed 配置 .................................................................................................... 61

4.1.2 High Speed 配置 ................................................................................................... 63

4.1.3 时钟配置 ............................................................................................................. 64

4.1.4 DDR 配置 .............................................................................................................. 66

4.1.5 PS-PL 配置 ............................................................................................................ 66

4.2 导出硬件信息 ................................................................................................................ 68

4.3 本章小结 ........................................................................................................................ 70

第五章 PS 点亮 PL 的 LED 灯....................................................................................................... 71

5.1 Vivado 工程建立 ............................................................................................................. 71

5.2 XDC 文件约束 PL 管脚 .................................................................................................... 77

5.3 导出硬件信息 ................................................................................................................ 79

第六章 PL 按键中断实验............................................................................................................. 81

6.1 Vivado 工程建立 ............................................................................................................. 81

配置中断 ....................................................................................................................... 83

6.2 XDC 文件约束 PL 管脚 .................................................................................................... 84

6.3 导出硬件信息 ................................................................................................................ 85

第七章 自定义 IP 实验 ................................................................................................................ 86

7.1 PWM 介绍 ....................................................................................................................... 86

7.2 Vivado 工程建立 ............................................................................................................. 87

7.2.1 创建一个 vivado 工程 ......................................................................................... 87

7.2.2 创建自定义 IP ..................................................................................................... 88

7.2.3 添加自定义 IP 到工程 ........................................................................................ 97

7.3 导出硬件信息 ................................................................................................................ 99

第八章 通过 BRAM 实现 PS 与 PL 数据交互 ............................................................................100

8.1 硬件环境搭建 ..............................................................................................................100

Block Design 添加逻辑分析仪方法 ............................................................................105

8.2 导出硬件信息 ..............................................................................................................107

第九章 PL 读写 PS 端 DDR 数据................................................................................................108

9.1 ZYNQ 的 HP 端口使用 ...................................................................................................108

9.2 硬件环境搭建 ..............................................................................................................108

9.3 PL 端 AXI Master ............................................................................................................113

9.4 ddr 读写数据的检验 .....................................................................................................115

9.5 Vivado 软件的调试技巧 ...............................................................................................115

9.6 导出硬件信息 ..............................................................................................................116

第十章 DMA 环通测试 ..............................................................................................................117

10.1 实验说明 ....................................................................................................................117

10.2 硬件环境搭建 ............................................................................................................118

10.3 导出硬件信息 ............................................................................................................124

芯驿电子科技(上海)有限公司

6 / 181

�

程

ALINX 黑金 ZYNQ MPSoC 开发平台配套教

第十一章 DMA 使用之 DAC 波形发生器(AN108) ....................................................................125

11.1 实验原理 ....................................................................................................................125

11.1.1 数模转换电路 .................................................................................................125

11.1.2 模数转换(AD)电路 ....................................................................................126

11.2 硬件环境搭建 ............................................................................................................128

11.2.1 搭建硬件 .........................................................................................................128

11.2.2 DAC 自定义 IP 功能介绍 .................................................................................130

11.3 导出硬件信息 ............................................................................................................131

11.4 自定义 IP 端口映射 ...................................................................................................131

第十二章 DMA 使用之 ADC 示波器(AN108) ............................................................................135

12.1 硬件环境搭建 ............................................................................................................136

12.1.1 搭建硬件 .........................................................................................................136

12.1.2 ADC 自定义 IP 功能介绍 .................................................................................139

12.2 导出硬件信息 ............................................................................................................140

第十三章 DMA 使用之 ADC 示波器(AN706) ......................................................................141

13.1 实验原理 ....................................................................................................................142

13.1.1 AD7606 时序 ....................................................................................................142

13.1.2 AD7606 配置 ....................................................................................................143

13.1.3 AD7606 AD 转换 ...............................................................................................144

13.2 硬件环境搭建 ............................................................................................................145

13.2.1 硬件搭建 .........................................................................................................145

13.2.2 ADC 自定义 IP 功能介绍 .................................................................................147

13.3 导出硬件信息 ............................................................................................................147

第十四章 基于 ADC 模块的 Scatter/Gather DMA 使用(AN108) ..............................................149

14.1 硬件环境搭建 ............................................................................................................149

14.2 导出硬件信息 ............................................................................................................150

第十五章 基于 DAC 模块的 Scatter/Gather DMA 使用(AN9767).......................................151

15.1 双通道 14 位 DA 模块说明........................................................................................151

15.2 硬件环境搭建 ............................................................................................................155

15.2.1 搭建硬件 .........................................................................................................155

15.2.2 DAC 自定义 IP 功能介绍 .................................................................................157

15.3 导出硬件信息 ............................................................................................................157

第十六章 AN5642 双目摄像头的采集显示 ...........................................................................158

16.1 OV5640 简介 ...............................................................................................................158

16.2 VDMA 的使用 ..............................................................................................................159

16.3 硬件环境搭建 ............................................................................................................159

16.4 导出硬件信息 ............................................................................................................165

16.5 双目摄像头以太网传输 ............................................................................................165

芯驿电子科技(上海)有限公司

7 / 181

�

程

ALINX 黑金 ZYNQ MPSoC 开发平台配套教

第十七章 7 寸触摸屏的使用 ....................................................................................................167

17.1 LCD 触摸屏说明介绍 ..................................................................................................167

17.2 硬件环境搭建 ............................................................................................................171

17.3 导出硬件信息 ............................................................................................................181

芯驿电子科技(上海)有限公司

8 / 181

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc