Xilinx_FPGA之Chipscope

2019年1月28日 22:56

1.建立工程

ChipScope是配合Xilinx Ise使用的片内逻辑分析工具,使用的第一步是建立ise工程文件,详细步骤可参考ise使用说

明。如果已有建好的ise工程,可跳过此步骤,打开已有工程即可。

建立工程时注意正确添加.v源文件和.ucf管脚配置文件。

2.插入及配置核

这里介绍的是ICON核和ILA核的使用方法。ILA核提供触发和跟踪功能,根据用户设置的触发条件捕获数据;然后在ICON的

控制下,通过边界扫描口将数据上传到PC;最后在Analyzer中显示出信号波形。

2.1运行Ise的Synthesize

单击选中sources栏中的顶层源文件,右键点击processs栏中的Synthesize,点击Run,进行代码综合。需综合通过

2.2 新建cdc文件

右键单击sources栏中顶层源文件,点击new source,选择chipscope definition and connection file,设好文件名及文

件路径,勾选add to project,然后一直点next完成建立。

变成了这样,说明添加完成。

2.3 配置核文件

双击sources栏中的刚刚建立的cdc文件,启动core inserter。点击两次next,进入ILA的设置界面,首先是trigger

parameters界面。

弹出netlist changed的提示框,点选ok刷新网表。通过number of input trigger ports可设置要观察波形的组数,通过

trigger width可设置每组观察的信号的数目。

点击next进入capture parameters界面。通过data depth可设置信号采集的时钟周期

数,采集数目越多,观察信号的时间越长。

点击next进入net connections界面。可以看到net connections端口列表显示红色字体,表示端口没有完全连接;当全部

端口都与具体信号连接时,字体变为黑色。

双击clock ports打开select net对话框。首先连接时钟信号,在右边net selections框中点clock signals,选择时钟的

信道CH0,在左下方的信号列表中找到时钟信号,单击选中,然后单击右下方make connections按钮,完成clk信号的连接。

分区 Xilinx_FPGA 的第 1 页

�

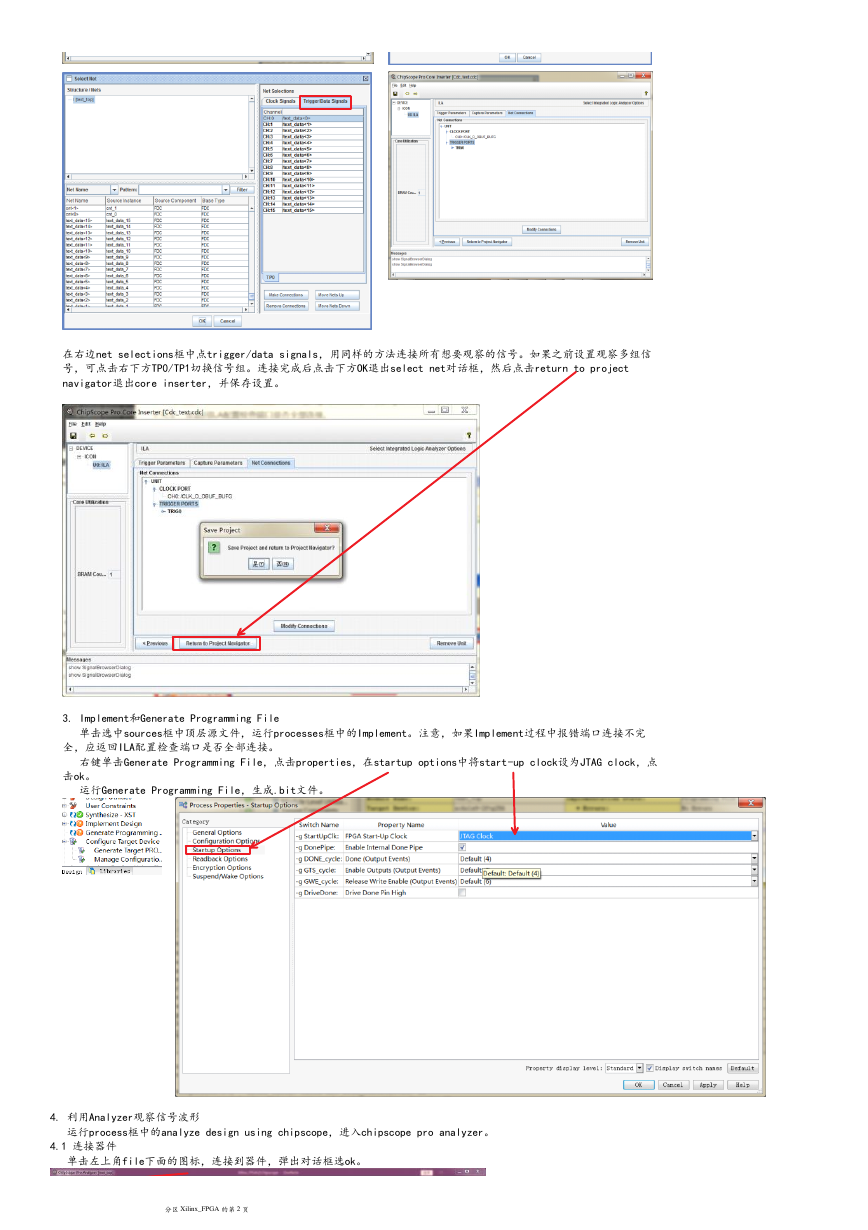

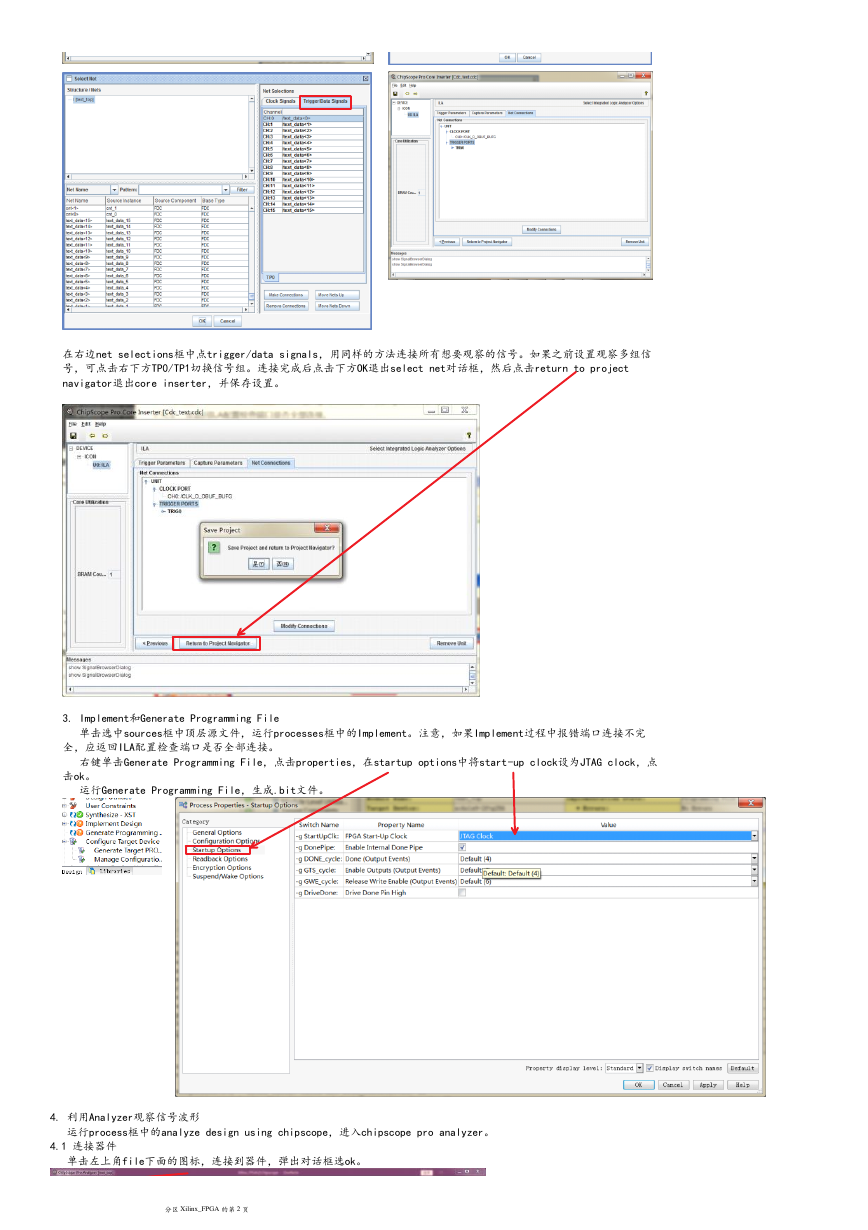

在右边net selections框中点trigger/data signals,用同样的方法连接所有想要观察的信号。如果之前设置观察多组信

号,可点击右下方TP0/TP1切换信号组。连接完成后点击下方OK退出select net对话框,然后点击return to project

navigator退出core inserter,并保存设置。

3. Implement和Generate Programming File

单击选中sources框中顶层源文件,运行processes框中的Implement。注意,如果Implement过程中报错端口连接不完

全,应返回ILA配置检查端口是否全部连接。

右键单击Generate Programming File,点击properties,在startup options中将start-up clock设为JTAG clock,点

击ok。

运行Generate Programming File,生成.bit文件。

4. 利用Analyzer观察信号波形

运行process框中的analyze design using chipscope,进入chipscope pro analyzer。

4.1 连接器件

单击左上角file下面的图标,连接到器件,弹出对话框选ok。

分区 Xilinx_FPGA 的第 2 页

�

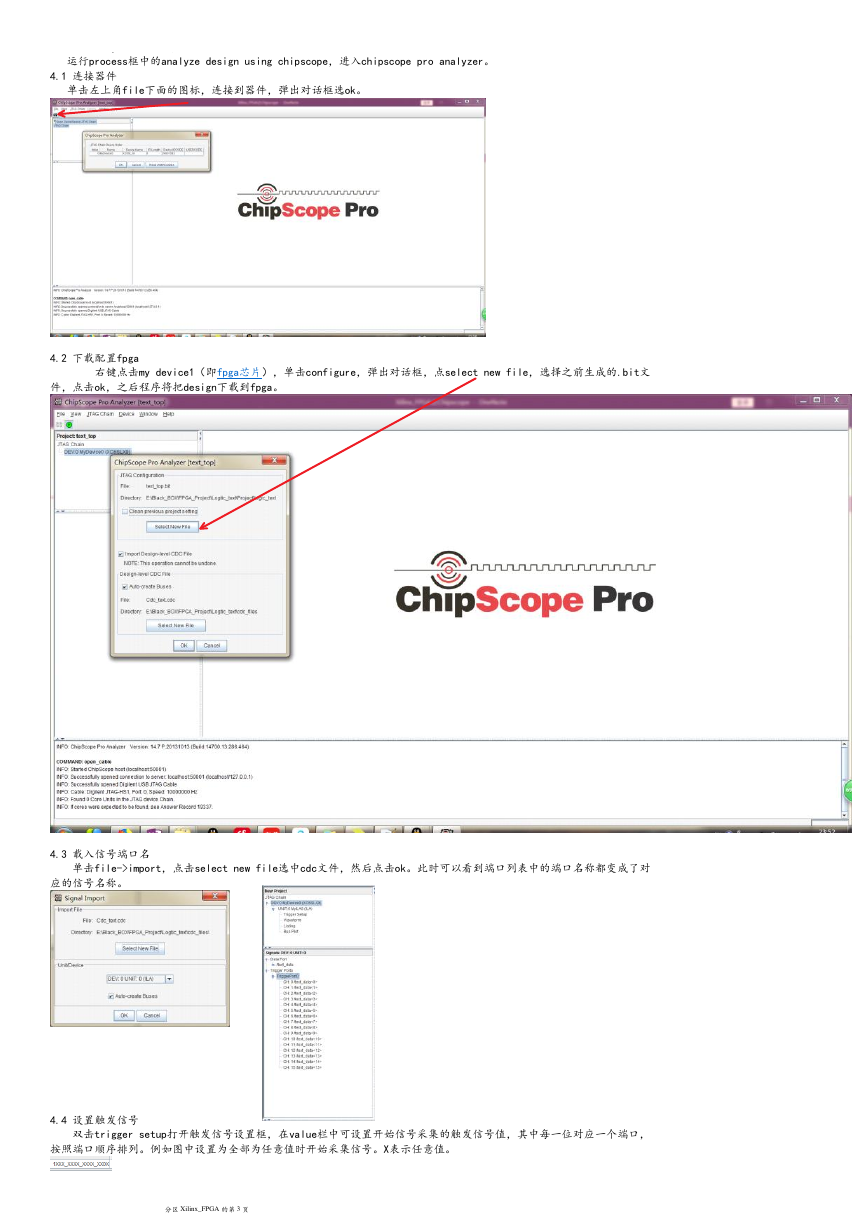

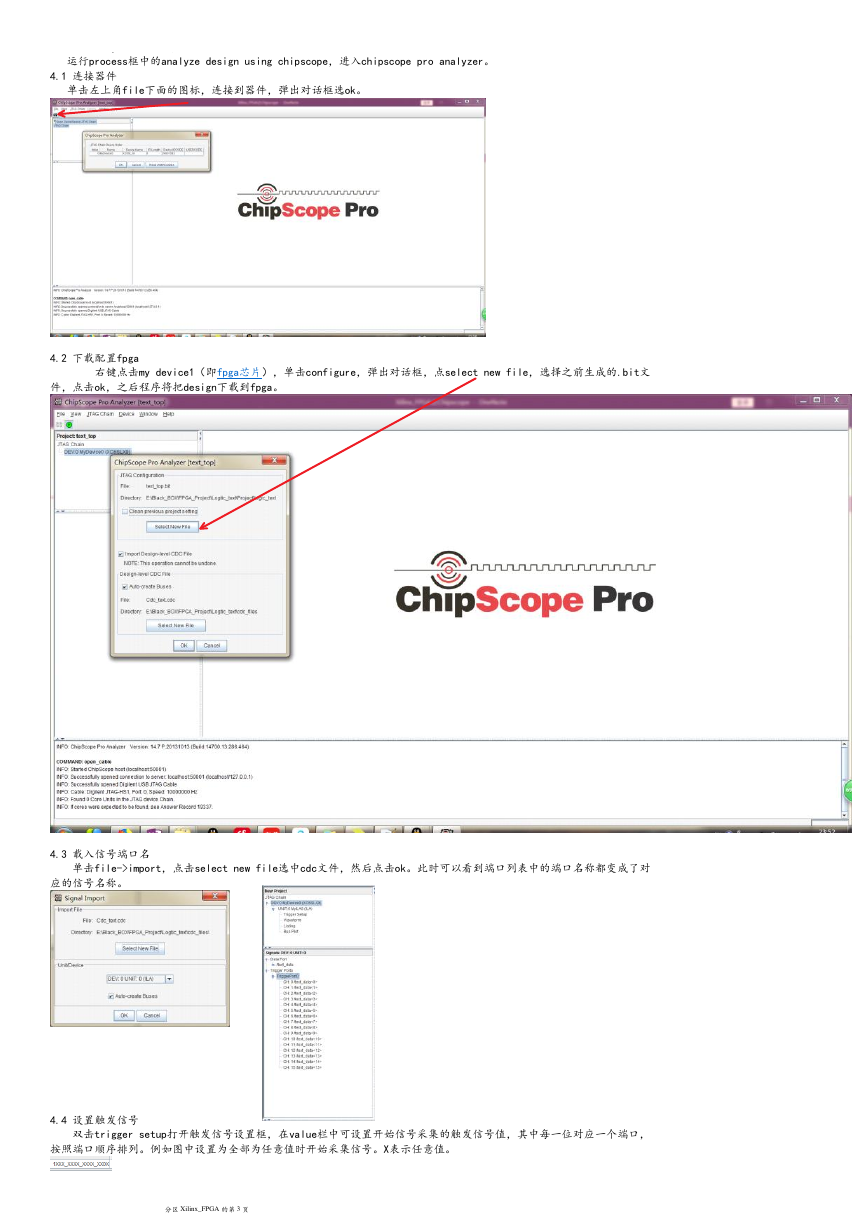

4. 利用Analyzer观察信号波形

运行process框中的analyze design using chipscope,进入chipscope pro analyzer。

4.1 连接器件

单击左上角file下面的图标,连接到器件,弹出对话框选ok。

4.2 下载配置fpga

右键点击my device1(即fpga芯片),单击configure,弹出对话框,点select new file,选择之前生成的.bit文

件,点击ok,之后程序将把design下载到fpga。

4.3 载入信号端口名

单击file->import,点击select new file选中cdc文件,然后点击ok。此时可以看到端口列表中的端口名称都变成了对

应的信号名称。

4.4 设置触发信号

双击trigger setup打开触发信号设置框,在value栏中可设置开始信号采集的触发信号值,其中每一位对应一个端口,

按照端口顺序排列。例如图中设置为全部为任意值时开始采集信号。X表示任意值。

这样表示当15位为1时,第1位为0时开始采集信号

分区 Xilinx_FPGA 的第 3 页

�

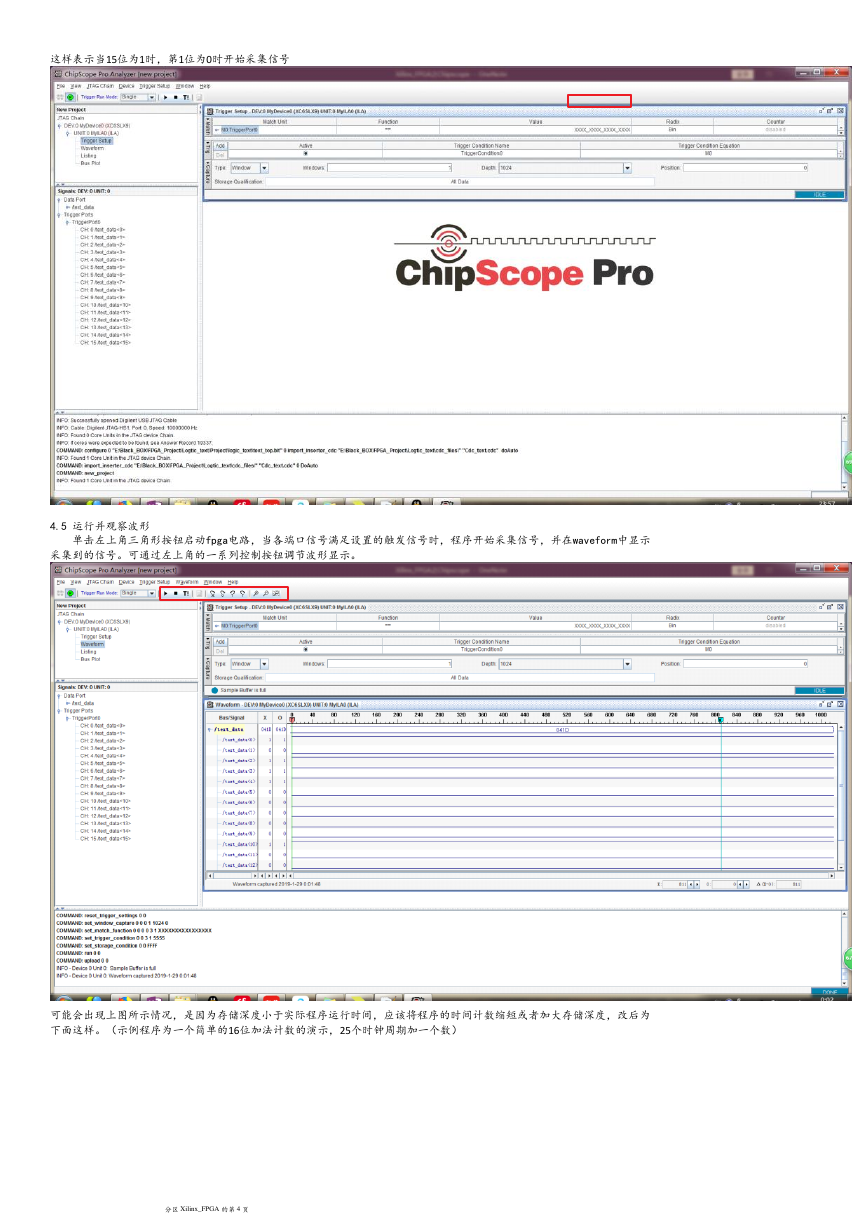

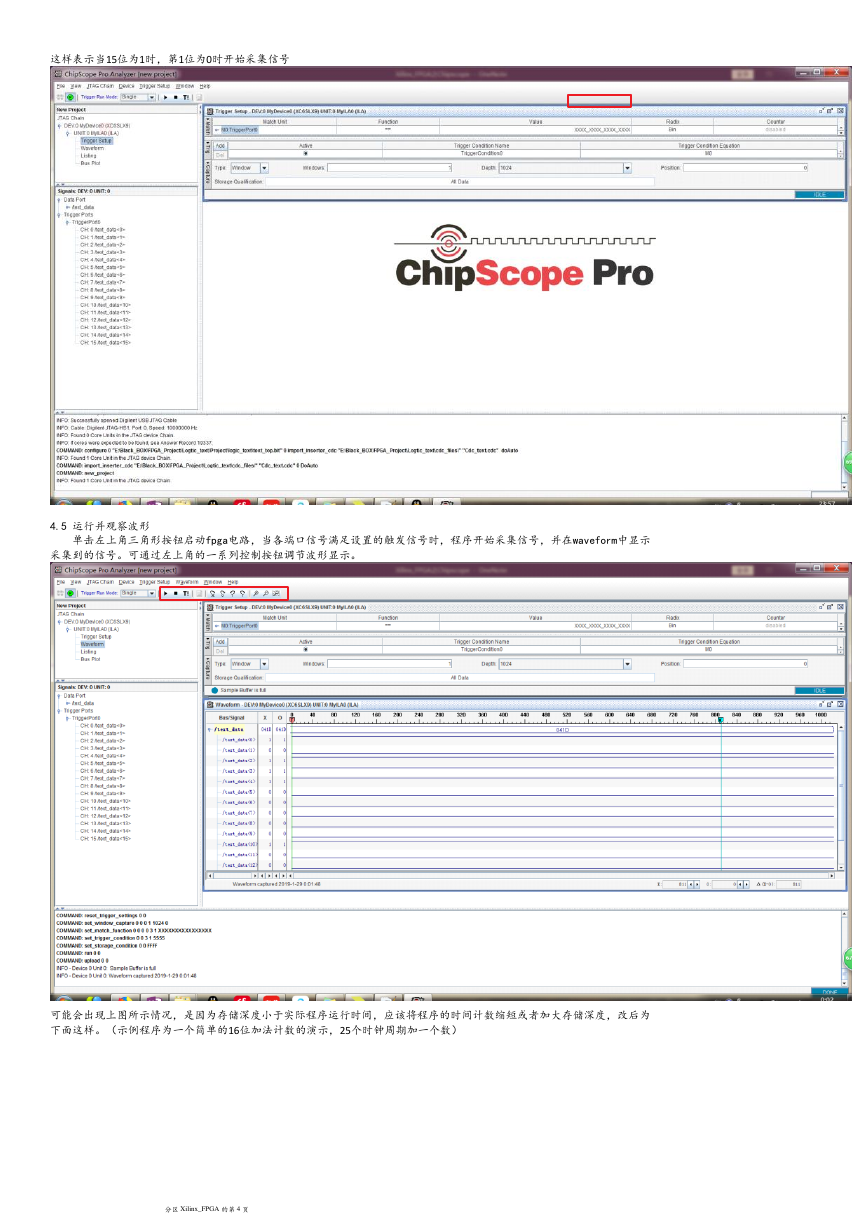

这样表示当15位为1时,第1位为0时开始采集信号

4.5 运行并观察波形

单击左上角三角形按钮启动fpga电路,当各端口信号满足设置的触发信号时,程序开始采集信号,并在waveform中显示

采集到的信号。可通过左上角的一系列控制按钮调节波形显示。

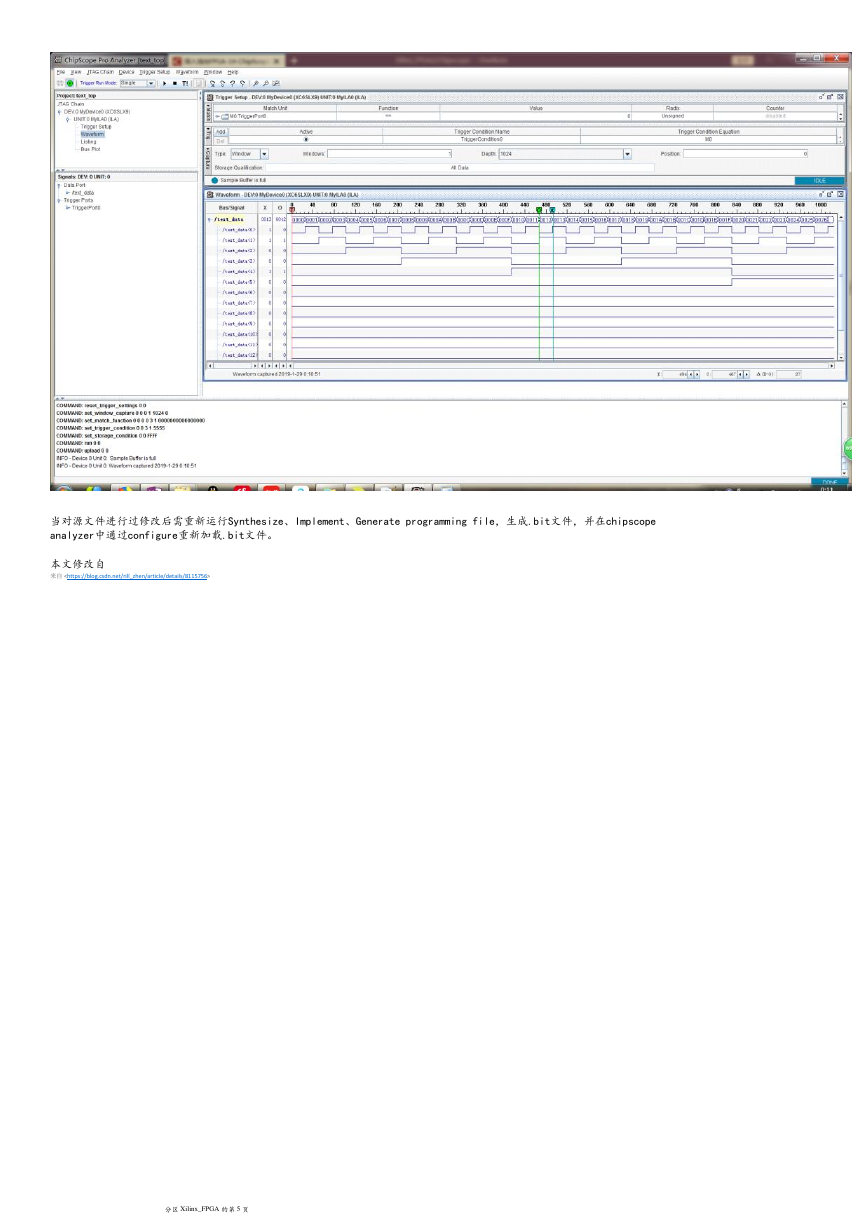

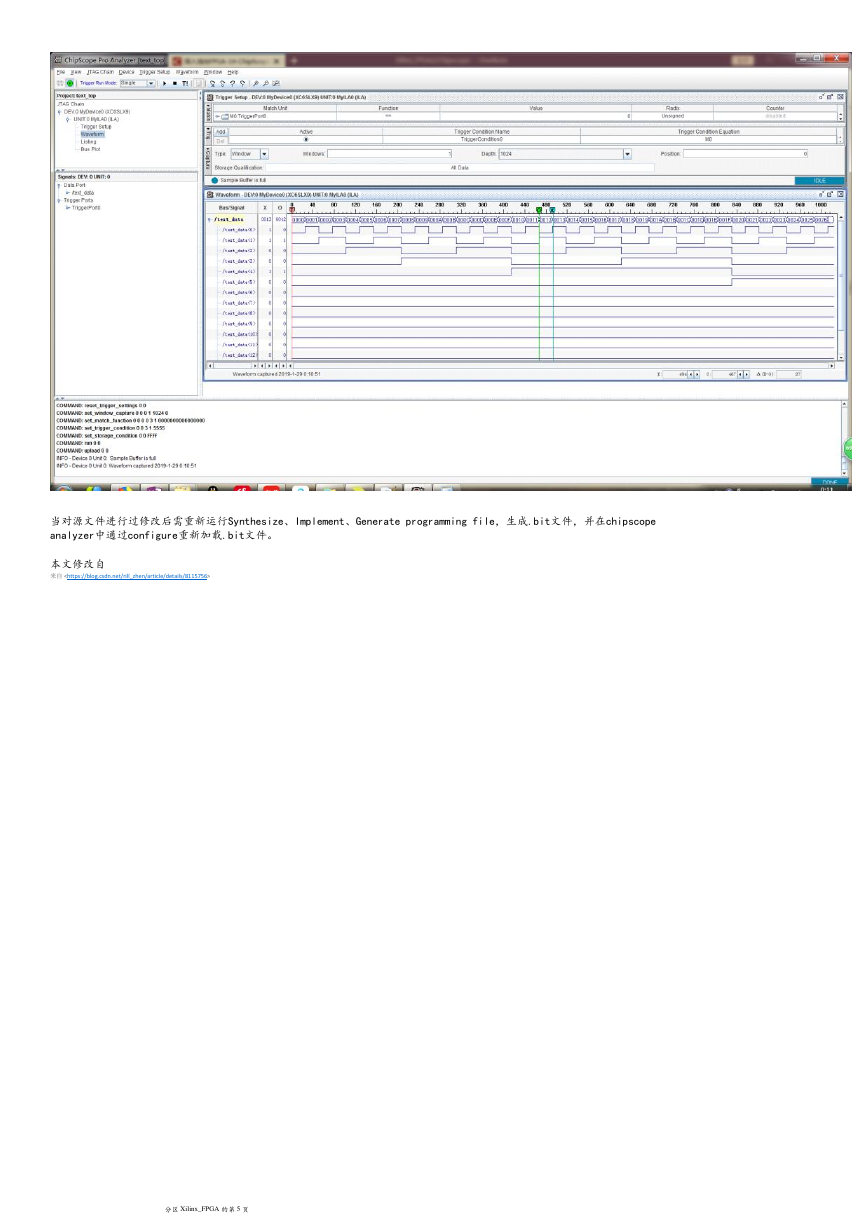

可能会出现上图所示情况,是因为存储深度小于实际程序运行时间,应该将程序的时间计数缩短或者加大存储深度,改后为

下面这样。(示例程序为一个简单的16位加法计数的演示,25个时钟周期加一个数)

分区 Xilinx_FPGA 的第 4 页

�

当对源文件进行过修改后需重新运行Synthesize、Implement、Generate programming file,生成.bit文件,并在chipscope

analyzer中通过configure重新加载.bit文件。

本文修改自

来自

分区 Xilinx_FPGA 的第 5 页

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc