专题报道

以 C P L D 为控制核心的

16 位高精度数字电压表设计

李秀梅, 李学华, 陆坤

(成都理工大学信息工程学院, 四川 成都,610059)

摘要:介绍了基于 E D A 技术的智能数字电压表的实现。本系统以 C P L D 为控制核心,在 M A X + P L U S

I I 环境下采用 V H D L 语言实现了数据采集、转换及显示。该系统具有集成度高、灵活性强、易于开发、

维 护 、 扩 展 等 特 点 。

关 键 词 :C P L D ;V H D L ;D V M

中图分类号:TP332;TM93 文献标识码:A 文章编号:1003-353X(2003)05-0054-03

Design of 16-bit high precision DVM based on CPLD

(Institute of Information Engineering , Chengdu University of Technology ,Chengdu 610059,China)

LI Xiu-mei,LI Xue-hua,LU Kun

A b s t r a c t : The implementation of the intelligent digital voltage meter based on EDA technology

is introduced. As the kernel of this system, CPLD implements data acquisition, conversion and

display driver through VHDL under MAX+PLUS II integrated developing environment. It features

the whole system with high integrity, good flexibility and better reliability. As a result, it is easy to

update, to maintain and to expand.

K e y w o r d s : CPLD ;VHDL ;D V M

1 引 言

CPLD ( Complex Programmable Logic Device ) 是

新型的可编程逻辑器件,与传统 ASIC 相比,具有

设计开发周期短、设计制造成本低、开发工具先进

等优点,特别适合于产品的样品开发和小批量生

产。传统的数字电压表多以单片机为控制核心,芯

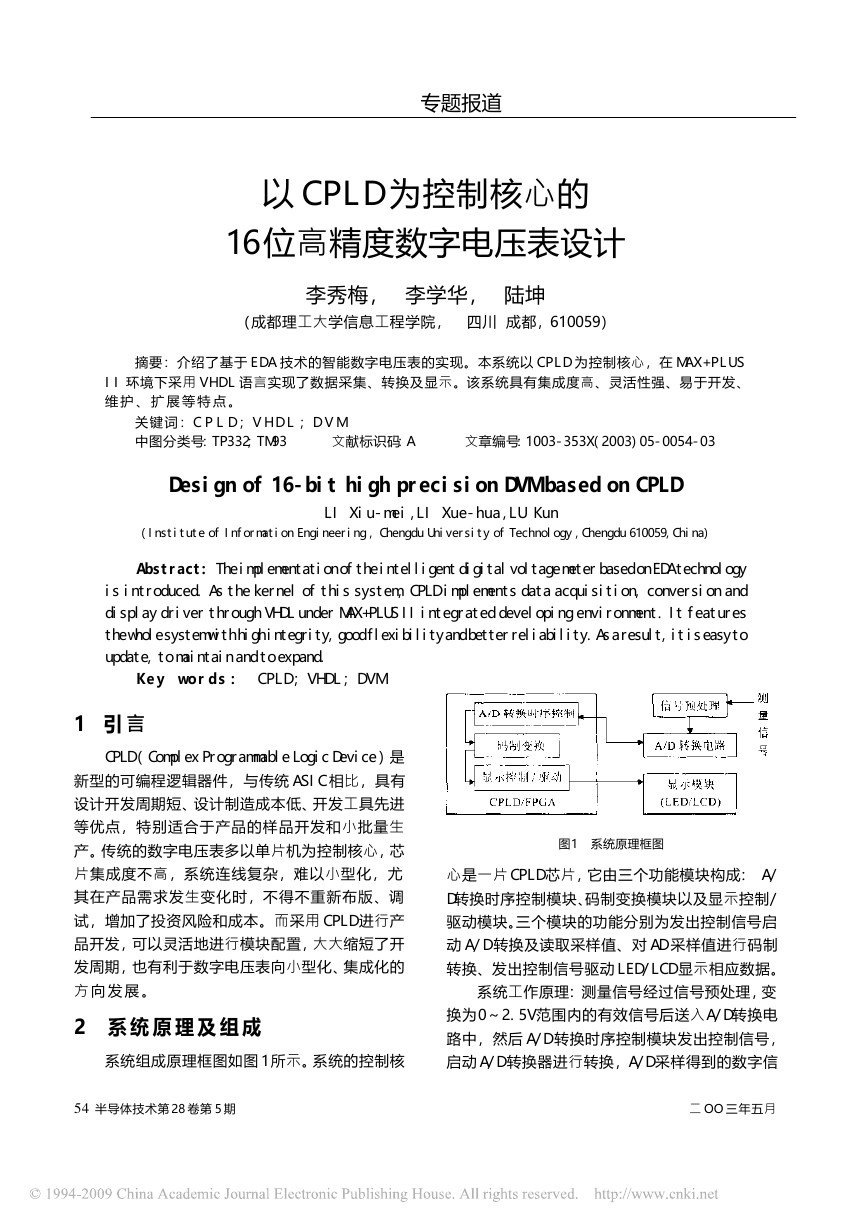

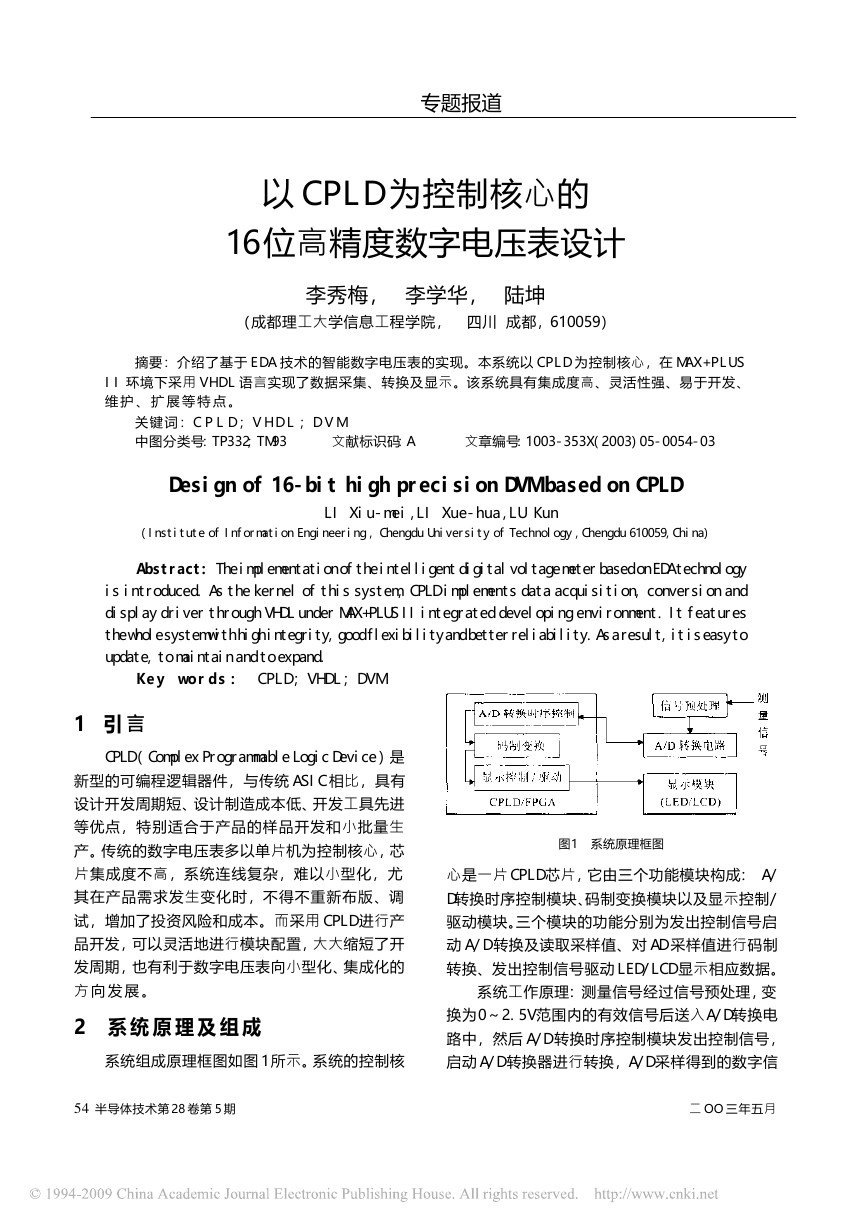

图1 系统原理框图

片集成度不高,系统连线复杂,难以小型化,尤

心是一片 CPLD 芯片,它由三个功能模块构成: A/

其在产品需求发生变化时,不得不重新布版、调

D转换时序控制模块、码制变换模块以及显示控制/

试,增加了投资风险和成本。而采用 CPLD 进行产

驱动模块。三个模块的功能分别为发出控制信号启

品开发,可以灵活地进行模块配置,大大缩短了开

动 A / D 转换及读取采样值、对 AD 采样值进行码制

发周期,也有利于数字电压表向小型化、集成化的

转换、发出控制信号驱动 LED/LCD 显示相应数据。

方 向 发 展 。

2 系 统 原 理 及 组 成

系统工作原理:测量信号经过信号预处理,变

换为0~2.5V 范围内的有效信号后送入A/D 转换电

路中,然后 A/D 转换时序控制模块发出控制信号,

系统组成原理框图如图 1 所示。系统的控制核

启动 A/D 转换器进行转换,A/D 采样得到的数字信

54

半导体技术第 28 卷第 5 期

二 O O 三年五月

�

专题报道

号在码制变换模块中转换为相应的显示代码,最后

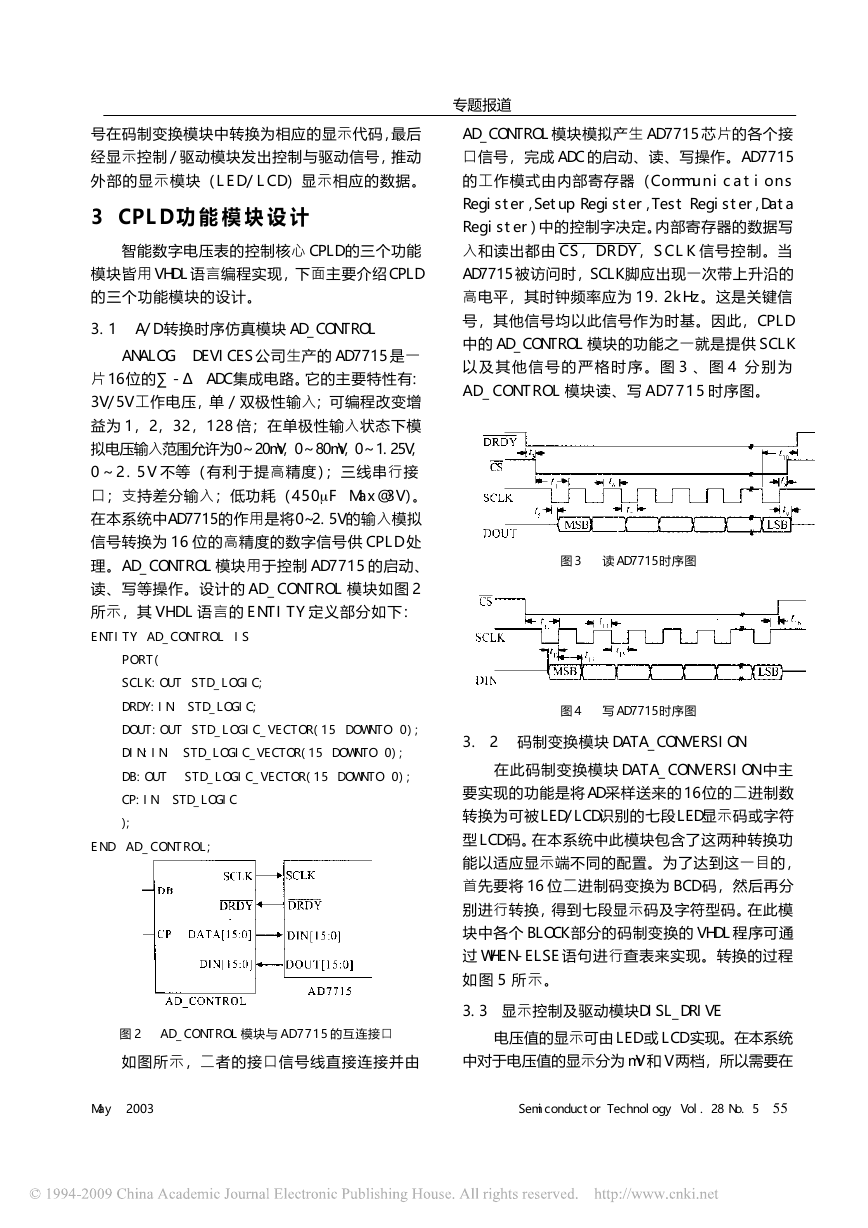

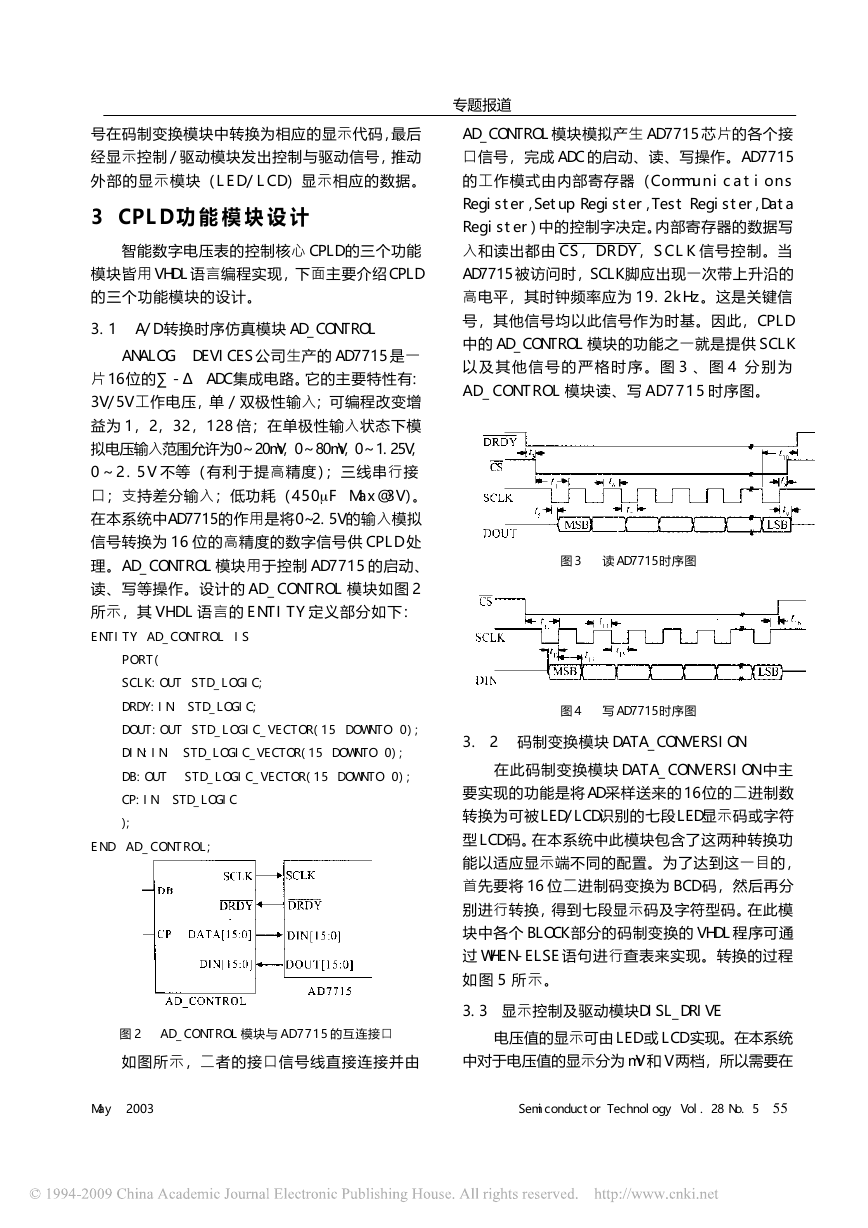

AD_CONTROL 模块模拟产生 AD7715 芯片的各个接

经显示控制 / 驱动模块发出控制与驱动信号,推动

口信号,完成 ADC 的启动、读、写操作。A D 7 7 1 5

外部的显示模块(L E D / L C D )显示相应的数据。

的工作模式由内部寄存器(C o m m u n i c a t i o n s

3 C P L D 功 能 模 块 设 计

Register,Setup Register,Test Register,Data

Register)中的控制字决定。内部寄存器的数据写

智能数字电压表的控制核心 CPLD 的三个功能

入和读出都由 C S ,D R D Y ,S C L K 信号控制。当

模块皆用 VHDL 语言编程实现,下面主要介绍 CPLD

AD7715 被访问时,SCLK 脚应出现一次带上升沿的

的三个功能模块的设计。

高电平,其时钟频率应为 1 9 . 2 k H z。这是关键信

3.1 A/D 转换时序仿真模块 AD_CONTROL

ANALOG DEVICES 公司生产的 AD7715 是一

片 16 位的∑- Δ ADC 集成电路。它的主要特性有:

3V/5V 工作电压,单/双极性输入;可编程改变增

益为 1 ,2,3 2 ,1 2 8 倍;在单极性输入状态下模

拟电压输入范围允许为0~20mV, 0~80mV, 0~1.25V,

0 ~2 . 5 V 不等(有利于提高精度);三线串行接

口;支持差分输入;低功耗(4 5 0m F M a x @ 3 V )。

在本系统中AD7715的作用是将0~2.5V的输入模拟

信号转换为 1 6 位的高精度的数字信号供 C P L D 处

理。A D _ C O N T R O L 模块用于控制 A D 7 7 1 5 的启动、

读、写等操作。设计的 A D _ C O N T R O L 模块如图 2

所示,其 V H D L 语言的 E N T I T Y 定义部分如下:

E N T I T Y A D _ C O N T R O L I S

P O R T (

S C L K : O U T S T D _ L O G I C ;

D R D Y : I N S T D _ L O G I C ;

D O U T : O U T S T D _ L O G I C _ V E C T O R ( 1 5 D O W N T O 0 ) ;

D I N : I N S T D _ L O G I C _ V E C T O R ( 1 5 D O W N T O 0 ) ;

D B : O U T S T D _ L O G I C _ V E C T O R ( 1 5 D O W N T O 0 ) ;

C P : I N S T D _ L O G I C

);

E N D A D _ C O N T R O L ;

号,其他信号均以此信号作为时基。因此,C P L D

中的 AD_CONTROL 模块的功能之一就是提供 S C L K

以 及 其 他 信 号 的 严 格 时 序 。图 3 、图 4 分 别 为

A D _ C O N T R O L 模块读、写 A D 7 7 1 5 时序图。

图 3 读 AD7715 时序图

图 4 写 AD7715 时序图

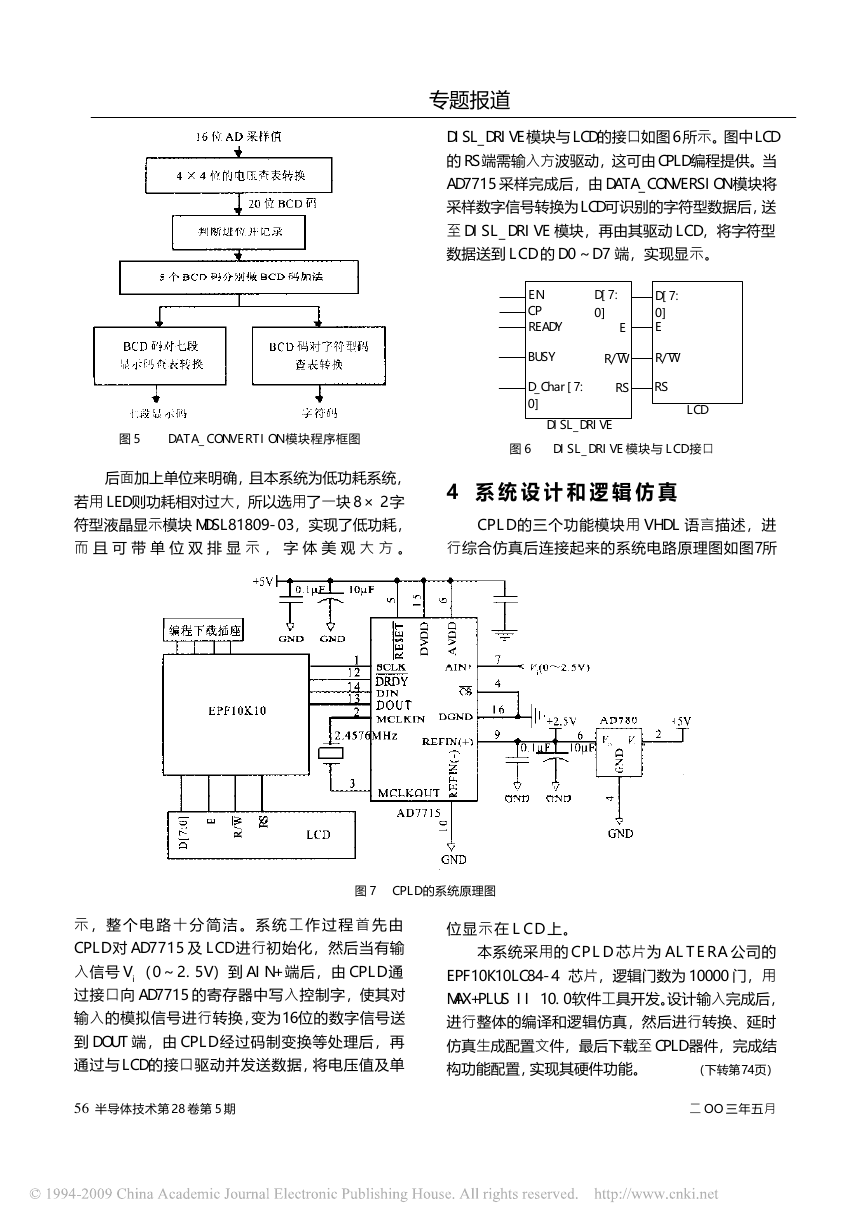

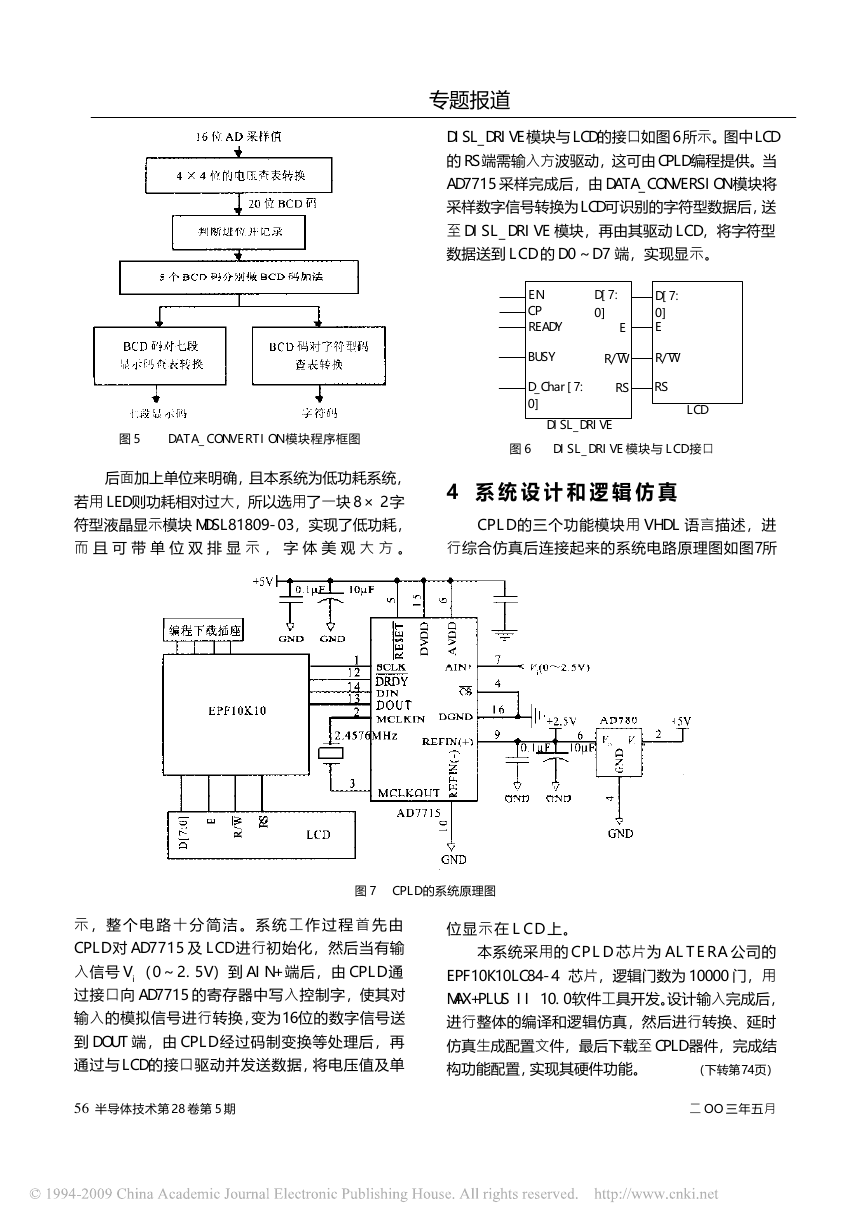

3 . 2 码制变换模块 DATA_CONVERSION

在此码制变换模块 D A T A _ C O N V E R S I O N 中主

要实现的功能是将 AD 采样送来的 16 位的二进制数

转换为可被LED/LCD识别的七段LED显示码或字符

型 LCD 码。在本系统中此模块包含了这两种转换功

能以适应显示端不同的配置。为了达到这一目的,

首先要将 16 位二进制码变换为 B C D 码,然后再分

别进行转换,得到七段显示码及字符型码。在此模

块中各个 BLOCK 部分的码制变换的 VHDL 程序可通

过 WHEN-ELSE 语句进行查表来实现。转换的过程

如图 5 所示。

3.3 显示控制及驱动模块DISL_DRIVE

图 2 A D _ C O N T R O L 模块与 A D 7 7 1 5 的互连接口

电压值的显示可由 LED 或 L C D 实现。在本系统

如图所示,二者的接口信号线直接连接并由

中对于电压值的显示分为 mV 和 V 两档,所以需要在

May 2003

Semiconductor Technology Vol. 28 No. 5

55

�

专题报道

DISL_DRIVE 模块与 LCD 的接口如图 6 所示。图中LCD

的 RS 端需输入方波驱动,这可由 CPLD 编程提供。当

AD7715 采样完成后,由 DATA_CONVERSION 模块将

采样数字信号转换为LCD 可识别的字符型数据后,送

至 DISL_DRIVE 模块,再由其驱动 LCD ,将字符型

数据送到 L C D 的 D 0 ~D 7 端,实现显示。

EN

CP

READY

BUSY

D_Char[7:

0]

D[7:

0]

E

D[7:

0]

E

R/W

R/W

RS

RS

DISL_DRIVE

LCD

图 6 DISL_DRIVE 模块与 L C D 接口

图 5 D A T A _ C O N V E R T I O N 模块程序框图

后面加上单位来明确,且本系统为低功耗系统,

若用 LED 则功耗相对过大,所以选用了一块 8 × 2 字

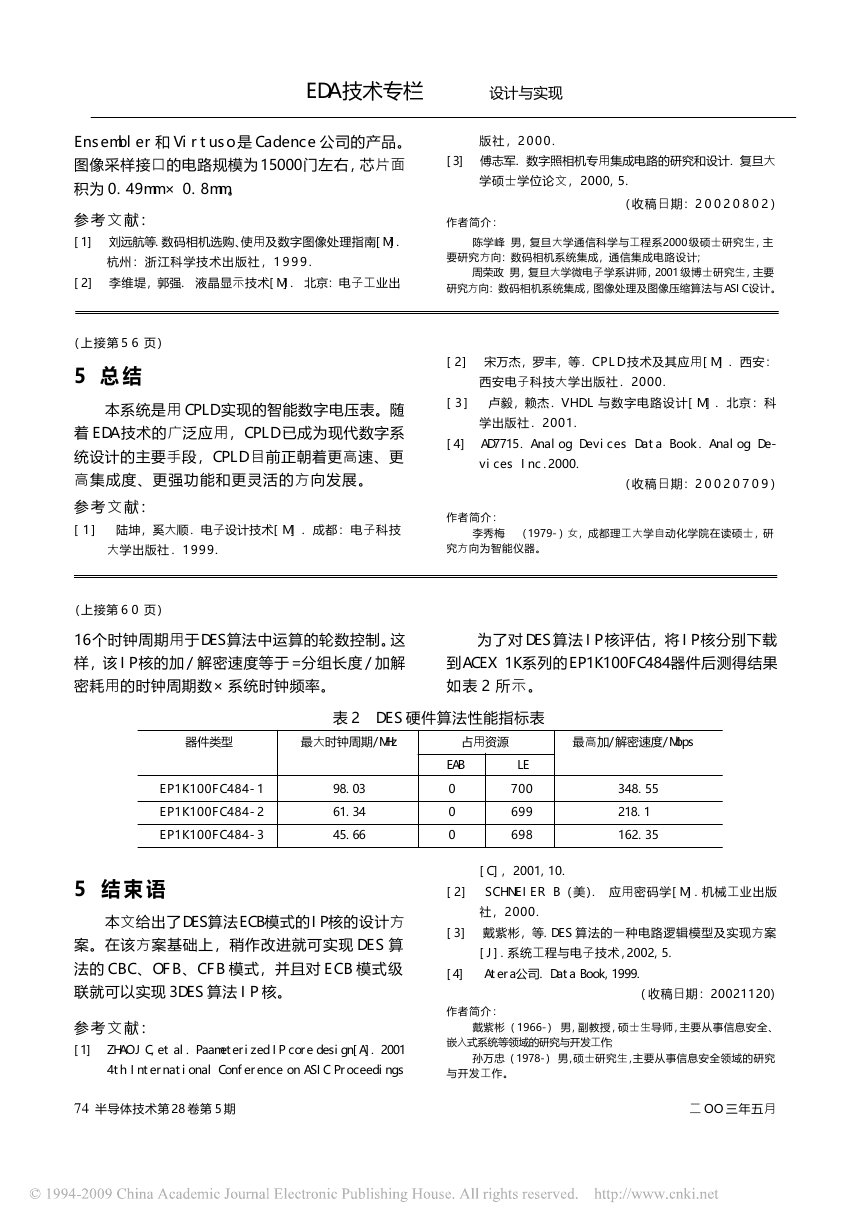

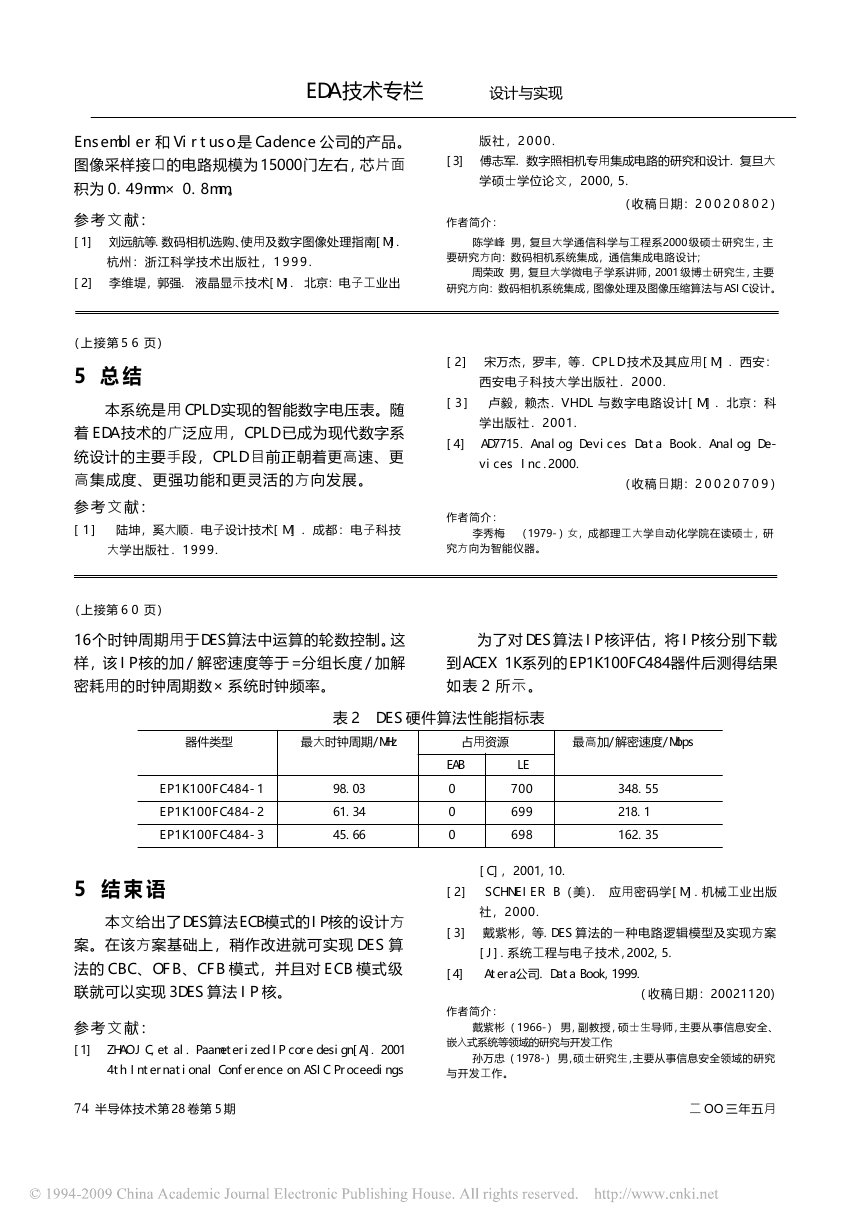

4 系 统 设 计 和 逻 辑 仿 真

符型液晶显示模块 MDSL81809-03,实现了低功耗,

C P L D 的三个功能模块用 V H D L 语言描述,进

而 且 可 带 单 位 双 排 显 示 , 字 体 美 观 大 方 。

行综合仿真后连接起来的系统电路原理图如图7所

图 7 C P L D 的系统原理图

示,整 个 电 路 十 分 简 洁 。系 统 工 作 过 程 首 先 由

位显示在 L C D 上。

C P L D 对 A D 7 7 1 5 及 L C D 进行初始化,然后当有输

i(0 ~2 . 5 V )到 A I N + 端后,由 C P L D 通

过接口向 AD7715 的寄存器中写入控制字,使其对

入信号 V

输入的模拟信号进行转换,变为16位的数字信号送

到 D O U T 端,由 C P L D 经过码制变换等处理后,再

通过与 LCD 的接口驱动并发送数据,将电压值及单

本系统采用的 C P L D 芯片为 A L T E R A 公司的

EPF10K10LC84-4 芯片,逻辑门数为 10000 门,用

MAX+PLUS II 10.0软件工具开发。设计输入完成后,

进行整体的编译和逻辑仿真,然后进行转换、延时

仿真生成配置文件,最后下载至 CPLD 器件,完成结

构功能配置,实现其硬件功能。 (下转第74页)

56

半导体技术第 28 卷第 5 期

二 O O 三年五月

�

EDA 技术专栏 设计与实现

Ensembler 和 Virtuso 是 Cadence 公司的产品。

版社,2 0 0 0 .

图像采样接口的电路规模为 15000 门左右,芯片面

[3] 傅志军. 数字照相机专用集成电路的研究和设计. 复旦大

积为 0 . 4 9 m m × 0 . 8 m m 。

参 考 文 献:

学硕士学位论文,2 0 0 0 , 5 .

(收稿日期:2 0 0 2 0 8 0 2 )

作者简介:

[1] 刘远航等.数码相机选购、使用及数字图像处理指南[M].

陈学峰 男,复旦大学通信科学与工程系2000 级硕士研究生,主

杭州:浙江科学技术出版社,1 9 9 9 .

[2] 李维堤,郭强. 液晶显示技术[M]. 北京:电子工业出

要研究方向:数码相机系统集成,通信集成电路设计;

周荣政 男,复旦大学微电子学系讲师,2001 级博士研究生,主要

研究方向:数码相机系统集成,图像处理及图像压缩算法与 ASIC 设计。

(上接第 5 6 页)

5 总 结

本系统是用 CPLD 实现的智能数字电压表。随

着 E D A 技术的广泛应用,CPLD 已成为现代数字系

统设计的主要手段,CPLD 目前正朝着更高速、更

高集成度、更强功能和更灵活的方向发展。

参 考 文 献:

[ 2 ] 宋万杰,罗丰,等.C P L D 技术及其应用[ M ] .西安:

西安电子科技大学出版社.2 0 0 0 .

[ 3 ] 卢毅,赖杰.V H D L 与数字电路设计[ M ] .北京:科

学出版社.2 0 0 1 .

[4] AD7715.Analog Devices Data Book.Analog De-

vices Inc.2000.

(收稿日期:2 0 0 2 0 7 0 9 )

作者简介:

[ 1 ] 陆坤,奚大顺.电子设计技术[ M ] .成都:电子科技

李秀梅 (1979-)女,成都理工大学自动化学院在读硕士,研

大学出版社.1 9 9 9 .

究方向为智能仪器。

(上接第 6 0 页)

16 个时钟周期用于DES 算法中运算的轮数控制。这

为了对 DES 算法 IP 核评估,将 IP 核分别下载

样,该 IP 核的加 / 解密速度等于 = 分组长度 / 加解

到ACEX 1K 系列的EP1K100FC484器件后测得结果

密耗用的时钟周期数×系统时钟频率。

如表 2 所示。

表 2 D E S 硬件算法性能指标表

器件类型 最大时钟周期/MHz 占用资源 最高加/解密速度/Mbps

EAB

LE

E P 1 K 1 0 0 F C 4 8 4 - 1

E P 1 K 1 0 0 F C 4 8 4 - 2

E P 1 K 1 0 0 F C 4 8 4 - 3

98.03

61.34

45.66

0

0

0

7 0 0

6 9 9

6 9 8

348.55

218.1

162.35

5 结 束 语

本文给出了DES算法ECB模式的IP核的设计方

案。在该方案基础上,稍作改进就可实现 D E S 算

法的 C B C 、O F B 、C F B 模式,并且对 E C B 模式级

联就可以实现 3DES 算法 I P 核。

参 考 文 献:

[1] ZHAO J C,et al. Paameterized IP core design[A]. 2001

[C],2001,10.

[ 2 ] S C H N E I E R B (美). 应用密码学[ M ] . 机械工业出版

社,2 0 0 0 .

[ 3 ] 戴紫彬,等. D E S 算法的一种电路逻辑模型及实现方案

[J].系统工程与电子技术,2002,5.

[4] Atera公司. Data Book,1999.

(收稿日期:2 0 0 2 1 1 2 0 )

作者简介:

戴紫彬 (1966-) 男,副教授,硕士生导师,主要从事信息安全、

嵌入式系统等领域的研究与开发工作;

孙万忠 (1978-) 男,硕士研究生,主要从事信息安全领域的研究

4th International Conference on ASIC Proceedings

与开发工作。

74

半导体技术第 28 卷第 5 期

二 O O 三年五月

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc