Introduction to general-purpose

SPC58 C Line automotive MCUs

April 2020

�

1

SPC58EC MCU and Discovery kit

2

SPC58xC Technical Capabilities

• Document resource

• MCU architecture & modules

• Development ecosystem

Agenda

3

SPC58xC reference design

4

SPC5Studio demo

• SPC58ECxx_RLA PIT Test Application for Discovery

2

�

SPC58EC MCU and Discovery kit

�

SPC58EC MCU and Discovery kit

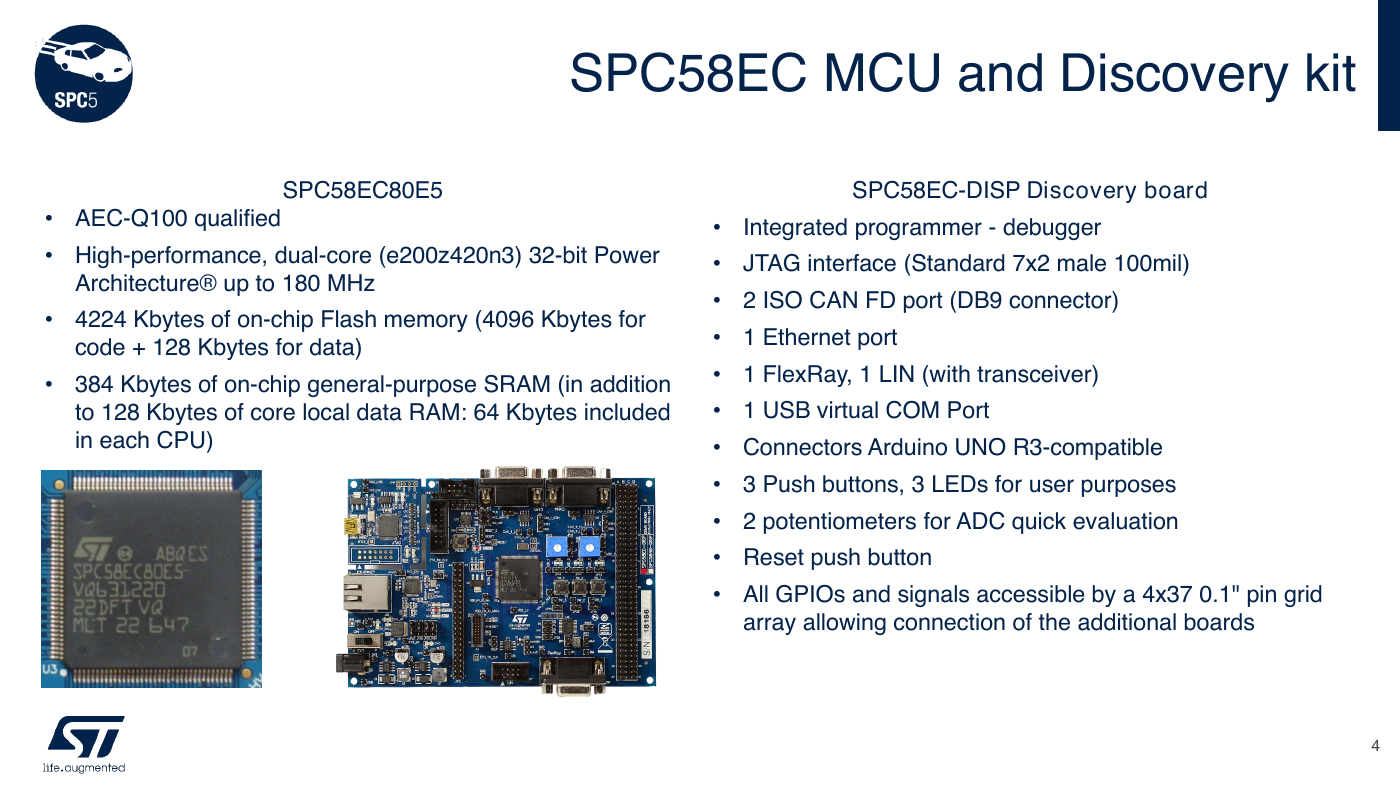

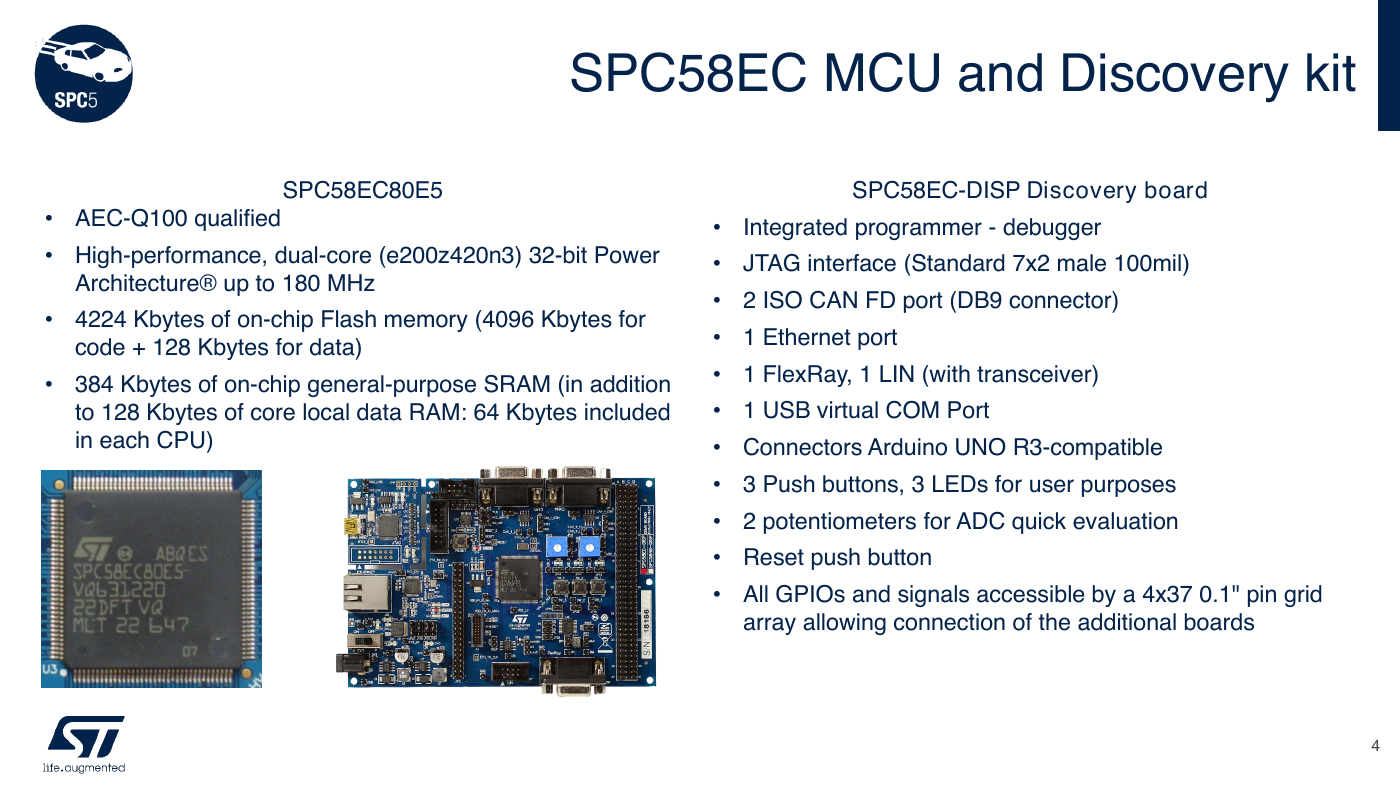

SPC58EC80E5

SPC58EC-DISP Discovery board

• AEC-Q100 qualified

• High-performance, dual-core (e200z420n3) 32-bit Power

Architecture® up to 180 MHz

• 4224 Kbytes of on-chip Flash memory (4096 Kbytes for

code + 128 Kbytes for data)

• 384 Kbytes of on-chip general-purpose SRAM (in addition

to 128 Kbytes of core local data RAM: 64 Kbytes included

in each CPU)

•

Integrated programmer - debugger

• JTAG interface (Standard 7x2 male 100mil)

• 2 ISO CAN FD port (DB9 connector)

• 1 Ethernet port

• 1 FlexRay, 1 LIN (with transceiver)

• 1 USB virtual COM Port

• Connectors Arduino UNO R3-compatible

• 3 Push buttons, 3 LEDs for user purposes

• 2 potentiometers for ADC quick evaluation

• Reset push button

• All GPIOs and signals accessible by a 4x37 0.1" pin grid

array allowing connection of the additional boards

4

�

SPC58 C Line technical capabilities

�

SPC58 C Line document resources

All SPC5 products and tools come with a complete set of document resources for developers

including:

• Databriefs, datasheets and errata sheets

• Technical notes

• Application notes

• User manuals

Visit the SPC58 C Line webpage for a complete list of available resources.

6

�

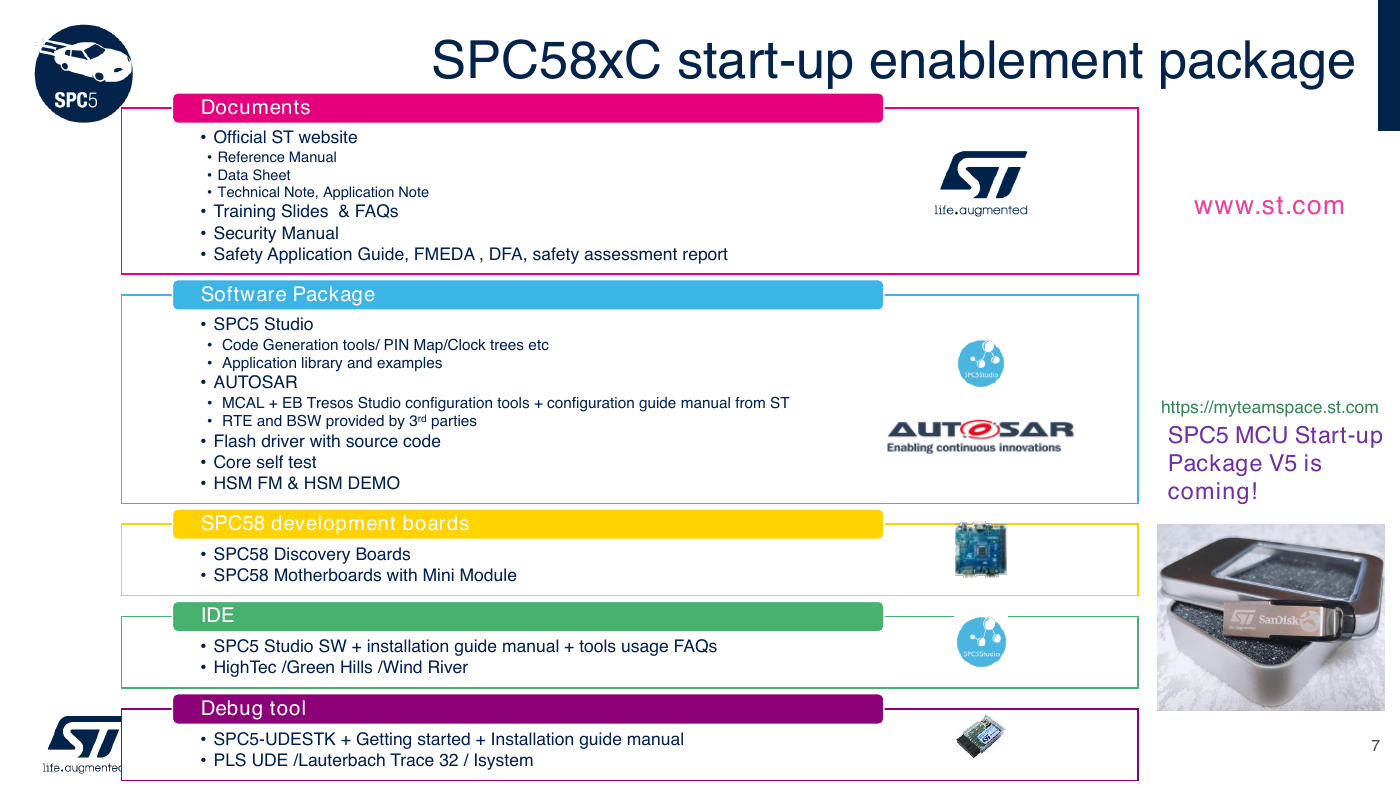

SPC58xC start-up enablement package

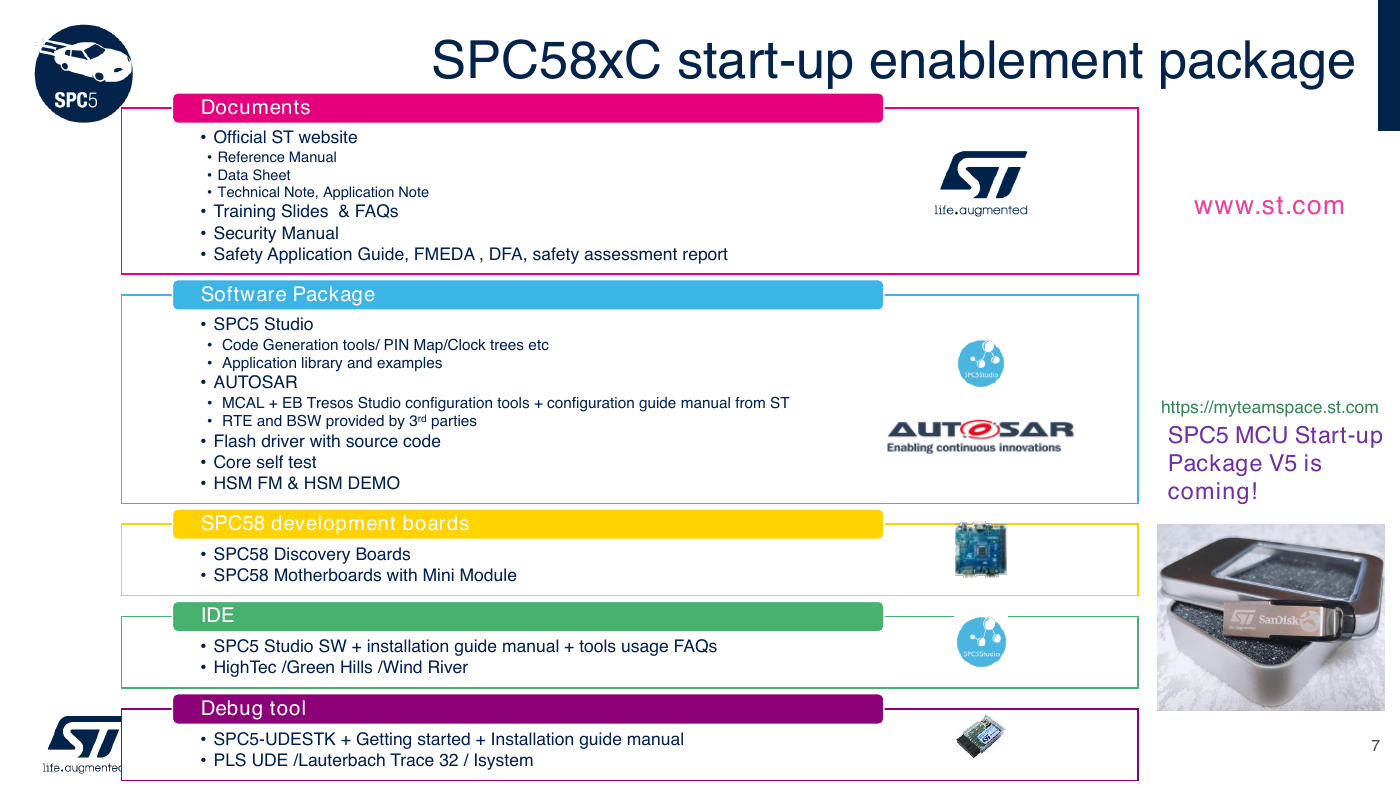

Documents

• Official ST website

• Reference Manual

• Data Sheet

• Technical Note, Application Note

• Training Slides & FAQs

• Security Manual

• Safety Application Guide, FMEDA , DFA, safety assessment report

Software Package

• SPC5 Studio

• Code Generation tools/ PIN Map/Clock trees etc

• Application library and examples

• AUTOSAR

• MCAL + EB Tresos Studio configuration tools + configuration guide manual from ST

• RTE and BSW provided by 3rd parties

• Flash driver with source code

• Core self test

• HSM FM & HSM DEMO

SPC58 development boards

• SPC58 Discovery Boards

• SPC58 Motherboards with Mini Module

IDE

• SPC5 Studio SW + installation guide manual + tools usage FAQs

• HighTec /Green Hills /Wind River

Debug tool

• SPC5-UDESTK + Getting started + Installation guide manual

• PLS UDE /Lauterbach Trace 32 / Isystem

www.st.com

https://myteamspace.st.com

SPC5 MCU Start-up

Package V5 is

coming!

7

�

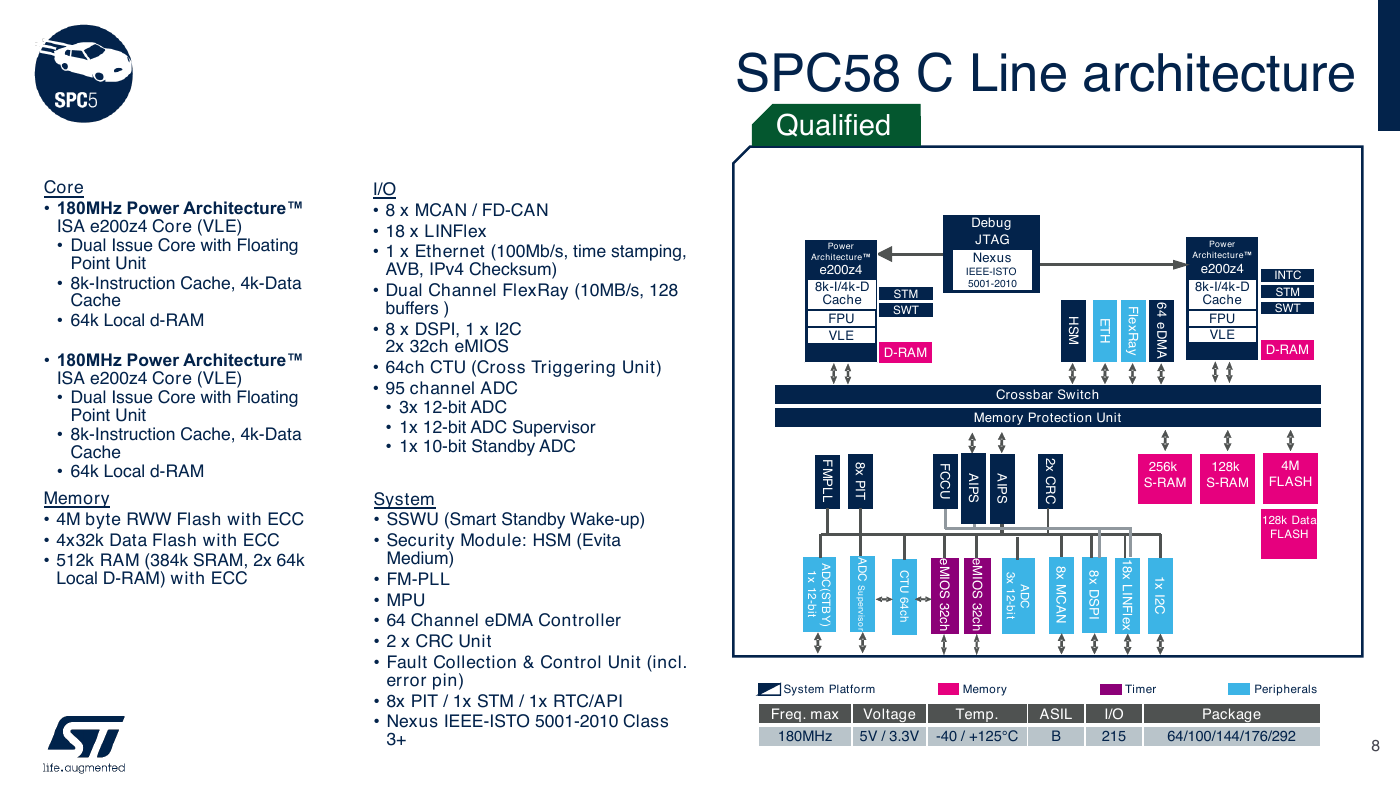

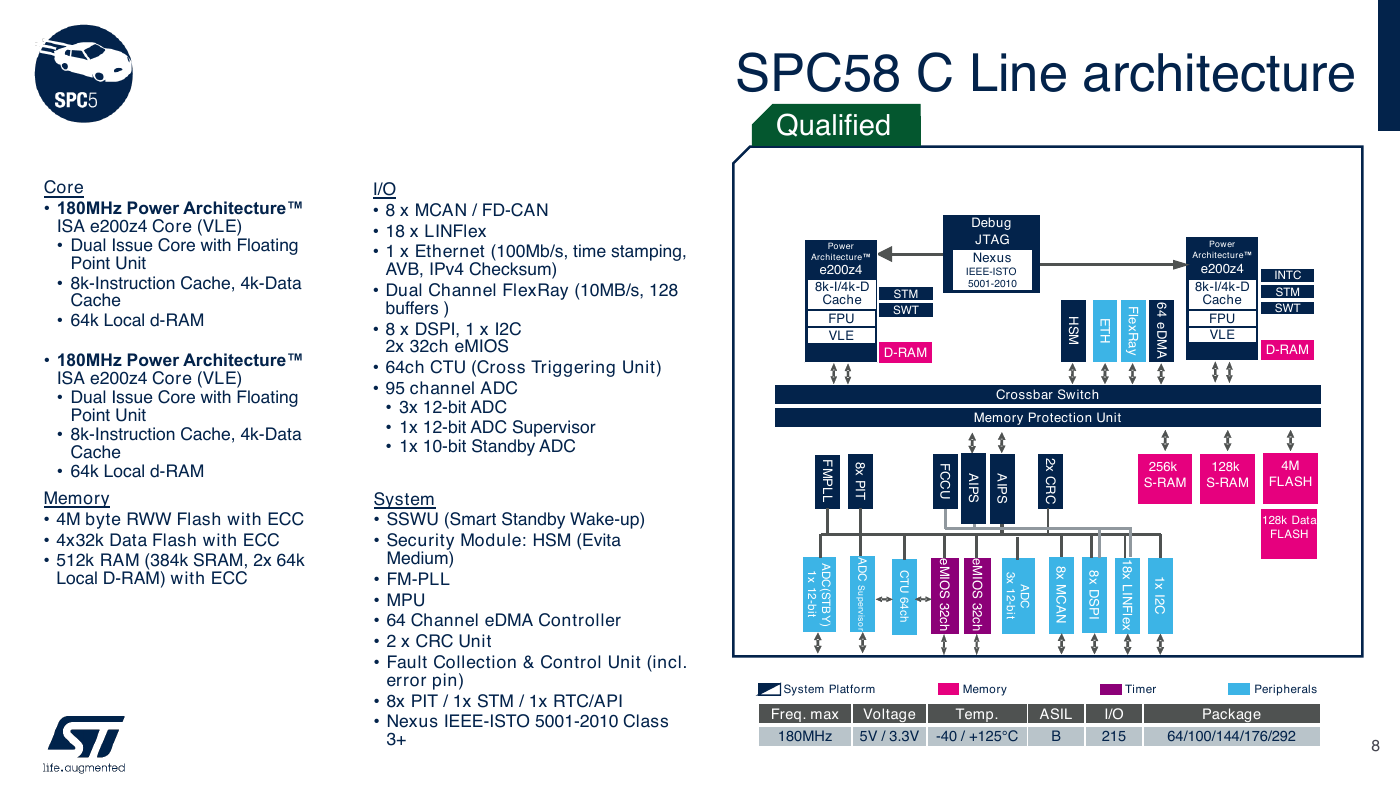

Core

• 180MHz Power Architecture™

ISA e200z4 Core (VLE)

• Dual Issue Core with Floating

Point Unit

• 8k-Instruction Cache, 4k-Data

Cache

• 64k Local d-RAM

• 180MHz Power Architecture™

ISA e200z4 Core (VLE)

• Dual Issue Core with Floating

Point Unit

• 8k-Instruction Cache, 4k-Data

Cache

• 64k Local d-RAM

Memory

• 4M byte RWW Flash with ECC

• 4x32k Data Flash with ECC

• 512k RAM (384k SRAM, 2x 64k

Local D-RAM) with ECC

I/O

• 8 x MCAN / FD-CAN

• 18 x LINFlex

• 1 x Ethernet (100Mb/s, time stamping,

AVB, IPv4 Checksum)

• Dual Channel FlexRay (10MB/s, 128

buffers )

• 8 x DSPI, 1 x I2C

2x 32ch eMIOS

• 64ch CTU (Cross Triggering Unit)

• 95 channel ADC

• 3x 12-bit ADC

• 1x 12-bit ADC Supervisor

• 1x 10-bit Standby ADC

System

• SSWU (Smart Standby Wake-up)

• Security Module: HSM (Evita

Medium)

• FM-PLL

• MPU

• 64 Channel eDMA Controller

• 2 x CRC Unit

• Fault Collection & Control Unit (incl.

error pin)

• 8x PIT / 1x STM / 1x RTC/API

• Nexus IEEE-ISTO 5001-2010 Class

3+

SPC58 C Line architecture

Qualified

Debug

JTAG

Nexus

IEEE-ISTO

5001-2010

Power

Architecture™

e200z4

8k-I/4k-D

Cache

FPU

VLE

STM

SWT

D-RAM

Power

Architecture™

e200z4

8k-I/4k-D

Cache

FPU

VLE

INTC

STM

SWT

D-RAM

H

S

M

E

T

H

F

l

e

x

R

a

y

6

4

e

D

M

A

Crossbar Switch

Memory Protection Unit

F

C

C

U

I

e

M

O

S

3

2

c

h

I

A

P

S

I

A

P

S

2

x

C

R

C

256k

S-RAM

128k

S-RAM

4M

FLASH

128k Data

FLASH

I

e

M

O

S

3

2

c

h

3

x

1

2

-

b

i

t

A

D

C

8

x

M

C

A

N

8

x

D

S

P

I

I

1

8

x

L

N

F

l

e

x

1

x

I

2

C

F

M

P

L

L

8

x

P

T

I

1

x

1

2

-

b

i

t

(

A

D

C

S

T

B

Y

)

A

D

C

S

u

p

e

r

v

i

s

o

r

C

T

U

6

4

c

h

System Platform

Memory

Timer

Peripherals

Freq. max

Voltage

Temp.

ASIL

180MHz

5V / 3.3V -40 / +125°C

B

I/O

215

Package

64/100/144/176/292

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc