MC9S12DP256/DG128

Hardware & Basic System Design

清华 Freescale MCU/DSP应用开发研究中心

�

Chinese Textbook

2007 修订本

2006 修订本

�

CPU12 Reference Book

458pages

�

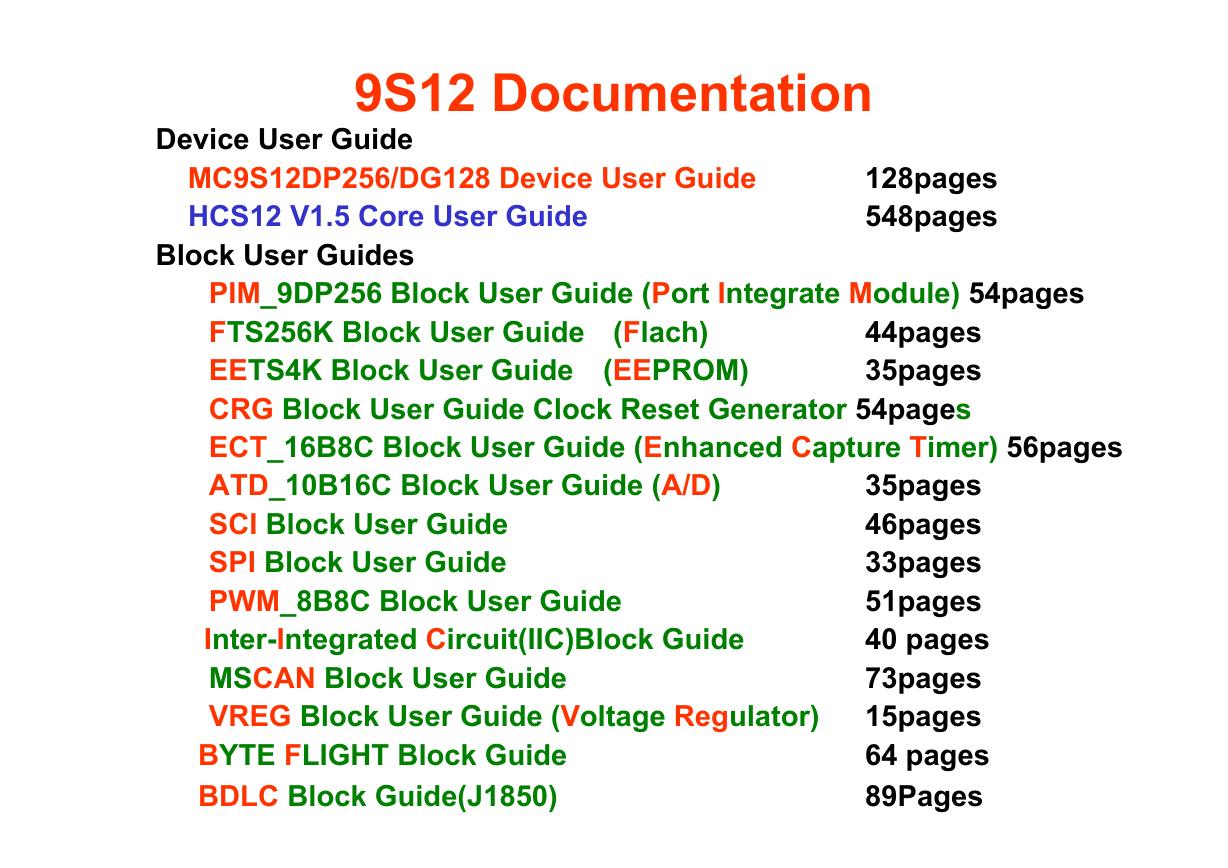

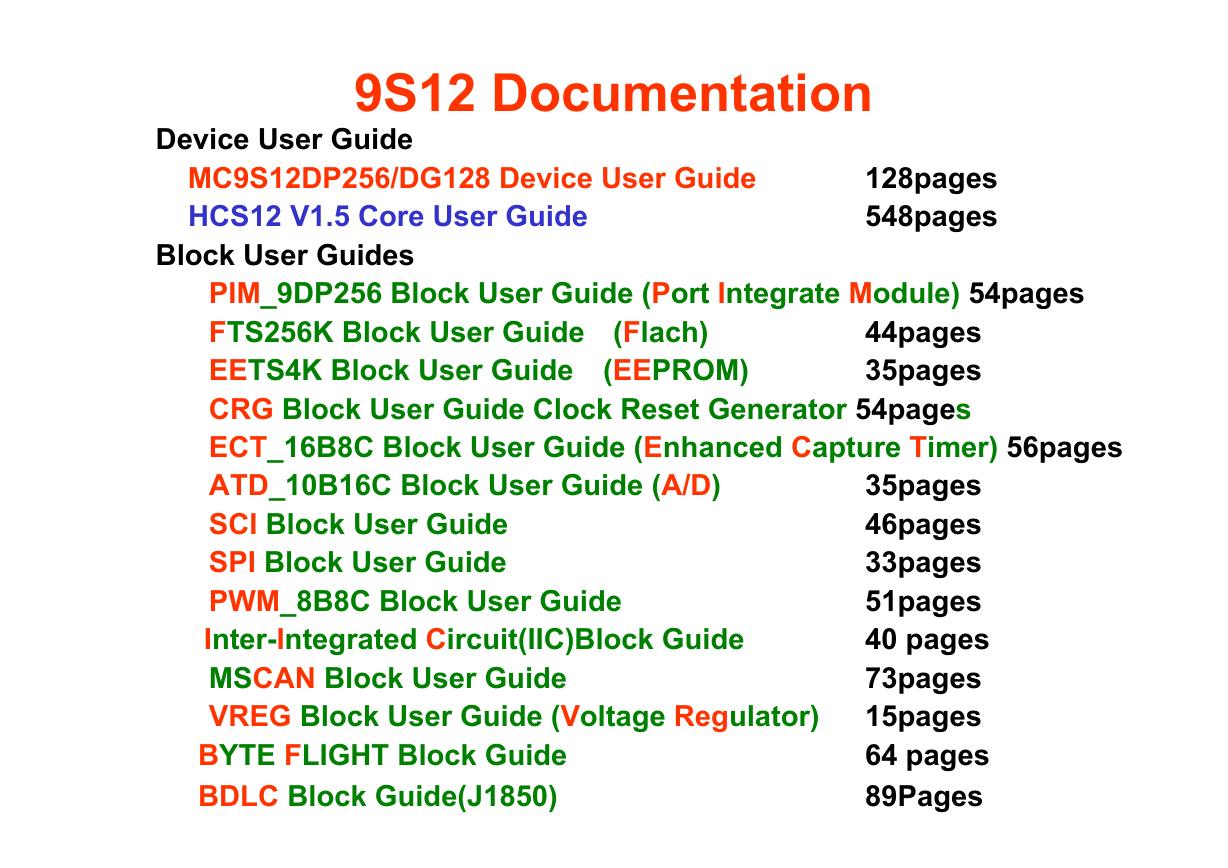

9S12 Documentation

MC9S12DP256/DG128 Device User Guide

HCS12 V1.5 Core User Guide

128pages

548pages

Device User Guide

Block User Guides

PIM_9DP256 Block User Guide (Port Integrate Module) 54pages

44pages

FTS256K Block User Guide (Flach)

EETS4K Block User Guide (EEPROM)

35pages

CRG Block User Guide Clock Reset Generator 54pages

ECT_16B8C Block User Guide (Enhanced Capture Timer) 56pages

ATD_10B16C Block User Guide (A/D)

SCI Block User Guide

SPI Block User Guide

PWM_8B8C Block User Guide

Inter-Integrated Circuit(IIC)Block Guide

MSCAN Block User Guide

VREG Block User Guide (Voltage Regulator)

BYTE FLIGHT Block Guide

BDLC Block Guide(J1850)

35pages

46pages

33pages

51pages

40 pages

73pages

15pages

64 pages

89Pages

�

Reference Manual

(Hardware)

122 pages (2.1M)

Data book

9S12DT128B manual

9S12DP256B manual

�

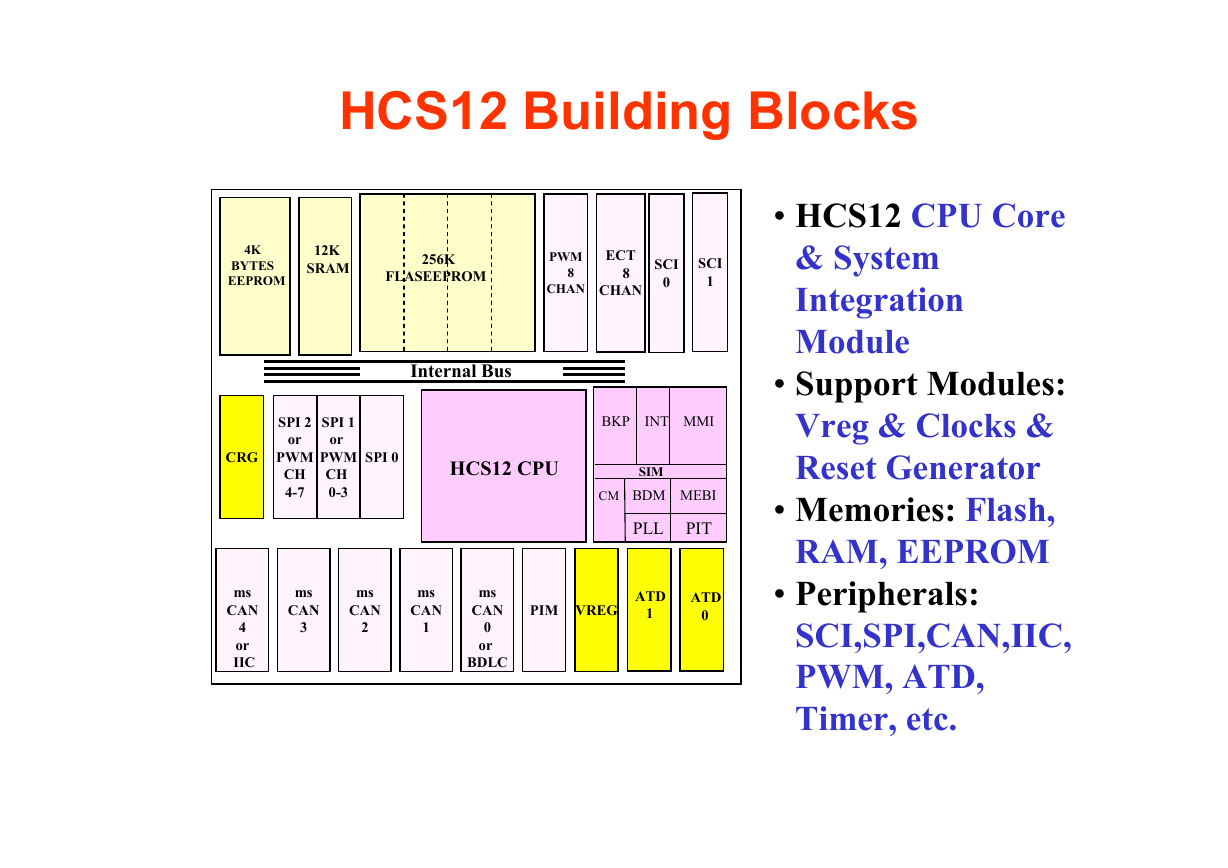

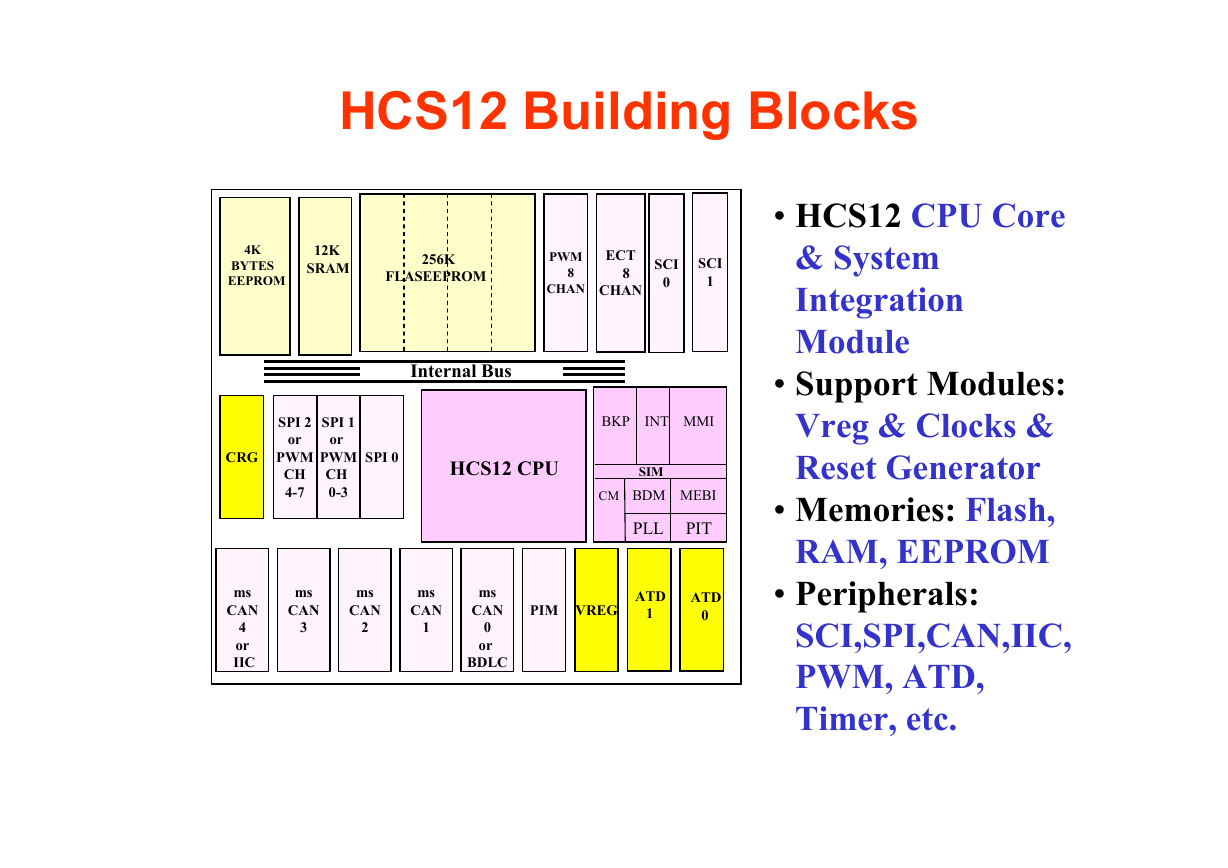

HCS12 Building Blocks

4K

BYTES

EEPROM

12K

SRAM

256K

FLASEEPROM

PWM

8

CHAN

ECT

8

CHAN

SCI

0

SCI

1

Internal Bus

SPI 2

or

PWM

CH

4-7

SPI 1

or

PWM

CH

0-3

SPI 0

HCS12 CPU

BKP INT MMI

SIM

CM BDM MEBI

PLL PIT

ms

CAN

3

ms

CAN

2

ms

CAN

1

ms

CAN

0

or

BDLC

PIM

VREG

ATD

1

ATD

0

CRG

ms

CAN

4

or

IIC

• HCS12 CPU Core

& System

Integration

Module

• Support Modules:

Vreg & Clocks &

Reset Generator

• Memories: Flash,

RAM, EEPROM

• Peripherals:

SCI,SPI,CAN,IIC,

PWM, ATD,

Timer, etc.

�

• 16-bit HCS12 CPU

Upward compatible with HC11

20-bit ALU

Instruction pipe

Enhanced indexed addressing

• SIM (System Integ. module)

MEB (Multiplexed External Bus)

MMC (Module Mapping Control)

BKP (Breakpoints)

BDM (Background Debug Mode)

• Clocks Reset Generator (CRG)

low current oscillator, PLL, reset,

clocks, COP watchdog,

Real time interrupt, clock

monitoring

Main Features:

• On-chip Voltage Regulator

2.25 to 2.75V Digital Supply Voltage

4.75V to 5.25V Analog and I/O Voltage

• Technology: 0.25 micron CMOS

50 MHz CPU equivalent to

25MHz bus

operation (66/33MHz in design)

�

Peripherals

2 x Serial Communications Interface (SCI)

3 x Serial Peripheral interface (SPI)

up to 5 x 1M b/s, CAN 2.0 A, B msCAN module

Byte Data Link Controller (BDLC,J1850)

Inter-IC Bus (IIC)

10-bit Analog-to-Digital Converter

Standard 8 channel Timer

Enhanced Capture Timer (ECT)

PWM module

Stepper Motor controller

•

•

•

•

•

•

•

•

•

•

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc