Hi3536 H.265 解码处理器

产品简介

文档版本

02

发布日期

2015-03-04

�

版权所有 © 深圳市海思半导体有限公司2015。保留一切权利。

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部,并不得以任何形式传播。

商标声明

、

、海思和其他海思商标均为深圳市海思半导体有限公司的商标。

本文档提及的其他所有商标或注册商标,由各自的所有人拥有。

注意

您购买的产品、服务或特性等应受海思公司商业合同和条款的约束,本文档中描述的全部或部分产品、服务或特性可

能不在您的购买或使用范围之内。除非合同另有约定,海思公司对本文档内容不做任何明示或默示的声明或保证。

由于产品版本升级或其他原因,本文档内容会不定期进行更新。除非另有约定,本文档仅作为使用指导,本文档中的

所有陈述、信息和建议不构成任何明示或暗示的担保。

深圳市海思半导体有限公司

地址:

深圳市龙岗区坂田华为基地华为电气生产中心 邮编:518129

网址:

http://www.hisilicon.com

客户服务电话:

+86-755-28788858

客户服务传真:

+86-755-28357515

客户服务邮箱:

support@hisilicon.com

�

Hi3536

Hi3536 H.265解码处理器

主要特点

处理器内核

ARM Cortex A17 四核@Max. 1.6GHz

− 32KB L1 I-Cache,32KB L1 D-Cache

− 1MB L2 Cache

− 主控处理器,用于运行外设驱动及应用程序

ARM Cortex A7 单核@Max. 900MHz

− 32KB L1 I-Cache,32KB L1 D-Cache

− 128KB L2 Cache

− 用于视频相关模块的控制

视频解码标准

H.265 Main Profile Level5.1 解码

H.264 Baseline/Main/High Profile Level5.0 解码

MPEG4 SP L0~L3/ASP L0~L5 解码

MJPEG/JPEG Baseline 解码

视频编码标准

H.264 Baseline/Main/High Profile Level5.1 编码

MJPEG/JPEG Baseline 编码

视频编解码处理

H.265/H.264&JPEG 多码流编解码性能

− 4x4K*2K(3840*2160)@30fps H.265/H.264解码

+2x1080p@30fps H.264编码 + 4x4K*2K@2fps

JPEG编码

− 16x1080p@30fps H.265/H.264解码

+2x1080p@30fps H.264编码 + 16x1080p@2fps

JPEG编码

− 9x1080p@30fps H.265/H.264解码 + 4Kx2K@30fps

H.264编码 + 9x1080p@2fps JPEG编码

− 32x720p@30fps H.265/H.264解码 + 4x720p@30fps

H.264编码 + 32x720p@2fps JPEG编码

− 64xD1@30fps H.265/H.264解码 + 8xD1@30fps

H.264编码 + 64xD1@2fps JPEG编码

− 9x720p@30fps JPEG解码

CBR/VBR 码率控制,16Kbit/s~40Mbit/s

编码帧率支持 1 fps~60fps

支持感兴趣区域(ROI)编码

支持彩转灰编码

GPU

集成 Mali-T720 GPU

支持 OpenGL ES3.1/2.0/1.1

支持 OpenCL 1.2/1.1/1.0

三角形填充率高达 63MTris/s

支持双精度 FP64 及抗锯齿功能

智能视频分析

集成 IVE2.0 智能分析加速引擎,支持多种智能分析应

用

− 运动侦测

− 视频诊断

− 周界防范

视频与图形处理

支持 3D 去噪、de-interlace、边缘平滑、动态对比度增

文档版本 02 (2015-03-04)

强、锐化

支持视频、图形输出抗闪烁处理

支持视频 1/8~16x 缩放

支持图形 1/2~2x 缩放

支持 4 个遮挡区域

支持 8 个区域 OSD 叠加

视频接口

视频输入接口

− 支持1个BT.1120 高清输入接口

− 支持一个视频输入通道,可用于双片级联

− 支持SDR和DDR两种模式

− 在SDR模式下最大可输入1080P@60fps

− 在DDR模式下最大可输入3840 x2160@30fps

视频输出接口

− 支持1个HDMI 2.0 超高清输出接口,最大输出

3840 x2160@60fps

− 支持1个VGA高清输出接口,最大输出2560 x

1600@60fps

− 支持1个BT.1120高清输出接口,在SDR模式下最

大可输出1080P@60fps,在DDR模式下最大可输

出3840 x2160@30fps

− 支持2个独立高清输出通道(DHD0、DHD1),

可通过任意高清接口(HDMI、VGA、BT.1120)

输出

− DHD0支持64画面输出,最大输出

3840x2160@60fps

− DHD1支持32画面输出,最大输出1080P@60fps

− 支持1个CVBS标清输出接口

− 支持3个RGB1555或RGB8888的全屏GUI图形层,

分别用于2路高清和1路标清

− 支持2个硬件鼠标层,格式为RGB1555、

RGB4444、RGB8888可配置,最大分辨率为256x

256

音频接口

集成 1 个 Audio codec

支持 3 个单向 I2S/PCM 接口

− 1个输入,支持16路复用输入

− 2个输出

支持 16bit 语音输入和输出

网络接口

支持 2 个千兆以太网接口

− 支持RGMII、RMII、MII三种接口模式

− 支持10/100Mbit/s半双工或全双工

− 支持1000Mbit/s全双工

− 支持TOE,降低CPU开销

安全引擎

硬件实现 AES/DES/3DES 加解密算法

硬件实现 SHA 摘要算法

RAID 加速引擎

支持 XOR 加速

XOR 最大支持 9 个数据源

海思专有和保密信息

版权所有 © 深圳市海思半导体有限公司

1

�

Hi3536

Hi3536 H.265解码处理器

支持 DMA 功能,数据块最大 16MB

支持 memory 初始化,初始值可配

支持描述子链表

外围接口

2 个 SATA3.0 接口

− 支持PM功能

− 支持eSATA

1 个 PCIe 2.0/SATA 3.0 复用接口

− 可配置为1*PCIe x2、1*PCIe x1 + 1*SATA 或

2*SATA

− 用于PCIe 2.0接口时,支持RC和EP功能

− 用于SATA 3.0接口时,支持eSATA和PM

2 个 USB 2.0 HOST 接口,支持 Hub 功能

1 个 USB 3.0 HOST 接口,支持 Hub 功能

2 个 SDIO 接口

− SDIO0支持SD卡(SD 2.0)、SDIO 2.0、MMC

4.4.1

− SDIO1支持SD卡(SD 2.0)、SDIO 2.0、MMC

4.4.1、eMMC 4.5

− 支持SDXC卡(仅支持3.3V模式)

− SDIO0与BT.1120输出管脚复用

− SDIO1与NAND Flash接口管脚复用

4 个 UART 接口,其中 2 个支持 4 线

支持 1 个 IR 接口

支持 1 个 I2C 接口

支持多个 GPIO 接口

支持 1 个低速 ADC 接口

存储器接口

2 个 32bit DDR3/4 SDRAM 接口

− 最高频率933MHz(1.866Gbps)

− 支持双通道

− 支持ODT功能

− 最大容量支持3GB

SPI NOR/NAND Flash 接口

− 1、2、4bit SPI NOR/NAND Flash

− 2个片选

− (仅对NOR flash)每个片选支持的最大容量为

32MByte

− (仅对NAND flash)每个片选支持的最大容量为

8GByte

− (仅对NAND flash)2KB/4KB pagesize

− (仅对NAND flash)支持8bit/1Kbyte ECC及

24bit/1Kbyte ECC

NAND Flash 接口

− 支持8bit NAND Flash

− 2个片选

− 支持SLC, MLC

− 支持8/24/40/64bit ECC(基于1Kbyte数据块)

内置 64KB bootROM 和 88KB SRAM

独立供电 RTC

RTC 可通过电池独立供电

启动模式

支持从 bootROM 启动

支持从 SPI NOR Flash 启动

支持从 SPI NAND Flash 启动

支持从 NAND Flash 启动

支持从 eMMC 启动

支持 PCIe 从片启动

SDK

提供基于 Linux 3.10 的开发包

提供多种协议的音频编解码库

提供 H.265/H.264 的高性能 PC 解码库

芯片物理规格

功耗

− 4.3W典型功耗

− 支持多级功耗控制

工作电压

− Core电压为0.9V

− CPU电压为1.0V(可降压至0.9V)

− IO电压为3.3V

− DDR3/4 SDRAM接口电压为1.5/1.2V

封装

− RoHS,EDHS-PBGA

− 管脚间距:0.8mm

− 27mmx27mm封装大小

工作温度:0~70°C

文档版本 02 (2015-03-04)

海思专有和保密信息

版权所有 © 深圳市海思半导体有限公司

2

�

Hi3536

Hi3536 H.265解码处理器

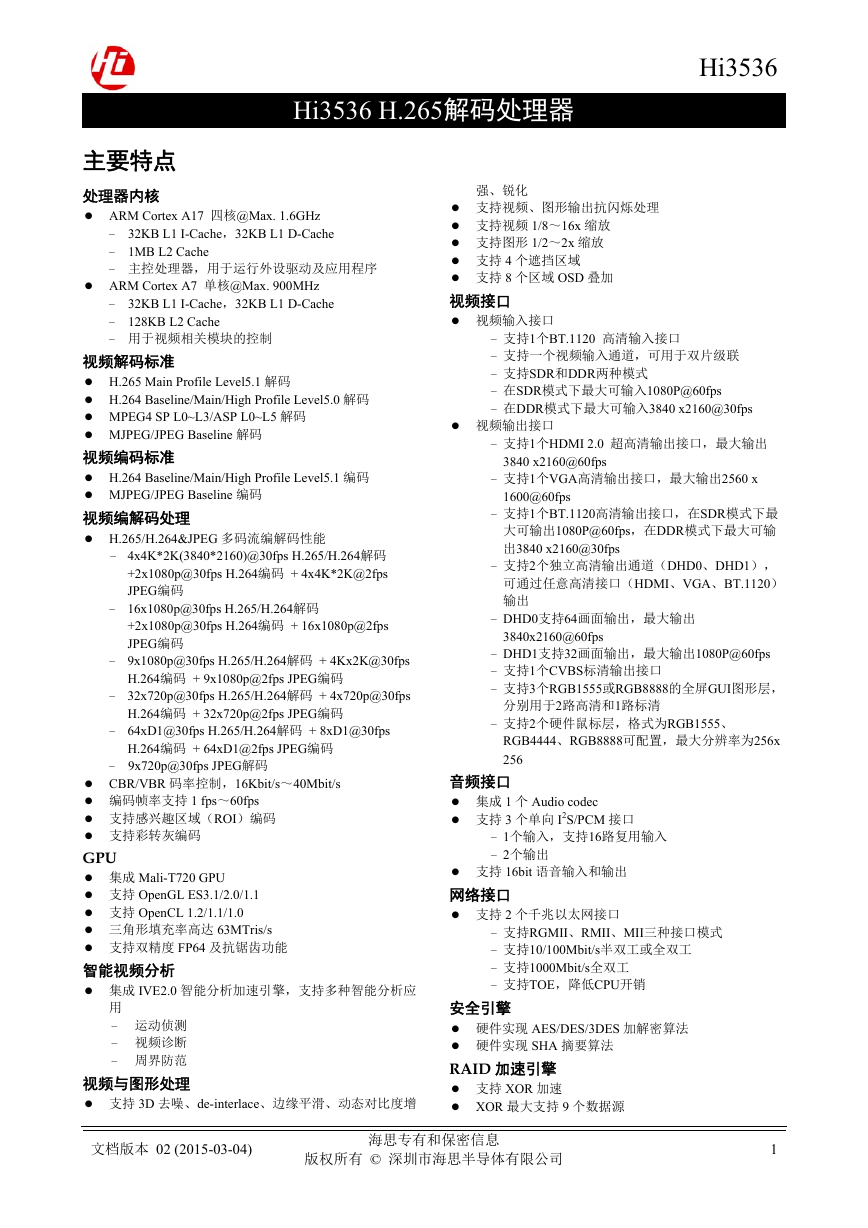

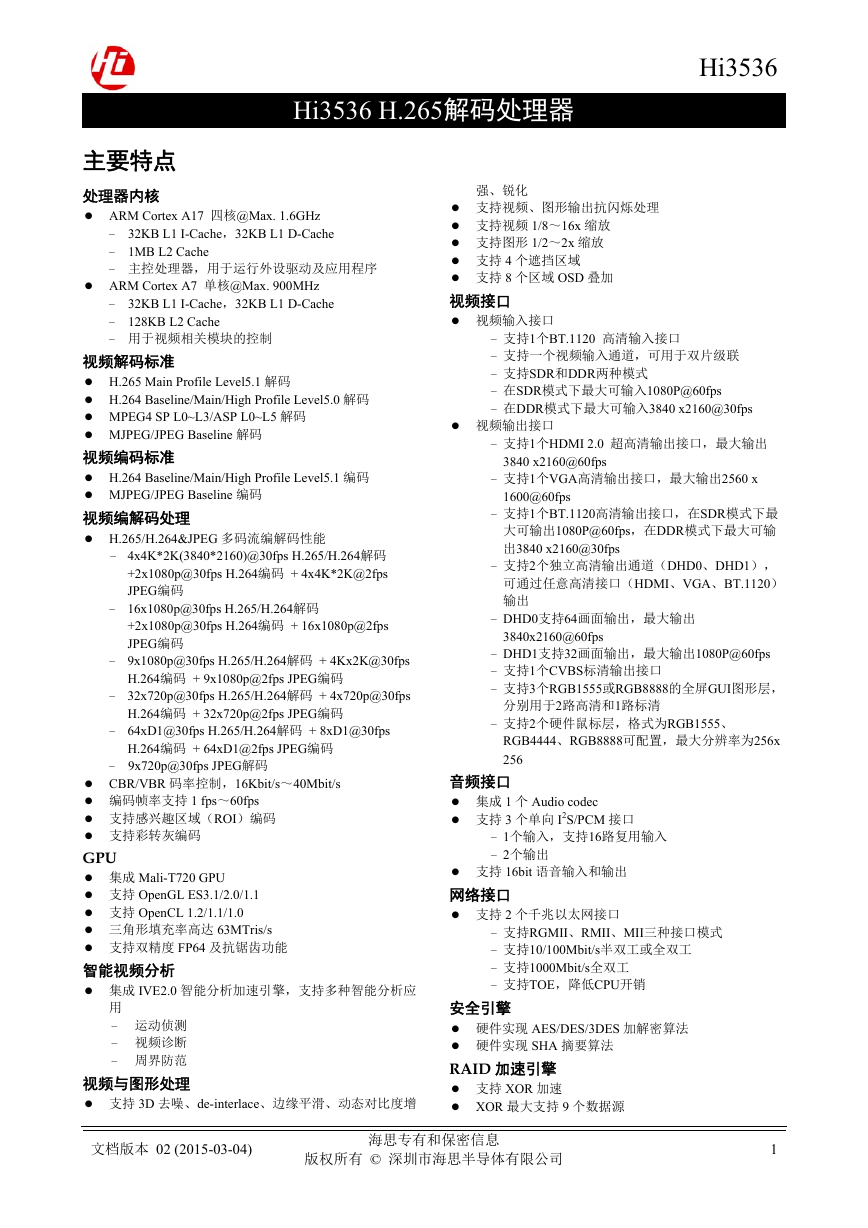

功能框图

DDRCx1

SATA3.0 x2

PCIe 2.0 2x/

SATA3.0 x2

SFC

MACx2

(TOE)

USB 2.0

Host x2

USB 3.0

Host x1

NANDC/

eMMC

I2S

ARM Subsystem

A17 quad core@1.6GHz

32KB/32KB L1 Cache

1MB L2 Cache

A7@900MHz

32KB/32KB L1 Cache

128KB L2 Cache

Image Subsystem

VPSS

VGS

HDMI/

VGA/

BT.1120/

CVBS

IVS ENGINE

TDE

AMBA3.0 BUS

Video Encoder

H.264/

MJPEG/JPEG

GPU

Mali T720

DMAC

RTC

I2C

SRAM

BootROM

IR

UARTx4

PWMx2

GPIOs

LSADC

Video Decoder

H.265/H.264/

MPEG-4/

MJPEG/JPEG

AES/DES/

3DES

SHA

Audio

Codec

Hi3536是针对多路高清或多路D1 NVR产品应用开发的专业高端SoC芯片。Hi3536内置高性能A17处理器和具有高达16路

1080p解码能力的多协议视频解码引擎,集成了具备多项复杂图像处理算法的高性能视频/图像处理引擎,结合双路高清显

示输出能力,为客户产品提供优异的图像质量。Hi3536集成了丰富的外围接口,在为客户提供差异化产品功能、性能、图

像质量要求的同时,大大降低ebom成本。

16路1080p实时解码(16路轮询预览)

2路1080p实时编码

1080p @32fps JPEG抓拍

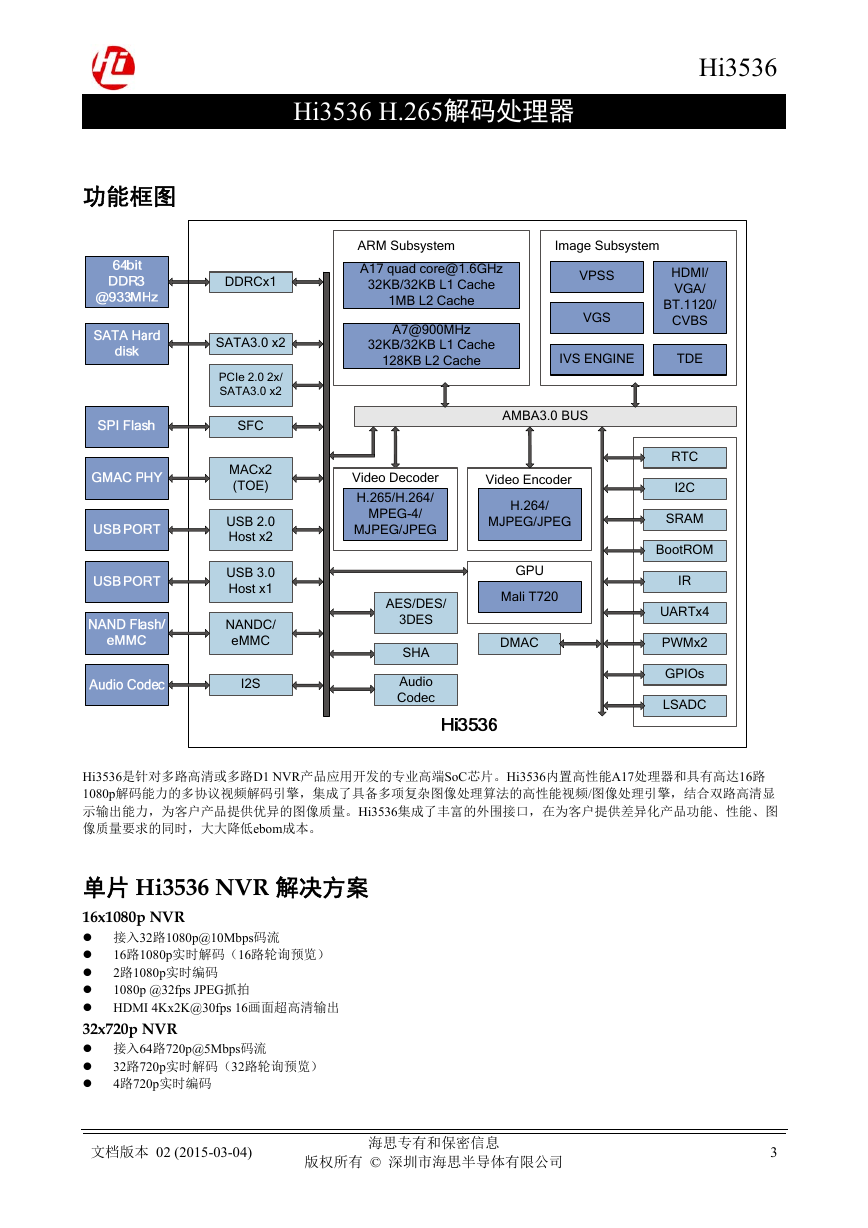

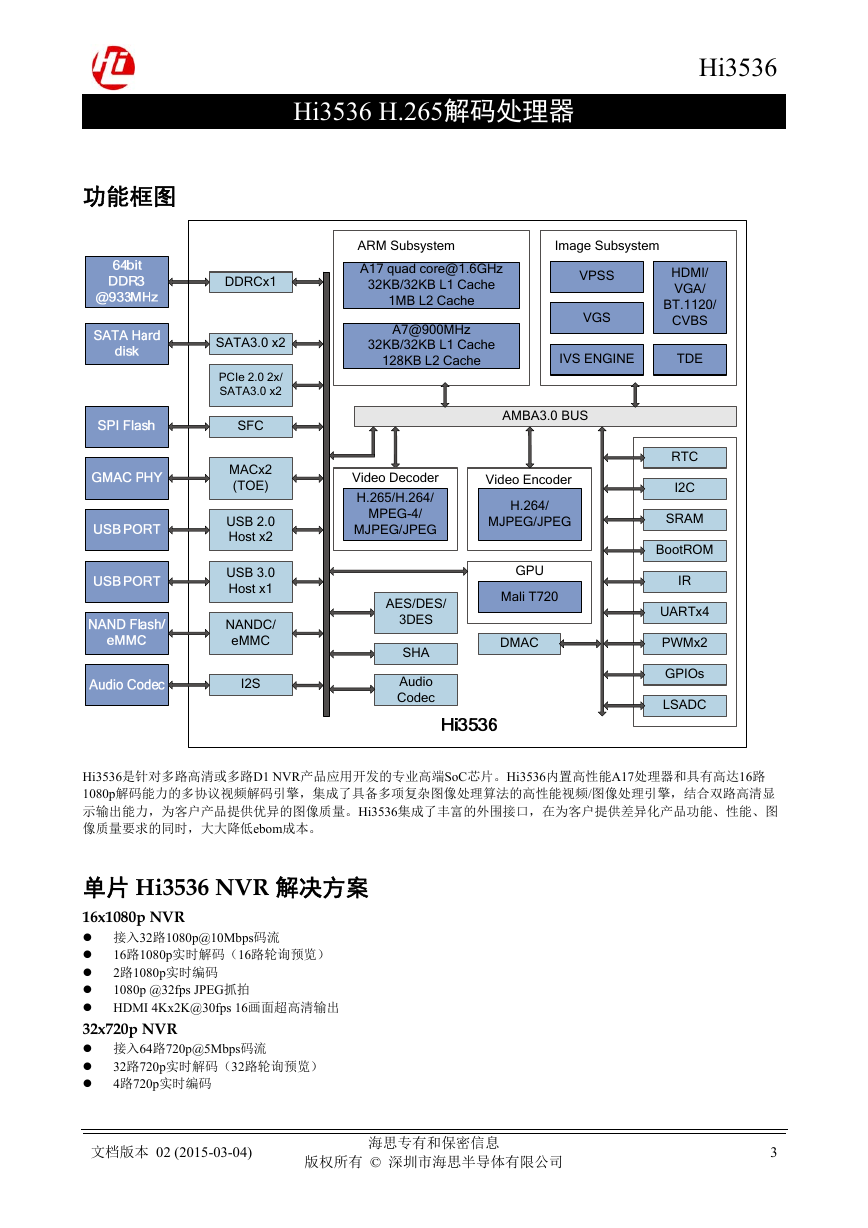

单片 Hi3536 NVR 解决方案

16x1080p NVR

接入32路1080p@10Mbps码流

HDMI 4Kx2K@30fps 16画面超高清输出

32x720p NVR

接入64路720p@5Mbps码流

32路720p实时解码(32路轮询预览)

4路720p实时编码

文档版本 02 (2015-03-04)

海思专有和保密信息

版权所有 © 深圳市海思半导体有限公司

3

�

Hi3536

Hi3536 H.265解码处理器

720p @64fps JPEG抓拍

HDMI+VGA 1080p@60fps双16画面高清输出

64D1 NVR

接入128路D1@2.5Mbps码流

D1 @128fps JPEG抓拍

HDMI 4Kx2K@30fps 64画面超高清输出

64D1实时解码(64路实时预览)

8路d1实时编码

SATA

HDD

SATA

HDD

SATA

HDD

LCD Monitor

LCD Monitor

LCD Monitor

HDMI PHY

SATA

Port Multiplier

SATA

Port Multiplier

HDMI

VGA

BT.1120

I2S

SATA

SATA

Flash

DDR3/4

DDR Ctrl

Hi3536

USB2.0 Host

USB3.0 Host

GMAC

GMAC0

GMAC1

PCIe

GE PHY

GE PHY

LAN/WAN

IP Camera

文档版本 02 (2015-03-04)

海思专有和保密信息

版权所有 © 深圳市海思半导体有限公司

4

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc