Phase Lock Loops and

Frequency Synthesis

Phase Lock Loops and Frequency Synthesis V.F. Kroupa

2003 John Wiley & Sons, Ltd

ISBN: 0-470-84866-9

�

Phase Lock Loops and

Frequency Synthesis

Vˇenceslav F. Kroupa

Academy of Sciences of the Czech Republic, Prague

�

Copyright 2003

John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester,

West Sussex PO19 8SQ, England

Telephone (+44) 1243 779777

Email (for orders and customer service enquiries): cs-books@wiley.co.uk

Visit our Home Page on www.wileyeurope.com or www.wiley.com

All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or

transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or

otherwise, except under the terms of the Copyright, Designs and Patents Act 1988 or under the terms of

a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London W1T 4LP,

UK, without the permission in writing of the Publisher. Requests to the Publisher should be addressed

to the Permissions Department, John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West

Sussex PO19 8SQ, England, or emailed to permreq@wiley.co.uk, or faxed to (+44) 1243 770620.

This publication is designed to provide accurate and authoritative information in regard to the subject

matter covered. It is sold on the understanding that the Publisher is not engaged in rendering

professional services. If professional advice or other expert assistance is required, the services of a

competent professional should be sought.

Other Wiley Editorial Offices

John Wiley & Sons Inc., 111 River Street, Hoboken, NJ 07030, USA

Jossey-Bass, 989 Market Street, San Francisco, CA 94103-1741, USA

Wiley-VCH Verlag GmbH, Boschstr. 12, D-69469 Weinheim, Germany

John Wiley & Sons Australia Ltd, 33 Park Road, Milton, Queensland 4064, Australia

John Wiley & Sons (Asia) Pte Ltd, 2 Clementi Loop #02-01, Jin Xing Distripark, Singapore 129809

John Wiley & Sons Canada Ltd, 22 Worcester Road, Etobicoke, Ontario, Canada M9W 1L1

Wiley also publishes its books in a variety of electronic formats. Some content that appears

in print may not be available in electronic books.

British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

ISBN 0-470-84866-9

Typeset in 10.5/13pt Times by Laserwords Private Limited, Chennai, India

Printed and bound in Great Britain by TJ International, Padstow, Cornwall

This book is printed on acid-free paper responsibly manufactured from sustainable forestry

in which at least two trees are planted for each one used for paper production.

�

To my wife Magda for her encouragement in starting and finishing this work

�

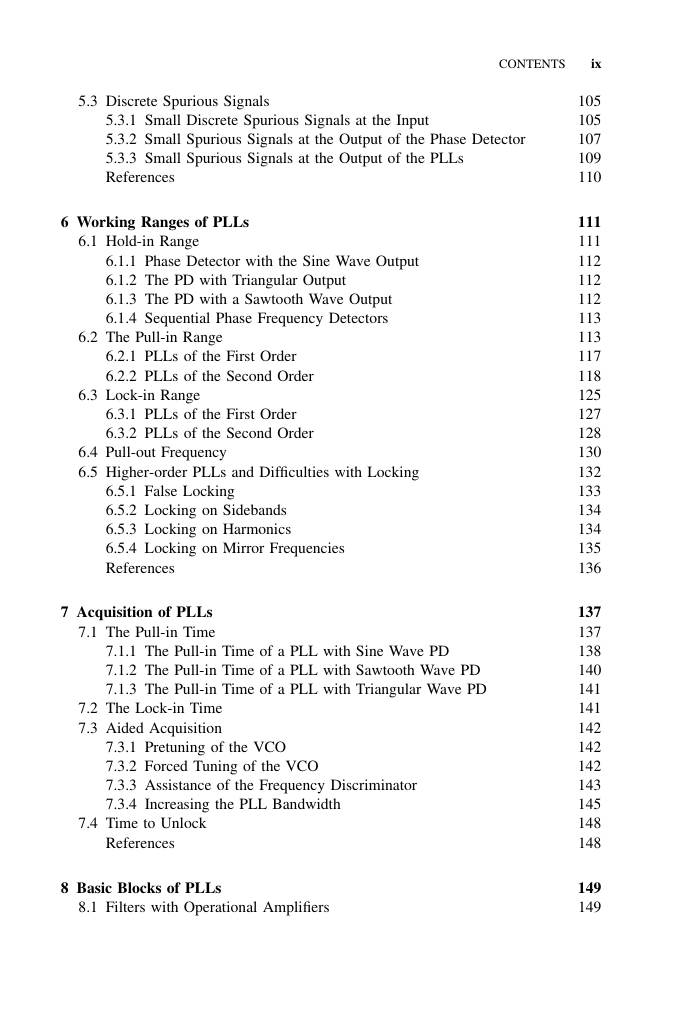

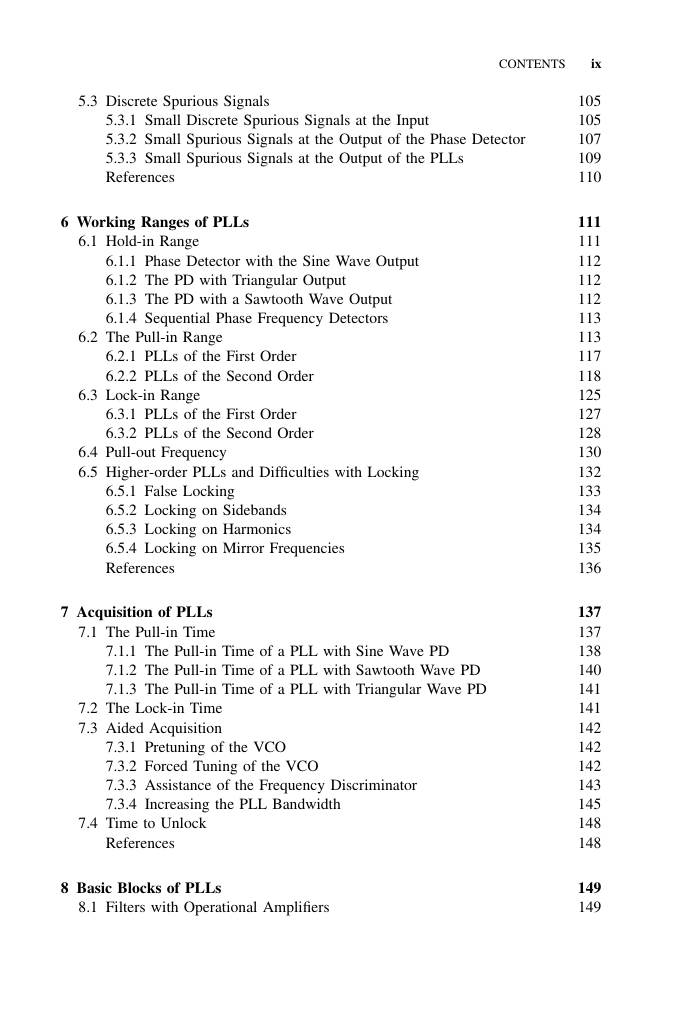

Contents

Preface

1 Basic Equations of the PLLs

1.1 Introduction

1.2 Basic Equations of the PLLs

1.3 Solution of the Basic PLL Equation in the Time Domain

1.3.1 Solution in the Closed Form

1.3.2 Linearized Solution

1.4 Solution of Basic PLL Equations in the Frequency Domain

1.5 Order and Type of PLLs

1.5.1 Order of PLLs

1.5.2 Type of PLLs

1.5.3 Steady State Errors

1.6 Block Diagram Algebra

References

2 PLLs of the First and Second Order

2.1 PLLs of the First Order

2.2 PLLs of the Second Order

2.2.1 A Simple RC Filter

2.2.2 Phase Lag-lead RRC or RCC Filter

2.3 PLLs of the Second Order of Type 2

2.3.1 PLLs of the Second Order of Type 2 with Voltage Output PD

2.3.2 PLLs of the Second Order of Type 2 with Current Output Phase

Detector

2.4 Second-order PLLs with Frequency Dividers in the Feedback Path

References

3 PLLs of the Third and Higher Orders

3.1 General Open-loop Transfer Function G(s)

3.1.1 Additional RC Section

3.1.2 Two RC Sections

xiii

1

1

1

4

4

5

6

7

8

9

9

10

12

13

13

15

15

17

20

21

23

26

27

29

30

30

30

�

viii

CONTENTS

3.1.3 Active Second-order Low-pass Filter

3.1.4 Twin-T RC Filter

3.1.5 PLLs with a Selective Filter in the Feedback Path

3.1.6 Time Delays in PLLs

3.2 Higher-order Type 2 PLLs

3.2.1 Third-order Loops: Lag-lead Filter with Additional RC Section

3.2.2 Third-order Loop: Second-order Lag Filter Plus RC Section

3.2.3 Fourth-order Loops

3.2.4 Fifth-order Loops

3.3 PLLs with Transmission Blocks in the Feedback Path

3.3.1 Divider in the Feedback Path

3.3.2 IF Filter in the Feedback Path

3.3.3 IF Filter and Divider in the Feedback Path

3.4 Sampled Higher-order Loops

3.4.1 Third-order Loops with the Current Output Phase Detector

3.5 Higher-order Loops of Type 3

3.6 Computer Design of a Higher-order PLL

References

4 Stability of the PLL Systems

4.1 Hurwitz Criterion of Stability

4.2 Computation of the Roots of the Polynomial P (s)

4.3 Expansion of the Function 1/[1 + G(s)] into a Sum of Simple Fractions

4.3.1 Polynomial S(s) Contains Simple Roots Only

4.3.2 Polynomial S(s) Contains a Pair of Complex Roots

4.3.3 Polynomial S(s) Contains Multiple-order Roots

4.4 The Root-locus Method

4.5 Frequency Analysis of the Transfer Functions – Bode Plots

4.5.1 Bode Plots

4.5.2 Polar Diagrams

4.6 Nyquist Criterion of Stability

4.7 The Effective Damping Factor

4.8 Appendix

References

5 Tracking

5.1 Transients in PLLs

5.1.1 Transients in First-order PLLs

5.1.2 Transients in Second-order PLLs

5.1.3 Transients in Higher-order Loops

5.2 Periodic Changes

5.2.1 Phase Modulation of the Input Signal

5.2.2 Frequency Modulation of the Input Signal

32

33

35

38

41

41

43

46

49

55

55

56

56

56

56

59

60

63

65

66

68

69

69

69

70

70

73

74

81

83

88

91

92

93

93

94

94

101

101

104

104

�

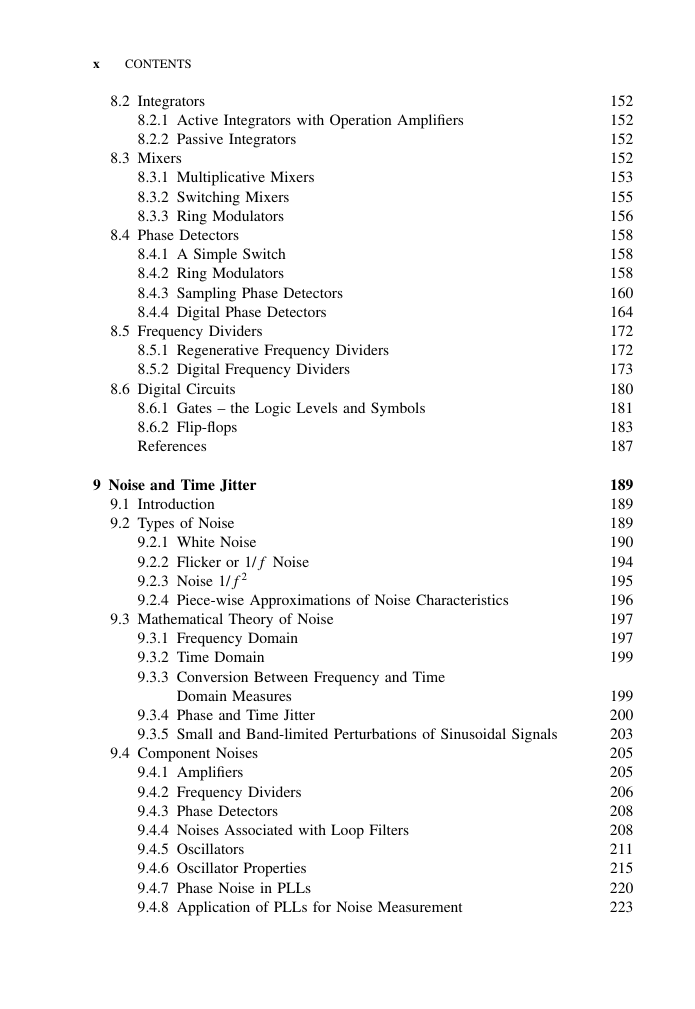

CONTENTS

ix

5.3 Discrete Spurious Signals

5.3.1 Small Discrete Spurious Signals at the Input

5.3.2 Small Spurious Signals at the Output of the Phase Detector

5.3.3 Small Spurious Signals at the Output of the PLLs

References

6 Working Ranges of PLLs

6.1 Hold-in Range

6.1.1 Phase Detector with the Sine Wave Output

6.1.2 The PD with Triangular Output

6.1.3 The PD with a Sawtooth Wave Output

6.1.4 Sequential Phase Frequency Detectors

6.2 The Pull-in Range

6.2.1 PLLs of the First Order

6.2.2 PLLs of the Second Order

6.3 Lock-in Range

6.3.1 PLLs of the First Order

6.3.2 PLLs of the Second Order

6.4 Pull-out Frequency

6.5 Higher-order PLLs and Difficulties with Locking

6.5.1 False Locking

6.5.2 Locking on Sidebands

6.5.3 Locking on Harmonics

6.5.4 Locking on Mirror Frequencies

References

7 Acquisition of PLLs

7.1 The Pull-in Time

7.1.1 The Pull-in Time of a PLL with Sine Wave PD

7.1.2 The Pull-in Time of a PLL with Sawtooth Wave PD

7.1.3 The Pull-in Time of a PLL with Triangular Wave PD

7.2 The Lock-in Time

7.3 Aided Acquisition

7.3.1 Pretuning of the VCO

7.3.2 Forced Tuning of the VCO

7.3.3 Assistance of the Frequency Discriminator

7.3.4 Increasing the PLL Bandwidth

7.4 Time to Unlock

References

8 Basic Blocks of PLLs

8.1 Filters with Operational Amplifiers

105

105

107

109

110

111

111

112

112

112

113

113

117

118

125

127

128

130

132

133

134

134

135

136

137

137

138

140

141

141

142

142

142

143

145

148

148

149

149

�

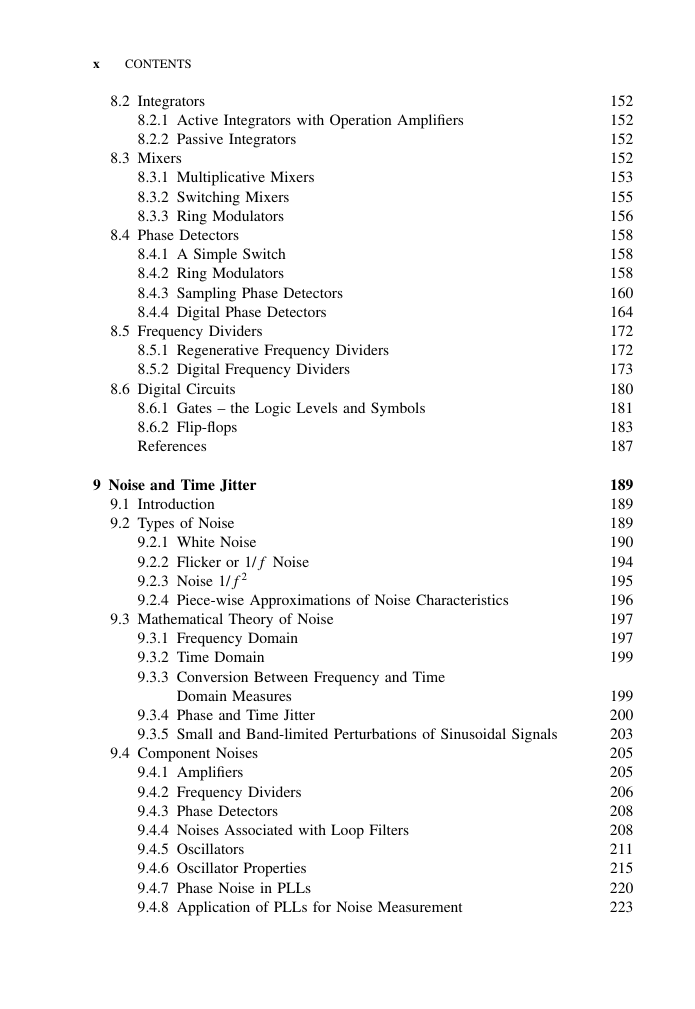

x

CONTENTS

8.2 Integrators

8.2.1 Active Integrators with Operation Amplifiers

8.2.2 Passive Integrators

8.3 Mixers

8.3.1 Multiplicative Mixers

8.3.2 Switching Mixers

8.3.3 Ring Modulators

8.4 Phase Detectors

8.4.1 A Simple Switch

8.4.2 Ring Modulators

8.4.3 Sampling Phase Detectors

8.4.4 Digital Phase Detectors

8.5 Frequency Dividers

8.5.1 Regenerative Frequency Dividers

8.5.2 Digital Frequency Dividers

8.6 Digital Circuits

8.6.1 Gates – the Logic Levels and Symbols

8.6.2 Flip-flops

References

9 Noise and Time Jitter

9.1 Introduction

9.2 Types of Noise

9.2.1 White Noise

9.2.2 Flicker or 1/f Noise

9.2.3 Noise 1/f 2

9.2.4 Piece-wise Approximations of Noise Characteristics

9.3 Mathematical Theory of Noise

9.3.1 Frequency Domain

9.3.2 Time Domain

9.3.3 Conversion Between Frequency and Time

Domain Measures

9.3.4 Phase and Time Jitter

9.3.5 Small and Band-limited Perturbations of Sinusoidal Signals

9.4 Component Noises

9.4.1 Amplifiers

9.4.2 Frequency Dividers

9.4.3 Phase Detectors

9.4.4 Noises Associated with Loop Filters

9.4.5 Oscillators

9.4.6 Oscillator Properties

9.4.7 Phase Noise in PLLs

9.4.8 Application of PLLs for Noise Measurement

152

152

152

152

153

155

156

158

158

158

160

164

172

172

173

180

181

183

187

189

189

189

190

194

195

196

197

197

199

199

200

203

205

205

206

208

208

211

215

220

223

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc