�

XILINXVeriog编程大全2015版(SLX9)酷炫论坛主页www.osrc.cnFPGAQQ群:867306081第一章Verilog语法基础............................................................................................................................................51.1技术背景......................................................................................................................................................51.1.1学习VHDL还是verilog...............................................................................................................51.1.2时序设计第一种办法——状态机设计..........................................................................................51.1.3时序设计第二种方法——FPGA中运行CPU..................................................................................61.1.4用FPGA好还是专用的集成电路(ASIC)....................................................................................61.1.5一段求和的C代码..........................................................................................................................61.1.6一段求和的verilog代码.............................................................................................................61.2Verilog最最基础语法.............................................................................................................................71.2.1C语言和verilog相对应的关键词和结构。..............................................................................71.2.2C语言和verilog相对应的运算符.............................................................................................71.3关键字...........................................................................................................................................................81.3.1信号....................................................................................................................................................81.3.2结构..................................................................................................................................................81.3.3符号..................................................................................................................................................91.3.4参数..................................................................................................................................................101.3.5预处理命令......................................................................................................................................111.4Verilog中数值表示的方式....................................................................................................................11第二章Verilog语法实战.....................................................................................................................................122.1简单的Verilog模块...............................................................................................................................122.1.1EX01-加法器设计.........................................................................................................................122.1.2EX02-计数器设计.........................................................................................................................142.2Verilog语言模块的调用........................................................................................................................162.2.1EX03-8bit计数器.......................................................................................................................172.2.2EX04-8bit串进并出,并进串出使用移位模块设计.............................................................19第三章Verilog实战应用案例.................................................................................................................................233.1EX01-RunLed设计...................................................................................................................................233.2EX02-RunLed另一种实现.......................................................................................................................253.3EX03-FlashLed闪耀灯设计.................................................................................................................263.4EX04-按钮实验(延时去抖动,同步电路设计).................................................................................283.5EX05-SPI通信协议设计.........................................................................................................................313.6EX06-SPI通过74HC595扩展IO数码动态显示................................................................................383.7EX07-SPI通过74HC595扩展IO实现数码计数器............................................................................443.8EX08-常规串口发送模块设计.................................................................................................................463.9EX09-常规的串口接受模块设计.............................................................................................................503.10EX10-PS2键盘解码实验........................................................................................................................543.11EX11-VGA彩条实验...............................................................................................................................603.12EX12-VGA多彩动画屏保......................................................................................................................643.13EX13-I2C通信协议设计读写EEPROM24LC02..................................................................................683.14EX14-串口发送代码的优化设计...........................................................................................................823.15EX15-串口接收模块的优化改进设计...................................................................................................873.16EX16-UartLOOP串口回传程序..............................................................................................................90第四章SRAM、SDRAM、DDR2内存应用实战..........................................................................................................94

XILINXVeriog编程大全2015版(SLX9)酷炫论坛主页www.osrc.cnFPGAQQ群:8673060824.1异步SRAM-61LV25616Busrt读写测试Verilog..................................................................................944.2SDRSDRAM读写测试Verilog...............................................................................................................1004.3DDR2SDRAM基于MCB硬核读写测试Verilog....................................................................................107第五章Block模块方案实战................................................................................................................................1235.1ADC/DAC模块使用实验..........................................................................................................................1235.1.1主要硬件参数..............................................................................................................................1235.1.2ADC部分原理图..........................................................................................................................1245.1.3DAC部分原理图..........................................................................................................................1255.1.4基于FPGA的高速ADCDAC驱动程序设计..............................................................................1255.2CY7C68013AUSB2.0高速采集模块使用实验......................................................................................1285.2.1主要硬件参数..............................................................................................................................1285.2.2ADC部分原理图:......................................................................................................................1295.2.3USB2.0部分原理图....................................................................................................................1305.2.4CY7C68013AUSB2.0FPGAADC采集方案...............................................................................1305.2.5CY7C68013AUSB2.0固件设计.................................................................................................1325.2.6基于MFC界面设计....................................................................................................................1345.3视频图像卡图像采集输出.....................................................................................................................1355.3.1图像采集输出原理.......................................................................................................................1355.3.2基于SRAM的简单的视频采集输出.........................................................................................1375.3.3基于SDRSDRAM的简单的视频采集输出............................................................................1535.3.4基于DDR2SDRAM的简单的视频采集输出...........................................................................169第六章MicroblazeAXI4BUS32BITSCPUSOC开发实战..............................................................................1896.1SOC第一课:Helloworld....................................................................................................................1896.2SOC第二课:SRAM测试.........................................................................................................................1976.3SOC第三课:RunLed流水灯...............................................................................................................2016.4SOC第四课:Button按钮输入.............................................................................................................2046.5SOC第五课:STimer自定义超级定时器.............................................................................................2076.6SOC第六课:Timer系统定时器中断..................................................................................................2126.7SOC第七课:GPIO中断.........................................................................................................................2146.8SOC第八课:UART中断.........................................................................................................................2166.9SOC第九课:SPI回传...........................................................................................................................2186.10SOC第十课:I2C读写24LC02实验...................................................................................................2216.11SOC第十一课:数码管Verilog驱动...............................................................................................2246.12SOC第十二课:CPU+Verilog驱动彩屏.............................................................................................2276.13SOC第十三课:CPU+Verilog图片显示实验.....................................................................................2306.14SOC第十四课:SD卡链接测试实验..................................................................................................2316.15SOC第十五课:SD卡图片显示实验...................................................................................................2336.16SOC第十六课:UCOSIII操作系统实验............................................................................................2346.17SOC第十七课:10M以太网通信实验.................................................................................................236第七章XILINX常用IP测试实验......................................................................................................................2417.1IP第一课:简单端口ROM....................................................................................................................2417.2IP第二课:单端口先写模式................................................................................................................2467.3IP第三课:单端口先读模式................................................................................................................2537.4IP第四课:单端口无变化模式............................................................................................................2607.5IP第五课:简单双端口RAM无改变模式............................................................................................267�

XILINXVeriog编程大全2015版(SLX9)酷炫论坛主页www.osrc.cnFPGAQQ群:8673060837.6IP第六课:FIFO....................................................................................................................................2747.7IP第七课:DCM......................................................................................................................................2797.8IP第八课:PLL......................................................................................................................................285第八章ISE新建工程以及联合Modelsim仿真实例..........................................................................................2888.1ISE新建工程..........................................................................................................................................2888.2新建源码文件..........................................................................................................................................2898.3新建仿真测试文件-TestBench.............................................................................................................2918.4设置第三方仿真工具Modelsim.............................................................................................................2928.5编译XILINX仿真库...............................................................................................................................2938.6ISE、Modelsim联合仿真......................................................................................................................2968.7添加UCF管脚约束文件并编译工程....................................................................................................297第九章在线逻辑分析仪Chipscope在线仿真实例...........................................................................................2989.1添加ChipcopeIP-CORE.........................................................................................................................2989.2设置需要观察的仿真信号......................................................................................................................2989.3编译工程并启动chipscope逻辑分析仪.................................................................................................3019.4确保开发板通电,并通过JTAG链接到电脑之后运行逻辑分析仪....................................................301第十章XILINX下载器使用................................................................................................................................30410.1XILINXJTAG下载程序入门...............................................................................................................30410.1.1酷炫XILINXJTAG下载器MINI工程师便携版...................................................................30410.1.2酷炫XILINXJTAG下载器链接示意图...................................................................................30410.2下载BIT格式程序到FPGA.................................................................................................................30610.3下载PROM文件....................................................................................................................................30910.3.1生成PROM文件.........................................................................................................................30910.3.2下载程序到PROM.......................................................................................................................311�

XILINXVeriog编程大全2015版(SLX9)酷炫论坛主页www.osrc.cnFPGAQQ群:867306084序言玩开发板是一件很有趣和有意义的事情,一方面用开发板可以DIY实用的小东西,另一方面开发板的技术也能运用到工程项目中,带来经济效益。在中国,在全世界,都有很大一批人在玩开发板,玩开发板对搞技术的工程师来说,就是一道盛宴。回想,笔者刚开始玩XILINXFPGA开发板的,刚毕业没多久,在2009年左右,那时候XILINXFPGA的开发板是超级的贵,一个spartan3e的开发板国产的很少,至少也得1K,USB下载器也要200多,手头拮据,耽误了不少时间,后来自己借到一块spartan2的开发板,然后根据官方提供spartan3e的开发板图纸,简化设计了一款板子,那可是国产第一款低价的sparan3e的开发板,很有成就感,几年过去,现在设计的板子也是也来越复杂,功能也是越来越强大。几年下来,结交了很多和笔者一样喜欢玩开发板,专研技术的朋友,笔者感觉这是最大的幸运。经过这几年的积累,目前笔者的开发板内容也是越来越丰富,但是总感觉只是做开发板,不是什么大的理想,也没有太大的意义。又是经过一段时间思考后以及笔者和网友的探讨,笔者定位为,完全开源基础学习类型的内容,并且提高核心技术的支持。以基础学习免费,开源,免费技术支持,核心技术以技术支持形式收取一定费用的的思路。2014年下半年是我们实现第一步计划关键的一年,这半年首先我们将公布大量免费技术资料和源码,以及免费的技术支持,对于工作0-5年内从事FPGA工作的新手,或者工程师都会有很多参考学习的价值。目前,笔者已经建设了论坛www.osrc.cn,欢迎技术爱好者参与进来,和我们一起分享玩转开发板的乐趣,分享技术带来的成就感,也欢迎志同道合合者,一起参与到2016版的编程大全的编写做。在这里面简单介绍下<>,本版本是笔者编写的第一个版本,主要例子都是笔者这些年积累下来的精华,学习中给出了大量的实战例子给读者来学习,练手,全面覆盖了Verilog基础语法、XILINXFPGA编程基础、内存操作、图像处理、网络传输、MicroblazeSOC嵌入式开发、Modelsim仿真,Chipcope在线逻辑分析的使用,仿真下载器的使用。在后续的版本中笔者将同小伙伴们对FPGA的三大应用领域进行详细讲说,即通信行业、图像视频行业、工控自动化行业。在三个行业领域内,我们将从该行业的常用接口、常用算法、常用协议等等方面的FPGA实现为基础,进一步深入到各个行业各个应用,提高读者对感兴趣的一个行业的认识。具体而言,通信行业我们将主要讲到光通信,无线通信,计算机网络通信;图像视频行业,我们将讲到图像压缩,图像密写,图像预处理算法,视频压缩,视频特效,视频拼接;工控自动化行业,我们将讲到运动控制,ETHERCAT总线控制与机器人,机器视觉,数控系统等等。由于时间和精力有限,本版本难免会有错误和遗漏之处,恳请读者给予批评和指正。有梦想就有希望,感恩感谢!汤金元2014年9月6日南京�

XILINXVeriog编程大全2015版(SLX9)酷炫论坛主页www.osrc.cnFPGAQQ群:867306085第一章Verilog语法基础1.1技术背景大规模集成电路设计制造技术和数字信号处理技术,近三十年来,各自得到了迅速的发展。这两个表面上看来没有什么关系的技术领域实质上是紧密相关的。因为数字信号处理系统往往要进行一些复杂的数学运算和数据的处理,并且又有实时响应的要求,它们通常是由高速专用数字逻辑系统或专用数字信号处理器所构成,电路是相当复杂的。因此只有在高速大规模集成电路设计制造技术进步的基础上,才有可能实现真正有意义的实时数字信号处理系统。对实时数字信号处理系统的要求不断提高,也推动了高速大规模集成电路设计制造技术的进步。现代专用集成电路的设计是借助于电子电路设计自动化(EDA)工具完成的。学习和掌握硬件描述语言(HDL)是使用电子电路设计自动化(EDA)工具的基础。1.1.1学习VHDL还是verilog笔者建议verilog,虽然很多学校古董级的老师还在教VHDL.当然VHDL也是要了解的,因为这门古老的语言的历史遗留问题,现在还有很多VHDL的模块,有的时候我们要拿来主义,所以还有必要了解下的。但是历史的车轮总是在前进,优胜劣汰。也许不久的将来verilog也会被C,C++这种高级语言代替。为了更方面地切入主题,笔者假设,你已经学过单片机,并且掌握C语言。因为单片机,和C语言,可以说是当代大学生的一项基本能力。有了这个基础,再学习其他现代计算机编程,算法,才能达到事半功倍的效果。如果你还不会单片机和C语言,建议你首先学会单片机,或者C语言。当然,这只是笔者的建议,不会单片机,或者C语言,并不代表学不好Verilog语言。学过单片机的都知道,我们的程序代码是一条指令一条指令来执行的。CPU首先通过总线,读取一条指令,然后解析这条指令,再然后执行这条指令。我们写的C代码总是一条一条地执行。如果我们同时要处理10个子程序,那么CPU必须一个个子程序来执行。如果其中有一部子程序实时性要求很高,但是其中某些子程序执行起来又耽误非常多的时间,那么可想而知,很可能就没法实现这个功能,或者需要用非常高,非常高的CPU频率。另外比如,我们的单片机在用串口接收数据,并且也要发送数据,同时我们的单片机要处理外部的IO信号,如果我们的IO信号非常快,并且有几百个信号,可能同一个时刻触发,很显然,如果这些信号比较快,那么我们的单片机,就没法实现了。这是笔者简单举了两种情况,那么如果使用FPGA就可以很方便地解决以上问题。比如用一个FPGA,就可以同时完成串口的收发,以及IO的监控,因为FPGA的程序实际上就是电路,是瞬间就完成了,我们只要用verilog写出来相应功能的程序模块,这些模块是同时运行的。这样看来FPGA真是太强大了,太完美了。不要高兴地太早,FPGA确实速度很快,瞬间完成,但是如果我们要让他跟单片机能够被我们控制着,一个任务,一个任务来走,那就麻烦了。因为FPGA总是瞬间完成了。世界上永远没有完美的东西,我们在获得一种优势的时候,往往也获得了一种劣势。但是,办法总比问题多。1.1.2时序设计第一种办法——状态机设计可以说,我们用Verilog来写程序,状态机无处不在。顾名思义,通过设计状态机,我们可�

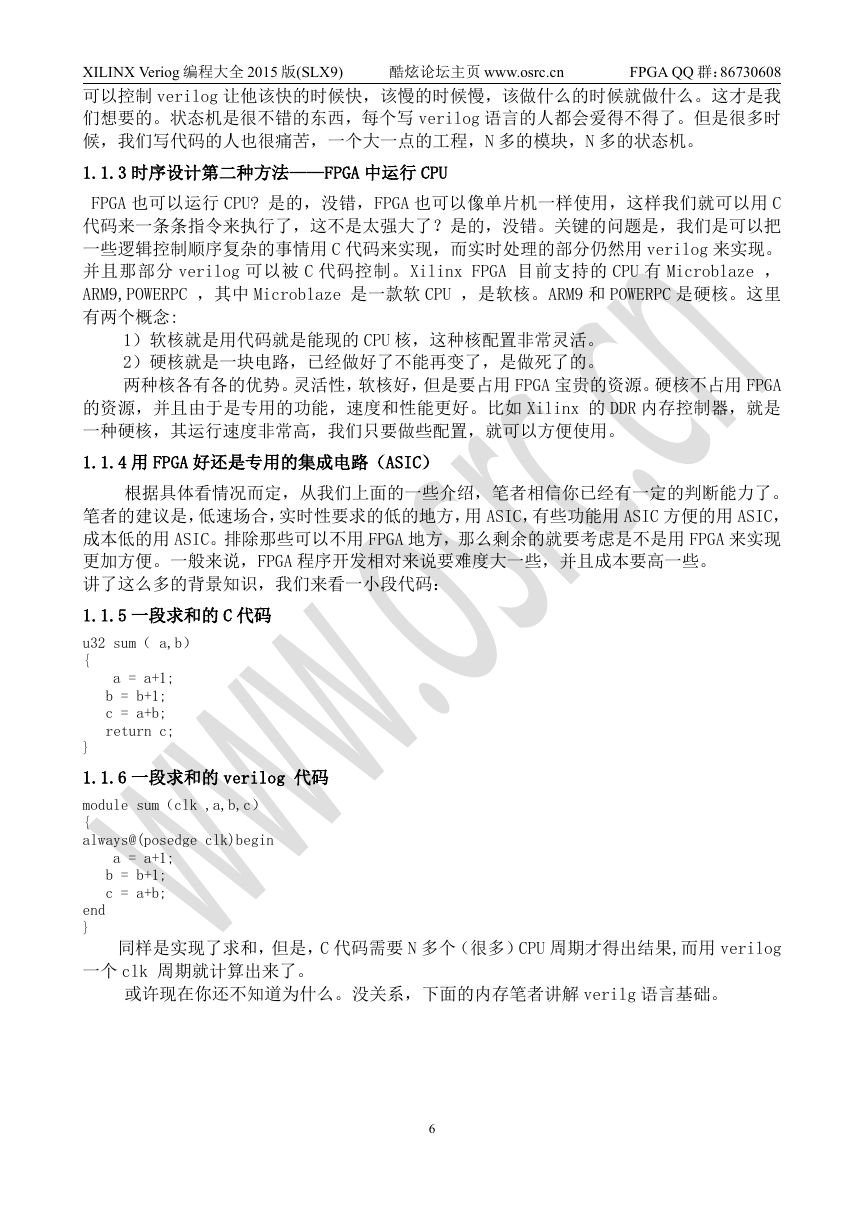

XILINXVeriog编程大全2015版(SLX9)酷炫论坛主页www.osrc.cnFPGAQQ群:867306086可以控制verilog让他该快的时候快,该慢的时候慢,该做什么的时候就做什么。这才是我们想要的。状态机是很不错的东西,每个写verilog语言的人都会爱得不得了。但是很多时候,我们写代码的人也很痛苦,一个大一点的工程,N多的模块,N多的状态机。1.1.3时序设计第二种方法——FPGA中运行CPUFPGA也可以运行CPU?是的,没错,FPGA也可以像单片机一样使用,这样我们就可以用C代码来一条条指令来执行了,这不是太强大了?是的,没错。关键的问题是,我们是可以把一些逻辑控制顺序复杂的事情用C代码来实现,而实时处理的部分仍然用verilog来实现。并且那部分verilog可以被C代码控制。XilinxFPGA目前支持的CPU有Microblaze,ARM9,POWERPC,其中Microblaze是一款软CPU,是软核。ARM9和POWERPC是硬核。这里有两个概念:1)软核就是用代码就是能现的CPU核,这种核配置非常灵活。2)硬核就是一块电路,已经做好了不能再变了,是做死了的。两种核各有各的优势。灵活性,软核好,但是要占用FPGA宝贵的资源。硬核不占用FPGA的资源,并且由于是专用的功能,速度和性能更好。比如Xilinx的DDR内存控制器,就是一种硬核,其运行速度非常高,我们只要做些配置,就可以方便使用。1.1.4用FPGA好还是专用的集成电路(ASIC)根据具体看情况而定,从我们上面的一些介绍,笔者相信你已经有一定的判断能力了。笔者的建议是,低速场合,实时性要求的低的地方,用ASIC,有些功能用ASIC方便的用ASIC,成本低的用ASIC。排除那些可以不用FPGA地方,那么剩余的就要考虑是不是用FPGA来实现更加方便。一般来说,FPGA程序开发相对来说要难度大一些,并且成本要高一些。讲了这么多的背景知识,我们来看一小段代码:1.1.5一段求和的C代码u32sum(a,b){a=a+1;b=b+1;c=a+b;returnc;}1.1.6一段求和的verilog代码modulesum(clk,a,b,c){always@(posedgeclk)begina=a+1;b=b+1;c=a+b;end}同样是实现了求和,但是,C代码需要N多个(很多)CPU周期才得出结果,而用verilog一个clk周期就计算出来了。或许现在你还不知道为什么。没关系,下面的内存笔者讲解verilg语言基础。�

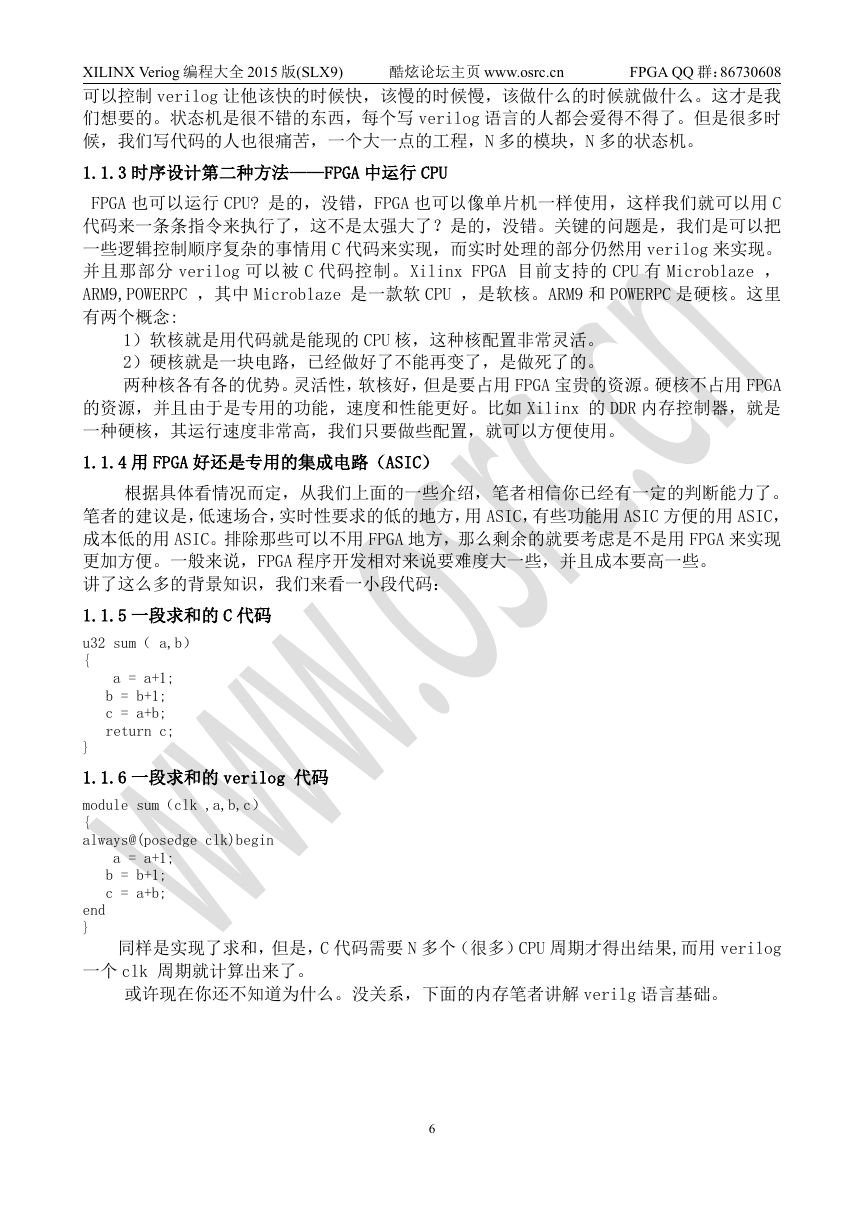

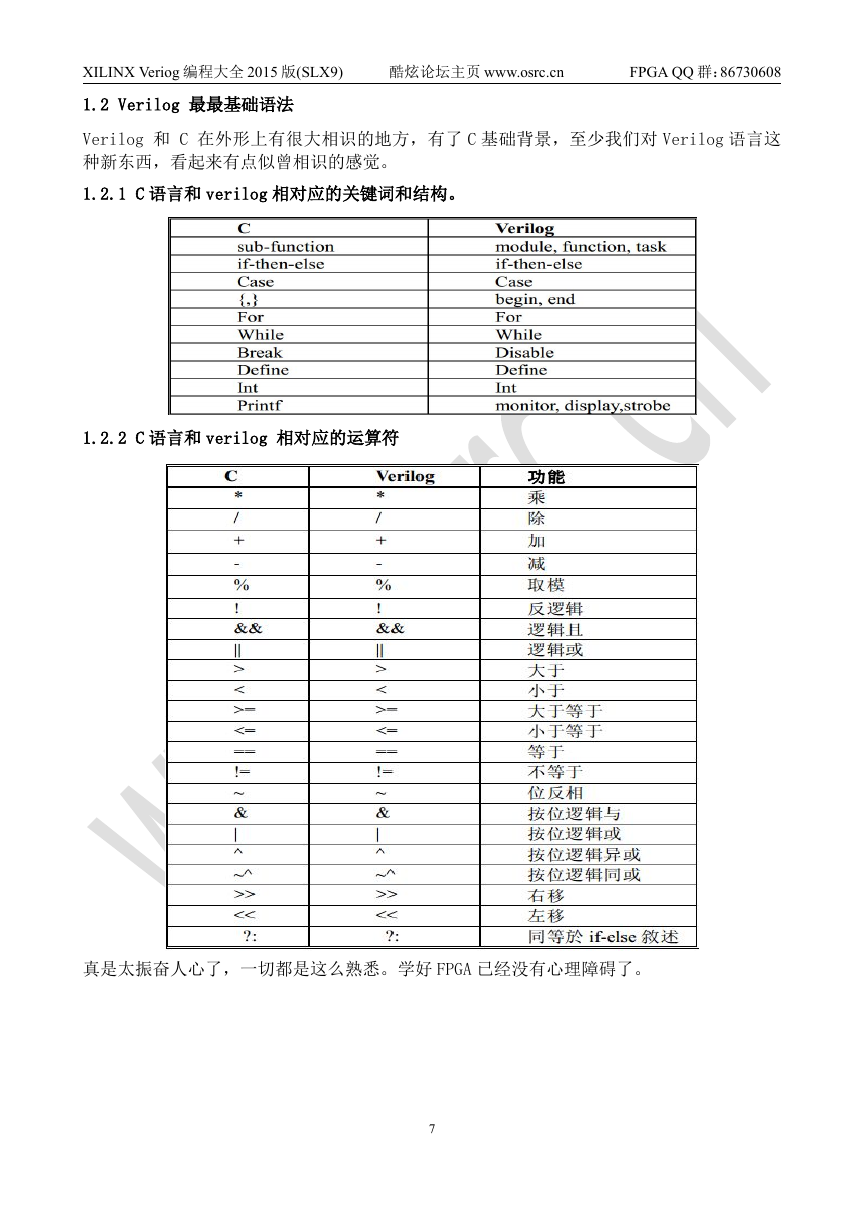

XILINXVeriog编程大全2015版(SLX9)酷炫论坛主页www.osrc.cnFPGAQQ群:8673060871.2Verilog最最基础语法Verilog和C在外形上有很大相识的地方,有了C基础背景,至少我们对Verilog语言这种新东西,看起来有点似曾相识的感觉。1.2.1C语言和verilog相对应的关键词和结构。1.2.2C语言和verilog相对应的运算符真是太振奋人心了,一切都是这么熟悉。学好FPGA已经没有心理障碍了。�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc