博客 学院 下载 GitChat 论坛

搜博主文章

写博客

发Chat

zoomdy's blog

懂硬件,做软件。Coding for hardware!

0

目录

收藏

评论

微信

微博

QQ

RSS订阅

个人资料

半斗米

关注

原创

128

粉丝

77

喜欢

23

评论

22

等级:

访问: 25万+

积分: 3878

排名: 1万+

勋章:

综合布线

最新文章

中国传统哲学与马克思主义哲学

《嵌入式系统设计师教程》读后感:2.6嵌

入式系统电源

嵌入式系统的分类

NB-IoT通信模组读取IMEI、ICCID、IMSI

嵌入式软件异步编程:单线程编程模型(前

后台系统编程模型)

个人分类

物联网、智能传感器

嵌入式系统

微控制器

事件驱动、异步编程

开发工具

展开

归档

2018年4月

2018年3月

2018年2月

2018年1月

2017年12月

14篇

15篇

36篇

10篇

25篇

2篇

12篇

21篇

4篇

1篇

�

0

目录

收藏

评论

微信

微博

QQ

展开

热门文章

objdump反汇编用法示例

阅读量:13906

Linux设置串口波特率等参数

阅读量:13678

GDB错误:Cannot find bounds of current f

unction

阅读量:8383

NB-IoT通信模组/模块

阅读量:8153

eCos入门开发环境eCosBox简介

阅读量:7622

最新评论

C语言实现模版

myy629464:让清风带走你所有的烦恼,让星星永

远点缀你的天空!

大道至简——RISC-V架构之魂(...

Lee_feiyue:11

Linux环境下ARM开发工具Tr...

woshi_ziyu:写的很不错呢

Altium Designer拖动...

weixin_41628149:非常赞~

Ubuntu 16.04安装Bra...

weixin_40836227:我输入完sudo dpkg -i libgcrypt

11_1.5.3-2ubuntu4.4_i38...

人脸识别算法

联系我们

请扫描二维码联系客服

webmaster@csdn.net

400-660-0108

QQ客服 客服论坛

关于 招聘 广告服务 百度

©1999-2018 CSDN版权所有

京ICP证09002463号

经营性网站备案信息

网络110报警服务

中国互联网举报中心

北京互联网违法和不良信息举报中心

转 大道至简——RISC-V架构之魂(中)

2018年03月16日 13:52:32

阅读数:2310

�

本文为《RISC-V CPU设计》专栏和《RISC-V嵌入式软件开发》专栏系列文章之一。

注:本文节选自“硅农亚历山大”所著国内第一本系统介绍CPU与RISC-V设计的中文书籍《手把手教你设计CPU:RISC-V处理器篇》(预计将于

2018年3~4月上市)。

原文出处:大道至简——RISC-V架构之魂(中)

“大道至简——RISC-V架构之魂”——分成上中下三篇,本文是中篇。关注文末公众号后可查询上中下三篇的内容。

本文上接《大道至简——RISC-V架构之魂(上)》

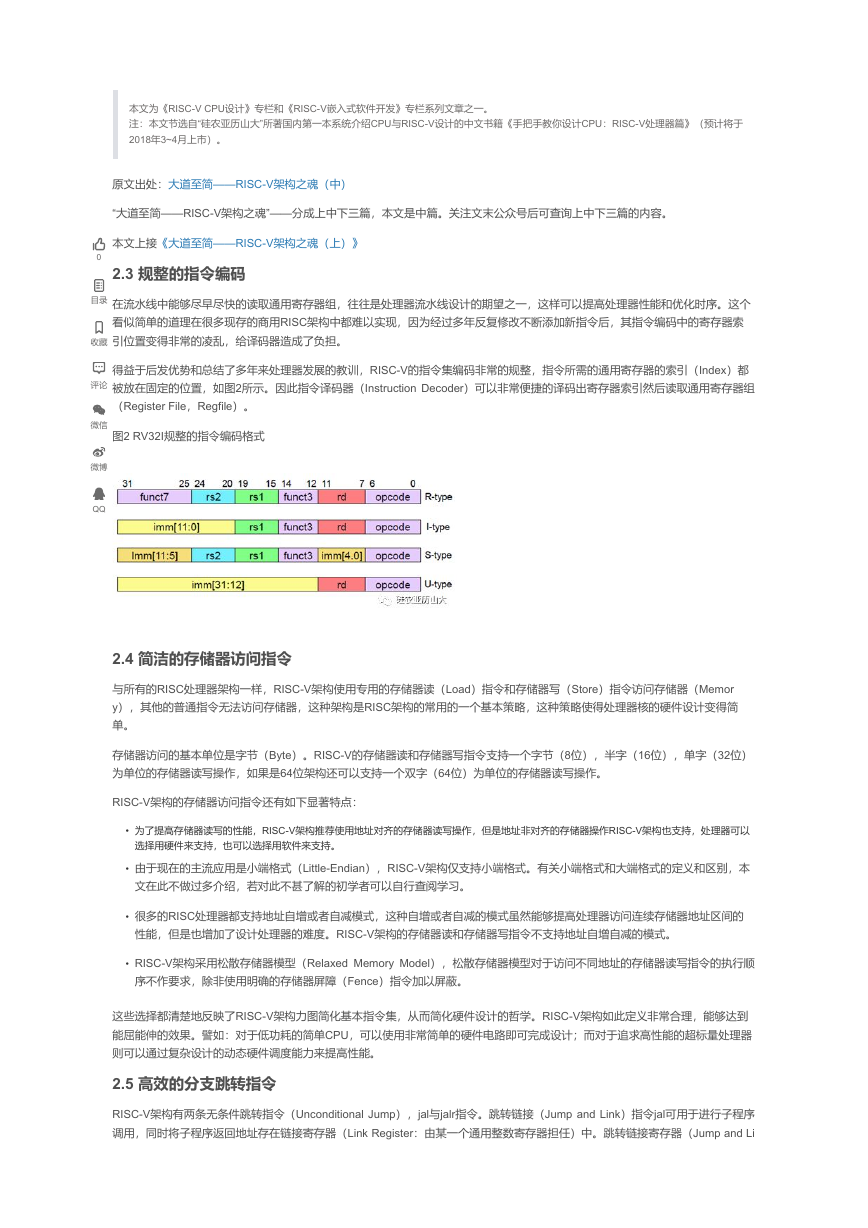

2.3 规整的指令编码

在流水线中能够尽早尽快的读取通用寄存器组,往往是处理器流水线设计的期望之一,这样可以提高处理器性能和优化时序。这个

看似简单的道理在很多现存的商用RISC架构中都难以实现,因为经过多年反复修改不断添加新指令后,其指令编码中的寄存器索

引位置变得非常的凌乱,给译码器造成了负担。

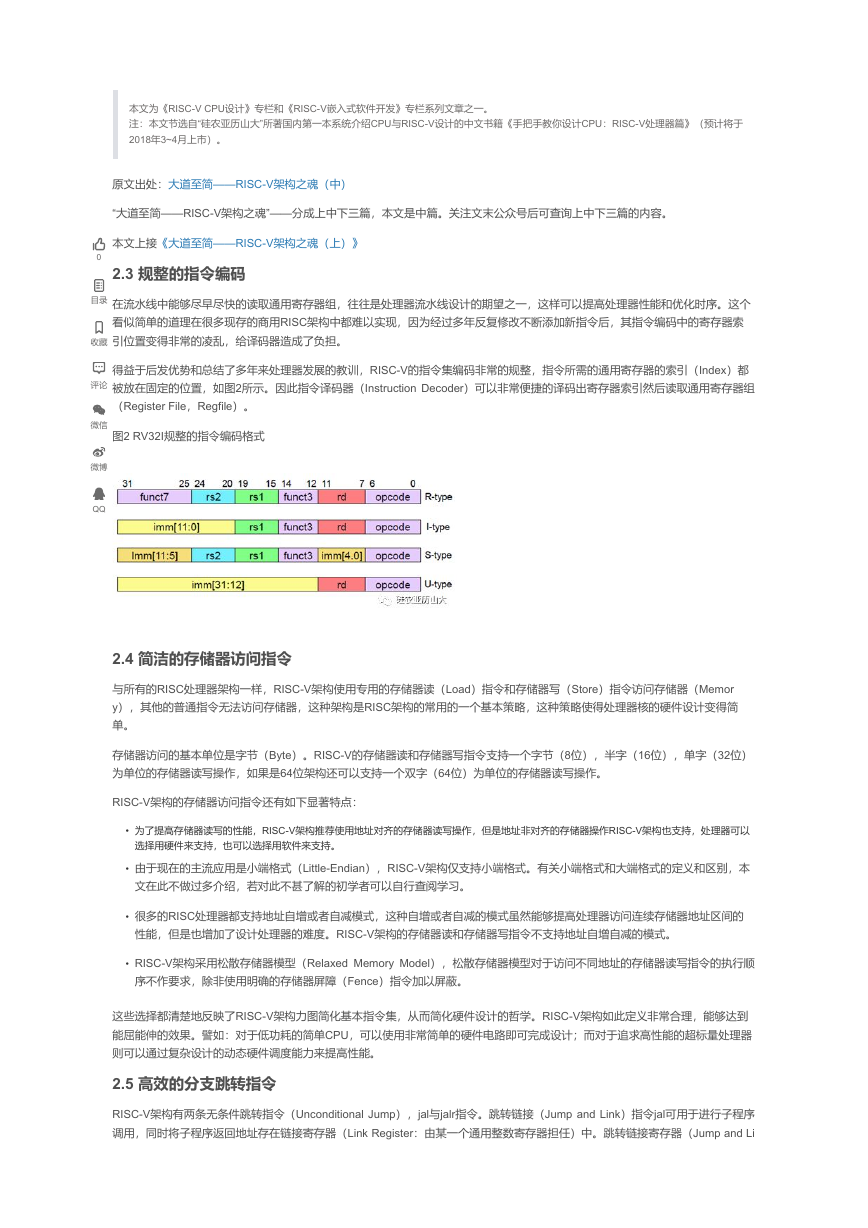

得益于后发优势和总结了多年来处理器发展的教训,RISC-V的指令集编码非常的规整,指令所需的通用寄存器的索引(Index)都

被放在固定的位置,如图2所示。因此指令译码器(Instruction Decoder)可以非常便捷的译码出寄存器索引然后读取通用寄存器组

(Register File,Regfile)。

图2 RV32I规整的指令编码格式

0

目录

收藏

评论

微信

微博

QQ

2.4 简洁的存储器访问指令

与所有的RISC处理器架构一样,RISC-V架构使用专用的存储器读(Load)指令和存储器写(Store)指令访问存储器(Memor

y),其他的普通指令无法访问存储器,这种架构是RISC架构的常用的一个基本策略,这种策略使得处理器核的硬件设计变得简

单。

存储器访问的基本单位是字节(Byte)。RISC-V的存储器读和存储器写指令支持一个字节(8位),半字(16位),单字(32位)

为单位的存储器读写操作,如果是64位架构还可以支持一个双字(64位)为单位的存储器读写操作。

RISC-V架构的存储器访问指令还有如下显著特点:

• 为了提高存储器读写的性能,RISC-V架构推荐使用地址对齐的存储器读写操作,但是地址非对齐的存储器操作RISC-V架构也支持,处理器可以

选择用硬件来支持,也可以选择用软件来支持。

• 由于现在的主流应用是小端格式(Little-Endian),RISC-V架构仅支持小端格式。有关小端格式和大端格式的定义和区别,本

文在此不做过多介绍,若对此不甚了解的初学者可以自行查阅学习。

• 很多的RISC处理器都支持地址自增或者自减模式,这种自增或者自减的模式虽然能够提高处理器访问连续存储器地址区间的

性能,但是也增加了设计处理器的难度。RISC-V架构的存储器读和存储器写指令不支持地址自增自减的模式。

• RISC-V架构采用松散存储器模型(Relaxed Memory Model),松散存储器模型对于访问不同地址的存储器读写指令的执行顺

序不作要求,除非使用明确的存储器屏障(Fence)指令加以屏蔽。

这些选择都清楚地反映了RISC-V架构力图简化基本指令集,从而简化硬件设计的哲学。RISC-V架构如此定义非常合理,能够达到

能屈能伸的效果。譬如:对于低功耗的简单CPU,可以使用非常简单的硬件电路即可完成设计;而对于追求高性能的超标量处理器

则可以通过复杂设计的动态硬件调度能力来提高性能。

2.5 高效的分支跳转指令

RISC-V架构有两条无条件跳转指令(Unconditional Jump),jal与jalr指令。跳转链接(Jump and Link)指令jal可用于进行子程序

调用,同时将子程序返回地址存在链接寄存器(Link Register:由某一个通用整数寄存器担任)中。跳转链接寄存器(Jump and Li

�

nk-Register)指令jalr指令能够用于子程序返回指令,通过将jal指令(跳转进入子程序)保存的链接寄存器用于jalr指令的基地址寄

存器,则可以从子程序返回。

RISC-V架构有6条带条件跳转指令(Conditional

数,然后对其进行比较,如果比较的条件满足时,则进行跳转。因此,此类指令将比较与跳转两个操作放到了一条指令里完成。

Branch),这种带条件的跳转指令跟普通的运算指令一样直接使用2个整数操作

作为比较,很多的其他RISC架构的处理器需要使用两条独立的指令。第一条指令先使用比较指令,比较的结果被保存到状态寄存

器之中;第二条指令使用跳转指令,判断前一条指令保存在状态寄存器当中的比较结果为真时则进行跳转。相比而言RISC-V的这

种带条件跳转指令不仅减少了指令的条数,同时硬件设计上更加简单。

对于没有配备硬件分支预测器的低端CPU,为了保证其性能,RISC-V的架构明确要求其采用默认的静态分支预测机制,即:如果

是向后跳转的条件跳转指令,则预测为“跳”;如果是向前跳转的条件跳转指令,则预测为“不跳”,并且RISC-V架构要求编译器也按

照这种默认的静态分支预测机制来编译生成汇编代码,从而让低端的CPU也能得到不错的性能。

为了使硬件设计尽量简单,RISC-V架构特地定义了所有的带条件跳转指令跳转目标的偏移量(相对于当前指令的地址)都是有符

号数,并且其符号位被编码在固定的位置。因此,这种静态预测机制在硬件上非常容易实现,硬件译码器可以轻松的找到这个固定

的位置,并判断其是0还是1来判断其是正数还是负数,如果是负数则表示跳转的目标地址为当前地址减去偏移量,也就是向后跳

转,则预测为“跳”。当然对于配备有硬件分支预测器的高端CPU,则可以采用高级的动态分支预测机制来保证性能。

2.6 简洁的子程序调用

为了理解此节,需先对一般RISC架构中程序调用子函数的过程予以介绍,其过程如下:

• 进入子函数之后需要用存储器写(Store)指令来将当前的上下文(通用寄存器等的值)保存到系统存储器的堆栈区内,这个

过程通常称为“保存现场”。

0

目录

收藏

评论

微信

微博

QQ

• 在退出子程序之时,需要用存储器读(Load)指令来将之前保存的上下文(通用寄存器等的值)从系统存储器的堆栈区读出

来,这个过程通常称为“恢复现场”。

“保存现场”和“恢复现场”的过程通常由编译器编译生成的指令来完成,使用高层语言(譬如C或者C++)开发的开发者对此可以不用

太关心。高层语言的程序中直接写上一个子函数调用即可,但是这个底层发生的“保存现场”和“恢复现场”的过程却是实实在在地发生

着(可以从编译出的汇编语言里面看到那些“保存现场”和“恢复现场”的汇编指令),并且还需要消耗若干的CPU执行时间。

为了加速这个“保存现场”和“恢复现场”的过程,有的RISC架构发明了一次写多个寄存器到存储器中(Store Multiple),或者一次从

存储器中读多个寄存器出来(Load Multiple)的指令,此类指令的好处是一条指令就可以完成很多事情,从而减少汇编指令的代码

量,节省代码的空间大小。但是此种“Load Multiple”和“Store Multiple”的弊端是会让CPU的硬件设计变得复杂,增加硬件的开销,

也可能损伤时序使得CPU的主频无法提高,笔者在曾经设计此类处理器时便深受其苦。

RISC-V架构则放弃使用这种“Load Multiple”和“Store Multiple”指令。并解释,如果有的场合比较介意这种“保存现场”和“恢复现场”的

指令条数,那么可以使用公用的程序库(专门用于保存和恢复现场)来进行,这样就可以省掉在每个子函数调用的过程中都放置数

目不等的“保存现场”和“恢复现场”的指令。

此选择再次印证了RISC-V追求硬件简单的哲学,因为放弃“Load Multiple”和“Store Multiple”指令可以大幅简化CPU的硬件设计,对

于低功耗小面积的CPU可以选择非常简单的电路进行实现,而高性能超标量处理器由于硬件动态调度能力很强,可以有强大的分支

预测电路保证CPU能够快速的跳转执行,从而可以选择使用公用的程序库(专门用于保存和恢复现场)的方式减少代码量,但是同

时达到高性能。

2.7 无条件码执行

很多早期的RISC架构发明了带条件码的指令,譬如在指令编码的头几位表示的是条件码(Conditional Code),只有该条件码对应

的条件为真时,该指令才被真正执行。

这种将条件码编码到指令中的形式可以使得编译器将短小的循环编译成带条件码的指令,而不用编译成分支跳转指令。这样便减少

了分支跳转的出现,一方面减少了指令的数目;另一方面也避免了分支跳转带来的性能损失。然而,这种“条件码”指令的弊端同样

会使得CPU的硬件设计变得复杂,增加硬件的开销,也可能损伤时序使得CPU的主频无法提高,笔者在曾经设计此类处理器时便深

受其苦。

RISC-V架构则放弃使用这种带“条件码”指令的方式,对于任何的条件判断都使用普通的带条件分支跳转指令。此选择再次印证了RI

SC-V追求硬件简单的哲学,因为放弃带“条件码”指令的方式可以大幅简化CPU的硬件设计,对于低功耗小面积的CPU可以选择非常

简单的电路进行实现,而高性能超标量处理器由于硬件动态调度能力很强,可以有强大的分支预测电路保证CPU能够快速的跳转执

行达到高性能。

�

2.8 无分支延迟槽

很多早期的RISC架构均使用了“分支延迟槽(Delay Slot)”,最具有代表性的便是MIPS架构,在很多经典的计算机体系结构教材

中,均使用MIPS对分支延迟槽进行过介绍。分支延迟槽就是指在每一条分支指令后面紧跟的一条或者若干条指令不受分支跳转的

影响,不管分支是否跳转,这后面的几条指令都一定会被执行。

早期的RISC架构很多采用了分支延迟槽诞生的原因主要是因为当时的处理器流水线比较简单,没有使用高级的硬件动态分支预测

器,所以使用分支延迟槽能够取得可观的性能效果。然而,这种分支延迟槽使得CPU的硬件设计变得极为的别扭,CPU设计人员对

此往往苦不堪言。

RISC-V架构则放弃了分支延迟槽,再次印证了RISC-V力图简化硬件的哲学,因为现代的高性能处理器的分支预测算法精度已经非

常高,可以有强大的分支预测电路保证CPU能够准确的预测跳转执行达到高性能。而对于低功耗小面积的CPU,由于无需支持分支

延迟槽,硬件得到极大简化,也能进一步减少功耗和提高时序。

2.9 无零开销硬件循环

很多RISC架构还支持零开销硬件循环(Zero Overhead Hardware Loop)指令,其思想是通过硬件的直接参与,通过设置某些循环

次数寄存器(Loop Count),然后可以让程序自动地进行循环,每一次循环则Loop Count自动减1,这样持续循环直到Loop Count

的值变成0,则退出循环。

之所以提出发明这种硬件协助的零开销循环是因为在软件代码中的for 循环( for i=0; i

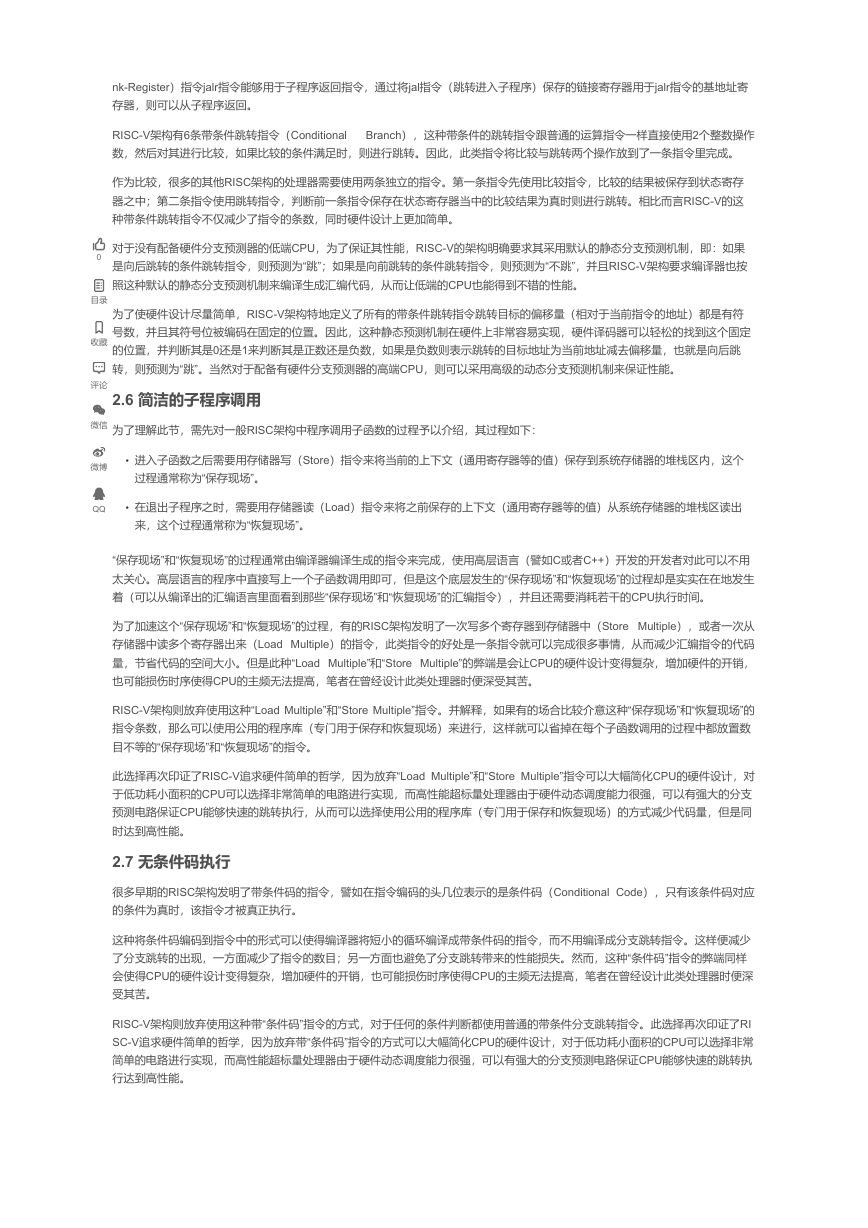

图3 各指令集架构的代码密度比较(数据越小越好)

0

目录

收藏

评论

“大道至简——RISC-V架构之魂”——分成上中下三篇,本文是中篇。关注文末公众号后可查询上中下三篇的内容。

本文上接《大道至简——RISC-V架构之魂(上)》

微信

(未完待续:请参见《大道至简——RISC-V架构之魂(下)》)

更多信息

微博

感兴趣的读者可以通过下面二维码关注公众号“硅农亚历山大”,了解Verilog、IC设计、CPU、RISC-V和人工智能AI相关的更多设计

技巧和经验分享,注意:由于干货太多,请自备茶水。

QQ

文章标签: RISC-V

个人分类: 微控制器

看后秒懂!从小白到AI大神,一份清晰的学习路线

查看更多>>

想对作者说点什么

Lee_feiyue

2018-04-20 08:56:54

#1楼

11

�

0

目录

收藏

评论

微信

微博

QQ

上一页 1 下一页

大道至简 - 大型电商平台从架构剖析设计到功能实现全程实录

本课程从无到有,搭建一个简易版的电商平台,并从不同角度分析设计此项目各个主要模块和功能点,将会应用到除迭代器模式以外的所有GoF设计

模式,旨在演示设计模式在项目中的实际应用,以及如何针对不同情况进行功能设计,希望可以帮助大家敲开设计之门。

学院 2018年01月23日 14:44

大道至简——RISC-V架构之魂(上)

本文为《RISC-V CPU设计》专栏和《RISC-V嵌入式软件开发》专栏系列文章之一。 注:本文节选自“硅农亚历山大”所著国内第一本系统介绍CPU与

RISC-V设计的中文书籍《手把手教你...

zoomdy

2018-03-16 13:33:37 阅读数:2961

程序员必读学习宝典!

必读!追随新技术浪潮!

广告

RISC-V学习第一篇 - boom环境的建立

一、相关工具 系统: RHEL 6.8 x64 GCC: 4.8.2 虚拟机; VMware 12 二、步骤 1. 第一步要升级GCC,因为RHEL 6.8的GCC版本好像是4.4.7,在后面

建立...

MayCiCi

2017-06-04 11:17:52 阅读数:4976

RISC-V架构能否让国产IC真正“自主研发”?

...

cf2SudS8x8F0v

2018-04-20 00:00:00 阅读数:446

RISC-V结构逻辑图

说明: 执行共有6级流水作业: 1. fetch(取指令) 2. decode(译码) 3. dispatch/renaming(分发/重命名) 4. select/wakeup(选择/唤醒) 5. ...

zzwu

2017-02-01 20:13:29 阅读数:2813

对RISC-V前途的一些看法

我是比较看好RISC-V的前途的,首先它出自大名鼎鼎的UC Berkeley;并且成立了RISC-V基金会,基金会成员中不乏高通这样的半导体公司和谷歌这

样的软件公司;它采用了比较宽松的BSD授权方式,...

zoomdy

2018-02-22 19:13:01 阅读数:724

程序猿不会英语怎么行?!试试这个数学公式

老司机教你一个数学公式秒懂天下英语

RISC-V介绍(无参考,但带图解)

risk-v介绍

zzwu

2017-02-01 12:09:23 阅读数:2829

RISC-V汇编指南

原文出处:https://github.com/riscv/riscv-asm-manual/blob/master/riscv-asm.md RISC-V Assembly Programme...

zoomdy

2018-02-23 16:16:56 阅读数:484

RISC-V相关的开源项目

和RISC-V相关的有如下一些开源项目: 工具链 1、riscv-tools - 基本上所有RISC-V相关工具链、仿真器、测试的宏项目,包含以下的项目 riscv-gnu

-t...

u013710265

2017-04-21 17:37:04 阅读数:4421

�

RISC-V

1、简介 “V”包含两层意思,一是这是Berkeley从RISC I开始设计的第五代指令集架构,二是它代表了变化(variation)和向量(vectors)。 RISC-V包含一

个非常小...

u013710265

2017-04-21 10:33:08 阅读数:1268

基于RISC-V架构的开源处理器及SoC研究综述(三)

RISC-V是一种新的指令集架构,发布以来得到了大量关注,在描述了RISC-V的产生背景、基本设计的基础上,简单比较了其与现有的开源指令集架

构、商业指令集架构的优劣,随后详细介绍了现有的采用RISC-...

0

leishangwen

2017-02-12 22:32:49 阅读数:3828

目录

RISC-V的开源性与用途

RISC-V 开源指令集 RISC-V介绍: RISC-V (pronounced "risk-five") is an open instruction set archi...

收藏

zzwu

2017-01-31 08:27:21 阅读数:2647

评论

微信

微博

QQ

RISC-V维基介绍,有参考(英文)

RISC-V From Wikipedia, the free encyclopedia RISC-V Designer University of California, Berk...

zzwu

2017-01-31 09:44:14 阅读数:1407

使用 OpenOCD 进行单步调试

虽然不喜欢进行单步调试,但是不可否认它的重要性,所以也尝试了一下,以帮助后来有需要的小伙伴。关于 ESP32 的更多博客,请查看 【ESP32

系列博客 - 目录】【安装 OpenOCD】 本人使...

tidyjiang

2017-05-22 15:25:48 阅读数:2502

50万码农评论:英语对于程序员有多重要?

不背单词和语法,一个公式学好英语

risc-v文档

2017年10月13日 1.9MB

下载

大量的RISC-V文章(可下载)

大量的RISC-V文章 下面是用户共享的文件列表,安装电驴后,您可以点击这些文件名进行下载 [开源精简指令集处理器RISC-V].homebrew-riscv-mas

ter.zip 3....

zzwu

2017-01-31 10:11:27 阅读数:5237

包云岗:关于RISC-V成为印度国家指令集的一些看法

作者 | 包云岗本文于2017年11月28日完稿,将在《中国计算机学会通讯》2018年第1期发表。处理器指令集是软硬件的接口,是核心基础软硬件生态

系统的基石,其重要性不言而喻。2011年加州大学伯克利...

dQCFKyQDXYm3F8rB0

2017-12-12 00:00:00 阅读数:700

基于RISC-V架构的开源处理器及SoC研究综述(二)

RISC-V是一种新的指令集架构,发布以来得到了大量关注,在描述了RISC-V的产生背景、基本设计的基础上,简单比较了其与现有的开源指令集架

构、商业指令集架构的优劣,随后详细介绍了现有的采用RISC-...

leishangwen

2017-02-12 22:30:12 阅读数:3994

基于RISC-V架构的开源处理器及SoC研究综述(一)

RISC-V是一种新的指令集架构,发布以来得到了大量关注,在描述了RISC-V的产生背景、基本设计的基础上,简单比较了其与现有的开源指令集架

构、商业指令集架构的优劣,随后详细介绍了现有的采用RISC-...

leishangwen

2017-02-12 22:24:56 阅读数:5345

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc