�

SystemVerilog

For Design

Second Edition

A Guide to Using SystemVerilog

for Hardware Design and Modeling

SystemVerilog

For Design

Second Edition

A Guide to Using SystemVerilog

for Hardware Design and Modeling

by

Stuart Sutherland

Simon Davidmann

Peter Flake

Foreword by Phil Moorby

1 3

�

Stuart Sutherland

Sutherland DHL, Inc.

22805 SW 92nd Place

Tualatin, OR 97062

USA

Simon Davidmann

The Old Vicerage

Priest End

Thame, Oxfordshire 0X9 3AB

United Kingdom

Peter Flake

Imperas, Ltd.

Imperas Buildings, North Weston

Thame, Oxfordshire 0X9 2HA

United Kingdom

SystemVerilog for Design, Second Edition

A Guide to Using SystemVerilog for Hardware Design and Modeling

Library of Congress Control Number: 2006928944

ISBN-10: 0-387-33399-1

ISBN-13: 9780387333991

e-ISBN-10: 0-387-36495-1

e-ISBN-13: 9780387364957

Printed on acid-free paper.

© 2006 Springer Science+Business Media, LLC

All rights reserved. This work may not be translated or copied in whole or in part without

the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring

Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or

scholarly analysis. Use in connection with any form of information storage and retrieval,

electronic adaptation, computer software, or by similar or dissimilar methodology now

known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms,

even if they are not identified as such, is not to be taken as an expression of opinion as to

whether or not they are subject to proprietary rights.

Printed in the United States of America.

9 8 7 6 5 4 3 2

springer.com

�

Dedications

To my wonderful wife, LeeAnn, and my children, Ammon, Tamara, Hannah, Seth and

Samuel — thank you for all your patience during the many long hours and late nights

while writing this book.

Stuart Sutherland

Portland, Oregon

To all of the staff of Co-Design and the many EDA colleagues that worked with me

over the years — thank you for helping to evolve Verilog and make its extension and

evolution a reality. And to Penny, Emma and Charles — thank you for allowing me

the time to indulge in language design (and in cars and guitars...).

Simon Davidmann

Santa Clara, California

To my wife Monique, for supporting me when I was not working, and when I was

working too much.

Peter Flake

Thame, UK

�

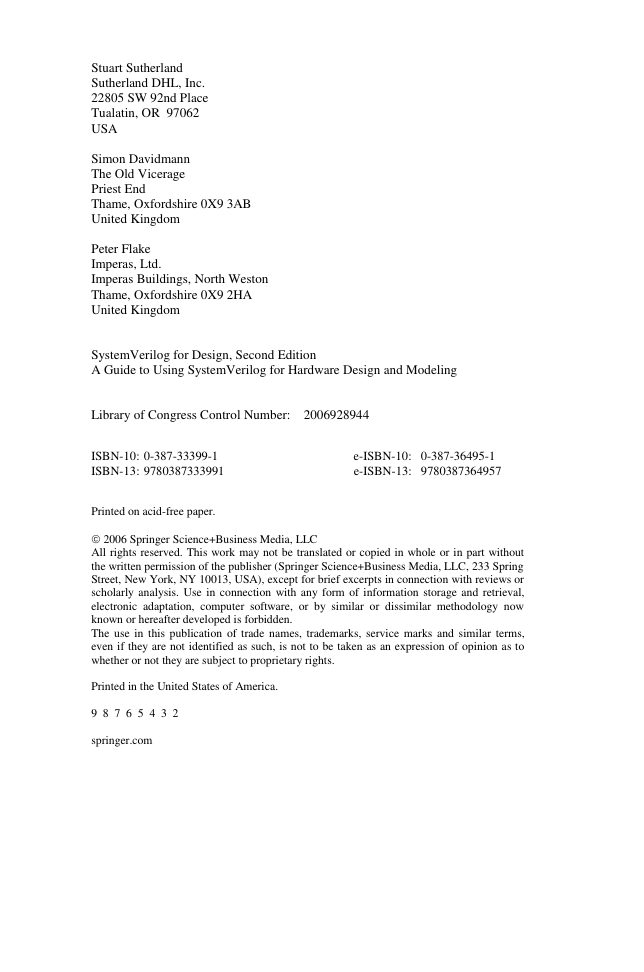

Table of Contents

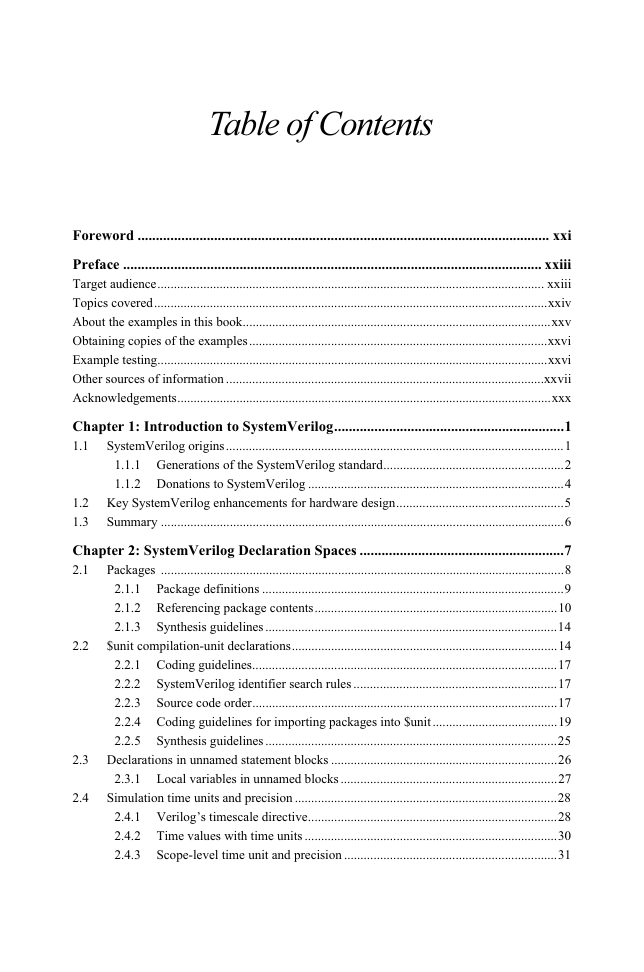

Foreword ................................................................................................................. xxi

Preface ................................................................................................................... xxiii

Target audience...................................................................................................................... xxiii

Topics covered........................................................................................................................xxiv

About the examples in this book..............................................................................................xxv

Obtaining copies of the examples...........................................................................................xxvi

Example testing.......................................................................................................................xxvi

Other sources of information .................................................................................................xxvii

Acknowledgements..................................................................................................................xxx

Chapter 1: Introduction to SystemVerilog...............................................................1

1.1

SystemVerilog origins.......................................................................................................1

1.1.1 Generations of the SystemVerilog standard.......................................................2

1.1.2 Donations to SystemVerilog ..............................................................................4

1.2 Key SystemVerilog enhancements for hardware design...................................................5

1.3

Summary ...........................................................................................................................6

Chapter 2: SystemVerilog Declaration Spaces ........................................................7

Packages ...........................................................................................................................8

2.1

2.1.1

Package definitions ............................................................................................9

2.1.2 Referencing package contents..........................................................................10

2.1.3

Synthesis guidelines.........................................................................................14

$unit compilation-unit declarations.................................................................................14

2.2.1 Coding guidelines.............................................................................................17

SystemVerilog identifier search rules ..............................................................17

2.2.2

2.2.3

Source code order.............................................................................................17

2.2.4 Coding guidelines for importing packages into $unit......................................19

2.2.5

Synthesis guidelines.........................................................................................25

2.3 Declarations in unnamed statement blocks .....................................................................26

2.3.1 Local variables in unnamed blocks..................................................................27

Simulation time units and precision ................................................................................28

2.4.1 Verilog’s timescale directive............................................................................28

2.4.2 Time values with time units .............................................................................30

2.4.3

Scope-level time unit and precision .................................................................31

2.2

2.4

�

3.3

3.5

3.6

3.7

2.4.4 Compilation-unit time units and precision.......................................................32

2.5

Summary .........................................................................................................................34

Chapter 3: SystemVerilog Literal Values and Built-in Data Types.....................37

Enhanced literal value assignments.................................................................................38

3.1

‘define enhancements......................................................................................................39

3.2

3.2.1 Macro argument substitution within strings.....................................................39

3.2.2 Constructing identifier names from macros.....................................................41

SystemVerilog variables..................................................................................................42

3.3.1 Object types and data types..............................................................................42

3.3.2

SystemVerilog 4-state variables.......................................................................43

3.3.3

SystemVerilog 2-state variables.......................................................................44

3.3.4 Explicit and implicit variable and net data types .............................................47

3.3.5

Synthesis guidelines.........................................................................................48

3.4 Using 2-state types in RTL models .................................................................................48

2-state type characteristics ...............................................................................49

3.4.1

3.4.2

2-state types versus 2-state simulation.............................................................49

3.4.3 Using 2-state types with case statements .........................................................51

Relaxation of type rules...................................................................................................52

Signed and unsigned modifiers .......................................................................................55

Static and automatic variables.........................................................................................56

3.7.1

Static and automatic variable initialization ......................................................59

3.7.2

Synthesis guidelines for automatic variables ...................................................60

3.7.3 Guidelines for using static and automatic variables.........................................61

3.8 Deterministic variable initialization ................................................................................61

Initialization determinism ................................................................................61

3.8.1

3.8.2

Initializing sequential logic asynchronous inputs ............................................65

Type casting ....................................................................................................................67

3.9.1

Static (compile time) casting............................................................................67

3.9.2 Dynamic casting...............................................................................................69

Synthesis guidelines.........................................................................................70

3.9.3

3.10 Constants .........................................................................................................................71

3.11 Summary .........................................................................................................................72

Chapter 4: SystemVerilog User-Defined and Enumerated Types .......................75

4.1 User-defined types...........................................................................................................75

4.1.1 Local typedef definitions..................................................................................76

4.1.2

Shared typedef definitions................................................................................76

4.1.3 Naming convention for user-defined types ......................................................78

Enumerated types ............................................................................................................79

4.2.1 Enumerated type label sequences.....................................................................83

3.9

4.2

viii

�

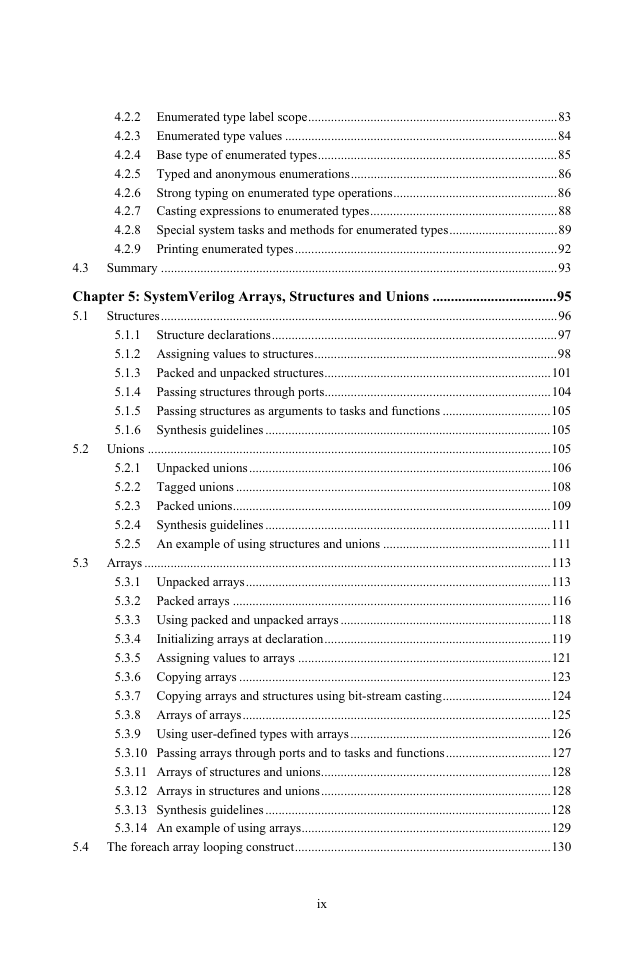

4.2.2 Enumerated type label scope............................................................................83

4.2.3 Enumerated type values ...................................................................................84

4.2.4 Base type of enumerated types.........................................................................85

4.2.5 Typed and anonymous enumerations...............................................................86

4.2.6

Strong typing on enumerated type operations..................................................86

4.2.7 Casting expressions to enumerated types.........................................................88

4.2.8

Special system tasks and methods for enumerated types.................................89

4.2.9

Printing enumerated types................................................................................92

4.3

Summary .........................................................................................................................93

Chapter 5: SystemVerilog Arrays, Structures and Unions ..................................95

Structures.........................................................................................................................96

5.1

5.1.1

Structure declarations.......................................................................................97

5.1.2 Assigning values to structures..........................................................................98

5.1.3

Packed and unpacked structures.....................................................................101

Passing structures through ports.....................................................................104

5.1.4

Passing structures as arguments to tasks and functions .................................105

5.1.5

5.1.6

Synthesis guidelines.......................................................................................105

5.2 Unions ...........................................................................................................................105

5.2.1 Unpacked unions............................................................................................106

5.2.2 Tagged unions ................................................................................................108

5.2.3

Packed unions.................................................................................................109

5.2.4

Synthesis guidelines.......................................................................................111

5.2.5 An example of using structures and unions ...................................................111

5.3 Arrays ............................................................................................................................113

5.3.1 Unpacked arrays.............................................................................................113

5.3.2

Packed arrays .................................................................................................116

5.3.3 Using packed and unpacked arrays................................................................118

5.3.4

Initializing arrays at declaration.....................................................................119

5.3.5 Assigning values to arrays .............................................................................121

5.3.6 Copying arrays ...............................................................................................123

5.3.7 Copying arrays and structures using bit-stream casting.................................124

5.3.8 Arrays of arrays..............................................................................................125

5.3.9 Using user-defined types with arrays.............................................................126

5.3.10 Passing arrays through ports and to tasks and functions................................127

5.3.11 Arrays of structures and unions......................................................................128

5.3.12 Arrays in structures and unions......................................................................128

5.3.13 Synthesis guidelines.......................................................................................128

5.3.14 An example of using arrays............................................................................129

The foreach array looping construct..............................................................................130

5.4

ix

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc