1 Introduction(介绍)

1.1 Overview(概述)

1.1.1NVMe over PCIe and NVMe over Fabrics

1.2Scope(范围)

1.3Outside of Scope(超出范围)

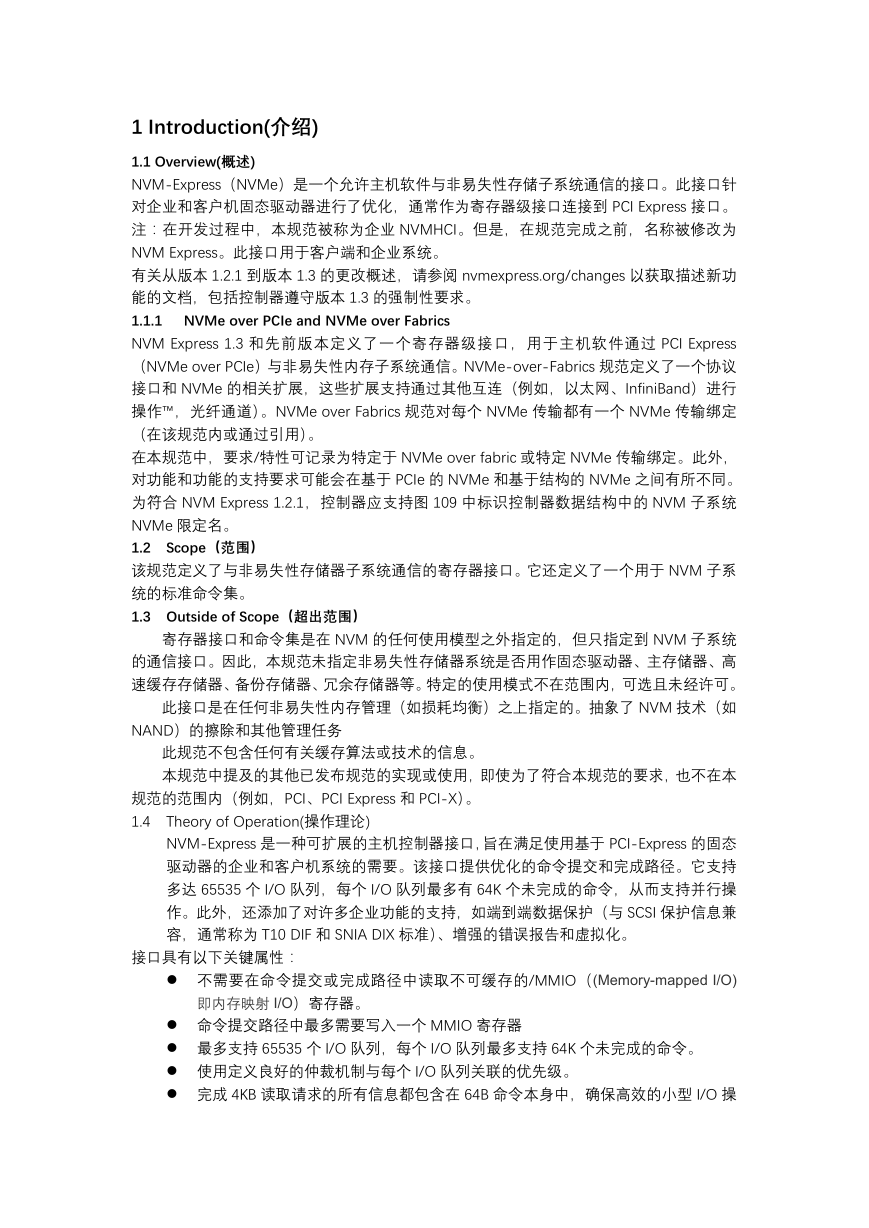

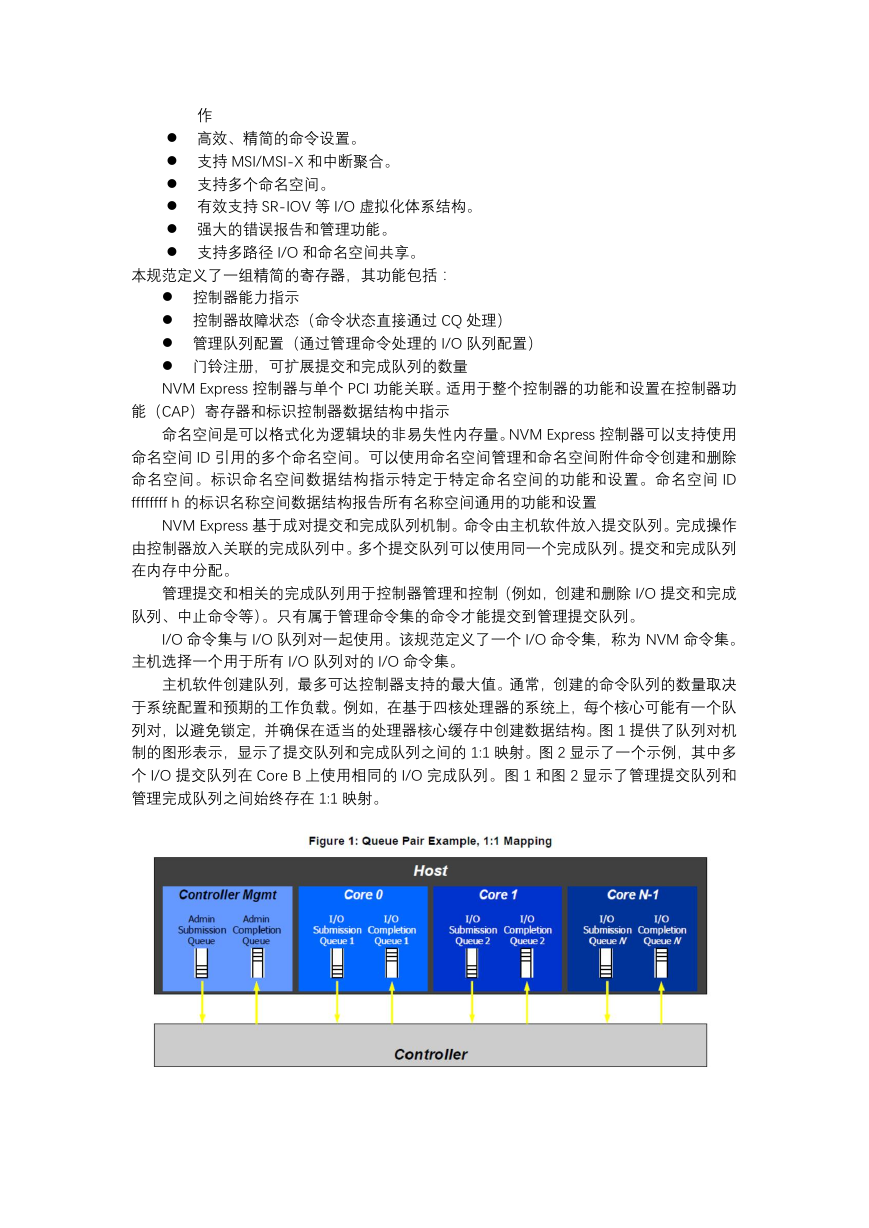

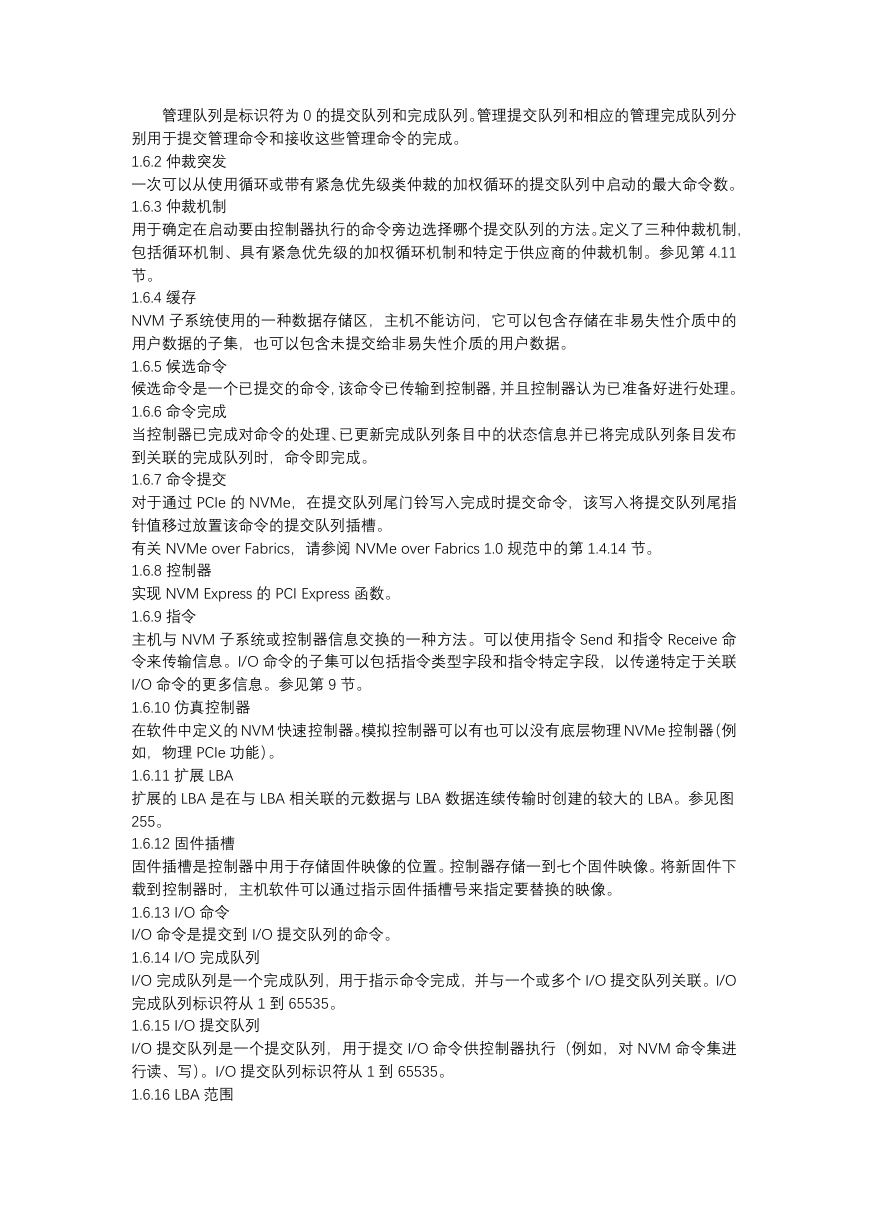

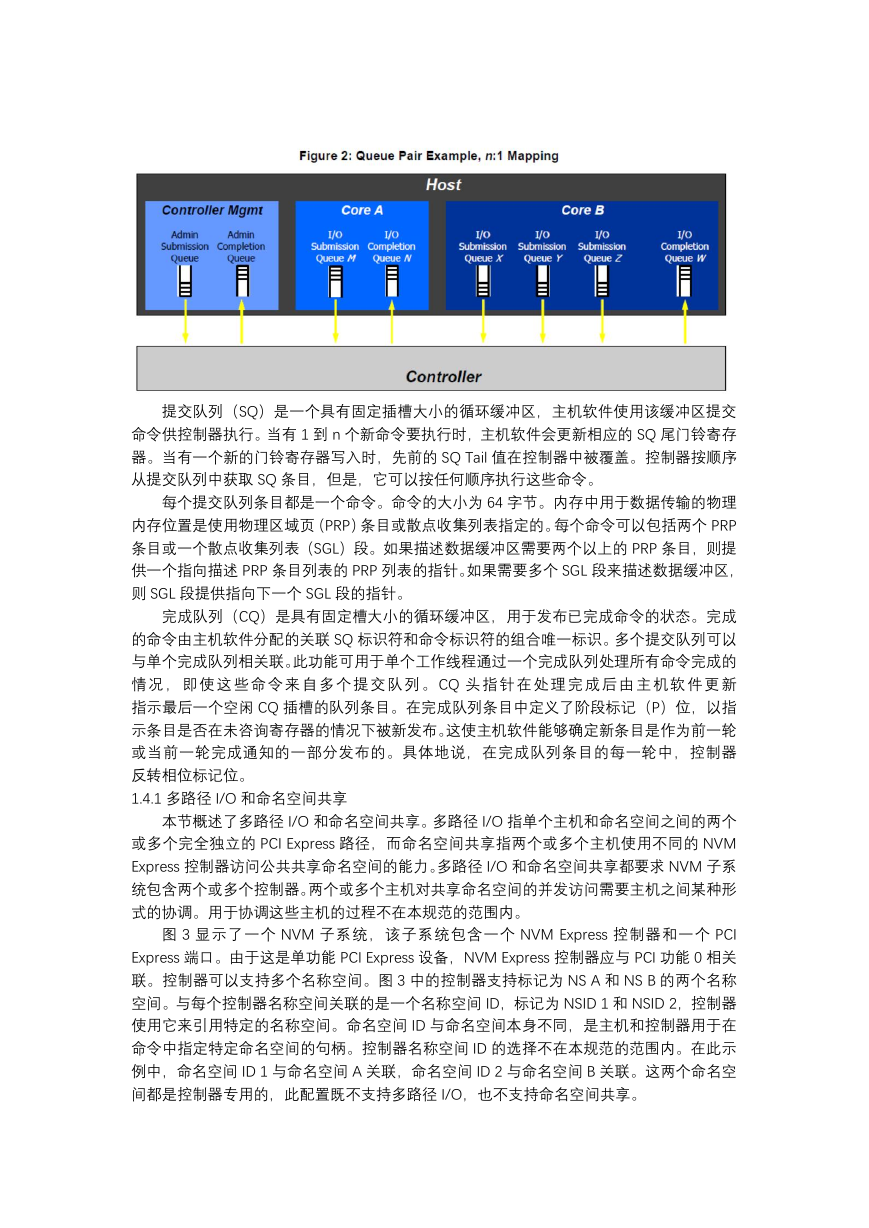

1.4Theory of Operation(操作理论)

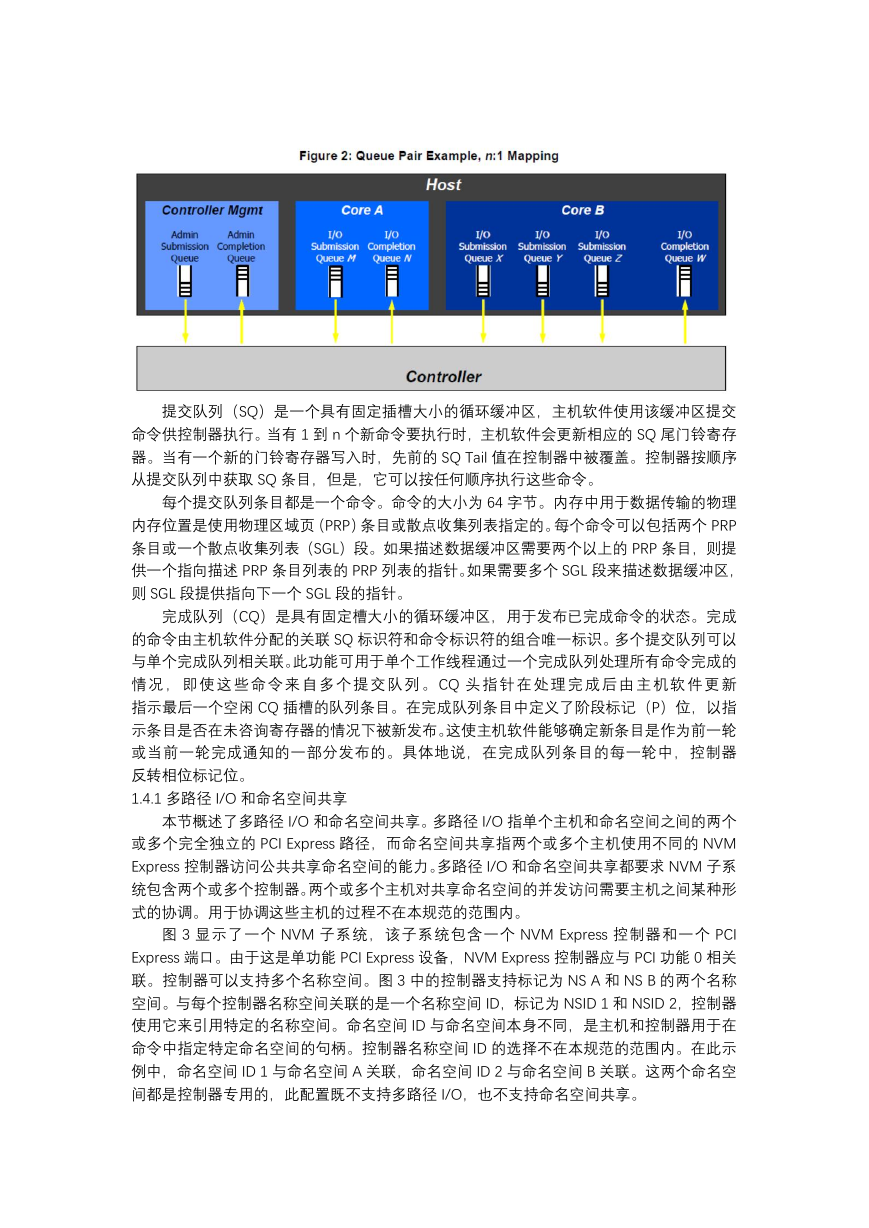

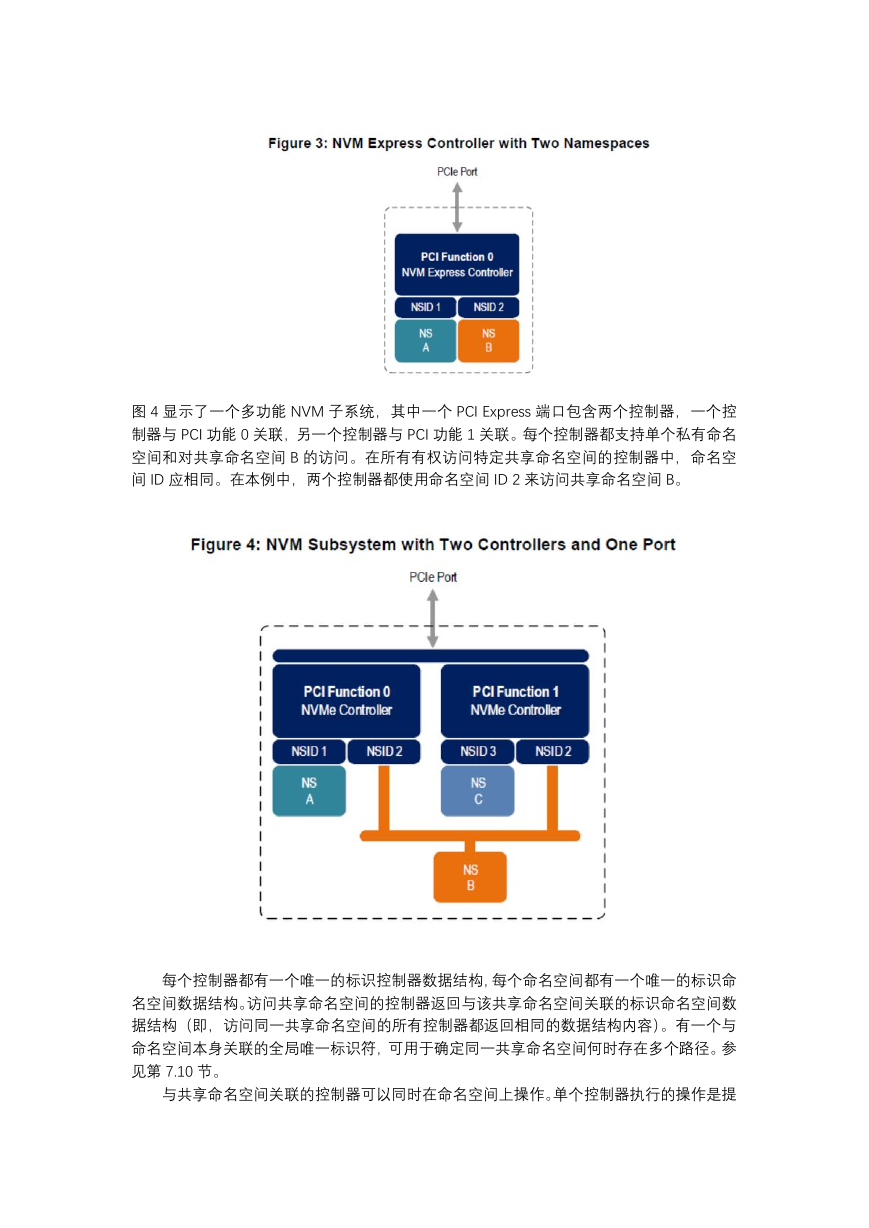

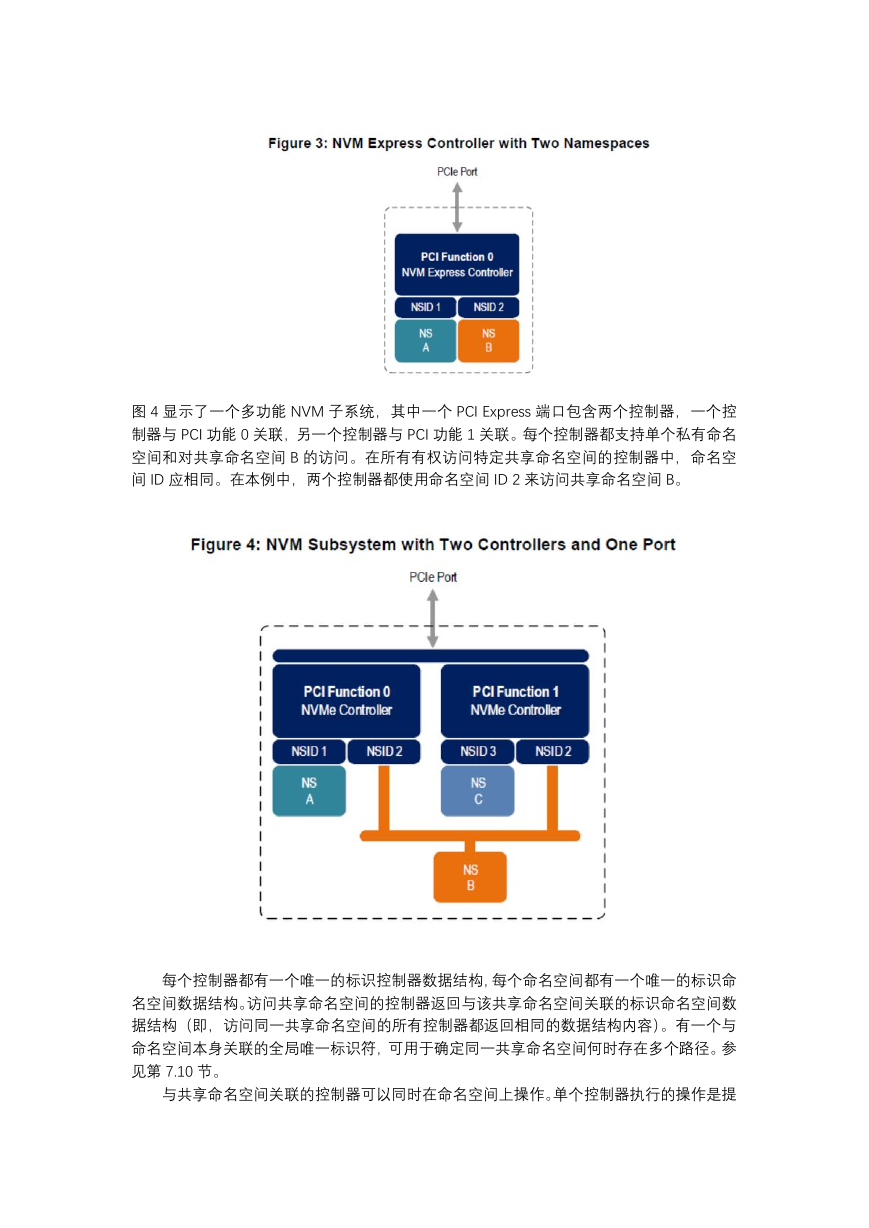

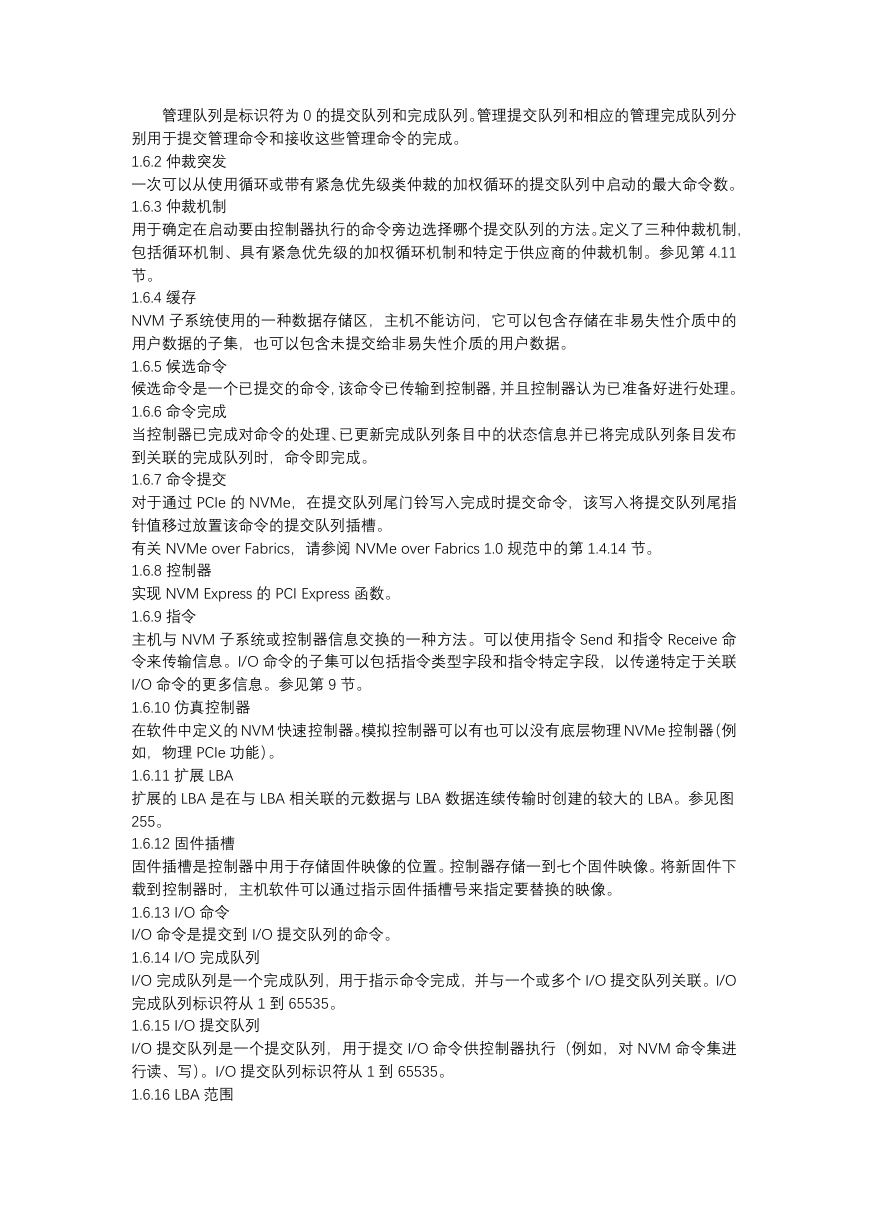

1.4.1多路径I/O和命名空间共享

1.5惯例

1.6定义

1.6.1 Admin Queue

1.6.2仲裁突发

1.6.3仲裁机制

1.6.4缓存

1.6.5候选命令

1.6.6命令完成

1.6.7命令提交

1.6.8控制器

1.6.9指令

1.6.10仿真控制器

1.6.11扩展LBA

1.6.12固件插槽

1.6.13 I/O命令

1.6.14 I/O完成队列

1.6.15 I/O提交队列

1.6.16 LBA范围

1.6.17逻辑块

1.6.18逻辑块地址(LBA)

1.6.19元数据

1.6.20命名空间

1.6.21命名空间ID(NSID)

1.6.22 NVM

1.6.23 NVM子系统

1.6.24主控制器

1.6.25私有命名空间

1.6.26特权行动

1.6.27运行时D3(断电)

1.6.28净化操作

1.6.29二级控制器

1.6.30共享命名空间

1.6.31用户数据

1.7关键词

1.7.1强制性

1.7.2 可以

1.7.3可选

1.7.4 R

1.7.5保留

1.7.6 shall

1.7.7 should

1.8字节、字和双字关系

1.9参考文献

1.10正在开发的参考文献

2. 系统总线(PCI Express)寄存器

2.1 PCI Header

2.1.1偏移量00h:ID-标识符

2.1.2偏移04h:CMD-命令

2.1.3偏移06h:STS-设备状态

2.1.4偏移量08h:RID-修订ID

2.1.5偏移量09h:CC-类别码

2.1.6偏移量0Ch:CLS–缓存线大小

2.1.7偏移量0Dh:MLT主延迟计时器

2.1.8偏移量0Eh:HTYPE–头类型

2.1.9偏移量0Fh:BIST内置自检(可选)

2.1.10偏移量10h:MLBAR(BAR0)–内存寄存器基址,低32位

2.1.11偏移量14h:MUBAR(BAR1)–存储器寄存器基址,高32位

2.1.12偏移18h:BAR2–索引/数据对寄存器基址或特定于供应商(可选)

2.1.13偏移量1Ch-20h:BAR3特定供应商

2.1.14偏移量20h-23h:BAR4特定供应商

2.1.15 24-27小时偏移量:BAR5:特定供应商

2.1.16偏移28h:CCPTR CardBus CIS指针

2.1.18偏移30h:EROM–扩展ROM(可选)

2.1.19偏移34h:CAP-能力指针

2.1.20偏移量3Ch:INTR-中断信息

2.1.21偏移量3Eh:MGNT–最小授权

2.1.22偏移量3Fh:MLAT–最大延迟

2.2 PCI电源管理能力

2.2.1偏移PMCAP:PID-PCI电源管理能力ID

2.2.2偏移PMCAP+2h:PC-PCI电源管理能力

2.2.3偏移PMCAP+4h:PMCS–PCI电源管理控制和状态

2.3 消息信号中断能力(可选)

2.3.1偏移量MSICAP:MID-消息信号中断标识符

2.3.2偏移量MSICAP+2h:MC—消息信号中断消息控制

2.3.3偏移量MSICAP+4h:MA——消息信号中断消息地址

2.3.4偏移量MSICAP+8h:MUA——消息信号中断上限地址

2.3.5偏移量MSICAP+Ch:MD–消息信号中断消息数据

2.3.6偏移量MSICAP+10h:MMASK–消息信号中断屏蔽位(可选)

2.3.7偏移量MSICAP+14h:MPEND–消息信号中断挂起位(可选)

2.4 MSI-X功能(可选)

2.4.1偏移量MSIXCAP:MXID–MSI-X标识符

2.4.2偏移量MSIXCAP+2h:MXC–MSI-X消息控制

2.4.3偏移量MSIXCAP+4h:MTAB–MSI-X表格偏移量/表格BIR

2.4.4偏移MSIXCAP+8h:MPBA–MSI-X PBA偏移/PBA BIR

2.5 PCI Express功能

2.5.1偏移量PXCAP:PXID–PCI Express功能ID

2.5.2偏移量PXCAP+2h:PXCAP–PCI Express功能

2.5.3偏移PXCAP+4h:PXDCAP–PCI Express设备功能

2.5.4偏移PXCAP+8h:PXDC–PCI Express设备控制

2.5.5偏移量PXCAP+Ah:PXDS–PCI Express设备状态

2.5.6偏移PXCAP+Ch:PXLCAP–PCI Express链路能力

2.5.7偏移量PXCAP+10h:PXLC–PCI Express链路控制

2.5.8偏移量PXCAP+12h:PXLS–PCI Express链路状态

2.5.9偏移PXCAP+24小时:PXDCAP2–PCI Express设备功能2

2.5.10偏移量PXCAP+28h:PXDC2–PCI Express设备控制2

2.6高级错误报告功能(可选)

2.6.1偏移AERCAP:AERID–AER能力ID

2.6.2偏移量AERCAP+4:AERUCES–AER不可纠正错误状态寄存器

2.6.3偏移AERCAP+8:AERUCEM–AER不可纠正错误屏蔽寄存器

2.6.4偏移量AERCAP+Ch:AERUCESEV–AER不可纠正错误严重性寄存器

2.6.5偏移AERCAP+10h:AERCS–AER可纠正错误状态寄存器

2.6.6偏移AERCAP+14h:AERCEM–AER可纠正错误屏蔽寄存器

2.6.7偏置AERCAP+18h:AERCC-AER能力和控制寄存器

2.6.8偏移量AERCAP+1Ch:AERHL–AER报头日志寄存器

2.6.9偏移量AERCAP+38h:AERTLP–AER TLP前缀日志寄存器(可选)

2.7其他能力指标

3. 控制器寄存器

3.1寄存器定义

3.1.1偏移00h:CAP–控制器能力

3.1.2偏移量08h:VS–版本

3.1.2.1 1.0兼容控制器的VS值

3.1.3偏移量0Ch:INTMS–中断掩码设置

3.1.4偏移量10h:INTMC–中断屏蔽清除

3.1.5偏移14h:CC–控制器配置

3.1.6偏移量1Ch:CSTS–控制器状态

3.1.7偏移量20h:NSSR–NVM子系统复位

3.1.8 24小时偏移量:AQA–管理队列属性

3.1.9偏移量28h:ASQ–管理员提交队列基地址

3.1.10偏移量30h:ACQ–管理完成队列基地址

3.1.11偏移量38h:CMBLOC–控制器内存缓冲区位置

3.1.12偏移量3Ch:CMBSZ–控制器内存缓冲区大小

3.1.13偏移40h:BPINFO–引导分区信息

3.1.14偏移44h:BPRSEL–引导分区读取选择

3.1.15偏移48h:BPMBL–引导分区内存缓冲区位置(可选)

3.1.16偏移量(1000h+((2y)*(4<

3.1.17偏移量(1000h+((2y+1)*(4<

3.2.1限制

3.2.2寄存器定义

3.2.3偏移量00h:IDX–索引寄存器

3.2.4偏移04h:DAT–数据寄存器

4 数据结构

4.1提交队列和完成队列定义

4.1.1空队列

4.1.2全队列

4.1.3队列大小

4.1.4队列标识符

4.1.5队列优先级

4.2提交队列条目-命令格式

4.3物理区域页面输入和列表

4.4散点集列表(SGL)

4.4.1 SGL示例

4.5元数据区域(MR)

4.6完成队列输入

4.6.1状态字段定义

4.6.1.1状态码类型(SCT)

4.6.1.2状态代码(SC)

4.6.1.2.1通用命令状态定义

4.6.1.2.2命令特定错误定义

4.6.1.2.3媒体和数据完整性错误定义

4.7控制器存储器缓冲器

4.8命名空间列表

4.9控制器链表

4.10融合操作

4.11命令仲裁

4.11.1循环仲裁

4.11.2具有紧急优先级仲裁的加权循环

4.11.3供应商特定仲裁

5管理命令集

5.1中止命令

5.1.1命令完成

5.2异步事件请求命令

5.2.1命令完成

5.3创建I/O完成队列命令

5.3.1命令完成

5.4创建I/O提交队列命令

5.4.1命令完成

5.5删除I/O完成队列命令

5.5.1命令完成

5.6删除I/O提交队列命令

5.6.1命令完成

5.7门铃缓冲器配置命令

5.7.1命令完成

5.8设备自检命令

5.8.1命令完成

5.9指令接收命令

5.9.1命令完成

5.10指令发送命令

5.10.1命令完成

5.11固件提交命令

5.11.1命令完成

5.12固件映像下载命令

5.12.1命令完成

5.13获取特征命令

5.13.1选择字段

5.13.2命令完成

5.14获取日志页命令

5.14.1日志特定信息

5.15.1命令完成

5.16保持活力命令

5.16.1命令完成

5.17 NVMe MI接收命令

5.17.1命令完成

5.18 NVMe MI Send命令

5.18.1命令完成

5.19.1命令完成

5.20名称空间管理命令

5.20.1命令完成

5.21.1特性特定信息

5.21.1.1仲裁(特征标识符01h)

5.21.1.2电源管理(功能标识02h)

5.21.1.3 LBA范围类型(特征标识符03h),(可选)

5.21.1.4温度阈值(特性标识符04h)

5.21.1.5错误恢复(功能标识符05h)

5.21.1.6易失性写缓存(功能标识符06h),(可选)

5.21.1.7队列数量(特征标识符07h)

5.21.1.8中断合并(特征标识符08h)

5.21.1.9中断向量配置(特征标识符09h)

5.21.1.10写入原子性正常(特征标识符0Ah)

5.21.1.11异步事件配置(功能标识符0Bh)

5.21.1.12自主电源状态转换(功能标识符0Ch),(可选)

5.21.1.13主机内存缓冲区(功能标识符0Dh),(可选)

5.21.1.15保持活动计时器(特征标识符0Fh)

5.21.1.16主机控制热管理(功能标识10h),(可选)

5.21.1.17非运行电源状态配置(功能标识符11h),(可选)

5.21.1.18软件进度标记(功能标识符80h),(可选)–特定于NVM命令集

5.21.1.19主机标识符(特征标识符81h),(可选1)

5.21.1.19.1 NVME over PCIE

5.21.1.19.2织物上的NVMe

5.21.1.20预订通知掩码(功能标识符82h),(可选2)

5.21.1.21保留持久性(特征标识符83h),(可选3)

5.21.2命令完成

5.22虚拟化管理指挥部

5.22.1命令完成

5.23格式NVM命令–NVM命令集特定

5.23.1命令完成

5.24 Sanitize命令–特定于NVM命令集

5.24.1命令完成

5.25安全接收命令–特定于NVM命令集

5.25.1命令完成

如果命令完成,则控制器应向管理完成队列发送一个完成队列条目,指示命令的状态。

5.25.3安全协议EAh

5.26安全发送命令–特定于NVM命令集

5.26.1命令完成

6 NVM命令集

6.1名称空间

6.2融合操作

6.2.1比较和写入

6.3指挥命令要求

6.4原子操作

6.4.1AWUN/NAWUN

6.4.1.1 AWUN/NAWUN示例(资料性

6.4.2 AWUPF/NAWUPF标准

6.4.2.1 AWUPF/NAWUPF示例(资料性)

6.4.3原子边界

6.5端到端保护信息

6.6比较命令

6.6.1命令完成

6.7数据集管理命令

6.7.1上下文属性

6.7.1.1解除分配

6.7.2命令完成

6.8刷新命令

6.8.1命令完成

6.9读取命令

6.9.1命令完成

6.10预定获取命令

6.10.1命令完成

6.11保留寄存器命令

6.11.1命令完成

6.12.1命令完成

6.13预订报告命令

6.13.1命令完成

6.14写入命令

6.14.1命令完成

6.15写入不可纠正命令

6.15.1命令完成

6.16写零命令

6.16.1命令完成

7控制器架构

7.1简介

7.2命令提交和完成机制(资料性)

7.2.1命令处理

7.2.2建立命令的基本步骤

7.2.3处理完成的命令

7.2.4与指挥有关的资源退役

7.2.5命令示例

7.2.5.1创建I/O提交队列

7.3重置

7.3.1 NVM子系统复位

7.3.2控制器电平复位

7.3.3队列级别

7.4队列管理

7.4.1队列设置和初始化

7.4.2队列协调

7.4.3队列中止

7.5中断

7.5.1基于管脚、单个MSI和多个MSI行为

7.5.1.1主机软件中断处理

7.5.1.1.1中断示例(资料性)

7.5.1.2基于引脚和MSI中断之间的差异

7.5.2基于MSI-X的行为

7.6控制器初始化和关闭处理

7.6.1初始化

7.6.1.1软件进度标记

7.6.2停机

7.7异步事件请求主机软件建议(资料性)

7.8特征值

7.9 NVMe限定名称

7.10标识符格式和布局(资料性)

7.10.1 PCI供应商ID(VID)和PCI子系统供应商ID(SSVID)

7.10.2序列号(SN)和型号(MN)

7.10.3 IEEE OUI标识符(IEEE)

7.10.4 IEEE扩展唯一标识符(EUI64)

7.10.5命名空间全局唯一标识符(NGUID)

7.11唯一标识符

7.12保持活力

7.12.1通过PCIe的NVMe

7.13使用影子门铃缓冲器更新控制器门铃寄存器

7.13.1影子门铃缓冲器概述

7.13.2控制器门铃寄存器更新示例算法(参考)

8特点

8.1固件更新过程

8.2元数据处理

8.3端到端数据保护(可选)

8.3.1实际钻头

8.3.1.1保护信息和写入命令

8.3.1.2实际位和读指令

8.3.1.3熔合操作的保护信息

8.3.1.4使用比较命令进行保护检查

8.3.1.5保护信息检查控制-PRCHK

8.4电源管理

8.4.1非运行功率状态

8.4.2自主电源状态转换

8.4.3 NVM子系统工作负载

8.4.4运行时D3转换

8.4.5主控热管理

8.5虚拟化增强(可选)

8.5.1 VQ资源定义

8.5.2 VI资源定义

8.5.3辅助控制器状态和资源配置

8.5.4单根I/O虚拟化和共享(SR-IOV)

8.6软件仿真的门铃步幅

8.7特定于供应商的标准命令格式

8.8预订(可选)

8.8.1预订通知

8.8.2登记

8.8.3预订类型

8.8.4注销

8.8.5获得预订

8.8.6解除预约

8.8.7抢先预订或登记

8.8.8清除预订

8.8.9报告预订状态

8.9主机内存缓冲区(可选)

8.10重放保护内存块(可选)

8.10.2 RPMB操作

8.10.2.1认证密钥编程

8.10.2.2读写计数器值

8.10.2.3验证数据写入

8.10.2.4认证数据读取

8.10.3认证设备配置块写入

8.10.4认证设备配置块读取

8.11设备自检操作(可选)

8.11.1短设备自检操作

8.11.2扩展设备自检操作

8.12命名空间管理(可选)

8.13引导分区(可选)

8.13.1从引导分区读取

8.13.2写入启动分区

8.13.3引导分区保护

8.14遥测(可选)

8.14.1遥测数据采集示例(资料性)

8.15消毒操作(可选)

9指令

9.1 I/O命令中的指令使用

9.2识别(指令类型00h)

9.2.1指令接收

9.2.1.1返回参数(指令操作01h)

9.2.2指令发送

9.2.2.1启用指令(指令操作01h)

9.3流(指令类型01h,可选)

9.3.1指令接收

9.3.1.1返回参数(指令操作01h)

9.3.1.2获取状态(指令操作02h)

9.3.1.3资源分配(指令操作03h)

9.3.2指令发送

9.3.2.1发布标识符(指令操作01h)

9.3.2.2发布资源(指令操作02h)

10错误报告和恢复

10.1命令和队列错误处理

10.2媒体和数据错误处理

10.3内存错误处理

10.4内部控制器错误处理

10.5控制器致命状态

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc