NAND Flash Memory - Fortis Flash

Features

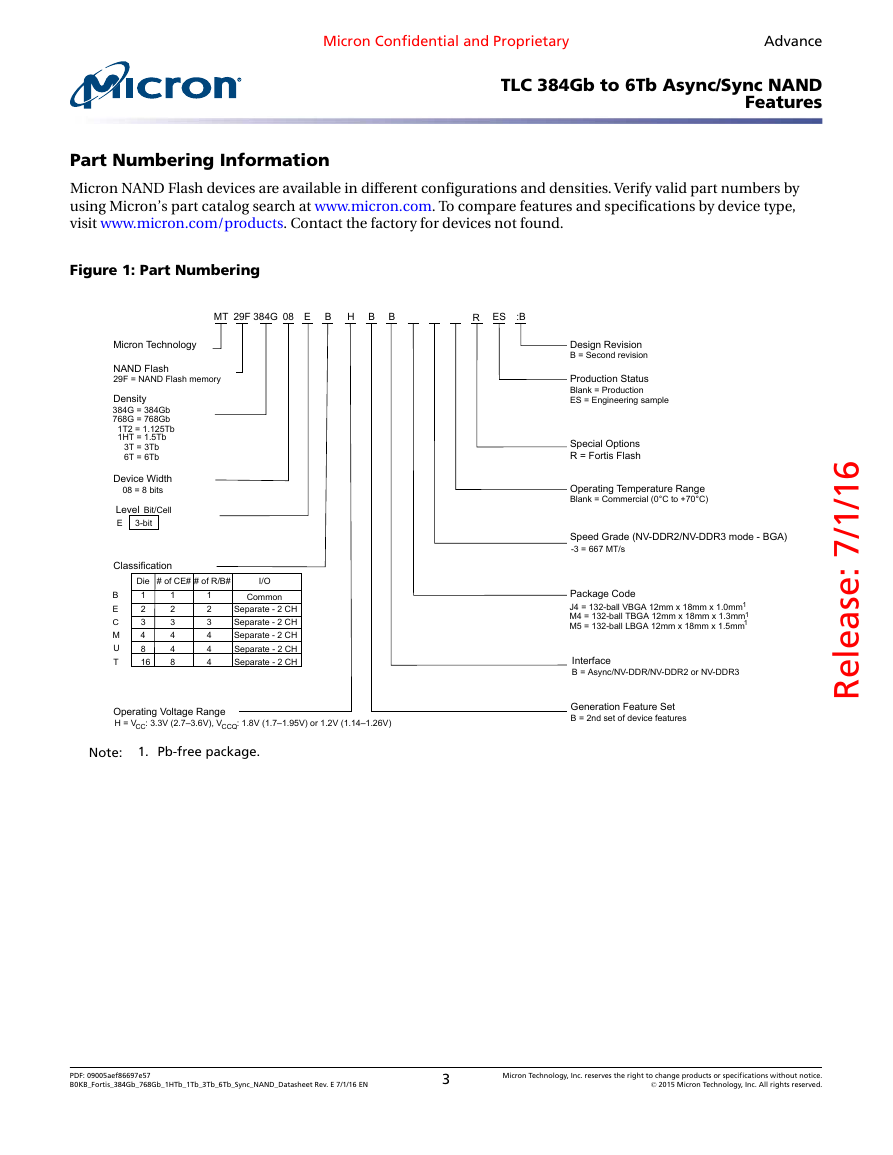

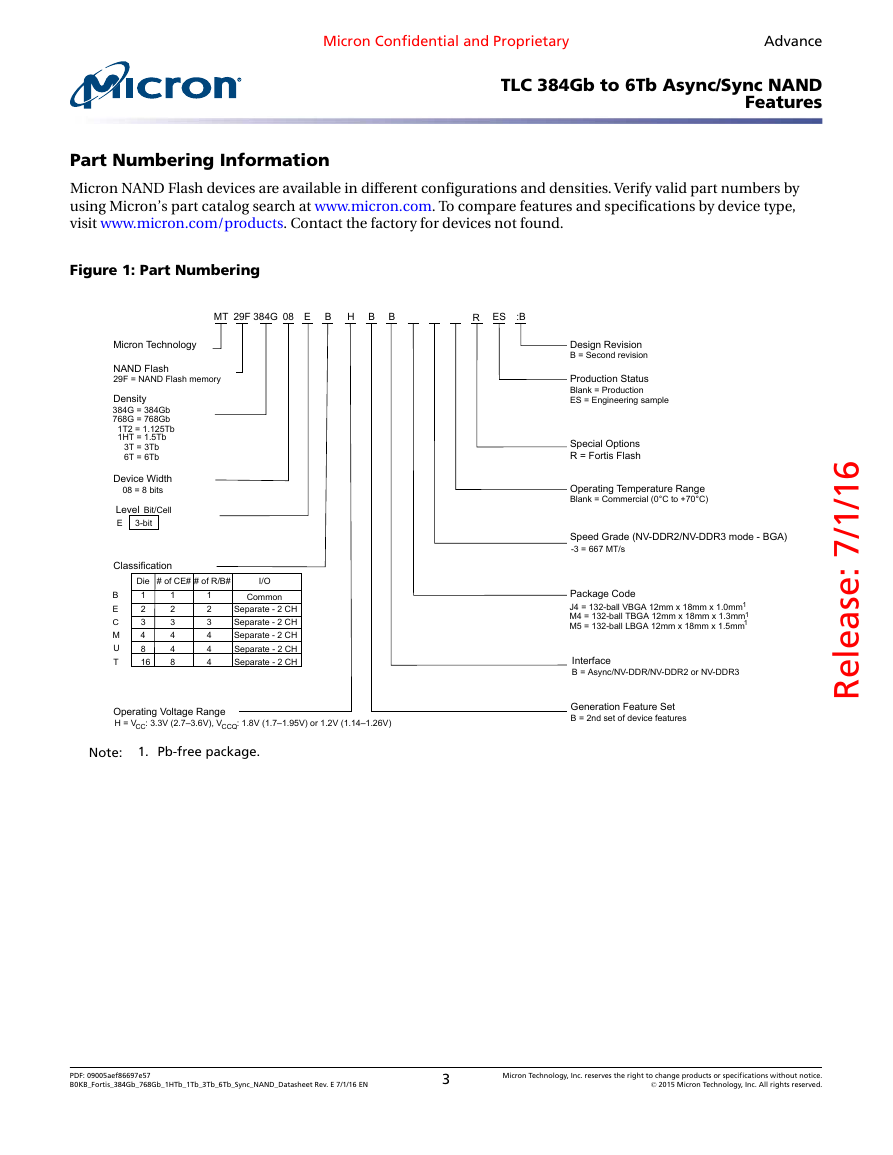

Part Numbering Information

General Description

Asynchronous, NV-DDR, NV-DDR2, NV-DDR3 Signal Descriptions

Signal Assignments

Package Dimensions

Architecture

Device and Array Organization

Bus Operation – Asynchronous Interface

Asynchronous Enable/Standby

Asynchronous Bus Idle

Asynchronous Pausing Data Input/Output

Asynchronous Commands

Asynchronous Addresses

Asynchronous Data Input

Asynchronous Data Output

Write Protect

Ready/Busy#

Bus Operation – NV-DDR Interface

NV-DDR Enable/Standby

NV-DDR Bus Idle/Driving

NV-DDR Pausing Data Input/Output

NV-DDR Commands

NV-DDR Addresses

NV-DDR DDR Data Input

NV-DDR Data Output

Write Protect

Ready/Busy#

Bus Operation – NV-DDR2 Interface

Differential Signaling

Warmup Cycles

On-die Termination (ODT)

Self-termination On-die Termination (ODT)

Matrix Termination

Matrix Termination Examples

NV-DDR2 Standby

NV-DDR2 Idle

NV-DDR2 Pausing Data Input/Output

NV-DDR2 Commands

NV-DDR2 Addresses

NV-DDR2 Data Input

NV-DDR2 Data Output

Write Protect

Ready/Busy#

Bus Operation – NV-DDR3 Interface

On-die Termination (ODT)

Device Initialization

VPP Initialization

Electronic Mirroring

Activating Interfaces

Activating the Asynchronous Interface

Activating the NV-DDR Interface

Activating the NV-DDR2 Interface

Activating the NV-DDR3 Interface

CE# Pin Reduction and Volume Addressing

Initialization Sequence

Volume Appointment Without CE# Pin Reduction

Appointing Volume Addresses

Selecting a Volume

Multiple Volume Operation Restrictions

Volume Reversion

Command Definitions

Reset Operations

RESET (FFh)

SYNCHRONOUS RESET (FCh)

RESET LUN (FAh)

HARD RESET (FDh)

Identification Operations

READ ID (90h)

READ ID Parameter Tables

READ PARAMETER PAGE (ECh)

Parameter Page Data Structure Tables

READ UNIQUE ID (EDh)

Configuration Operations

SET FEATURES (EFh)

GET FEATURES (EEh)

GET/SET FEATURES by LUN (D4h/D5h)

VOLUME SELECT (E1h)

ODT CONFIGURE (E2h)

ZQ Calibration

ZQ Calibration Long (F9h)

ZQ Calibration Short (D9h)

ZQ external resistor value, tolerance, and capacitive loading

Status Operations

READ STATUS (70h)

READ STATUS ENHANCED (78h)

FIXED ADDRESS READ STATUS ENHANCED (71h)

Column Address Operations

CHANGE READ COLUMN (05h-E0h)

CHANGE READ COLUMN ENHANCED (06h-E0h)

CHANGE READ COLUMN ENHANCED (00h-05h-E0h) Operation

CHANGE WRITE COLUMN (85h)

CHANGE ROW ADDRESS (85h)

Read Operations

READ MODE (00h)

READ PAGE (00h-30h)

READ PAGE CACHE SEQUENTIAL (31h)

READ PAGE CACHE RANDOM (00h-31h)

READ PAGE CACHE LAST (3Fh)

READ PAGE MULTI-PLANE (00h-32h)

Read Retry Operations

Auto Read Calibration

Two Pass Programming

PROGRAM PAGE (80h-10h)

PROGRAM PAGE CACHE (80h-15h)

PROGRAM PAGE MULTI-PLANE (80h-11h)

PROGRAM SUSPEND (84h) and PROGRAM RESUME (13h)

Program Continuation

SLC Operations

Erase Operations

ERASE BLOCK (60h-D0h)

ERASE BLOCK MULTI-PLANE (60h-D1h)

ERASE BLOCK MULTI-PLANE (60h-60h-D0h)

ERASE SUSPEND (61h) and ERASE RESUME (D2h)

Copyback Operations

COPYBACK READ (00h-35h)

COPYBACK PROGRAM (85h–10h)

COPYBACK READ MULTI-PLANE (00h-32h)

COPYBACK PROGRAM MULTI-PLANE (85h-11h)

One-Time Programmable (OTP) Operations

PROGRAM OTP PAGE (80h-10h)

PROTECT OTP AREA (80h-10h)

READ OTP PAGE (00h-30h)

Multi-Plane Operations

Multi-Plane Addressing

Interleaved Die (Multi-LUN) Operations

Error Management

Shared Pages - TLC

Output Drive Impedance

AC Overshoot/Undershoot Specifications

Input Slew Rate

Output Slew Rate

Power Cycle and Ramp Requirements

Electrical Specifications

Package Electrical Specification and Pad Capacitance

Electrical Specifications – DC Characteristics and Operating Conditions (Asynchronous)

Electrical Specifications – DC Characteristics and Operating Conditions (NV-DDR, NV-DDR2, NV-DDR3)

Electrical Specifications – DC Characteristics and Operating Conditions (VCCQ)

Single-Ended Requirements for Differential signals

Testing Conditions

Electrical Specifications – AC Characteristics and Operating Conditions (Asynchronous)

Electrical Specifications – AC Characteristics and Operating Conditions (NV-DDR, NV-DDR2, NV-DDR3)

Electrical Specifications – Array Characteristics

Asynchronous Interface Timing Diagrams

NV-DDR Interface Timing Diagrams

NV-DDR2 and NV-DDR3 Interface Timing Diagrams

Revision History

Rev. E – 7/1/16

Rev. D – 06/04/16

Rev. C – 5/13/16

Rev. B – 11/25/15

Rev. A – 08/05/15

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc