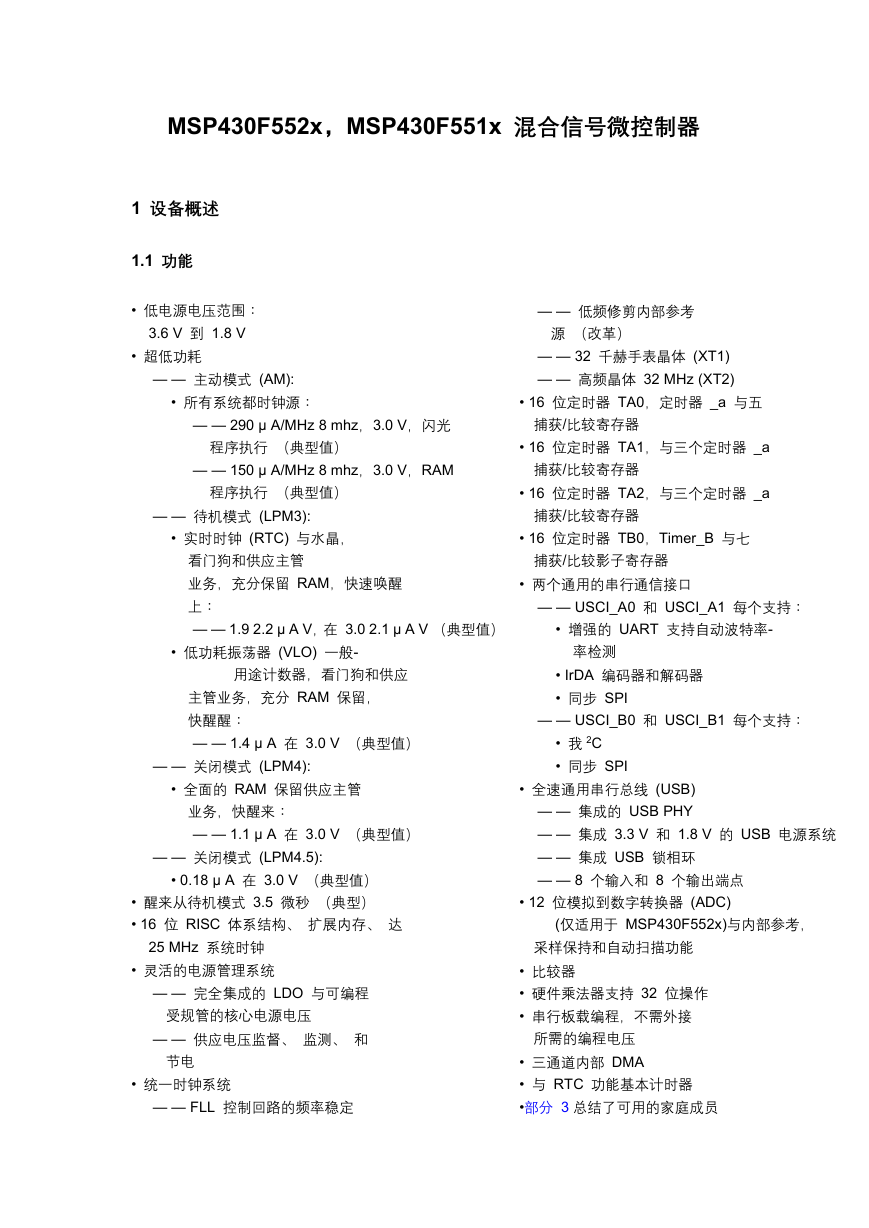

5.4 主动模式供应电流流进一个排除外部电流的 VCC

5.5 低功耗模式供应电流 (入 VCC) 排除外部电流

5.6 热特性

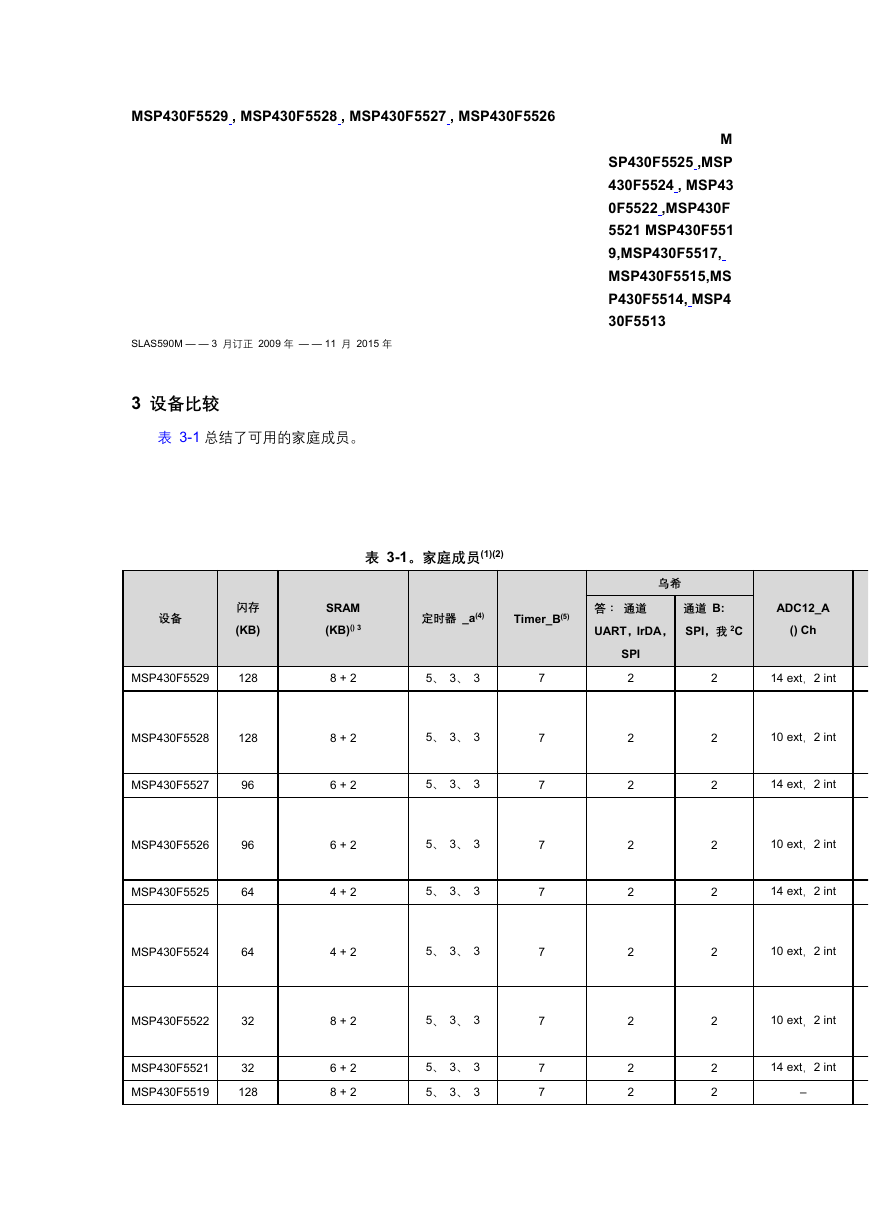

(P1.0 至 P1.7,P2.0 P2.7,P3.0 P3.7,P4.0 到 P4.7 到)(P

5.8 投入 — — 端口 P1 和 P2(1)(P1.0 至 P1.7,P2.0 到 P2.7)

(P1.0 至 P1.7,P2.0 P2.7,P3.0 P3.7,P4.0 到 P4.7 到)(P

(P1.0 至 P1.7,P2.0 P2.7,P3.0 P3.7,P4.0 到 P4.7 到)(P5

(P1.0 至 P1.7,P2.0 P2.7,P3.0 P3.7,P4.0 到 P4.7 到)(P5

(P1.0 至 P1.7,P2.0 P2.7,P3.0 P3.7,P4.0 到 P4.7 到)(P5

5.15 晶体振荡器、 XT1,低频模式(1)

5.16 晶体振荡器 XT2

5.17 内部非常低功率的低频振荡器 (VLO)

5.18 内部参考,低频振荡器 (改革)

5.19 DCO 频率

图 5-10。典型的 DCO 频率

5.21 PMM,核心电压

5.22 PMM、 SVS 偏高

5.23 PMM、 支持向量机高边

5.24 PMM、 SVS 偏低

5.25 PMM、 支持向量机偏低

5.26 叫醒时间从低功耗模式和重置

5.27 定时器 _a

5.28 Timer_B

5.29 (UART 模式) 时钟频率

5.30 乌希 (UART 模式)

5.31 乌希 (SPI 主模式) 时钟频率

5.32 乌希 (SPI 主模式)

5.33 (SPI 奴隶模式)

5.35 电源和输入范围条件

5.36 12 位 ADC,定时参数

参考电压

5.38 12 位模数转换器,使用内部参考电压的线性参数

5.40 REF,外部引用

5.41 REF,内置参考

5.42 Comparator_B

5.43 端口 PU.0 和 PU.1

DP 和 DM 5.44 USB 输出端口

DP 和 DM 5.45 USB 输入的端口

5.46 USB 压水堆 (USB 电源系统)

5.47 USB 锁相环 (USB 锁相环路)

5.48 快闪记忆体

5.49 JTAG 和间谍双线接口

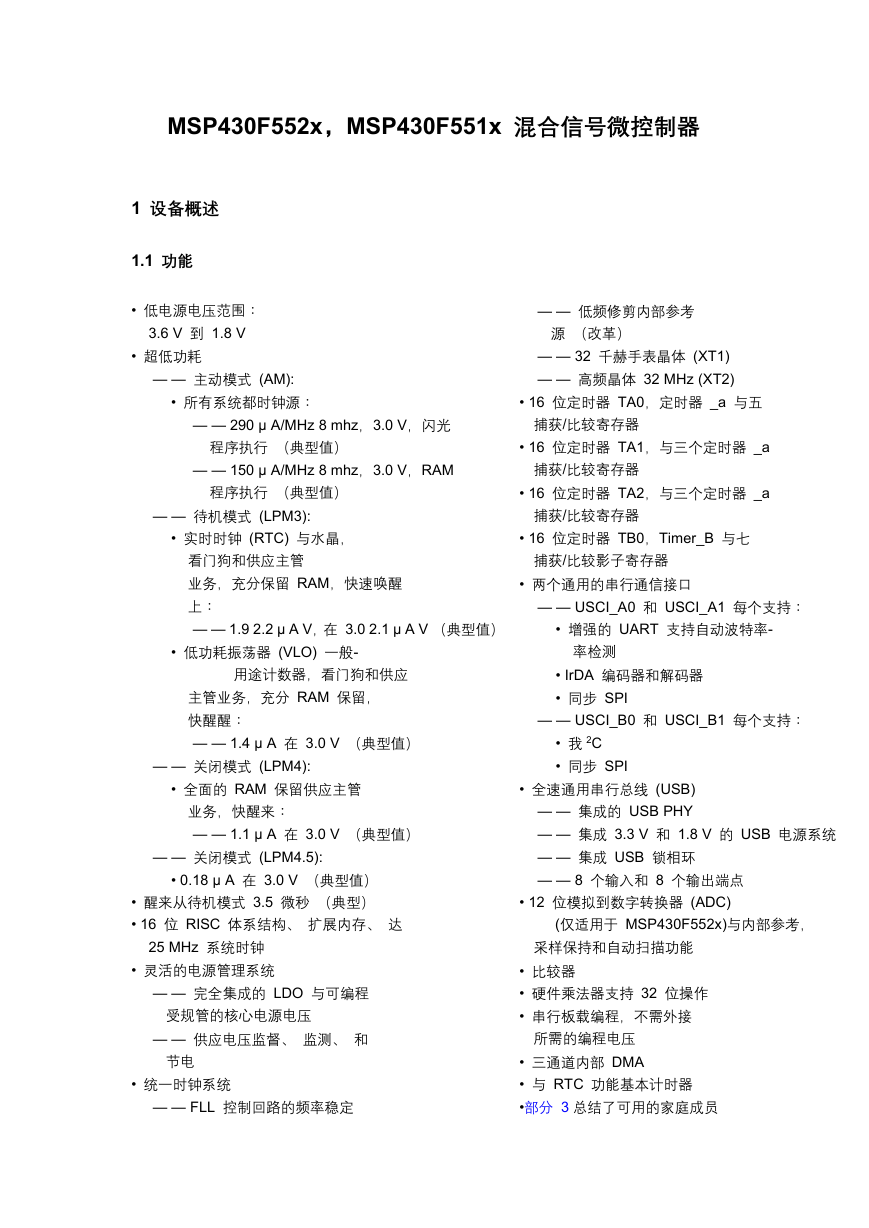

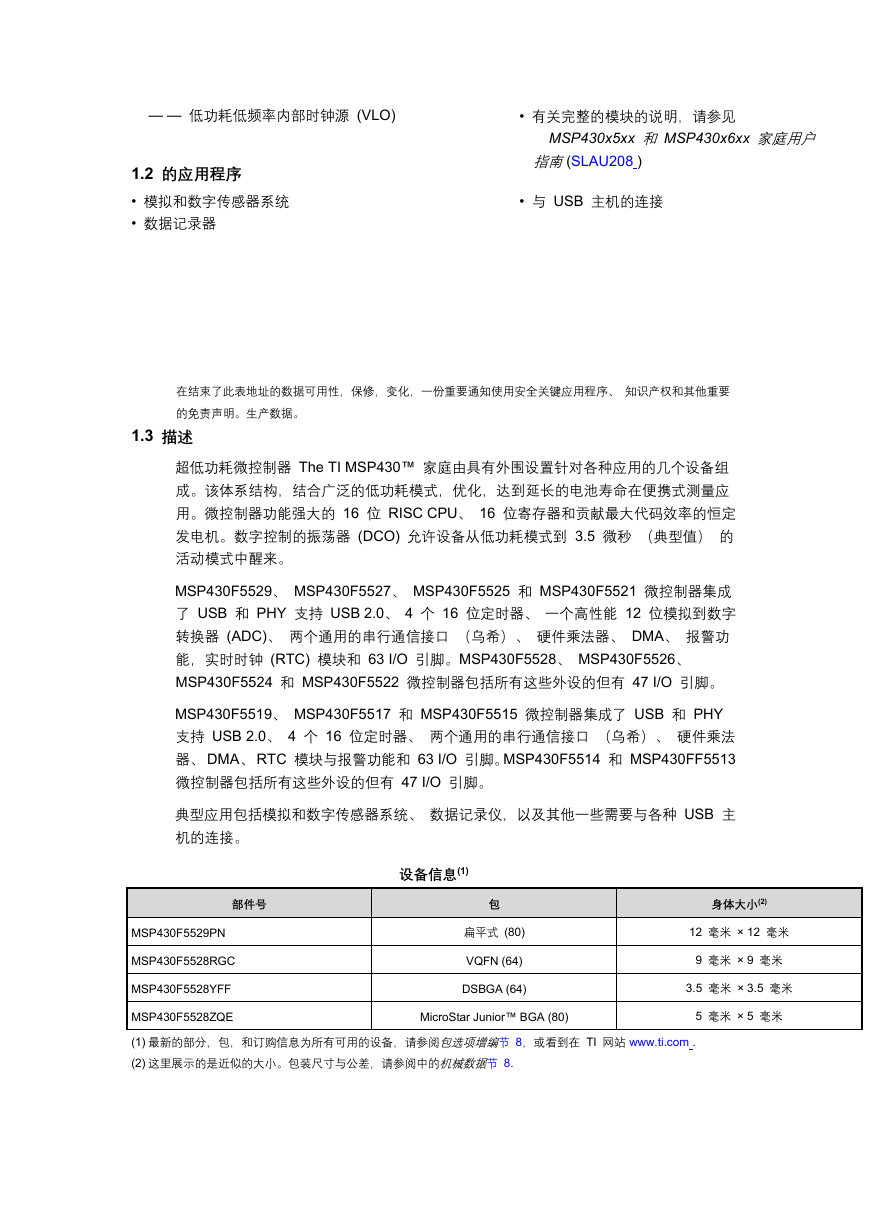

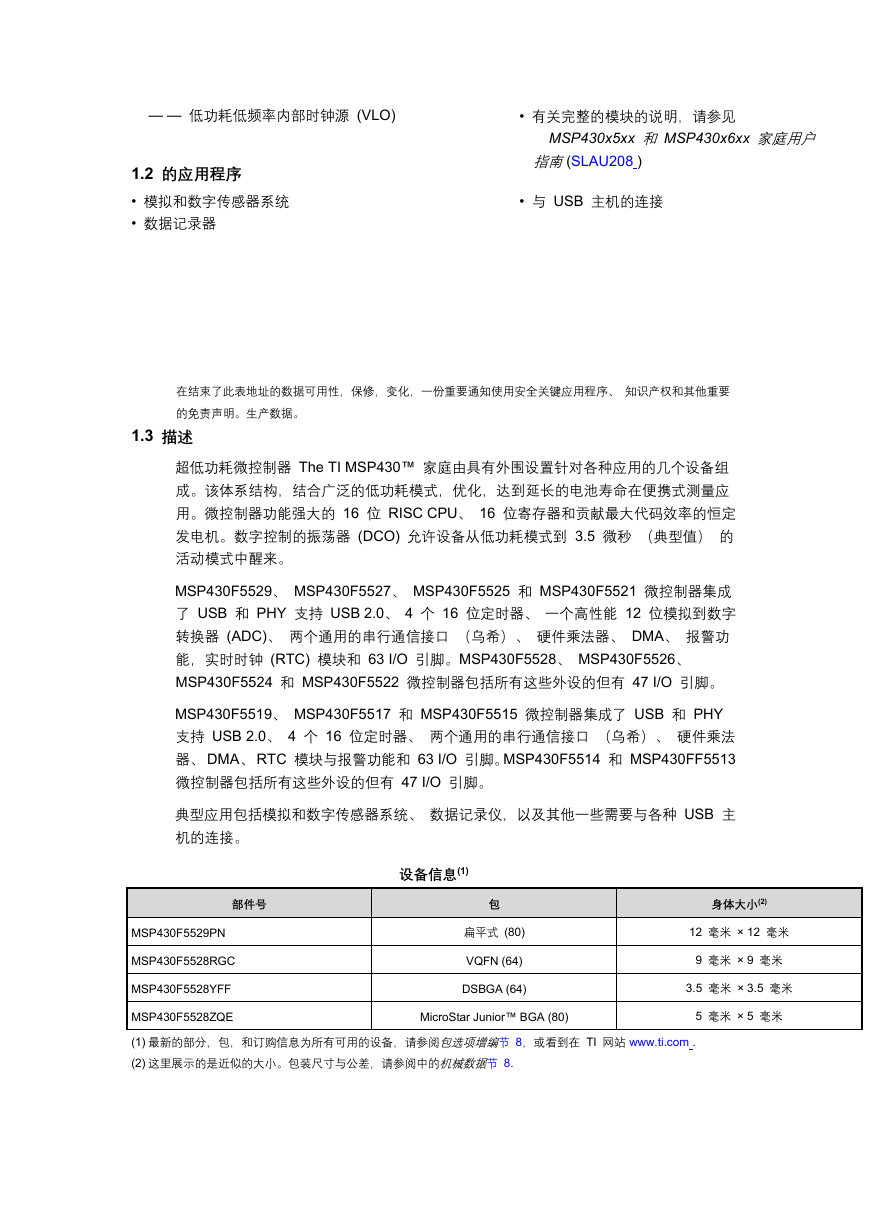

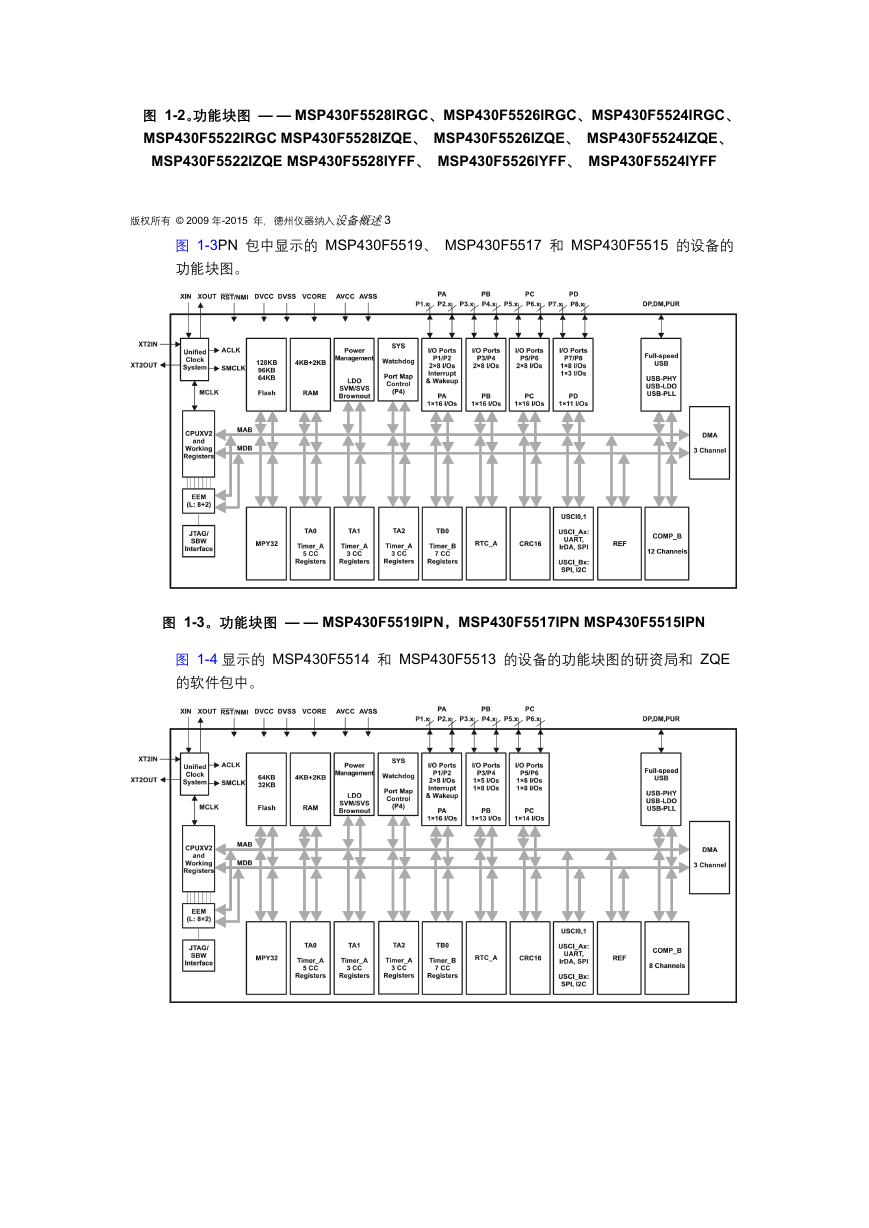

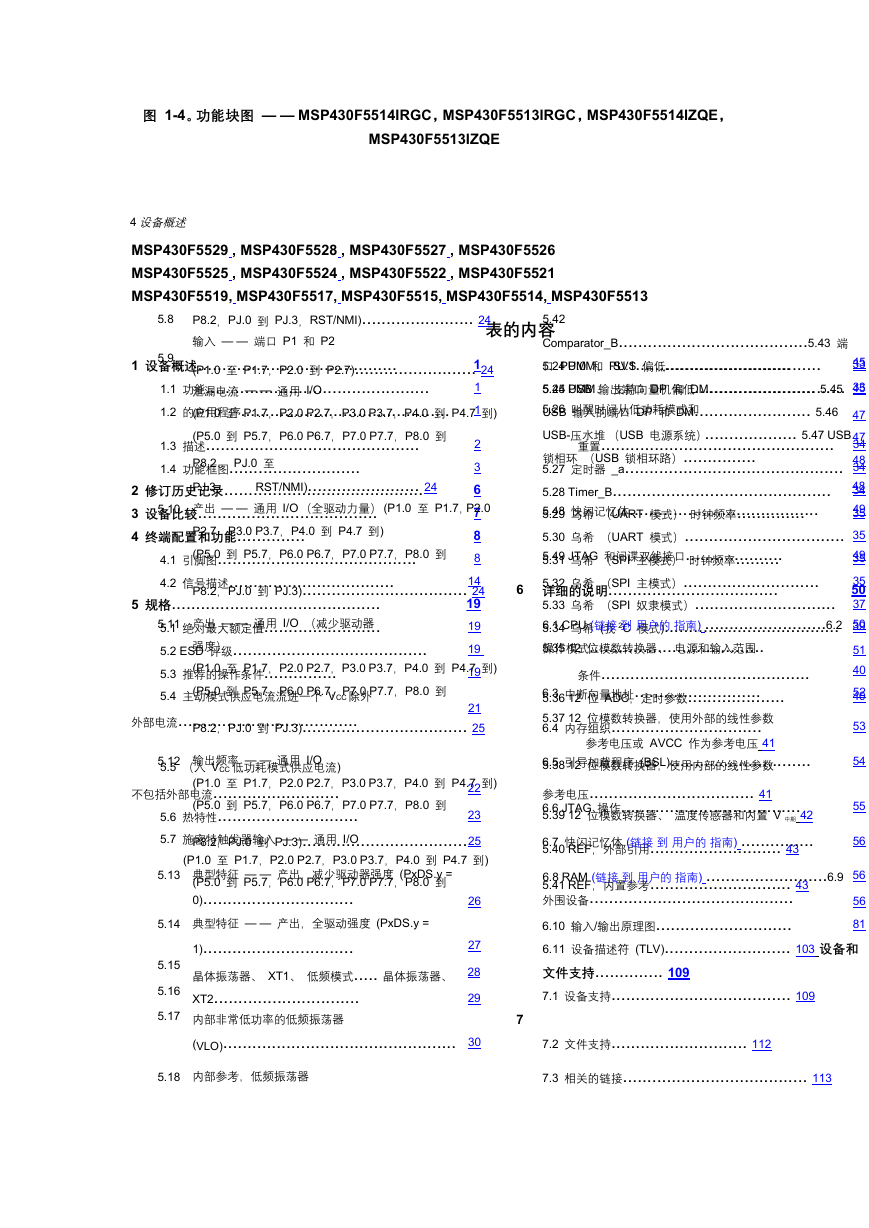

6 详细的描述

6.1 CPU

6.2 操作模式

6.3 中断向量地址

6.4 内存组织

6.5 引导加载程序 (BSL)

6.5.1 USB BSL

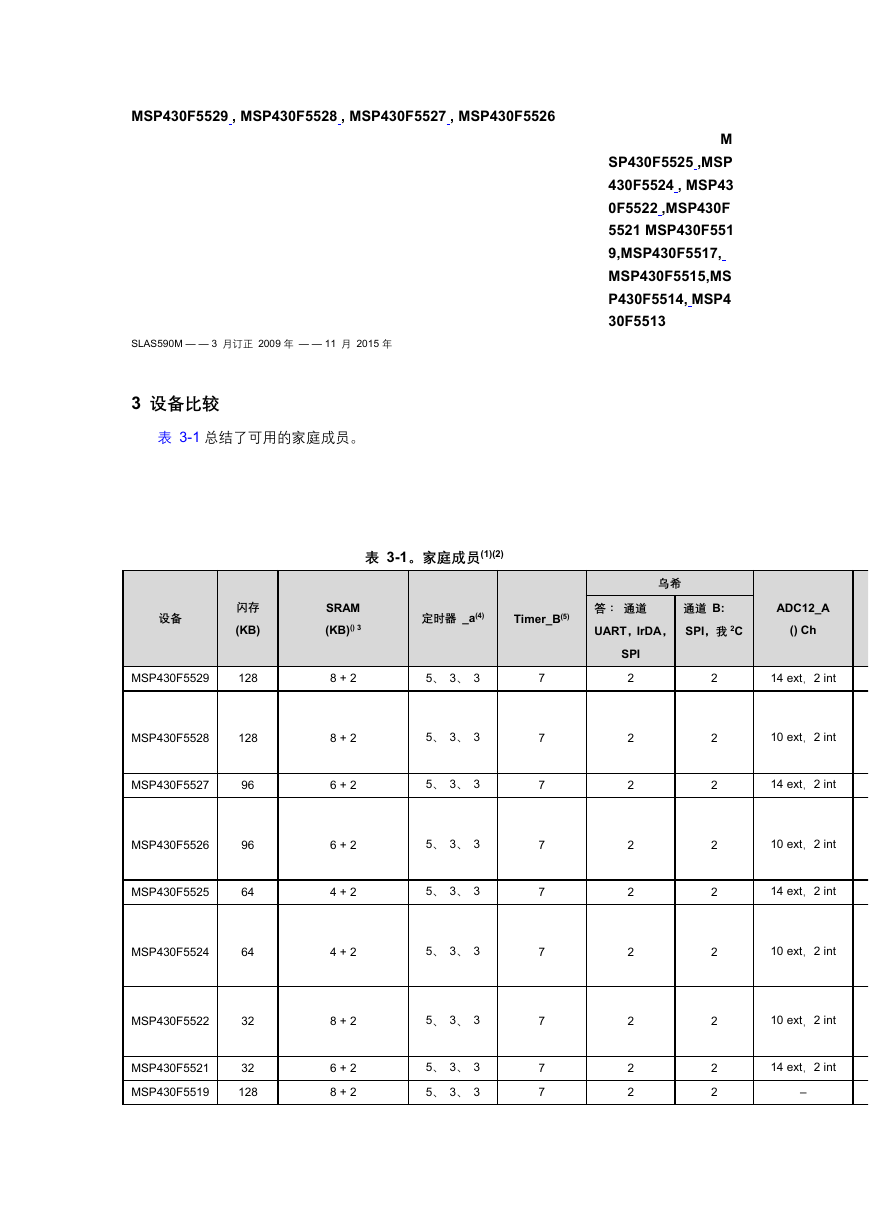

表 6-3。USB BSL Pin 要求和功能

注意

6.5.2 UART BSL

表 6-4。UART BSL Pin 要求和功能

6.6 JTAG 操作

6.6.1 JTAG 标准接口

表 6-5。JTAG Pin 要求和功能

6.6.2 间谍双线接口

表 6-6。间谍双线 Pin 要求和功能

6.7 闪速存储器

6.8 RAM

6.9 外设

6.9.1 数字 I/O

6.9.2 端口映射控制器

表 6-7。端口映射助记键和功能

表 6-8。默认映射

6.9.3 振荡器和系统时钟

6.9.4 电源管理模块 (PMM)

6.9.5 硬件乘法器

6.9.6 实时时钟 (RTC_A)

6.9.7 看门狗定时器 (WDT_A)

6.9.8 系统模块 (SYS)

表 6-9。系统模块中断向量寄存器

表 6-9。系统模块中断向量寄存器 (续)

6.9.9 DMA 控制器

表 6-10。DMA 触发任务(1)

表 6-10。DMA 触发任务(1) (续)

6.9.10 通用串行通讯接口 (乌希) (用户指南的链接︰

6.9.11 TA0

6.9.12 TA1

6.9.13 TA2

6.9.14 TB0

6.9.15 Comparator_B

6.9.16 ADC12_A

6.9.17 CRC16

6.9.18 REF 电压参考

6.9.19 通用串行总线 (USB)

6.9.20 嵌入式仿真模块 (EEM)

6.9.21 周边文件映射

表 6-15。外围设备

表 6-17。PMM 寄存器 (基址︰ 0120 h)

表 6-19。CRC16 寄存器 (基址︰ 0150 h)

表 6-22。UCS 寄存器 (基址︰ 0160 h)

表 6-23。SYS 寄存器 (基址︰ 0180 h)

表 6-25。端口映射寄存器

表 6-30。J 端口寄存器 (基址︰ 0320 h)

表 6-38。USCI_A0 寄存器 (基址︰ 05C0h)

6.10 输入/输出原理图

6.10.1 端口 P1,P1.0 至 P1.7,输入/输出与施密特触发器

6.10.2 P2、 到 P2.7 P2.0、 输入/输出与施密特触发器

表 6-47。P2 端口 (P2.0 到 P2.7) 引脚功能

6.10.3 P3、 P3.0 到 P3.7、 输入/输出与施密特触发器

表 6-48。P3 端口 (P3.0 到 P3.7) 引脚功能

6.10.4 P4、 P4.0 到 P4.7、 输入/输出与施密特触发器

表 6-49。端口 P4 (P4.0 到 P4.7) 引脚功能

6.10.5 P5.0 和 P5.1、 输入/输出与施密特触发器

表 6-50。端口 P5 (P5.0 和 P5.1) 引脚功能

6.10.6 P5.2、 输入/输出与施密特触发器

6.10.7 P5.3、 输入/输出与施密特触发器

表 6-51。端口 P5 (P5.2,P5.3) 引脚功能

表 6-52。端口 P5 (P5.4 和 P5.5) 引脚功能

6.10.8 端口 P5,到 P5.7 P5.6,输入/输出与施密特触发器

6.10.9 端口 P6、 P6.0 到 P6.7、 输入/输出与施密特触发器

表 6-54。端口 P6 (P6.0 到 P6.7) 引脚功能

6.10.10 P7、 P7.0 到 P7.3、 输入/输出与施密特触发器

表 6-55。端口 P7 (P7.0 到 P7.3) 引脚功能

6.10.11 P7、 P7.4 到 P7.7、 输入/输出与施密特触发器

6.10.12 P8,到 P8.2 P8.0,输入/输出与施密特触发器

6.10.13 PU.0/DP,PU.1/DM,PUR USB 端口

表 6-58。端口 PU.0/DP,PU.1/DM 输出功能(1)

表 6-59。端口 PU.0/DP,PU.1/DM 输入功能(1)

表 6-60。港口 PUR 输入的功能

6.10.14 J、 J.0 JTAG 引脚 TDO、 输入/输出与施密特触发器或输出

6.10.15 港 J、 J.1 到 J.3 JTAG 引脚 TMS,TCK,TDI/TCLK、 输

6.11 设备描述符 (TLV)

表 6-62。MSP430F552x 设备描述符表(1)

6 62。 MSP430F552x

7 设备和文件支持

7.1 设备支持

7.1.1 获取开始和下一步骤

7.1.2 开发工具支持

7.1.2.2.1 目标插座板

7.1.2.2.2 实验板

7.1.2.2.3 调试和编程工具

7.1.2.2.4 生产的程序员

7.1.2.3.1 集成开发环境

7.1.2.3.2 MSPWare

7.1.2.3.3 TI RTO

7.1.2.3.4 MSP430 USB 开发包

7.1.2.3.5 命令行程序员

7.1.3 设备和开发工具术语

7.2 文件支持

7.3 相关链接

表 7-1。相关的链接

7.4 社区资源

7.6 静电放电谨慎

8 机械、 包装和订购信息

包装信息

磁带和卷轴的信息

机械数据

重要通知

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc