®

www.digilentchina.com

25A, No.1369,Dongfang Road, Shanghai

Tel:+86-021-58893151 Fax: +86-021-58894598

Lab 1: 2 输入逻辑门的设计与实现

基于SPARTAN-6 XC6SLX16 开发板

Contains material © Digilent, Inc.

86 pages

�

Lab 1: 2 输入逻辑门的设计与实现

实验介绍

这个实验将指导你通过使用 ISE 软件进行简单的 2 输入逻辑门的设计与实现。

实验目标

使用 ISE 软件设计并仿真。

学会程序下载。

实验步骤

1. 编写文本文件并编译

2. 软件仿真

3. 进行硬件配置

实验原理

1.

ISE 软件是一个支持数字系统设计的开发平台

2. 用 ISE 软件进行设计开发时基于相应器件型号的。

注意:软件设计时选择 的器件型号是与实际下载板上的器件型号相同。

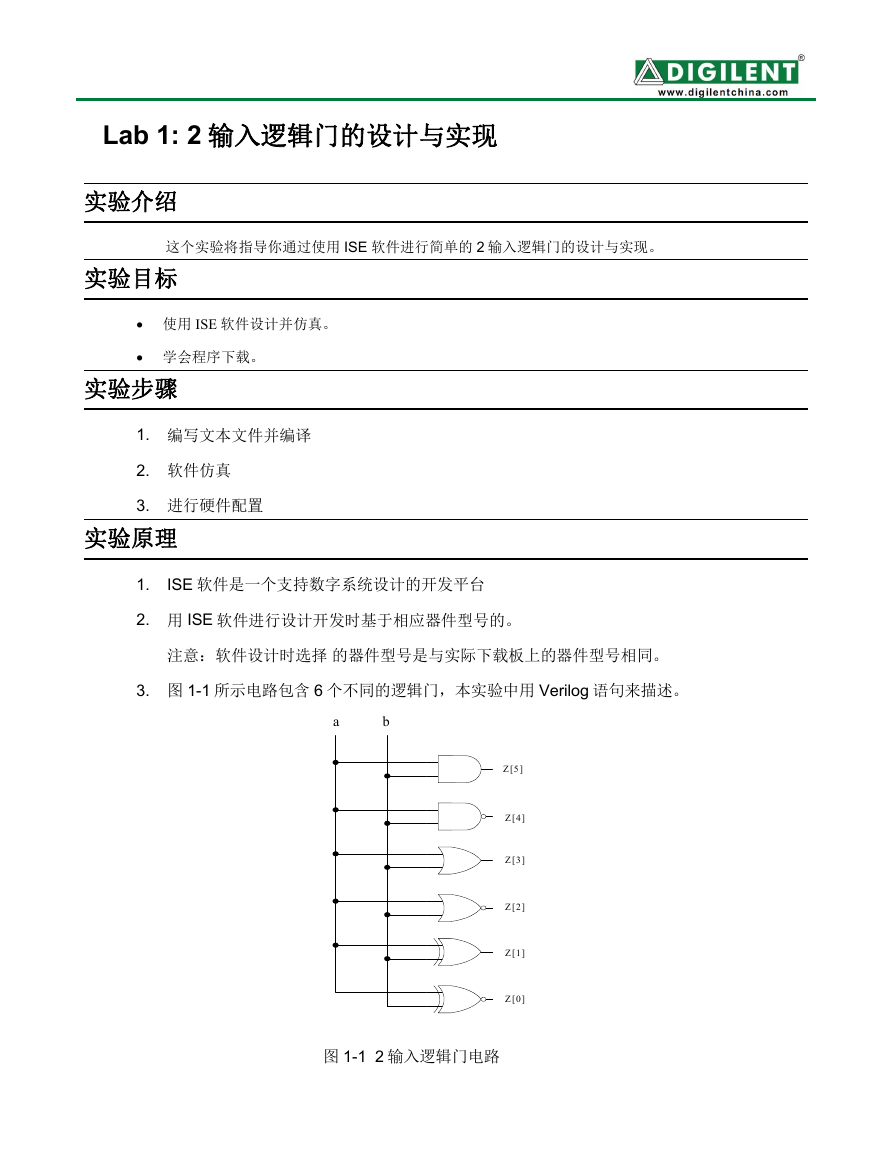

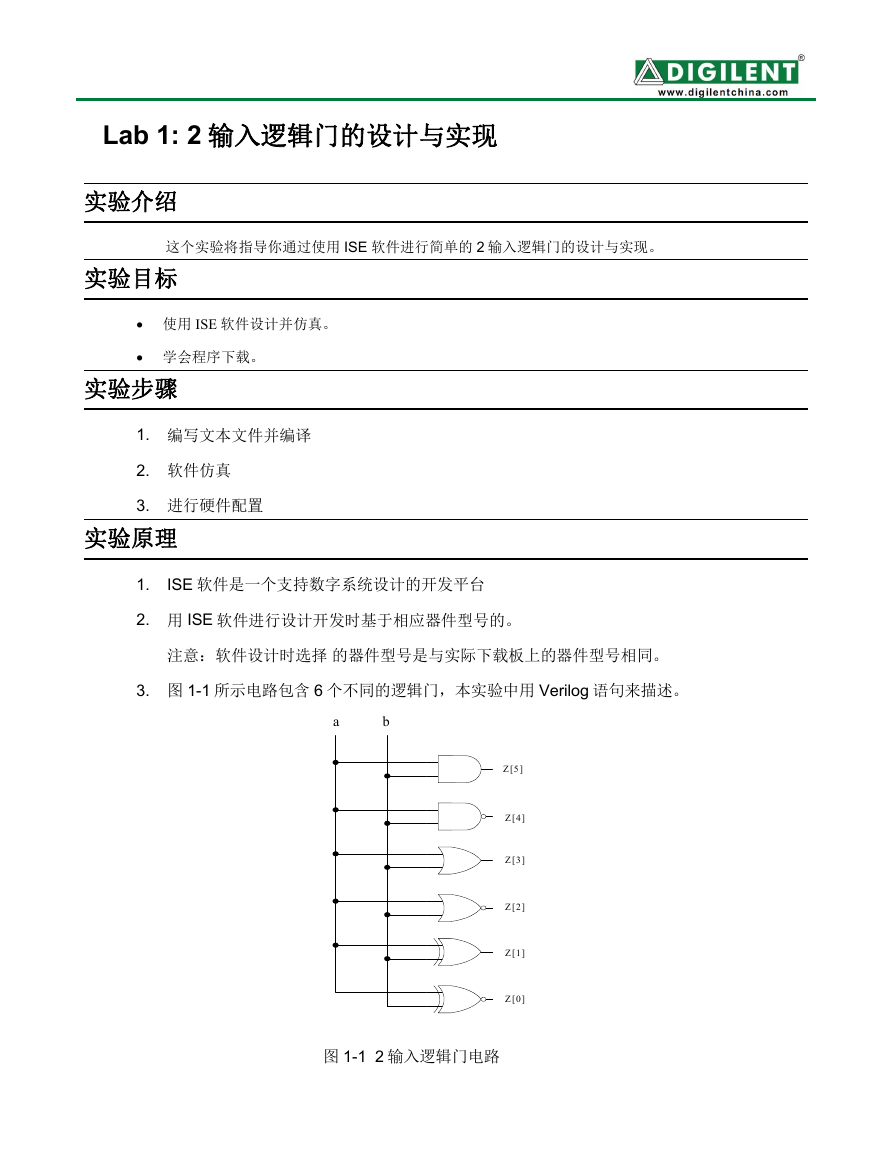

3. 图 1-1 所示电路包含 6 个不同的逻辑门,本实验中用 Verilog 语句来描述。

a

b

Z [5]

Z [4]

Z [3]

Z [2]

Z [1]

Z [0]

图 1-1 2 输入逻辑门电路

�

Step 1 新建工程

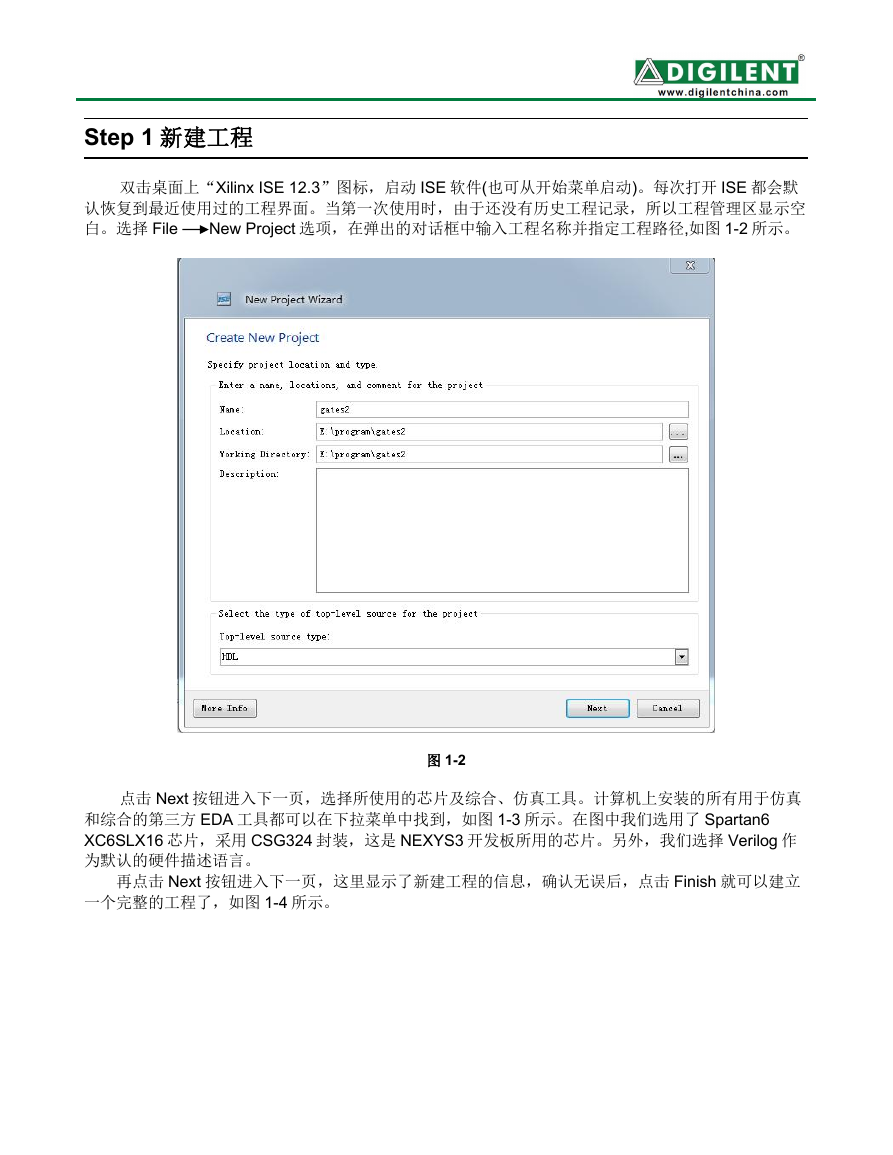

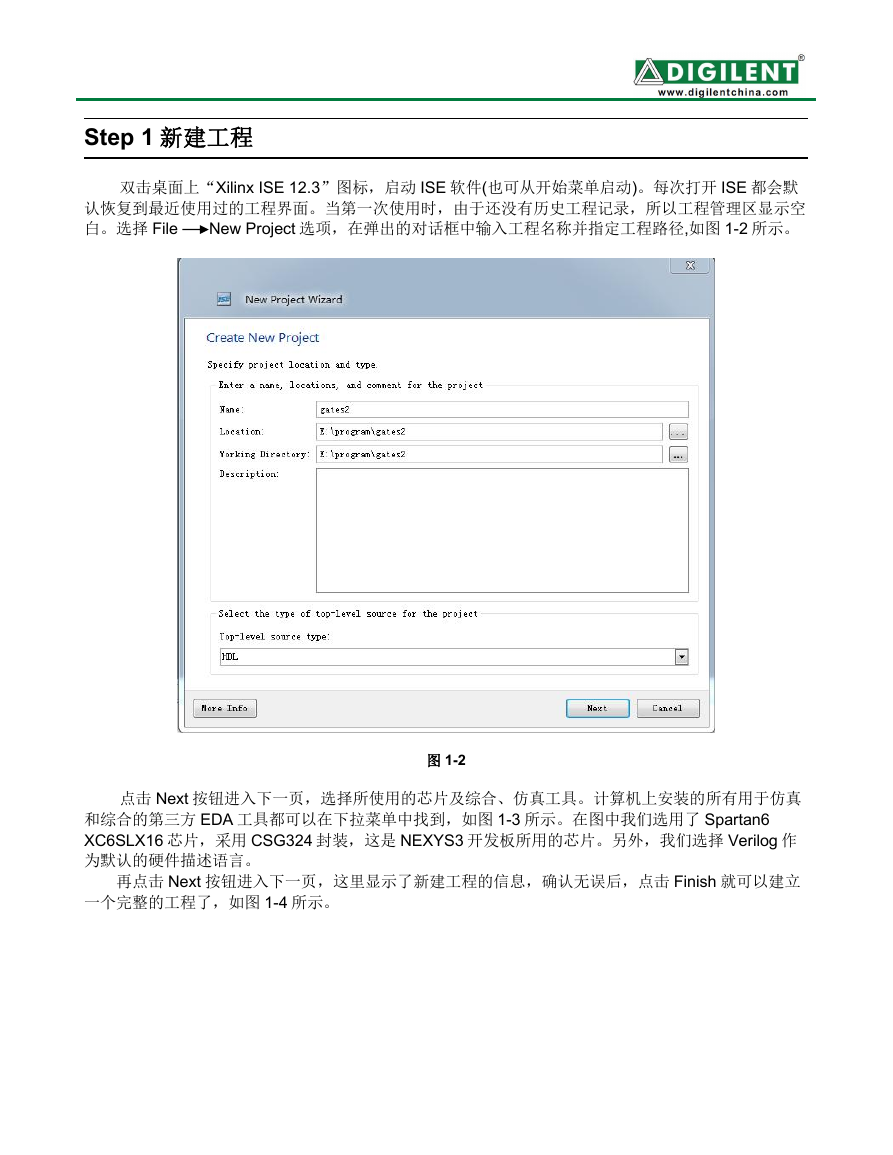

双击桌面上“Xilinx ISE 12.3”图标,启动 ISE 软件(也可从开始菜单启动)。每次打开 ISE 都会默

认恢复到最近使用过的工程界面。当第一次使用时,由于还没有历史工程记录,所以工程管理区显示空

白。选择 File

New Project 选项,在弹出的对话框中输入工程名称并指定工程路径,如图 1-2 所示。

图 1-2

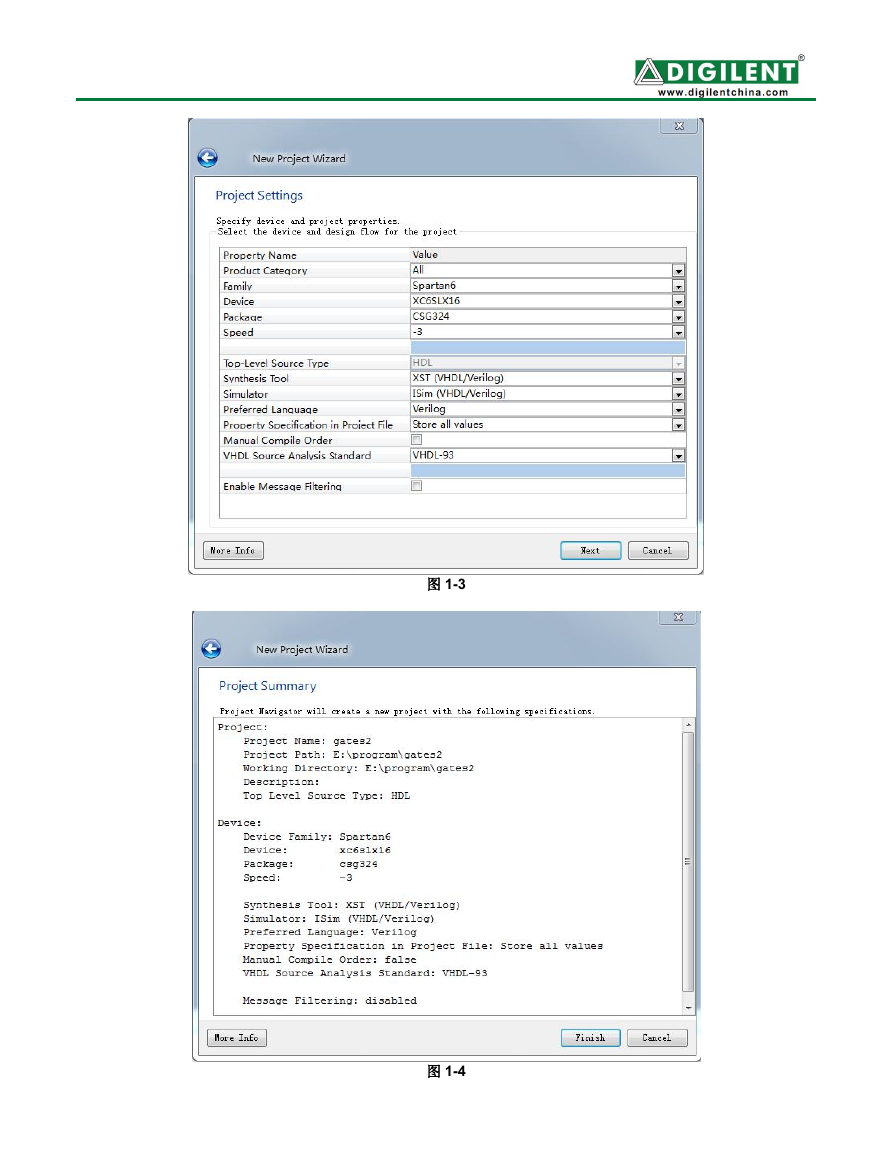

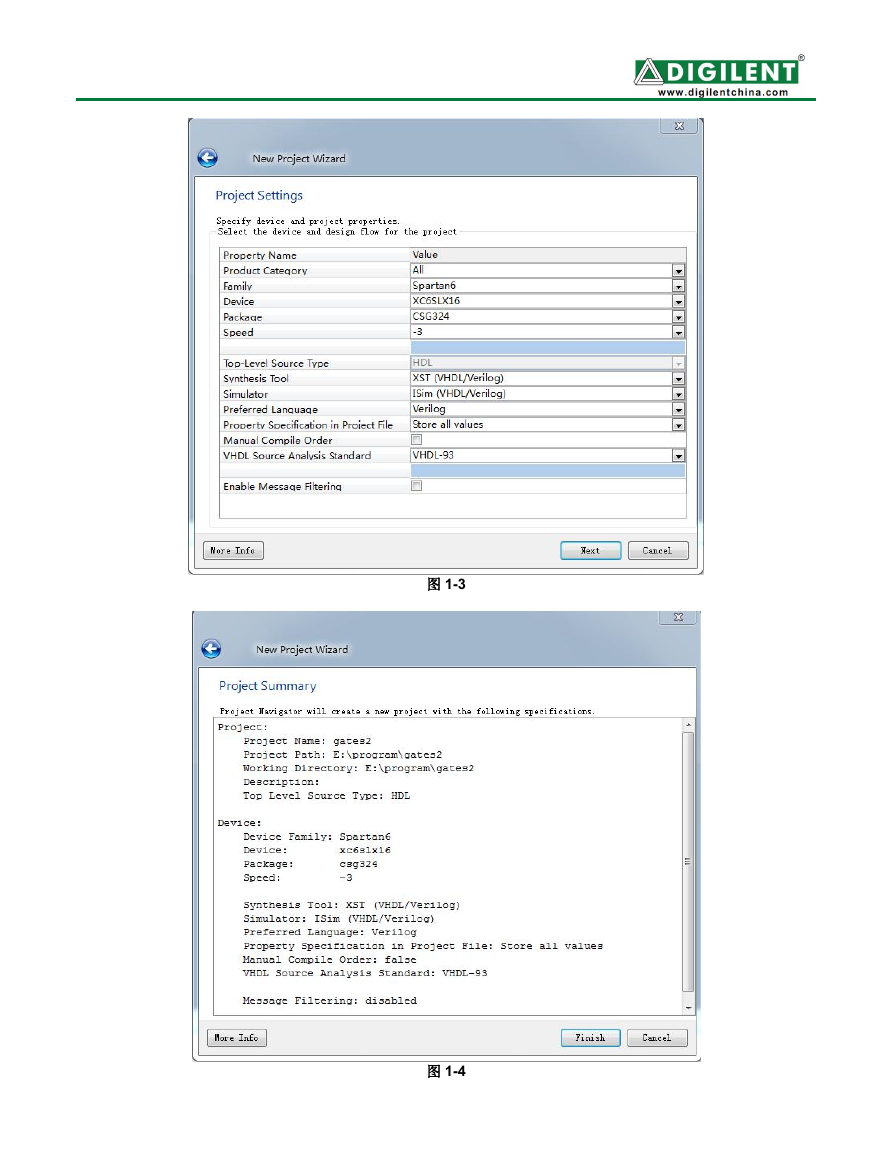

点击 Next 按钮进入下一页,选择所使用的芯片及综合、仿真工具。计算机上安装的所有用于仿真

和综合的第三方 EDA 工具都可以在下拉菜单中找到,如图 1-3 所示。在图中我们选用了 Spartan6

XC6SLX16 芯片,采用 CSG324 封装,这是 NEXYS3 开发板所用的芯片。另外,我们选择 Verilog 作

为默认的硬件描述语言。

再点击 Next 按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击 Finish 就可以建立

一个完整的工程了,如图 1-4 所示。

�

图 1-3

图 1-4

�

Step 2 设计输入和代码仿真

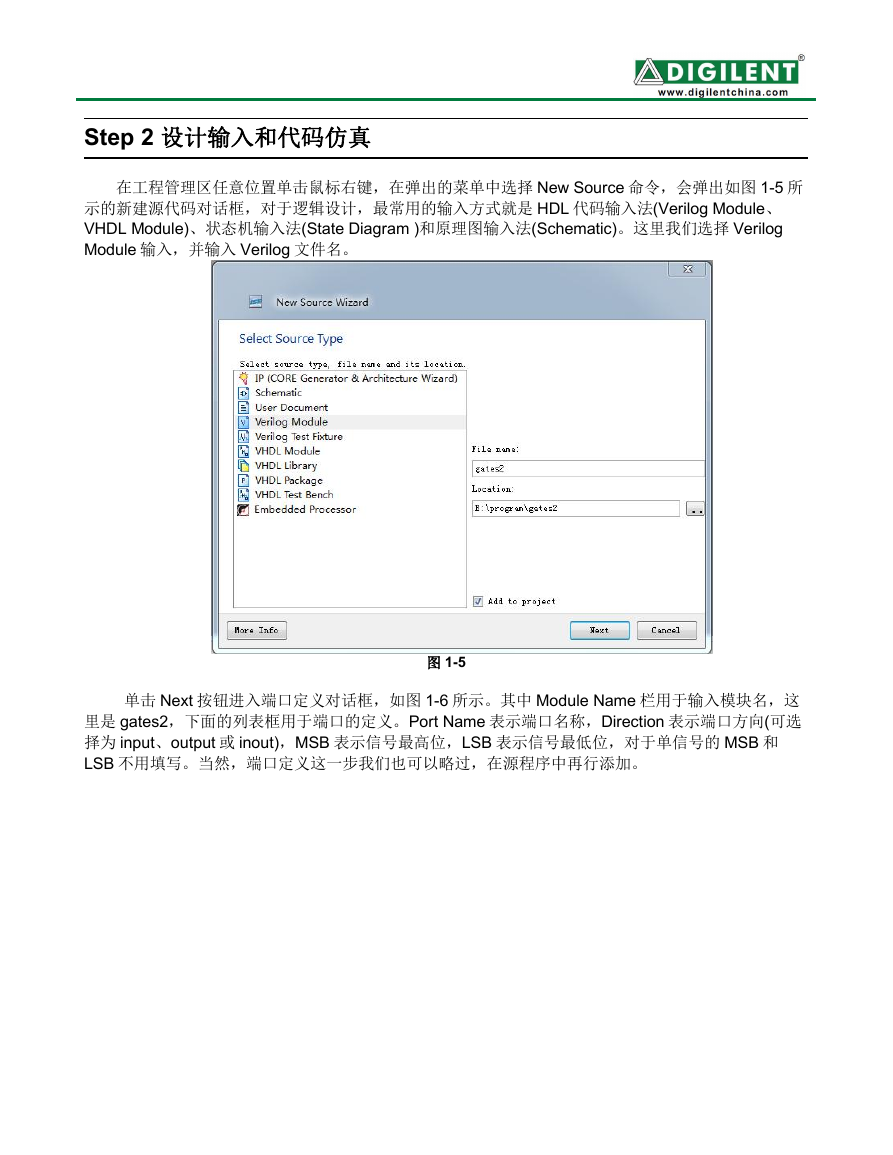

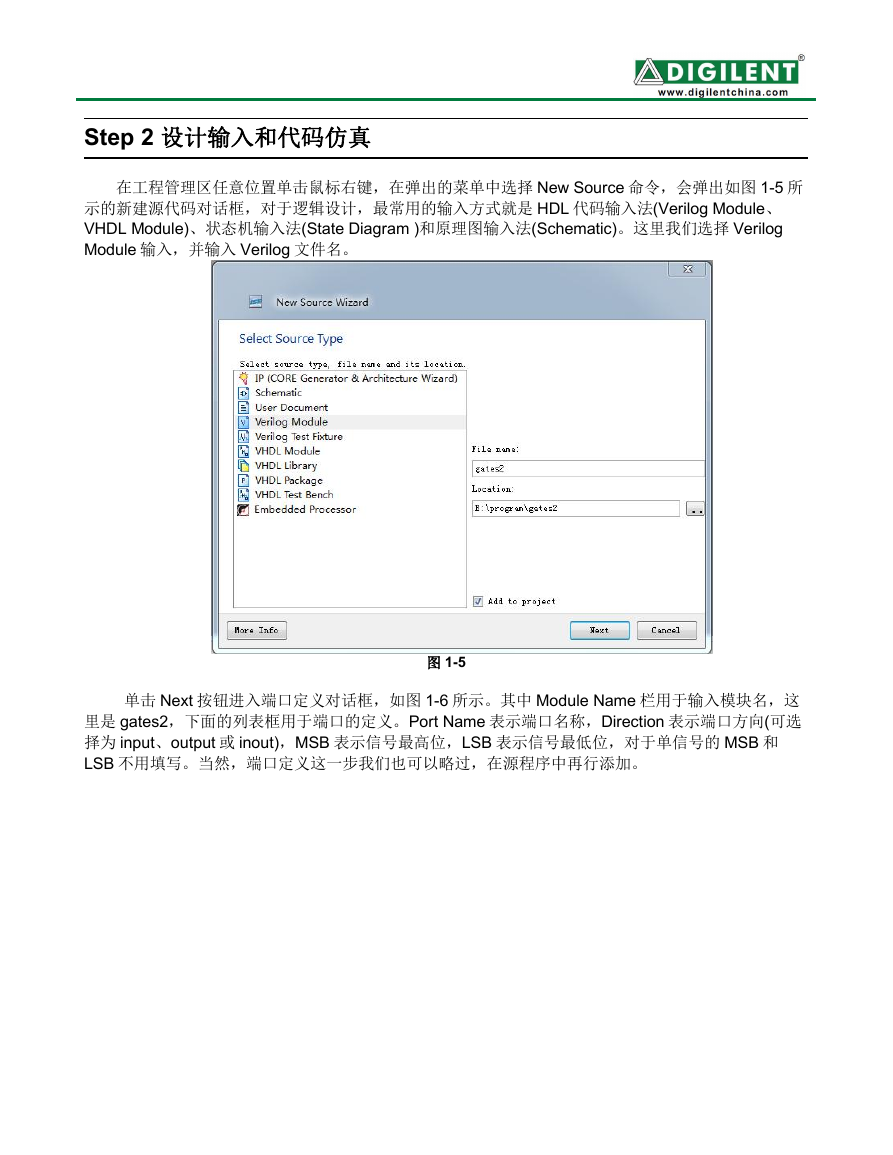

在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择 New Source 命令,会弹出如图 1-5 所

示的新建源代码对话框,对于逻辑设计,最常用的输入方式就是 HDL 代码输入法(Verilog Module、

VHDL Module)、状态机输入法(State Diagram )和原理图输入法(Schematic)。这里我们选择 Verilog

Module 输入,并输入 Verilog 文件名。

图 1-5

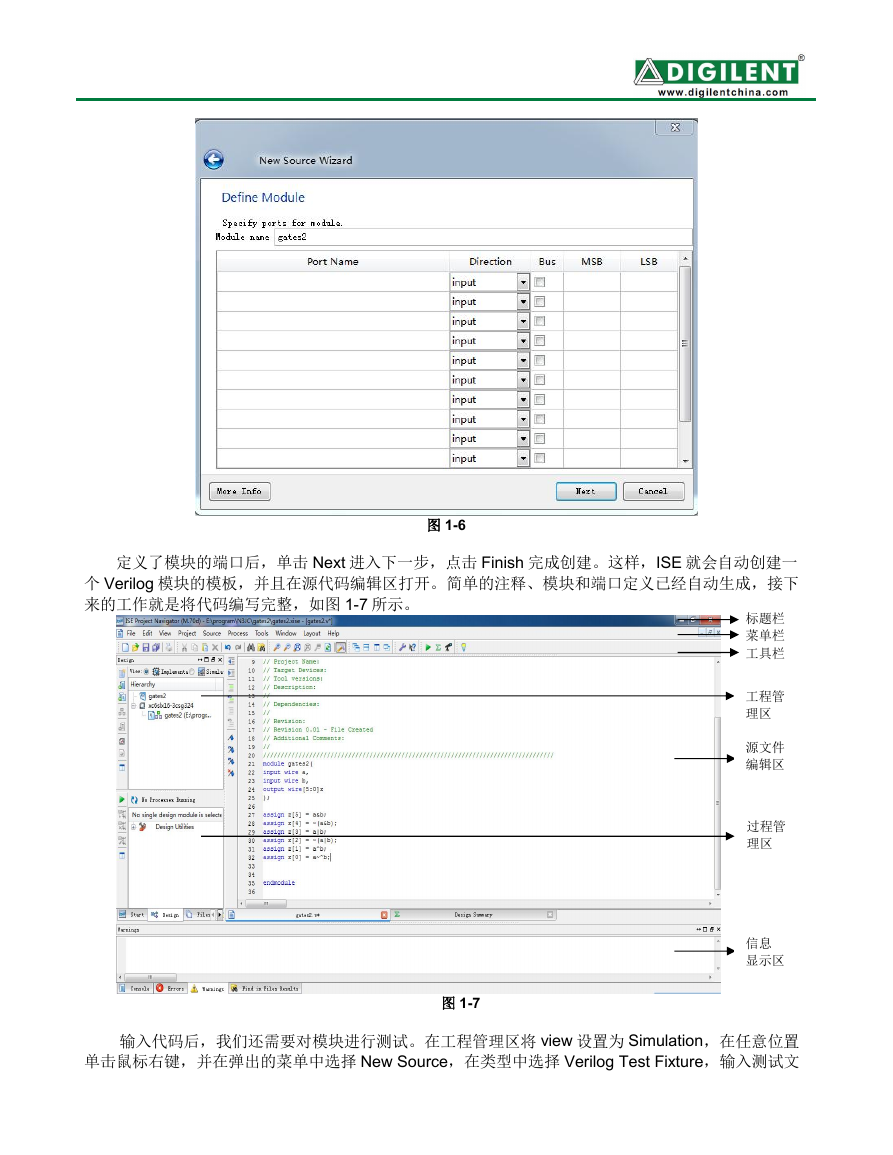

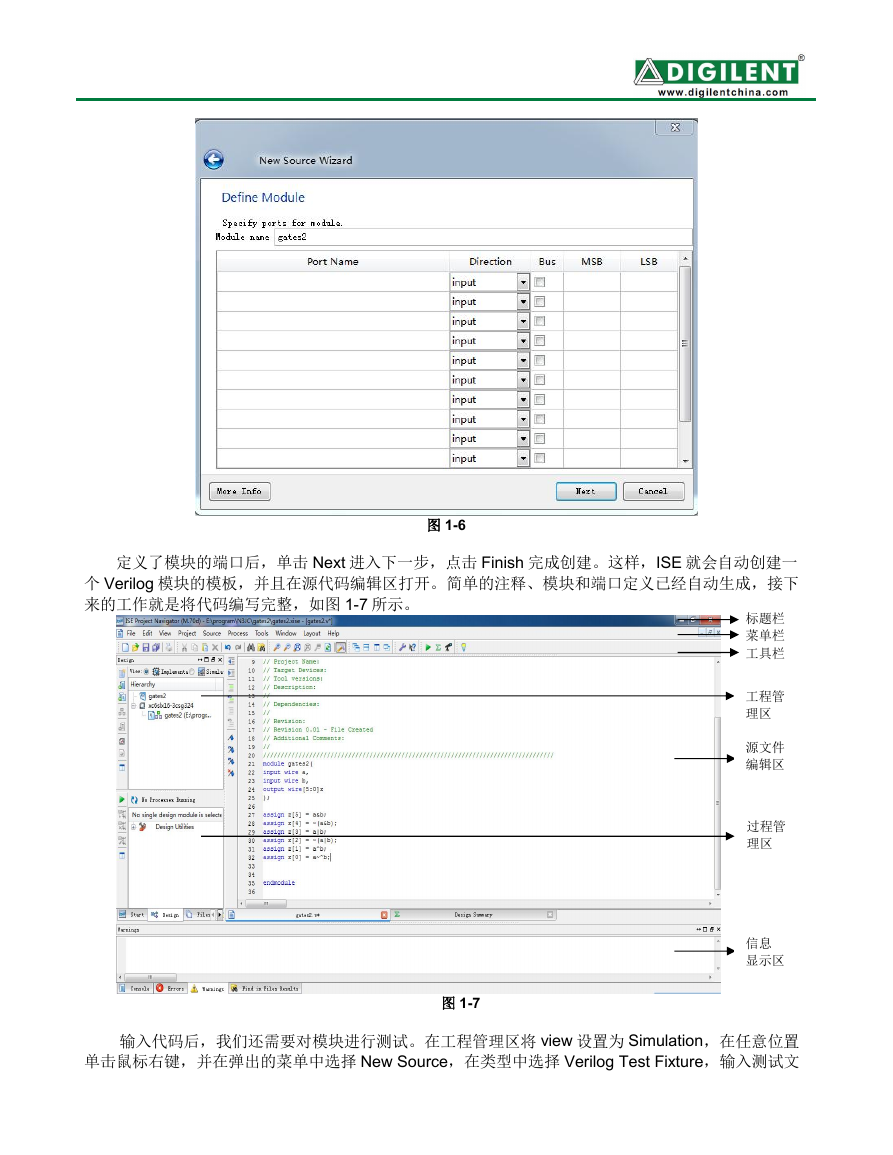

单击 Next 按钮进入端口定义对话框,如图 1-6 所示。其中 Module Name 栏用于输入模块名,这

里是 gates2,下面的列表框用于端口的定义。Port Name 表示端口名称,Direction 表示端口方向(可选

择为 input、output 或 inout),MSB 表示信号最高位,LSB 表示信号最低位,对于单信号的 MSB 和

LSB 不用填写。当然,端口定义这一步我们也可以略过,在源程序中再行添加。

�

图 1-6

定义了模块的端口后,单击 Next 进入下一步,点击 Finish 完成创建。这样,ISE 就会自动创建一

个 Verilog 模块的模板,并且在源代码编辑区打开。简单的注释、模块和端口定义已经自动生成,接下

来的工作就是将代码编写完整,如图 1-7 所示。

标题栏

菜单栏

工具栏

工程管

理区

源文件

编辑区

过程管

理区

信息

显示区

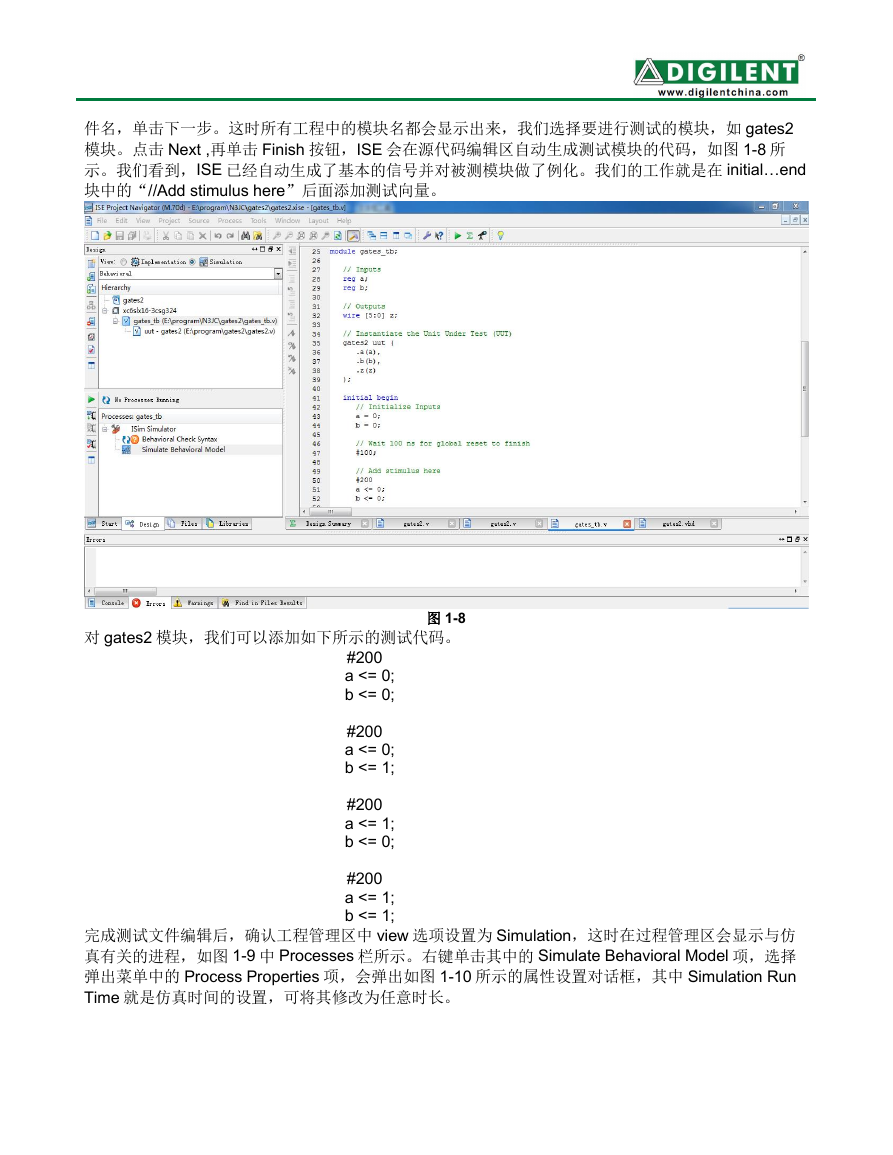

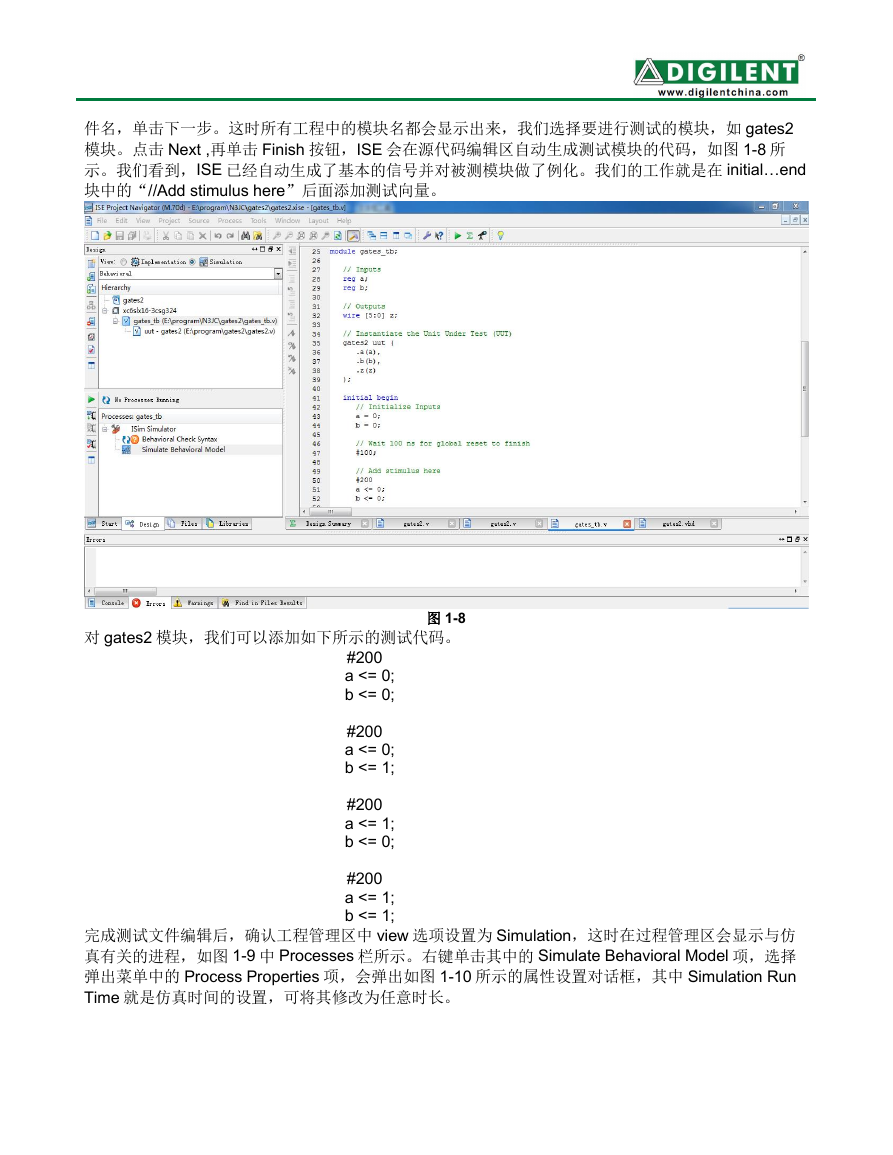

输入代码后,我们还需要对模块进行测试。在工程管理区将 view 设置为 Simulation,在任意位置

单击鼠标右键,并在弹出的菜单中选择 New Source,在类型中选择 Verilog Test Fixture,输入测试文

图 1-7

�

件名,单击下一步。这时所有工程中的模块名都会显示出来,我们选择要进行测试的模块,如 gates2

模块。点击 Next ,再单击 Finish 按钮,ISE 会在源代码编辑区自动生成测试模块的代码,如图 1-8 所

示。我们看到,ISE 已经自动生成了基本的信号并对被测模块做了例化。我们的工作就是在 initial…end

块中的“//Add stimulus here”后面添加测试向量。

图 1-8

对 gates2 模块,我们可以添加如下所示的测试代码。

#200

a <= 0;

b <= 0;

#200

a <= 0;

b <= 1;

#200

a <= 1;

b <= 0;

#200

a <= 1;

b <= 1;

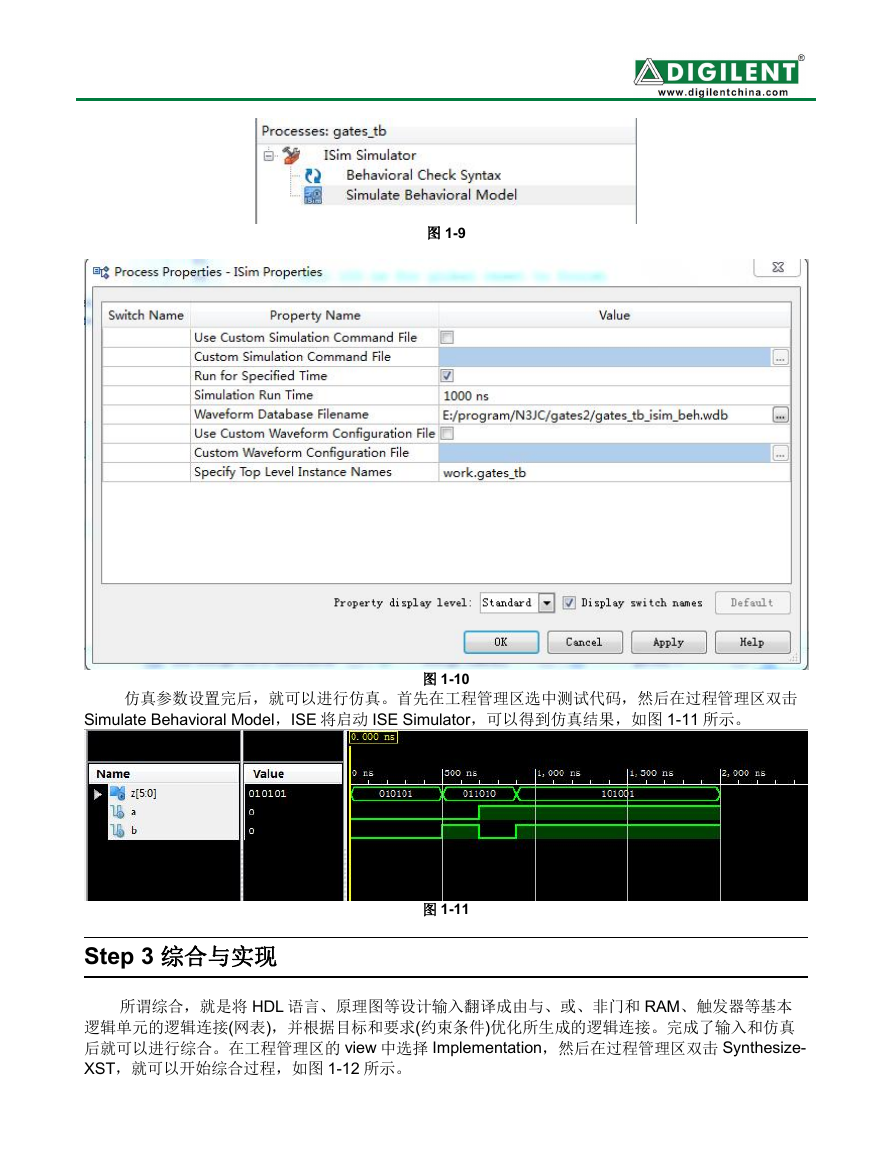

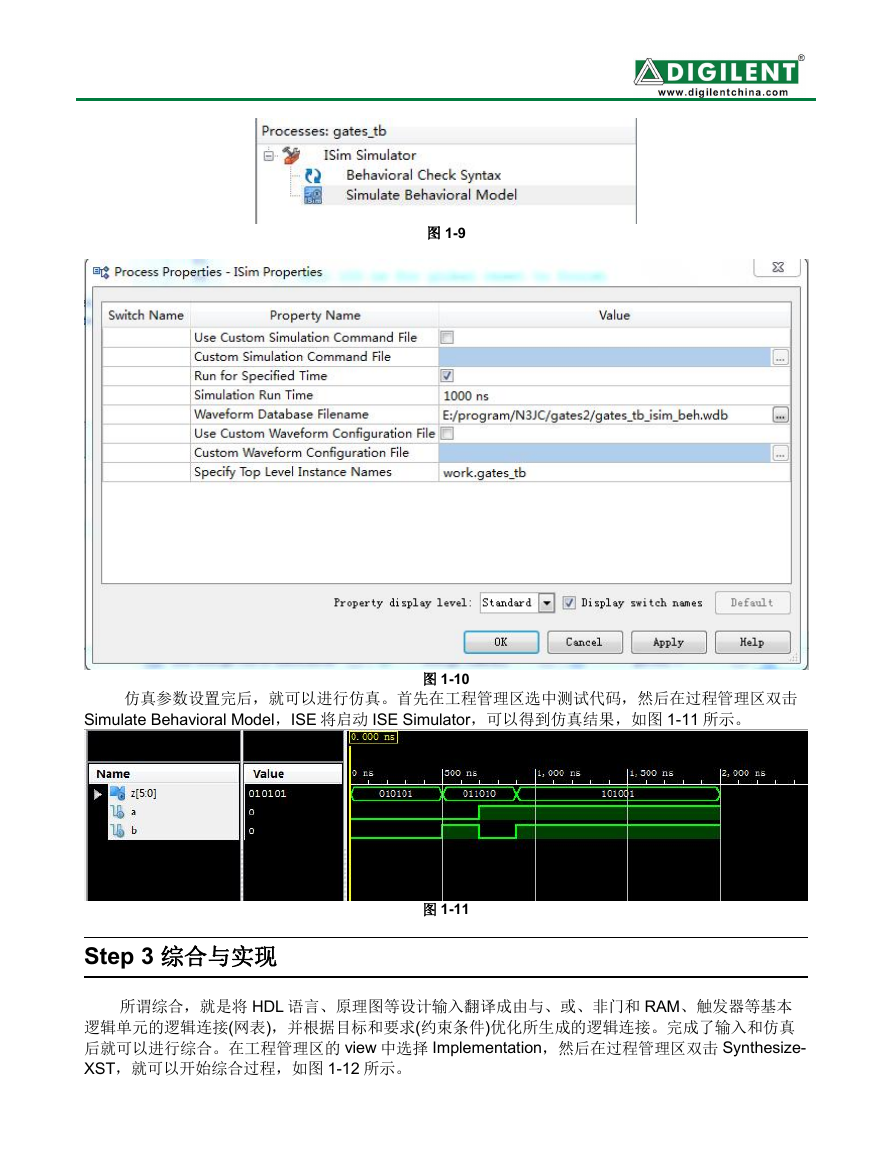

完成测试文件编辑后,确认工程管理区中 view 选项设置为 Simulation,这时在过程管理区会显示与仿

真有关的进程,如图 1-9 中 Processes 栏所示。右键单击其中的 Simulate Behavioral Model 项,选择

弹出菜单中的 Process Properties 项,会弹出如图 1-10 所示的属性设置对话框,其中 Simulation Run

Time 就是仿真时间的设置,可将其修改为任意时长。

�

图 1-9

仿真参数设置完后,就可以进行仿真。首先在工程管理区选中测试代码,然后在过程管理区双击

Simulate Behavioral Model,ISE 将启动 ISE Simulator,可以得到仿真结果,如图 1-11 所示。

图 1-10

Step 3 综合与实现

图 1-11

所谓综合,就是将 HDL 语言、原理图等设计输入翻译成由与、或、非门和 RAM、触发器等基本

逻辑单元的逻辑连接(网表),并根据目标和要求(约束条件)优化所生成的逻辑连接。完成了输入和仿真

后就可以进行综合。在工程管理区的 view 中选择 Implementation,然后在过程管理区双击 Synthesize-

XST,就可以开始综合过程,如图 1-12 所示。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc