Título

Prefacio

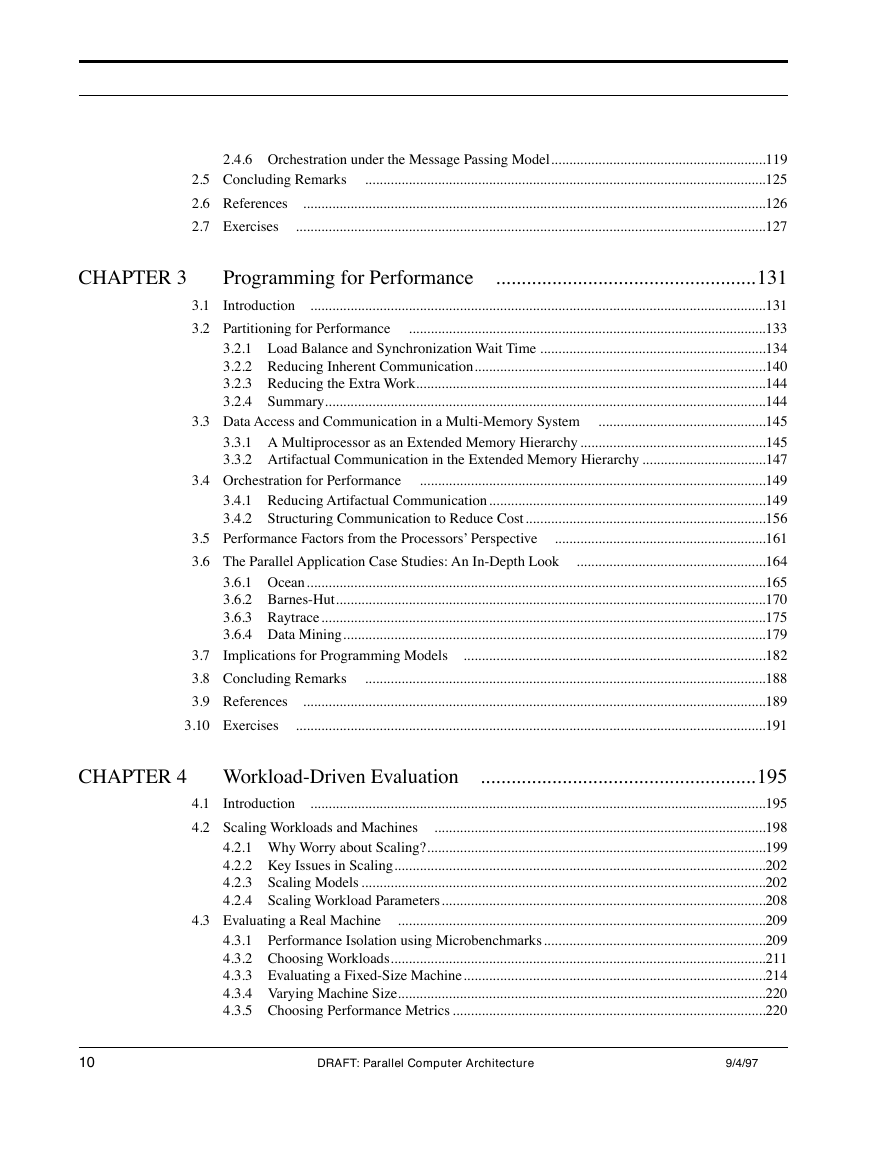

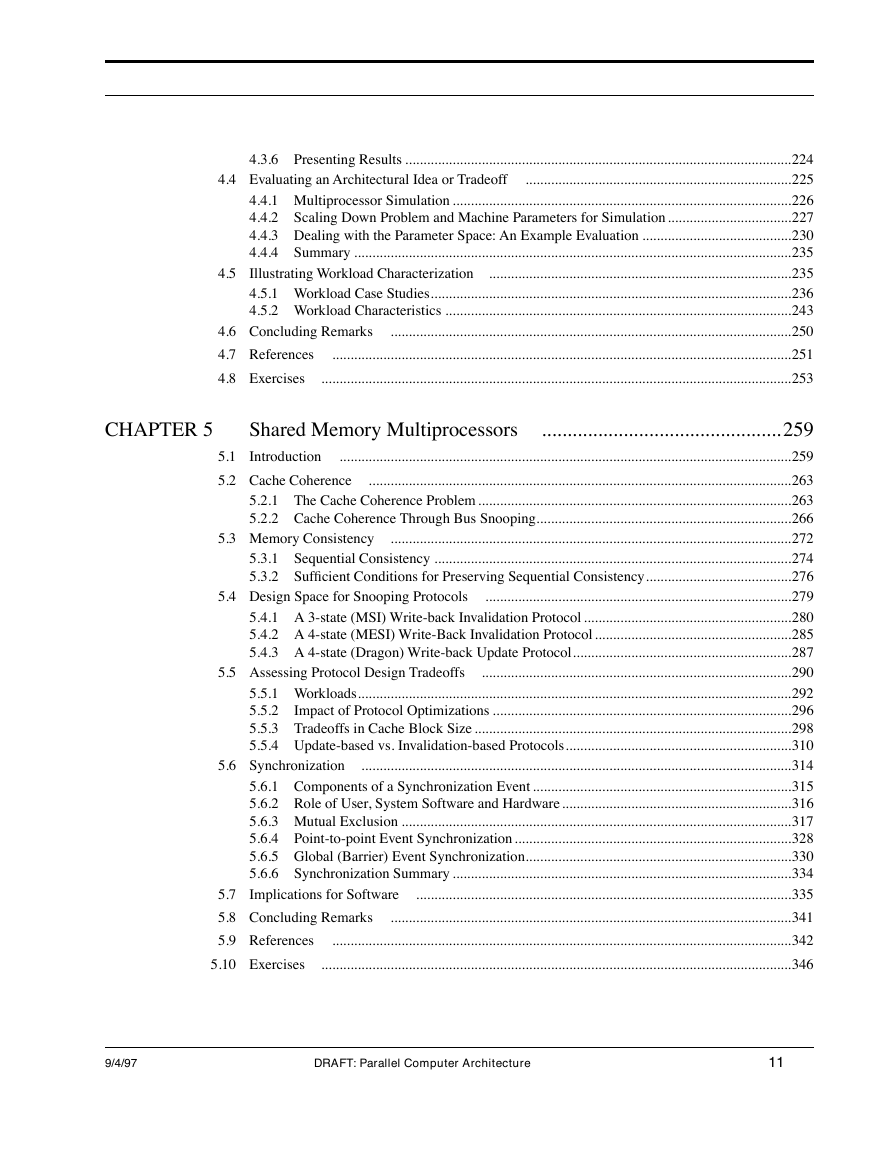

Índice

Capítulo 1

Chapter - CHAPTER 1 Introduction

1Heading - 1.1 Introduction

1Heading - 1.2 Why Parallel Architecture

Figure - Figure 1-1 Performance trends over time of micro, ...

2Heading - 1.2.1 Application Trends

Equation - .

Equation - .

3Heading - Scientific and Engineering Computing

Figure - Figure 1-2 Grand Challenge Application Requirement...

Figure - Figure 1-3 Speedup on Three Versions of a Parallel...

3Heading - Commercial Computing

Figure - Figure 1-4 TPC-C throughput versus number of proce...

Example - Example 1-1 The tpmC for the Tandem Himalaya and I...

2Heading - 1.2.2 Technology Trends

Figure - Figure 1-5 Improvement in logic density and clock ...

2Heading - 1.2.3 Architectural Trends

Figure - Figure 1-6 Number of transistors per processor chi...

Figure - Figure 1-7 Distribution of potential instruction-l...

Figure - Figure 1-8 Number of processors in fully configure...

Figure - Figure 1-9 Bandwidth of the shared memory bus in c...

2Heading - 1.2.4 Supercomputers

Figure - Figure 1-10 Uniprocessor performance of supercompu...

Figure - Figure 1-11 Performance of supercomputers and MPPs...

Figure - Figure 1-12 Type of systems used in 500 fastest co...

2Heading - 1.2.5 Summary

1Heading - 1.3 Convergence of Parallel Architectures

2Heading - 1.3.1 Communication Architecture

Figure - Figure 1-13 Layers of Abstraction in Parallel Comp...

2Heading - 1.3.2 Shared Memory

Figure - Figure 1-14 Typical memory model for shared-memory...

Figure - Figure 1-15 Extending a system into a shared-memor...

Figure - Figure 1-16 Typical Shared-Memory Multiprocessor I...

Figure - Figure 1-17 Physical and logical organization of t...

Figure - Figure 1-18 Physical and logical organization of t...

Figure - Figure 1-19 Non-uniform Memory Access (NUMA) Scala...

Figure - Figure 1-20 Cray T3E Scalable Shared Address Space...

2Heading - 1.3.3 Message-Passing

Figure - Figure 1-21 User level send/receive message passin...

Figure - Figure 1-22 Typical structure of an early message ...

Figure - Figure 1-23 IBM SP-2 Message Passing Machine

Figure - Figure 1-24 Intel Paragon

2Heading - 1.3.4 Convergence

2Heading - 1.3.5 Data Parallel Processing

Figure - Figure 1-25 Typical organization of a data paralle...

2Heading - 1.3.6 Other Parallel Architectures

3Heading - Dataflow Architecture

Figure - Figure 1-26 Dataflow graph and basic execution pip...

3Heading - Systolic Architectures

Figure - Figure 1-27 Systolic Array computation of an inner...

2Heading - 1.3.7 A Generic Parallel Architecture

Figure - Figure 1-28 Generic scalable multiprocessor organi...

1Heading - 1.4 Fundamental Design Issues

2Heading - 1.4.1 Communication Abstraction

2Heading - 1.4.2 Programming Model Requirements

2Heading - 1.4.3 Naming

3Heading - Operations

2Heading - 1.4.4 Ordering

2Heading - 1.4.5 Communication and Replication

2Heading - 1.4.6 Performance

Example - Example 1-2 Suppose a component can perform a spec...

3Heading - Data Transfer Time

Equation -

Equation - .

3Heading - Overhead and Occupancy

Equation -

3Heading - Communication Cost

Equation -

3Heading - Summary

1Heading - 1.5 Concluding Remarks

1Heading - 1.6 References

1Heading - 1.7 Exercises

Exercise - 1.1 Compute the annual growth rate in number of tr...

Exercise - 1.2 Compute the annual performance growth rates fo...

TableTitle - Table 1-1 Performance of leading workstations

Exercise - 1.3 Suppose you are given a program which does a f...

Exercise - 1.4 Given a histogram of available parallelism suc...

Exercise - 1.5 Locate the current TPC performance data on the...

Exercise - 1.6 In message passing models each process is prov...

Exercise - 1.7 To move an message along links in an unloaded ...

Exercise - 1.8 Consider a simple 2D finite difference scheme ...

ExerciseStep - All the values are 64-bit floating point numbers. ...

Exercise - 1.9 Consider the simple pipelined component descri...

Exercise - 1.10 Show that Equation�1.4 follows from Equation�...

Exercise - 1.11 What is the x-intercept of the line in Equati...

Exercise - 1.12 Suppose we have a machine with a 64-bit wide ...

Exercise - 1.13 Suppose this 32-byte line is transferred to a...

Exercise - 1.14 Suppose we have a machine with a message star...

Exercise - 1.15 Derive a general formula for the “half-power ...

Exercise - 1.16 Assuming that before transmitting a message t...

Exercise - 1.17 Consider a machine running at 100 MIPS on som...

Exercise - 1.18 Assume the instruction mix and miss rate as i...

Exercise - 1.19 Of course, no matter how many processors you ...

Capítulo 2

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc