第16卷,第1期

2009年3月

JOURNAL OF COMMUNICATION UNIVERSITY OF CHINA(SCIENCE AND TECHNOLOGY)

Mar,2009

中国传媒大学学报自然科学版

V01.16。No.1

电子时钟仿真及其FPGA实现

宋翠翠,董永鑫,郭华帅,陈同洲

(中国传媒大学信息工程学院,北京100024)

摘要:基于VHDL语言设计各个模块,用原理图文件的方式将各个模块连接起来,通过调试仿真,最终实现了24小

时时钟的正常显示,清零,暂停,调整时间的功能,并将其烧录至FLEX系列EPF 10k10LC84—4此种型号的芯片中,

按照设计的管脚设置对电路板进行连线,测试并验证了各项功能的正确性。

关键词:VHDL;PLD;编译;仿真

中图分类号:TN01l文献标识码:A文章编号:1673—4793(2009)01—0069—06

Simulation and FPGA Implementation on Electronic Clock

SONG Cui—cui,DONG YONG—fin,GUO Hua-shuai,CHEN Tong-zhou

(Information Engineering Institute,Communication University of China,Beijing 100024,China)

Abstract:Our project is designed in VHDL The modules ale cooperative by the way of schematic diagram

files,which call run as a 24一hour clock,including functions of the time displaying,clear,pause,etc.after

the simulation and debug.Then we burn the programm into the EPF lOklOLC84—4,FLEX series,and

verify the functions after the completation of the pins乇onnective on the circuit board according to the pre—

setting.

Key words:VHDL;PLD;compiler;simulation

1 引言

VHDL硬件描述语言和MAX+plus II开发软件。

VHDL硬件描述语言在电子设计自动化(EDA)

中扮演着重要的角色。由于采用了具有多层次描述

随着科学技术的迅猛发展,电子工业界经历了

系统硬件功能的能力的“自顶向下”(Top—Down)

巨大的飞跃。集成电路的设计正朝着速度快、性能

高、容量大、体积小和微功耗的方向发展。基于这种

情况,可编程逻辑器件的出现和发展大大改变了传

统的系统设计方法。

可编程逻辑器件和相应的设计技术体现在三个

主要方面:一是可编程逻辑器件的芯片技术;二是适

用于可逻辑编程器件的硬件编程技术,三是可编程

和基于库(Library—Based)的全新设计方法,它使设

计师们摆脱了大量的辅助设计工作,而把精力集中

于创造性的方案与概念构思上,用新的思路来发掘

硬件设备的潜力,从而极大地提高了设计效率,缩短

了产品的研制周期。

MAX+plusⅡ是集成了编辑器、仿真工具、检

查/分析工具和优化/综合工具的这些所有开发工具

逻辑器件设计的EDA开发工具,它主要用来进行可

编程逻辑器件应用的具体实现。在本实验中采用了

集成度较高的FPGA可编程逻辑器件,选用了

的一种集成的开发环境,通过该开发环境能够很方

便的检验设计的仿真结果以及建立起与可编程逻辑

器件的管脚之间对应的关系。

收稿日期:2008一lO—16

作者简介:宋翠翠(1984一),女(汉族),湖北襄樊人,中国传媒大学2007级硕士研究生.E-mail:Song eici@126.corn

万方数据

�

70

中同传媒大学学报自然科学版

第16卷

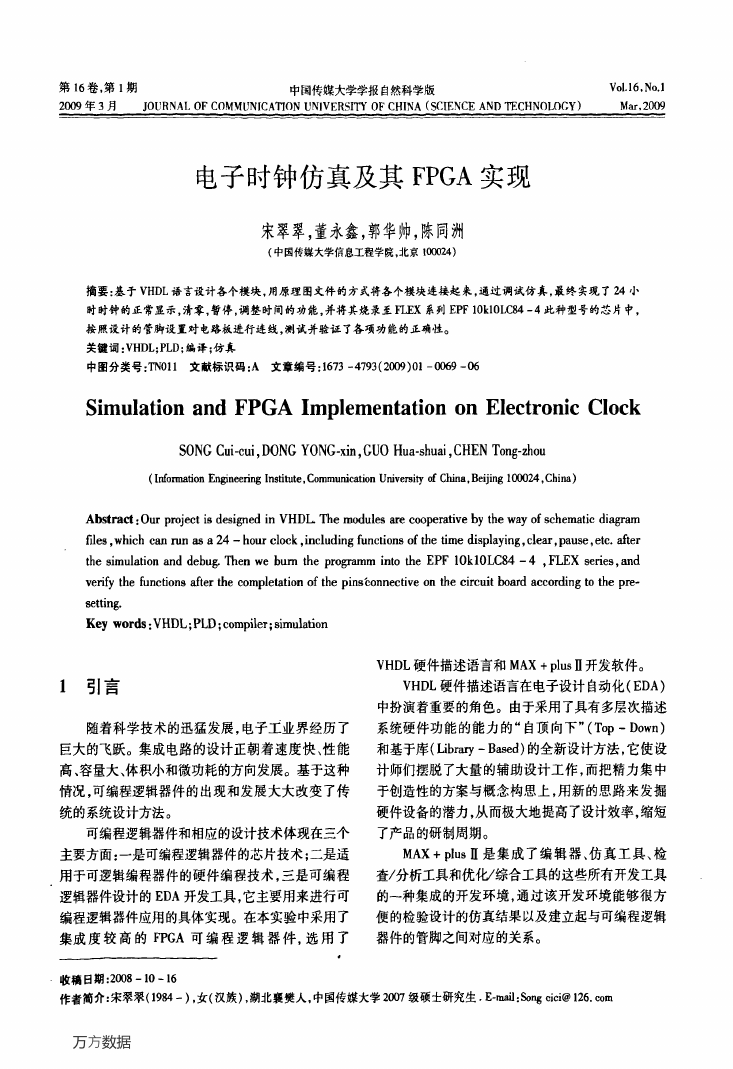

这种设计方法首先从系统设计入手,在顶层进

计数信号,分钟计数器的进位输出信号又作为小时

行功能方框图的划分和结构设计。在方框图一级进

计数器的计数信号。设计一个同时显示时、分、秒6

行仿真、纠错,并用硬件描述语言对高层次的系统行

个数字的数字钟,则需要6个七段显示器。若同时

为进行描述,在系统一级进行验证。然后用综合优

点亮这6个七段显示器,则电路中会产生一个比较

化工具生成具体门电路的网表,其对应的物理实现

大的电流,很容易造成电路烧坏,我们通过扫描电路

级可以是印刷电路板或专用集成电路。由于设计的

来解决这一问题,通过产生一个扫描信号LT(0)一

主要仿真和调试过程是在高层次上完成的,这不仅

LT(5)来控制6个七段显示器,依次点亮6个七段

有利于早期发现结构设计上的错误,避免设计工作

显示器,也就是每次只点亮一个七段显示器。只要

的浪费,而且也减少了逻辑功能仿真的工作量,提高

扫描信号CS(0)一CS(5)的频率超过人的眼睛视觉

了设计的一次成功率。

2时钟的综合设计

2.1整个系统设计的框图

暂留频率24Hz以上,就可以达到尽管每次点亮单

个七段显示器,却能具有6个同时显示的视觉效果,

而且显示也不致闪烁抖动。其中6位扫描信号一方

面控制七段显示器依次点亮,一方面控制6选1选

择器输出相应显示数字。

控制电路用来将控制时钟的一些功能加入到整

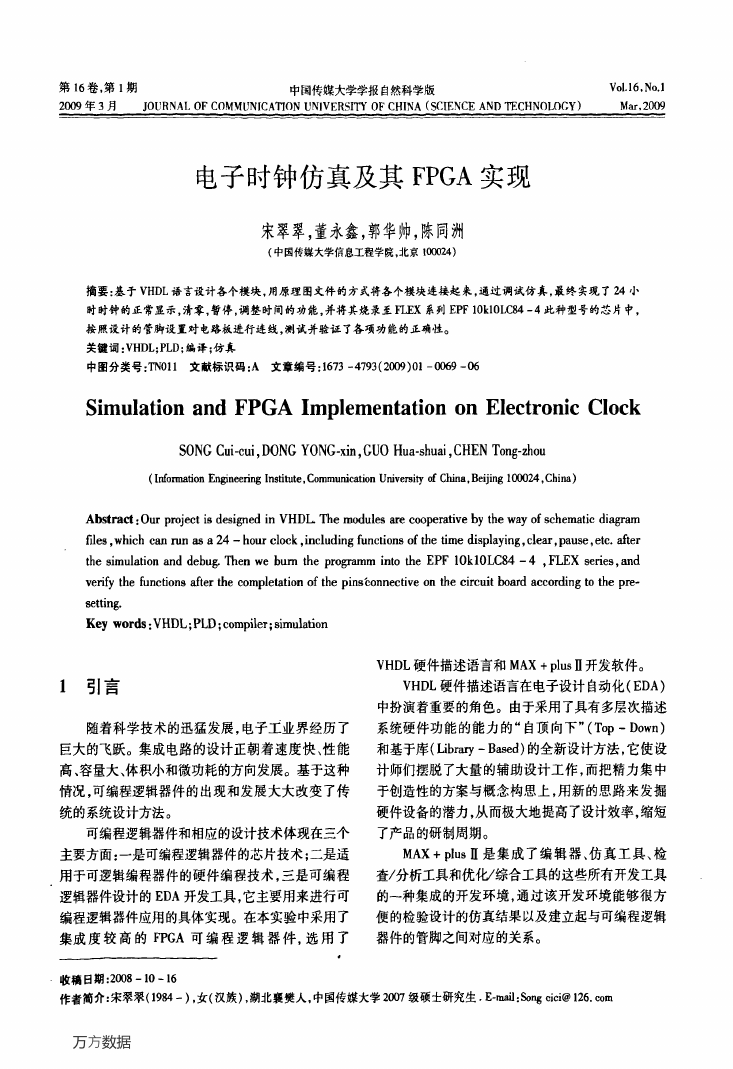

秒计数器的计数时钟信号为1 Hz的标准信号,

个正常计数的显示电路中,通过最终的显示来验证

可以由CPLD板上提供的20MHZ的信号通过分频

控制电路的正确性。图l为整体系统设计标图。

得到。秒计数器的进位输出信号作为分钟计数器的

图1整体系统设计的框图

2.2模块的设计

2.2.1分频模块

CPLD板上提供的时钟为20MHz的信号,通过

三次分频,将该信号经过1000,200,100次分频将其

变为lHz的输出时钟信号。时钟信号可以为占空

比为1:1的方波,也可以为其它形式占空比的方波。

2.2.2计数器模块

这里主要介绍60进制的计数模块,24小时的

计数模块与其原理完全一样。计数模块中,上述描

述的分频模块分出的l Hz的时钟信号作为该模块

万方数据

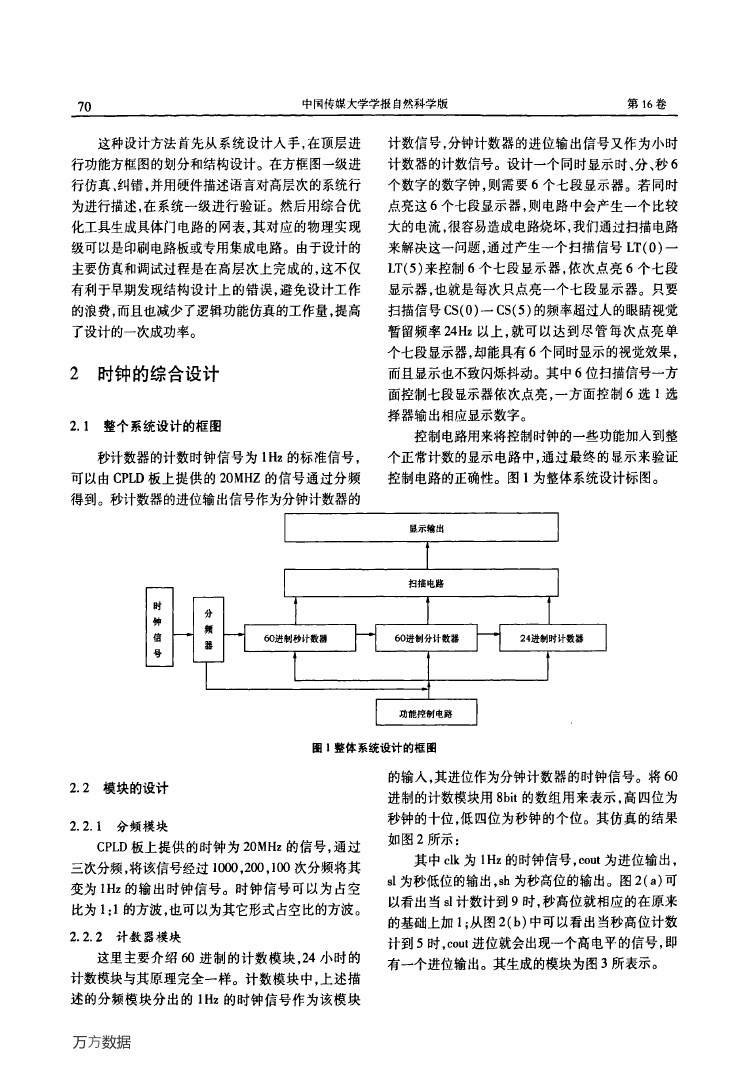

的输入,其进位作为分钟计数器的时钟信号。将60

进制的计数模块用8bit的数组用来表示,高四位为

秒钟的十位,低四位为秒钟的个位。其仿真的结果

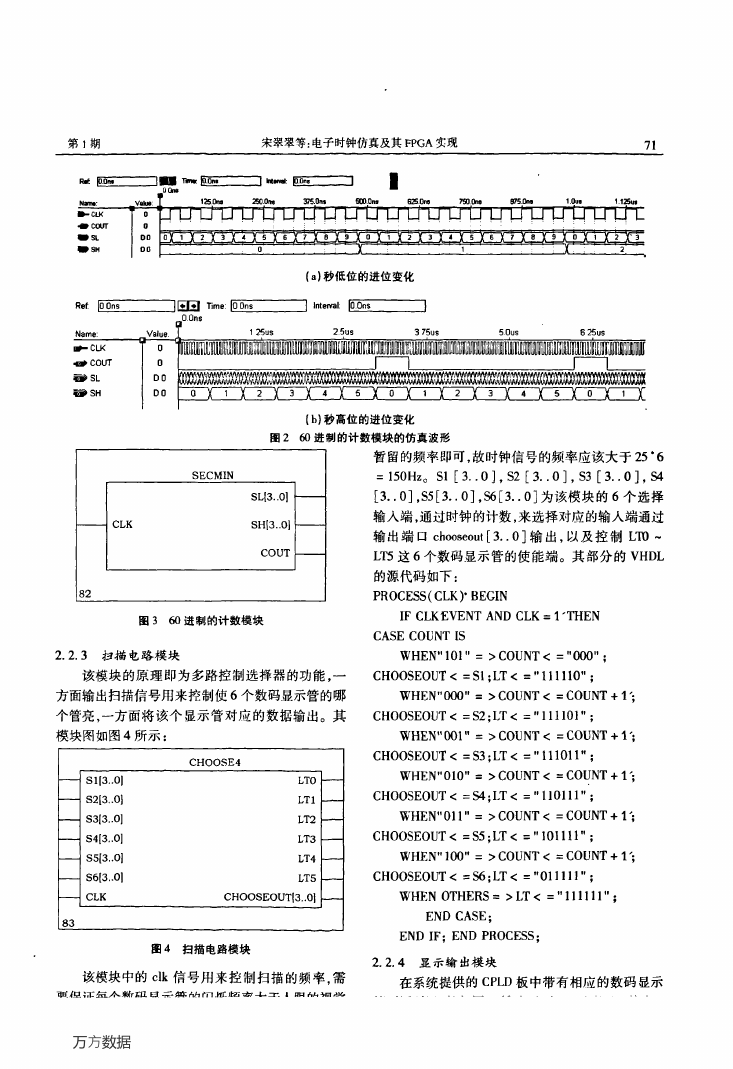

如图2所示:

其中clk为1Hz的时钟信号,cout为进位输出,

sl为秒低位的输出,sh为秒高位的输出。图2(a)可

以看出当sl计数计到9时,秒高位就相应的在原来

的基础上加1;从图2(b)中可以看出当秒高位计数

计到5时,eout进位就会出现一个高电平的信号,即

有一个进位输出。其生成的模块为图3所表示。

�

第1期

宋翠翠等:电子时钟仿真及其FPGA实现

71

:=m一巴竺L——J-一巴竺巴—一

■

125n碍2邬_0咐

O 』U—L几j_U]一n』_叫L』-L几.厂州U—L门-厂U1门_rUl肌

D0 百】r丁]f1—r丁11]rrT丁X t X!址X!X!X 2 j!X!x_5 J 6 X!X!X!X!X!X!j【=L

晤0ms

鲫On.

瑚0晴

eT5J)ns

1 0ue

'126¨

3750m

..VIII∞:.

0

Nm:

■--CI.K

●COUT

-sL

-81"1

00

.0

::

X

1

X

:.

2

Ref_匝互二]田Time。匝三二]Inte晌l:匝互二]

(a)秒低位的进位变化

ml-CLK

啊●COLrr

曰SL

i爹SH

0 眦珈砌舢0㈣哦删聊堋舢』唧删伽册砌唧册舢删舢姗哪砌咖删肌肌㈣姗0唧舢唧m叽眦孤㈣删『

000c00c00330勰㈣黜50c3㈣3c30c0000cc800c00c00|:000030ccoc30c000c30∞30c030c3黜c030030090c908300030锄030030c00ccccc0000003《

厂]

广]

0

D 0

D0

(b)秒高位的进位变化

图2

60进制的计数模块的仿真波形

暂留的频率即可,故时钟信号的频率应该大于25’6

=150Hz。S1[3..0],s2[3..0],s3[3..O],S4

[3..0],S5[3..0],S6[3..0]为该模块的6个选择

输入端,通过时钟的计数,来选择对应的输入端通过

输出端口chooseout[3..0]输出,以及控制LT0一

LT5这6个数码显示管的使能端。其部分的VHDL

的源代码如下:

PROCESS(CLK)’BEGIN

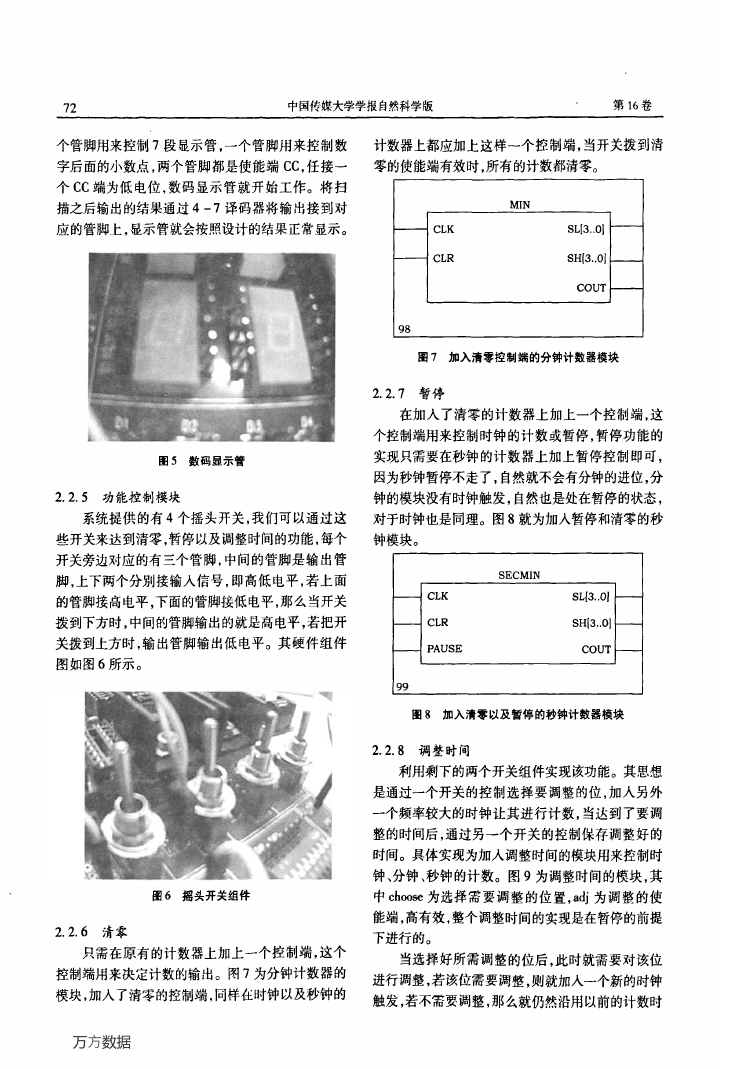

图3

60进制的计数模块

IF CLKEVENT AND CLK=1’THEN

CASE COUNT IS

2.2.3扫描电路模块

WHEN”101”=>COUNT<=”000”:

该模块的原理即为多路控制选择器的功能,一

CHOOSEOUT<=S1:LT<=”111110”:

方面输出扫捕信号用来控制使6个数码显示管的哪

个管亮,一方面将该个显示管对应的数据输出。其

模块图如图4所示:

CHOOSE4

WHEN”000”=>COUNT<=COUNT+1,.

CHOOSEOUT<=S2:LT<=”111101”;

WHEN”001”=>COUNT<=COUNT+1,.

CHOOSEOUT<=S3:LT<=”111011”;

WHEN”010”=>COUNT<=COUNT+1,.

CHOOSEOUT<=S4:IX<=”110111”;

WHEN”01 l”=>COUNT<=COUNT+1乇

CHOOSEOUT<=S5:LT<=”101111”;

WHEN”100”=>COUNT<=COUNT+1,.

CHOOSEOUT<=S6:LT<=”011111”;

LTO

LTl

LT2

LT3

LT4

LT5

S1【3。0l

$213..0】

$313..0】

S413..0】

s513..0】

$613..01

CLK

CHOOSEOUT[3..0l

WHEN 0THERS=>LT<=”111lll”:

图4扫描电路模块

END CASE:

END IF;END PROCESS;

2.2.4显示输出模块

该模块中的elk信号用来控制扫描的频率,需

萌f里;正氩小黼m日;咎Mm.I,ff.蠕赤上I l阳M拥幽

在系统提供的CPLD板中带有相应的数码显示

万方数据

�

72

中国传媒大学学报自然科学版

第16卷

个管脚用来控制7段显示管,一个管脚用来控制数

计数器上都应加上这样~个控制端,当开关拨到清

字后面的小数点,两个管脚都是使能端CC,任接一

零的使能端有效时,所有的计数都清零。

个CC端为低电位,数码显示管就开始工作。将扫

描之后输出的结果通过4—7译码器将输出接到对

应的管脚上,显示管就会按照设计的结果正常显示。

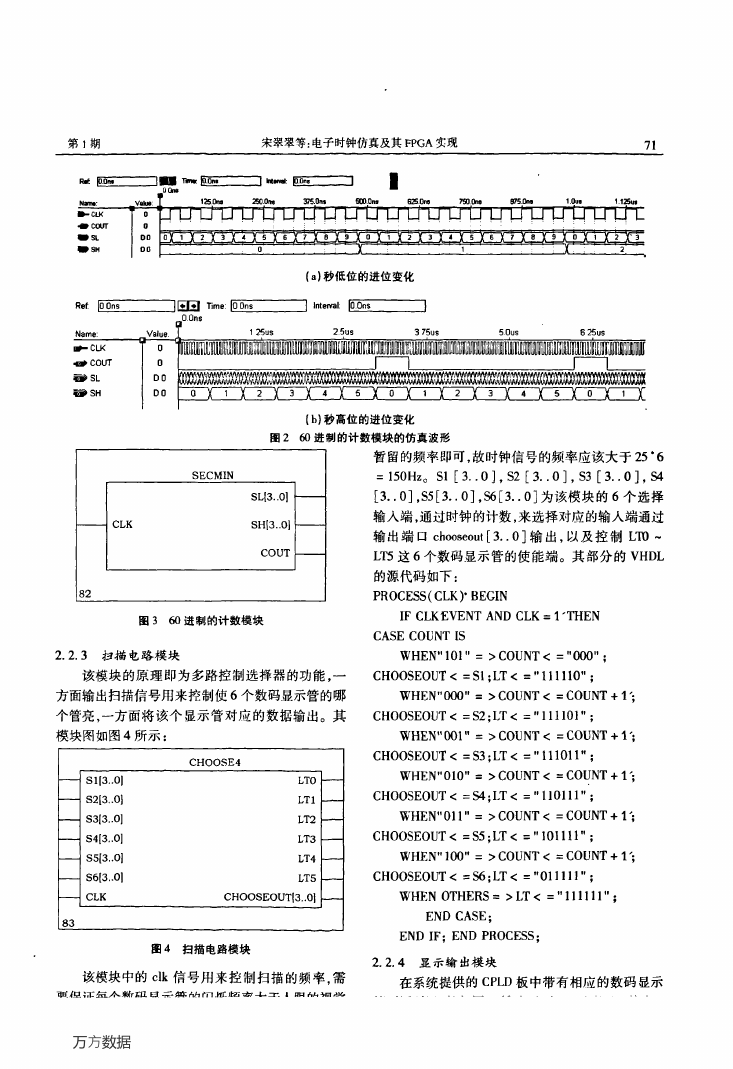

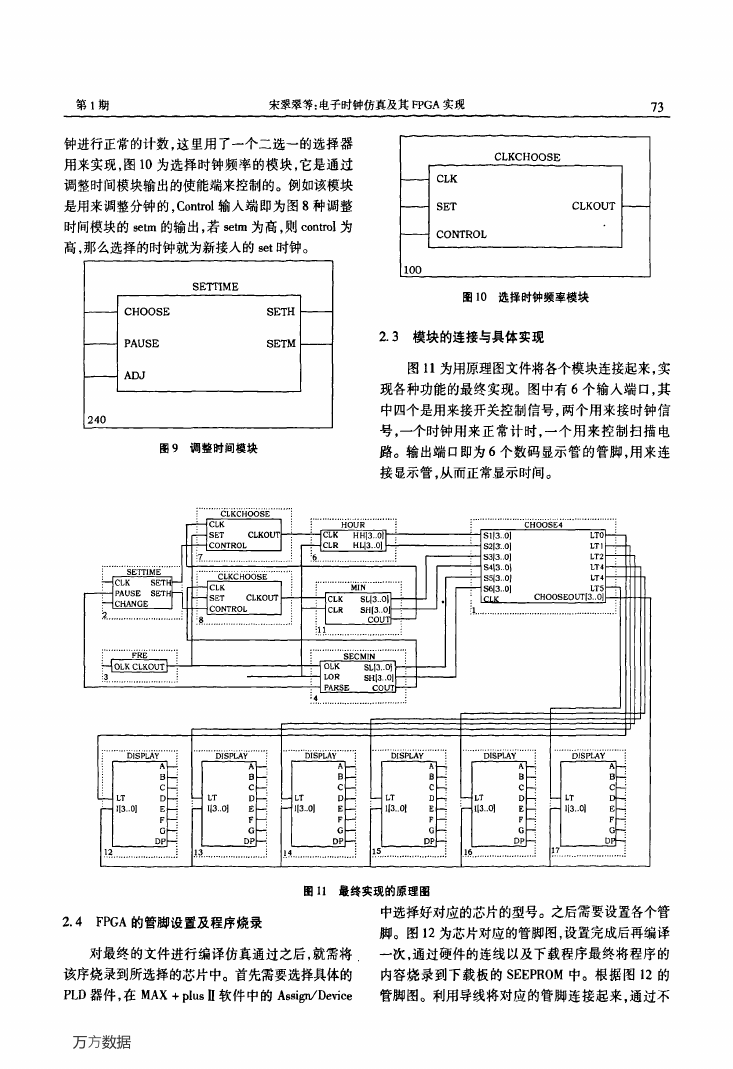

图5数码显示管

2.2.5功能控制模块

图7加入清零控制端的分钟计数器模块

2.2.7暂停

在加入了清零的计数器上加上一个控制端,这

个控制端用来控制时钟的计数或暂停,暂停功能的

实现只需要在秒钟的计数器上加上暂停控制即可,

因为秒钟暂停不走了,自然就不会有分钟的进位,分

钟的模块没有时钟触发,自然也是处在暂停的状态,

系统提供的有4个摇头开关,我们可以通过这

对于时钟也是同理。图8就为加入暂停和清零的秒

些开关来达到清零,暂停以及调整时间的功能,每个

钟模块。

开关旁边对应的有三个管脚,中间的管脚是输出管

脚,上下两个分别接输人信号,即高低电平,若上面

的管脚接高电平,下面的管脚接低电平,那么当开关

拨到下方时,中间的管脚输出的就是高电平,若把开

关拨到上方时,输出管脚输出低电平。其硬件组件

图如图6所示。

图8加入清零以及暂停的秒钟计数器模块

2.2.8 调整时间

利用剩下的两个开关组件实现该功能。其思想

是通过一个开关的控制选择要调整的位,加入另外

一个频率较大的时钟让其进行计数,当达到了要调

整的时间后,通过另一个开关的控制保存调整好的

时间。具体实现为加入调整时间的模块用来控制时

钟、分钟、秒钟的计数。图9为调整时间的模块,其

中choose为选择需要调整的位置,a由为调整的使

能端,高有效,整个调整时间的实现是在暂停的前提

下进行的。

当选择好所需调整的位后,此时就需要对该位

进行调整,若该位需要调整,则就加入一个新的时钟

触发,若不需要调整,那么就仍然沿用以前的计数时

图6摇头开关组件

2.2.6清零

只需在原有的计数器上加上一个控制端,这个

控制端用来决定计数的输出。图7为分钟计数器的

模块,加入了清零的控制端,同样在时钟以及秒钟的

万方数据

�

第1期

宋翠翠等:电子时钟仿真及其FPG^实现

73

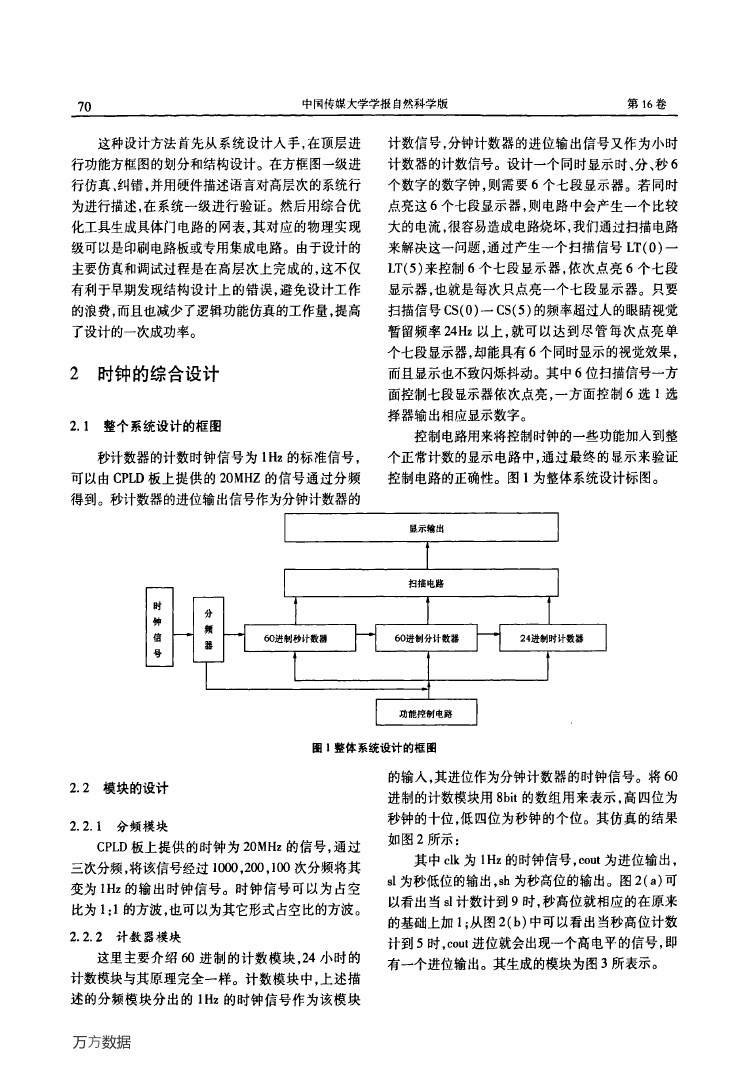

钟进行正常的计数,这里用了一个二选一的选择器

用来实现,图10为选择时钟频率的模块,它是通过

调整时间模块输出的使能端来控制的。例如该模块

是用来调整分钟的,Control输入端即为图8种调整

时间模块的setm的输出,若setm为高,则control为

高,那么选择的时钟就为新接人的set时钟。

图10选择时钟频率模块

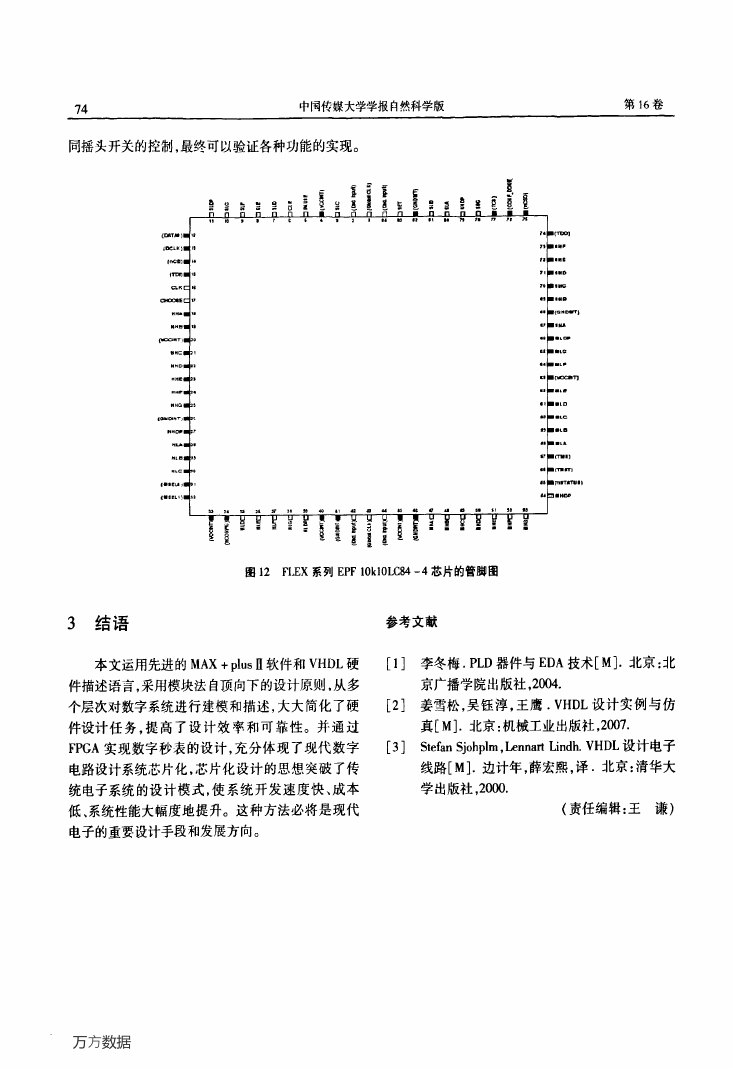

2.3模块的连接与具体实现

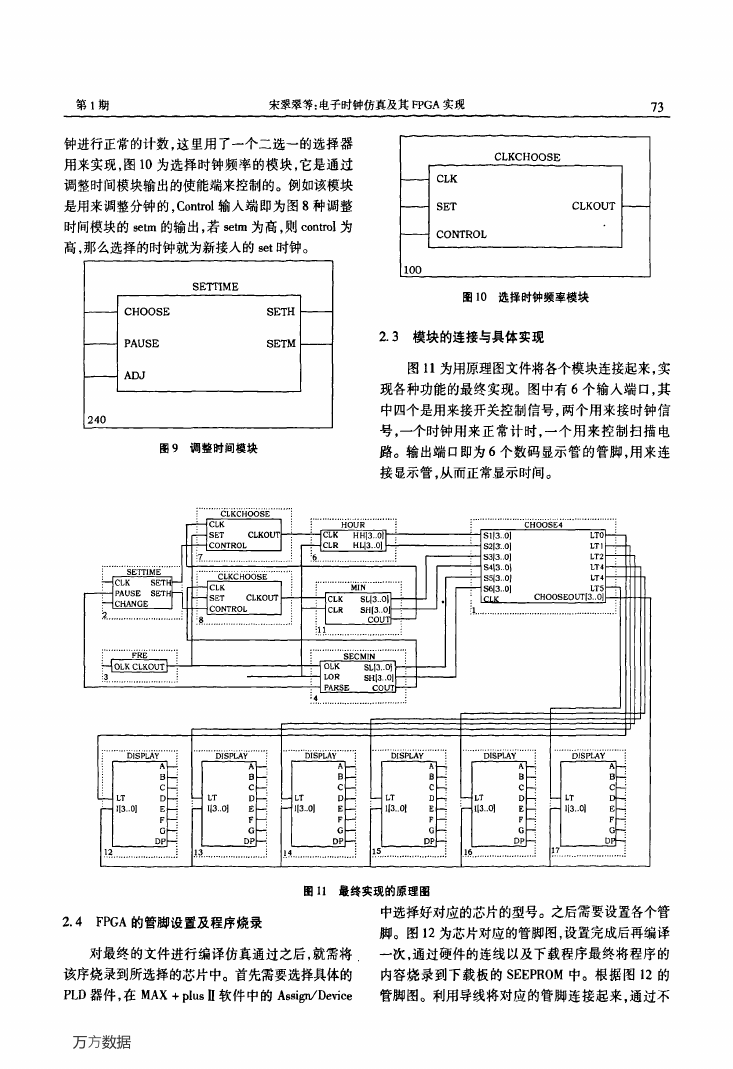

图1 1为用原理图文件将各个模块连接起来,实

现各种功能的最终实现。图中有6个输入端口,其

中四个是用来接开关控制信号,两个用来接时钟信

号,一个时钟用来正常计时,一个用来控制扫描电

路。输出端口即为6个数码显示管的管脚,用来连

接显示管,从而正常显示时间。

图9调整时间模块

图11最终实现的原理图

2.4

FPGA的管脚设置及程序烧录

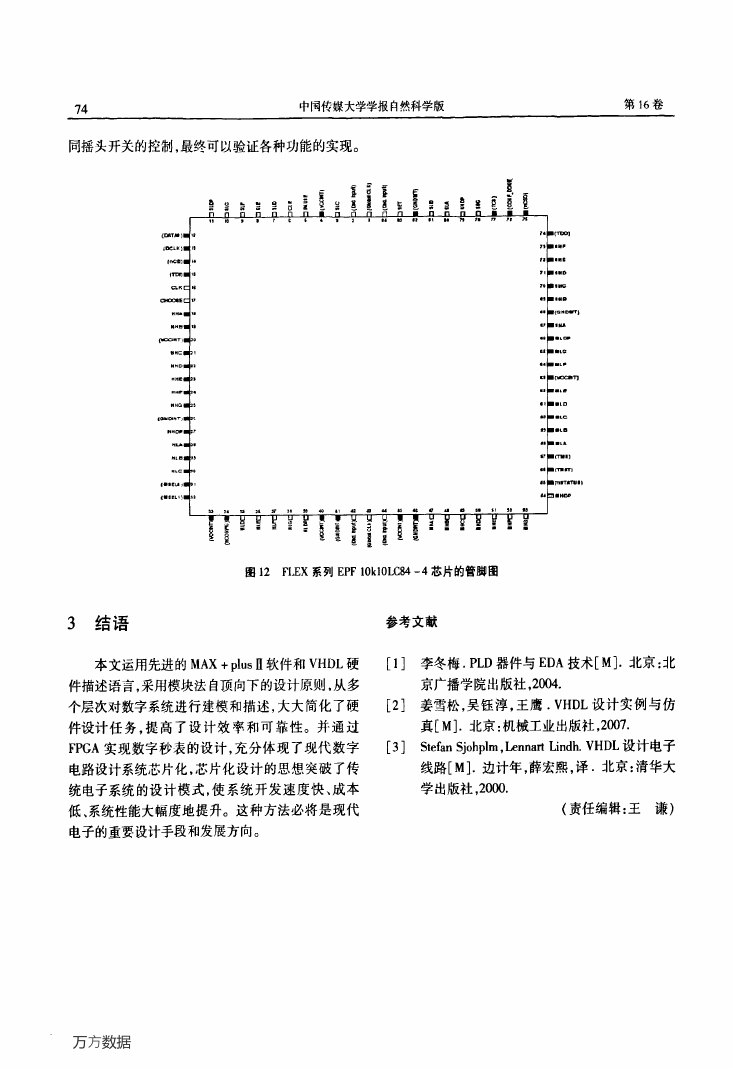

中选择好对应的芯片的型号。之后需要设置各个管

脚。图12为芯片对应的管脚图,设置完成后再编译

对最终的文件进行编译仿真通过之后,就需将

一次,通过硬件的连线以及下载程序最终将程序的

该序烧录到所选择的芯片中。首先需要选择具体的

内容烧录到下载板的SEEPROM中。根据图12的

PLD器件,在MAX+plus II软件中的Assign/Device

管脚图。利用导线将对应的管脚连接起来,通过不

万方数据

�

74

中同传媒大学学报自然科学版

第16卷

同摇头开关的控制,最终可以验证各种功能的实现。

图12 FLEX系列EPF 10klOLC84—4芯片的管脚图

3 结语

参考文献

本文运用先进的MAX+plus 11软件和VHDL硬

件描述语言,采用模块法自顶向下的设计原则,从多

李冬梅.PLD器件与EDA技术[M].北京:北

京广播学院出版社,2004.

个层次对数字系统进行建模和描述,大大简化了硬

[2]

姜雪松,吴钰淳,王鹰.VHDL设计实例与仿

件设计任务,提高了设计效率和可靠性。并通过

FPGA实现数字秒表的设计,充分体现了现代数字

[3]

电路设计系统芯片化,芯片化设计的思想突破了传

真[M].北京:机械工业出版社,2007.

Stefan Sjohplm,Lennart Lindh.VHDL设计电子

线路[M].边计年,薛宏熙,译.北京:清华大

统电子系统的设计模式,使系统开发速度快、成本

学出版社,2000.

低、系统性能大幅度地提升。这种方法必将是现代

(责任编辑:王谦)

电子的重要设计手段和发展方向。

万方数据

�

电子时钟仿真及其FPGA实现

作者:

宋翠翠, 董永鑫, 郭华帅, 陈同洲, SONG Cui-cui, DONG Yong-xin, GUO Hua-shuai

作者单位:

刊名:

, CHEN Tong-zhou

中国传媒大学信息工程学院,北京,100024

中国传媒大学学报(自然科学版)

英文刊名:

JOURNAL OF COMMUNICATION UNIVERSITY OF CHINA SCIENCE AND TECHNOLOGY

年,卷(期):

2009,16(1)

0次

引用次数:

参考文献(3条)

1.李冬梅 PLD器件与EDA技术 2004

2.姜雪松.吴钰淳.王鹰 VHDL.设计实例与仿真 2007

3.Stefan sjohplm.Lennart Lindh.边计年.薛宏熙 VHDL设计电子线路 2000

相似文献(10条)

1.期刊论文 李丰林 VHDL语言在PLD编程中的应用 -淮海工学院学报(自然科学版)2002,11(1)

可编程逻辑器件(PLD)可实现很复杂的数字系统.VHDL语言能方便地进行数字系统描述,而且能使逻辑综合产生更大的设计密度.介绍了VHDL语言的程

序结构、描述方式、特点,提出用VHDL语言设计PLD的流程.应用实例说明了利用VHDL语言可大大降低复杂PLD系统设计的难度,提高工作效率.

2.期刊论文 刘珊中.张赖.闫保定.Liu Shanzhong.Zhang Lai.Yan Baoding PLD和VHDL设计技术在电阻炉控制系统

中的应用 -电气自动化2005,27(2)

采用PLD作为电阻炉炉温的控制器,应用VHDL设计技术实现数据采集和增量式PLD控制.研究表明,该控制系统能对被控对象实现有效的PLD控制,效果良

好.

3.期刊论文 李锋.卢佩.刘成臣.石东 应用VHDL语言在PLD器件上设计实现可编程计数器 -现代电子技术2002(5)

研究用VHDL语言采用TOP TO D0WN设计方法实现了一种可以完成二进制、十进制、可逆计数功能的可编程计数器;采用MAX+PLUSII集成开发环境编辑

、综合、仿真,并下载到PLD器件中,经仿真和实际电路测试,该计数器性能可靠.

4.学位论文 李俊 基于PLD的RS码编译码器设计 2003

为了保障HCTR在无线链路中能够可靠的传输数据,就需要进行信道编码.RS码由于其特殊的编码规则,特别适用于突发性错误译码.但其算法比较复杂

,因此它的译码大都交由DSP来实现,在处理速度上受到一定限制.而可编程逻辑器件(PLD)以硬件速度执行指令,速度可得到保证.并且随着工艺水平的提高

,其规模越来越大,使它足以有能力进行复杂算法设计.该论文研究的重点就是利用CPLD实现RS码的编译码器.论文简要介绍了信道编译码的基本概念,详细

描述了RS码的编译码算法,并将算法影射为电路结构,使之以硬件形式完成所需功能.最后给出了可综合的RS(63,45)码编译码器的VHDL模型,并将它综合在

Altera公司的FPGA芯片中.由仿真结果和在实际环境中运行证明,此编译码器性能优良,运行速度满足系统设计要求.

5.期刊论文 徐晓峰.李鹏 可编程逻辑器件(PLD)的发展及VHDL语言的应用 -煤炭科技2002(2)

可编程逻辑器件(PLD)具有多种优点,将其应用于数字电子系统,可以提高系统的整体集成度和可靠性,缩短研发周期,是一种新型的电子器件。

6.期刊论文 秦长江.余子全.李玉泉.曹奇英.QIN Chang-jiang.YU Zi-quan.LI Yu-quan.CAO Qi-ying PLD与AVR总

线通信接口VHDL设计与实现 -微计算机信息2008,24(17)

可编程逻辑器件(PLD)在嵌入式系统中的应用越来越广泛.文中针对PLD与高速嵌入式单片机AVR间的通信,设计了一种采用读写方式的总线接口模块

,用硬件编成语言VHDL在Ahera公司的Max II系列器件EPM570中实现,通过仿真验证其能够完全满足通信功能;并简要介绍了PLD开发的流程.

7.期刊论文 刘宏杰.Liu Hongjie 可编程逻辑器件的VHDL语言优化设计方法 -测控技术2001,20(6)

叙述了可编程逻辑器件的VHDL语言典型设计流程,详细讨论了几种可更好地利用可编程逻辑器件实现特定逻辑功能以及提高器件利用率的VHDL优化

设计方法。

8.学位论文 胥洋央 PLD技术在计算机数字视频信号处理系统中的应用 2002

PLD是指可编程逻辑器件,是一种可将集成电路的设计与编程的方式写入到其逻辑阵列结构中的一种芯片.该论文讨论用PLD芯片作为主要控制逻辑来

设计计算机数字视频系统的一个典型应用型产品--LED视频电子显著屏系统的研制方法.该系统将计算机视频图像扫描到大屏幕显示板上,LED器件特性决

定了信号的控制是全数字式的,是数字视频信号处理的一个典型应用.该系统将PLD芯片设计成系统信号驱动的控制芯片,实现了电路结构的高度集成化.该

系统由计算机多媒体视频卡、驱动板和显示板组成.系统将多媒体视频卡输出的数字视频信号进行数据缓存、分块读取和脉宽调制等处理,形成符合显示

板结构的彩色运动图像扫描信号,输出到显示板.整个系统具有结构简单、集成度高、图像性能优越等特点.该系统在显示刷新频率为60HZ,灰度级别为

32级的条件下,图像显示清晰稳定.

9.期刊论文 王乐毅.WANG Le-yi DA设计技术与方法(Ⅰ)-EDA方法及其进展 -青岛化工学院学报(自然科学版)

2000,21(4)

EDA是现代电子学的标志。本研究对EDA设计方法及其发展进行了综述。

10.期刊论文 梁柏华.孟志华 PLD技术在计算机数字视频信号处理系统中的应用 -武汉工程职业技术学院学报

2004,16(4)

本文介绍了用PLD芯片作为主要控制逻辑来设计计算机数字视频系统,驱动控制逻辑 PLD芯片为载体通过数字集成电路方式实现,控制逻辑的功能设计

是用IEEE标准的集成电路设计语言VHDL作为行为描述语言.最后,用ACEXlK30芯片实现了该数字视频系统.

�

本文链接:http://d.g.wanfangdata.com.cn/Periodical_bjgbxyxb200901013.aspx

下载时间:2010年5月12日

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc