基于 FPGA 芯片的 FIR 滤波器电路设计

摘要:提出了一种基于 FPGA 芯片的 FIR 滤波器电路设计流程,该流程能够有效的将各种阶数与系数的 FIR

滤波器精确映射为使用单个乘法累加器结构的滤波电路,同时能够有效的设计电路的流水线级数,从而满

杜伟韬

足不同的时序需求。

引言

有限长冲击响应(FIR)滤波器因其具有线性

相位、计算结果对有限字长效应不敏感等优点[1],

在数字通信,信号处理、自动控制等领域有着广泛

的应用。近年来,随着半导体制造技术的飞速发展,

可编程逻辑阵列 FPGA 芯片的集成密度不断提高

[4],同时 FPGA 芯片所具有的无可比拟的灵活性使

其在工业领域中的应用日益普遍。

本文提出了一种基于 FPGA 芯片的 FIR 滤波器

电路设计流程,使用该流程能够较好的将不同阶数

与系数的 FIR 滤波器精确的映射转换为使用单个乘

法累加器结构的滤波电路,同时能够有效的设计电

路的流水线级数,从而满足不同的时序需求。

后续段落内容组织如下,算法设计与验证部分

描述了滤波器系数和阶数的设计方法,以及滤波器

的定点算法测试方法;电路结构设计部分给出了本

文滤波器的电路模块的组织结构以及各模块的功

能;存储方案设计部分描述电路 RAM 地址空间的

使用方案以及算法公式中的数据标号和 RAM 地址

的对应关系;流水线设计部分描述了流水线的设计

方法;实验结果部分给出了使用该流程设计的滤波

器的实验结果。

算法设计与验证

对于 N-1 阶 FIR 滤波器,其第 n 个输入 x(n)对

应 的 输 出 y(n) 的 计 算 公 式 如 式 1 所 示 ,

( )

y n

N

1

i

0

( )

h i

(

x n i

)

(1)

其中 滤波器的幅频特性由系数 h(n)决定,阶数越

高,滤波器的过渡带则越陡峭,阻带抑制特性也越

好,但同时计算资源的开销也越大,在工程应用中,

使用 MATLAB 软件的信号处理和滤波器设计工具

箱[2]可以方便的使用多种约束条件设计满足不同

资源开销或滤波性能的滤波器系数矢量。

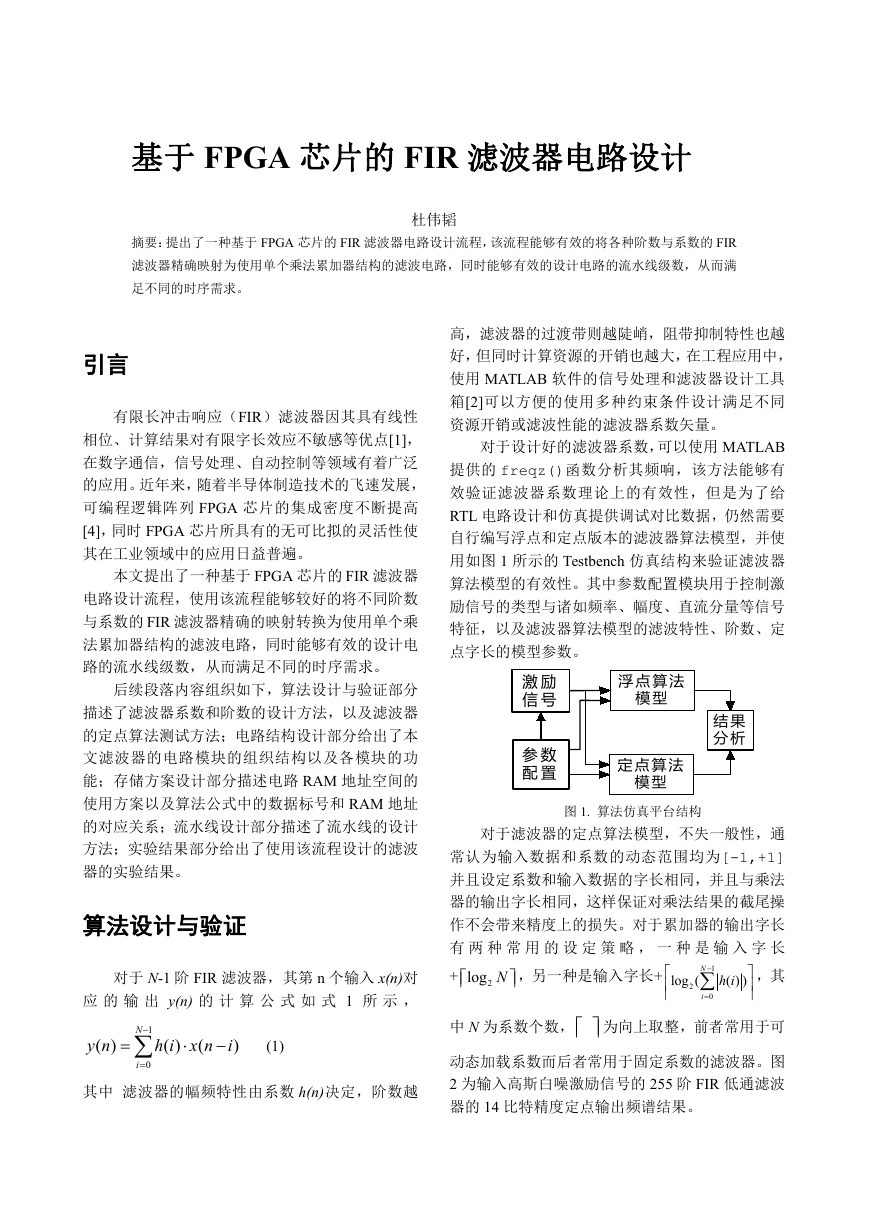

对于设计好的滤波器系数,可以使用 MATLAB

提供的 freqz()函数分析其频响,该方法能够有

效验证滤波器系数理论上的有效性,但是为了给

RTL 电路设计和仿真提供调试对比数据,仍然需要

自行编写浮点和定点版本的滤波器算法模型,并使

用如图 1 所示的 Testbench 仿真结构来验证滤波器

算法模型的有效性。其中参数配置模块用于控制激

励信号的类型与诸如频率、幅度、直流分量等信号

特征,以及滤波器算法模型的滤波特性、阶数、定

点字长的模型参数。

激 励

信 号

参 数

配 置

浮 点 算 法

模 型

定 点 算 法

模 型

结 果

分 析

图 1. 算法仿真平台结构

对于滤波器的定点算法模型,不失一般性,通

常认为输入数据和系数的动态范围均为[-1,+1]

并且设定系数和输入数据的字长相同,并且与乘法

器的输出字长相同,这样保证对乘法结果的截尾操

作不会带来精度上的损失。对于累加器的输出字长

有 两 种 常 用 的 设 定 策 略 , 一 种 是 输 入 字 长

+

,另一种是输入字长+

log N

( ) )

h i

,其

2

log (

2

N

1

i

0

中 N 为系数个数, 为向上取整,前者常用于可

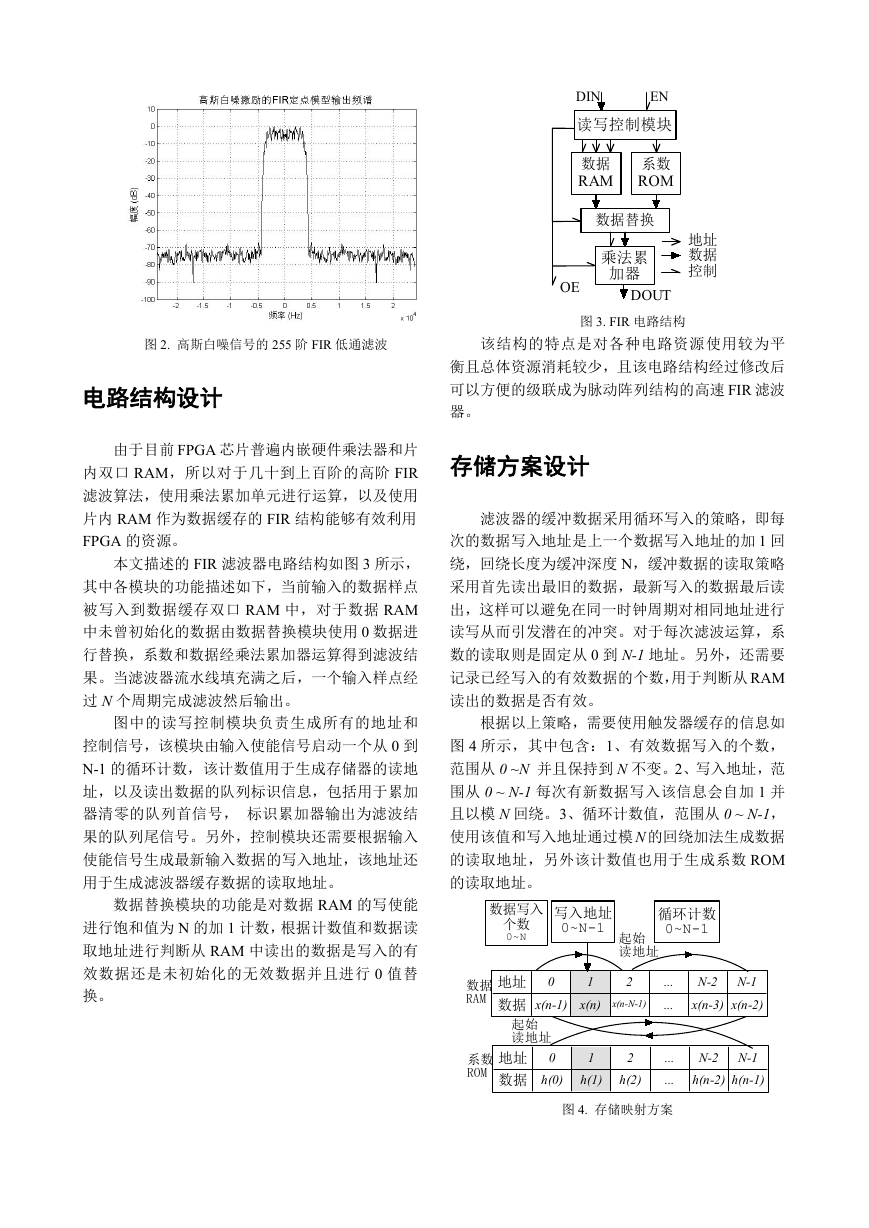

动态加载系数而后者常用于固定系数的滤波器。图

2 为输入高斯白噪激励信号的 255 阶 FIR 低通滤波

器的 14 比特精度定点输出频谱结果。

�

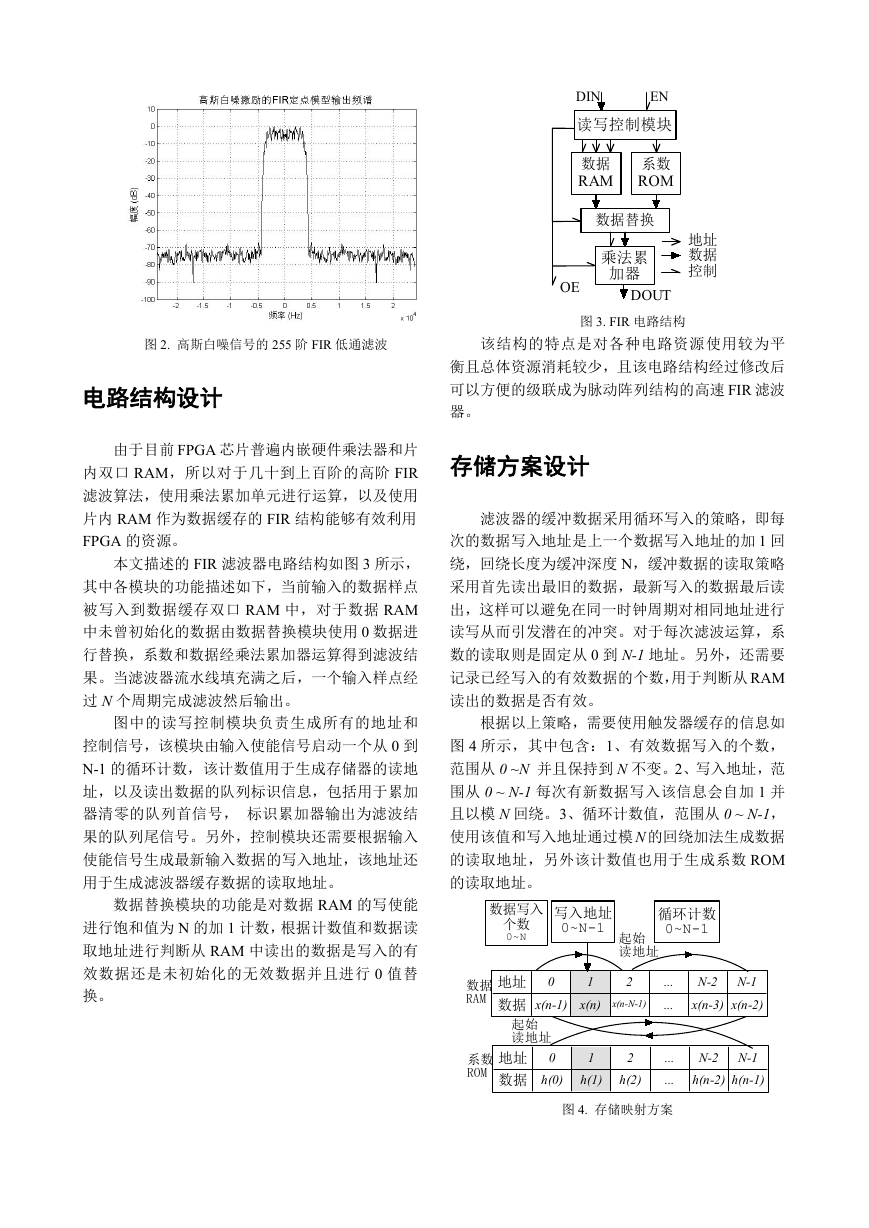

DIN

EN

读写控制模块

数据

RAM

系数

ROM

数据替换

地址

数据

控制

乘法累

加器

DOUT

OE

图 3. FIR 电路结构

该结构的特点是对各种电路资源使用较为平

衡且总体资源消耗较少,且该电路结构经过修改后

可以方便的级联成为脉动阵列结构的高速 FIR 滤波

器。

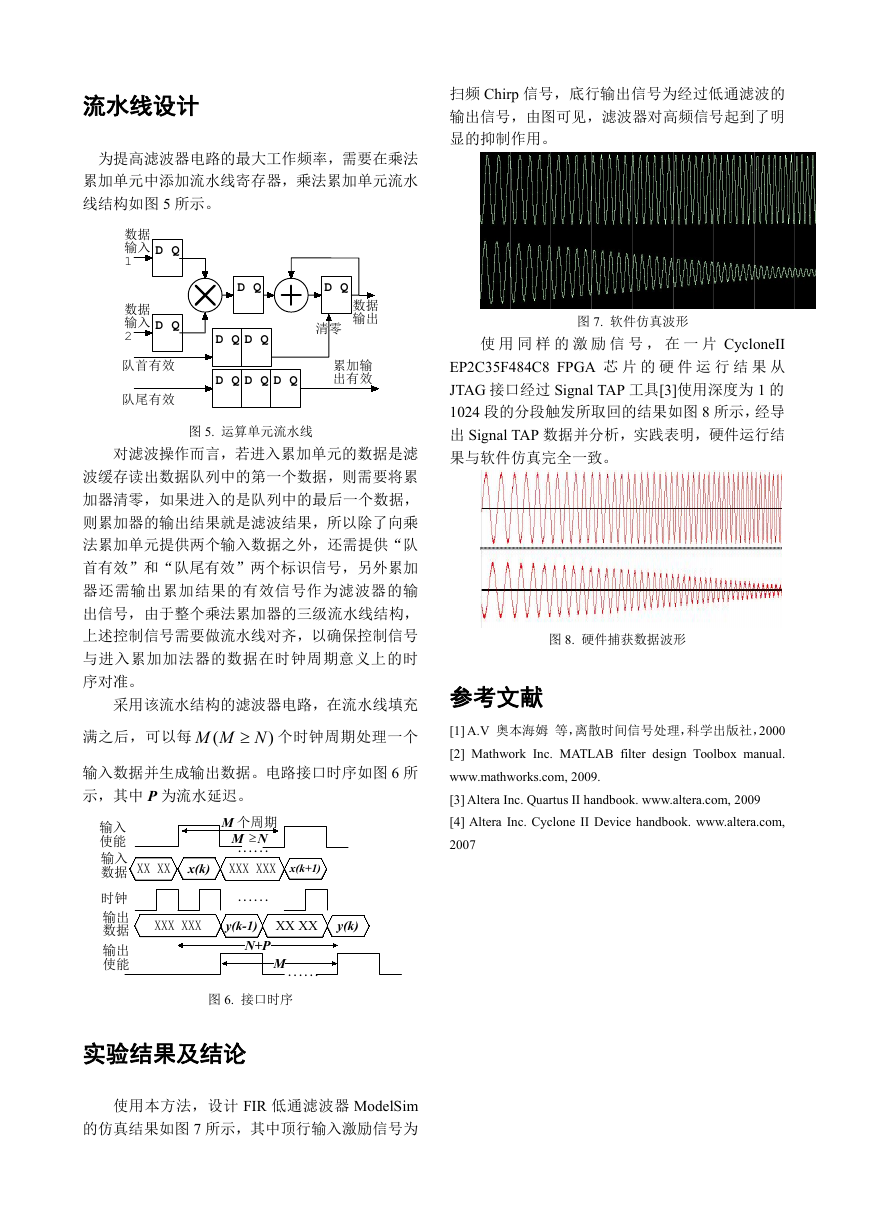

存储方案设计

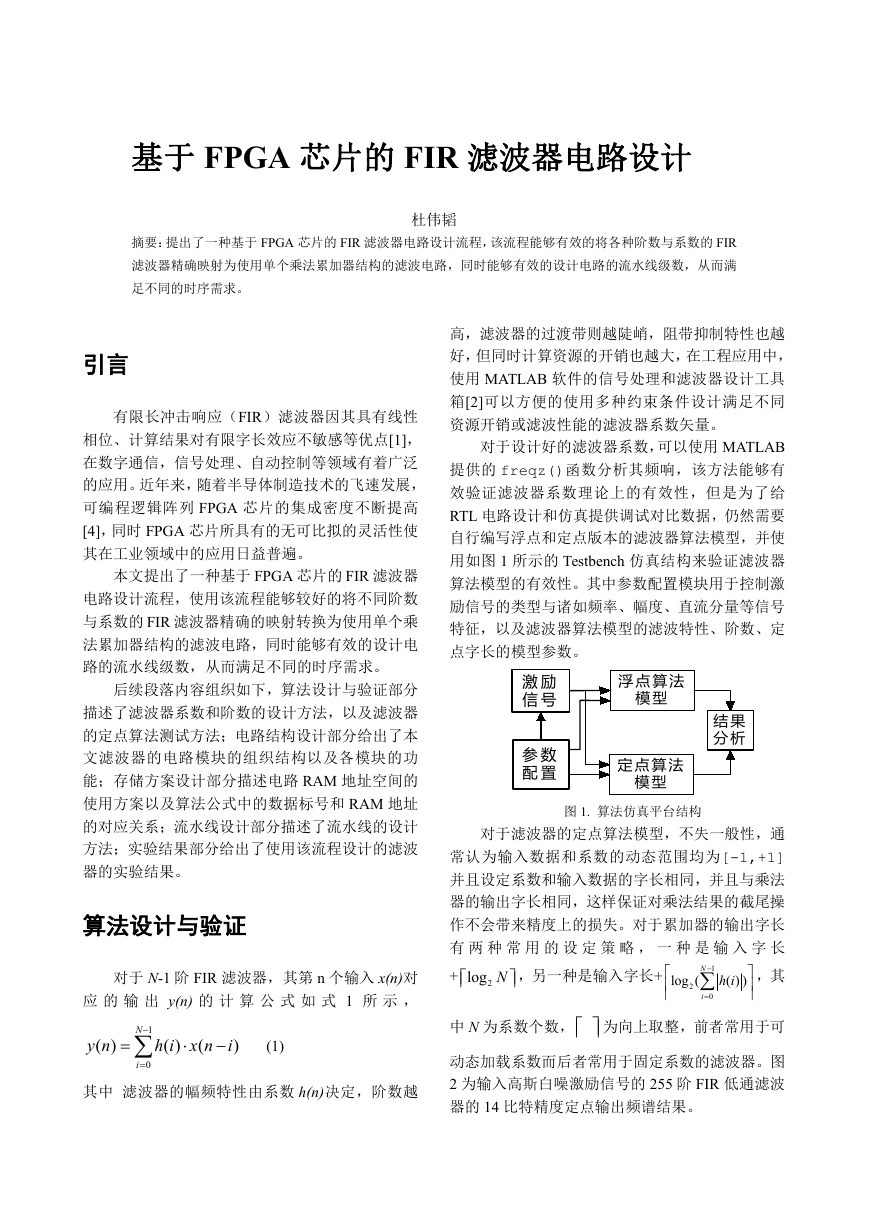

滤波器的缓冲数据采用循环写入的策略,即每

次的数据写入地址是上一个数据写入地址的加 1 回

绕,回绕长度为缓冲深度 N,缓冲数据的读取策略

采用首先读出最旧的数据,最新写入的数据最后读

出,这样可以避免在同一时钟周期对相同地址进行

读写从而引发潜在的冲突。对于每次滤波运算,系

数的读取则是固定从 0 到 N-1 地址。另外,还需要

记录已经写入的有效数据的个数,用于判断从 RAM

读出的数据是否有效。

根据以上策略,需要使用触发器缓存的信息如

图 4 所示,其中包含:1、有效数据写入的个数,

范围从 0 ~N 并且保持到 N 不变。2、写入地址,范

围从 0 ~ N-1 每次有新数据写入该信息会自加 1 并

且以模 N 回绕。3、循环计数值,范围从 0 ~ N-1,

使用该值和写入地址通过模 N 的回绕加法生成数据

的读取地址,另外该计数值也用于生成系数 ROM

的读取地址。

数据写入

个数

0~N

写入地址

0~N-1

循环计数

0~N-1

起始

读地址

数据

RAM

地址 0

数据 x(n-1)

1

x(n)

2

x(n-N-1)

起始

读地址

地址 0

数据 h(0)

系数

ROM

1

h(1)

2

h(2)

...

...

...

...

N-1

N-2

x(n-3) x(n-2)

N-1

N-2

h(n-2) h(n-1)

图 4. 存储映射方案

图 2. 高斯白噪信号的 255 阶 FIR 低通滤波

电路结构设计

由于目前 FPGA 芯片普遍内嵌硬件乘法器和片

内双口 RAM,所以对于几十到上百阶的高阶 FIR

滤波算法,使用乘法累加单元进行运算,以及使用

片内 RAM 作为数据缓存的 FIR 结构能够有效利用

FPGA 的资源。

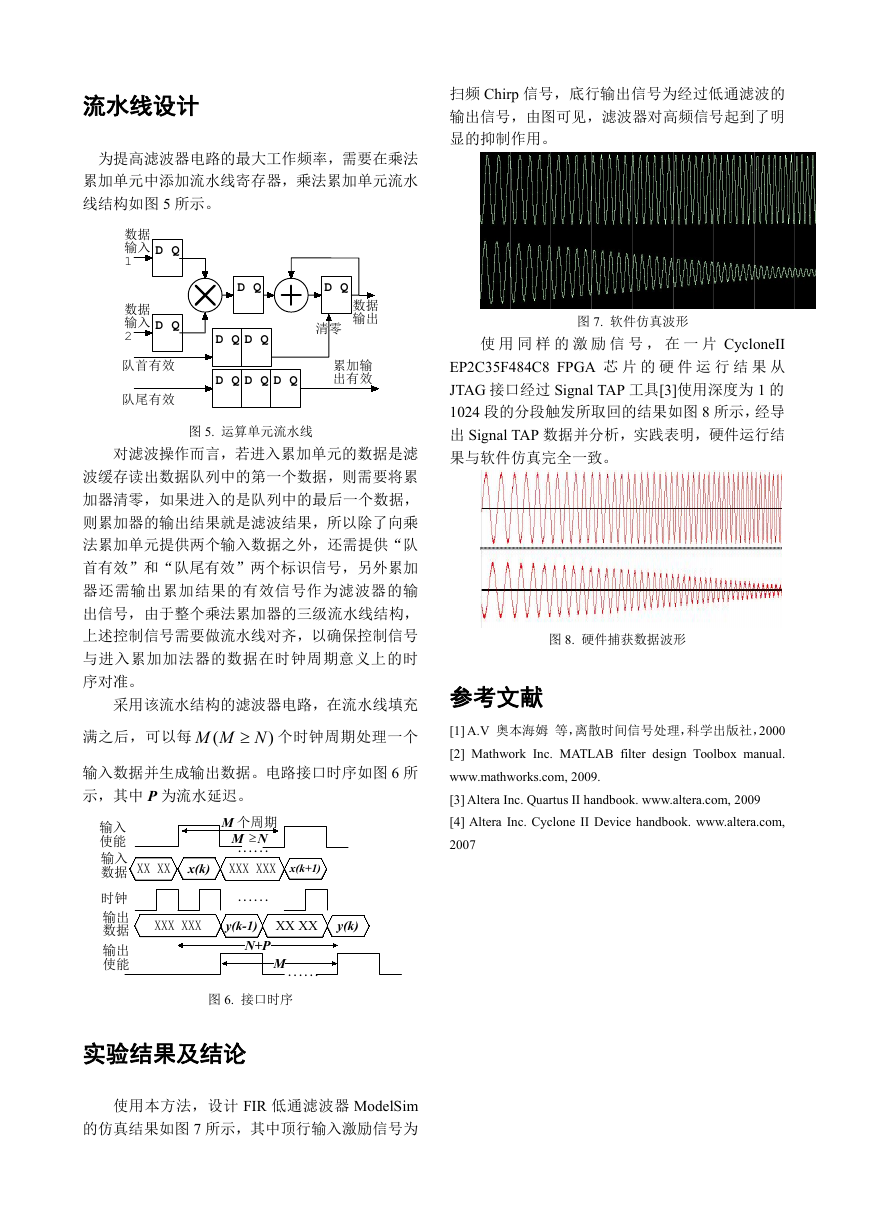

本文描述的 FIR 滤波器电路结构如图 3 所示,

其中各模块的功能描述如下,当前输入的数据样点

被写入到数据缓存双口 RAM 中,对于数据 RAM

中未曾初始化的数据由数据替换模块使用 0 数据进

行替换,系数和数据经乘法累加器运算得到滤波结

果。当滤波器流水线填充满之后,一个输入样点经

过 N 个周期完成滤波然后输出。

图中的读写控制模块负责生成所有的地址和

控制信号,该模块由输入使能信号启动一个从 0 到

N-1 的循环计数,该计数值用于生成存储器的读地

址,以及读出数据的队列标识信息,包括用于累加

器清零的队列首信号, 标识累加器输出为滤波结

果的队列尾信号。另外,控制模块还需要根据输入

使能信号生成最新输入数据的写入地址,该地址还

用于生成滤波器缓存数据的读取地址。

数据替换模块的功能是对数据 RAM 的写使能

进行饱和值为 N 的加 1 计数,根据计数值和数据读

取地址进行判断从 RAM 中读出的数据是写入的有

效数据还是未初始化的无效数据并且进行 0 值替

换。

�

扫频 Chirp 信号,底行输出信号为经过低通滤波的

输出信号,由图可见,滤波器对高频信号起到了明

显的抑制作用。

图 7. 软件仿真波形

使 用 同 样 的 激 励 信 号 , 在 一 片 CycloneII

EP2C35F484C8 FPGA 芯 片 的 硬 件 运 行 结 果 从

JTAG 接口经过 Signal TAP 工具[3]使用深度为 1 的

1024 段的分段触发所取回的结果如图 8 所示,经导

出 Signal TAP 数据并分析,实践表明,硬件运行结

果与软件仿真完全一致。

图 8. 硬件捕获数据波形

参考文献

[1] A.V 奥本海姆 等,离散时间信号处理,科学出版社,2000

[2] Mathwork Inc. MATLAB filter design Toolbox manual.

www.mathworks.com, 2009.

[3] Altera Inc. Quartus II handbook. www.altera.com, 2009

[4] Altera Inc. Cyclone II Device handbook. www.altera.com,

2007

流水线设计

为提高滤波器电路的最大工作频率,需要在乘法

累加单元中添加流水线寄存器,乘法累加单元流水

线结构如图 5 所示。

数据

输入

1

D Q

D Q

数据

输入

2

队首有效

队尾有效

D Q

D Q D Q

D Q D Q D Q

D Q

清零

数据

输出

累加输

出有效

图 5. 运算单元流水线

对滤波操作而言,若进入累加单元的数据是滤

波缓存读出数据队列中的第一个数据,则需要将累

加器清零,如果进入的是队列中的最后一个数据,

则累加器的输出结果就是滤波结果,所以除了向乘

法累加单元提供两个输入数据之外,还需提供“队

首有效”和“队尾有效”两个标识信号,另外累加

器还需输出累加结果的有效信号作为滤波器的输

出信号,由于整个乘法累加器的三级流水线结构,

上述控制信号需要做流水线对齐,以确保控制信号

与进入累加加法器的数据在时钟周期意义上的时

序对准。

采用该流水结构的滤波器电路,在流水线填充

满之后,可以每 (

M M N 个时钟周期处理一个

)

输入数据并生成输出数据。电路接口时序如图 6 所

示,其中 P 为流水延迟。

输入

使能

输入

数据

时钟

输出

数据

输出

使能

M 个周期

M N

. . . . . .

XX XX

x(k)

XXX XXX

x(k+1)

. . . . . .

XXX XXX

y(k-1)

XX XX

y(k)

N+P

M

. . . . . .

图 6. 接口时序

实验结果及结论

使用本方法,设计 FIR 低通滤波器 ModelSim

的仿真结果如图 7 所示,其中顶行输入激励信号为

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc