课程设计实验报告

设计题目:六管 MOS 静态存储单元的

版图设计

报告人:朱旭

学号:20064693

合作者:王庆,李凤军

专业班级:微电子学 06-(1)班

学院:电子科学与应用物理系

实验日期:2009.12.15~2009.12.23

指导老师:杨依忠 汪涛

�

一.设计目的与意义

1. 本课程设计是一门综合性专业实践课程,目的是配合集成电路

设计基础、集成电路设计硬件描述语言、超大规模集成电路

CAD、器件模型 CAD、集成电路版图设计、微电子工艺等课程,

培养相关专业本科生 IC 设计的实践能力;

2. 让学生进一步掌握基本的集成电路与器件设计和调试的方法

与步骤;掌握设计输入、编译、模拟、仿真、综合、布图、下

载及硬件测试等 IC 设计基本过程;

3. 初步掌握应用典型的 HDL(VHDL、Verilog),基于 FPGA 的 IC

设计调试工具、Zeni2003 物理设计工具进行集成电路设计、

模拟与硬件仿真的方法和过程;

4. 进一步巩固所学 IC 设计相关的理论知识,提高运用所学知识

分析和解决实际集成电路工程设计问题的能力;

5. 经过查找资料、选择方案、设计仿真器件或电路、检查版图设

计、撰写设计报告等一系列实践过程,使学生得到一次较全面

的 IC 设计工程实践训练,通过理论联系实际,提高和培养创

新能力,为后续课程的学习,毕业设计,毕业后的工作打下基

础;

6. 通过对六管静态 MOS 存储器的设计,掌握由两个反相器级联组

成的双稳态电路组成的基本单元的原理和内部结构,并弄清楚

作为静态存储器的工作原理;

7.通过对整个设计的过程的熟悉,系的基本单元的原理和内部

结构,并弄清楚作为静态统的了解 linux 的各种命令,并熟

悉系统的功能。了解九天 EDA 软件,通过对电路图与版图的

验证,实现电路功能,为以后的学习打下良好的基础。

二.设计的主要内容和要求

内容:

要求:

六管 MOS 静态存储单元的版图设计

1. 分析六管 MOS 静态存储单元的逻辑功能及结构构成

2. 用反相器结构形式构建 CMOS 结构的电路图

3. 利用 EDA 工具 PDT 画出其相应版图

4. 利用几何设计规则文件进行在线 DRC 验证并优化版

图

�

三.设计思想及说明

SRAM 的基本单元是两个反相器级联构成的双稳态电路,它

是两个物理尺寸和特性完全相等的反相器,其中一个作为另一个

的输入。该双稳态电路的电压传输特性曲线为如图 2 所示的蝶形

图。

当电路工作在 A 或 B 点时,整个环路增益很小,即使产生

较大的偏离(只要不超过 C 点),也会逐渐减小直到消除。这个

特点就使电路可以稳定的存储一对相反的逻辑(高、低电平)。

SNM 可以反映存储器的稳定性。

当该电路作为 SRAM 的这会改变存储的信息。而写周期若

要改变存储的逻辑,只需其中的存储单元时,在读周期内两个反

向器输入端电压会发生变化,但不能越过 C 点,否一个反相器的

电压从 C 点的一边变到另一边。

图 1 是一个六管静态 MOS 存储单元,它由 6 个 MOS 管组成,

其中,T1 和 T2 构成一个触发器。当 T1 导通 T2 截止时,表示"0"状

态;相反则表示"1"状态。T3 和 T4 为负载管,每个 MOS 管相当于一

个电阻;T5 和 T6 用作选通门,控制读写操作。

这种六管 MOS 静态存储单元的三种状态如下:

(1)保持状态

当 C 线为"0"时,T5 和 T6 均截止,T1 和 T2 中必有一个是导通

的,另外一个 MOS 管则必然截止(当 T1 导通 T2 截止时,表示存储

了数据"0",相反则表示存储了数据"1"),导通的 MOS 管通过 T3 或

T4 连续提供电流。只要不停电,存储单元就能够永远保持原来的状

�

态,因此称为静态存储器。

(2)读出过程

当 C 线为"1"时,T5 和 T6 均导通。存储单元中原来存储的信息

经过位线输出。如果原来存储数据"1",则位线 1 输出为"1",位线 0

输出为"0";如果原来存储的数据为"0",则线 1 输出为"0",位线 0 输

出为"1"。

(3)写入过程

当 C 线为"1"时,T5 和 T6 均导通。如果要写入"1",则令位线 1

为"1",位线 0 为"0",这时,T2 导通,T1 截止;如果要写入"0",则

令位线 1 为"0",位线 0 为"1",这时,T1 导通,T2 截止。

C

Vdd

T3

T1

T4

T2

B

T6

D

A

T5

D

图1 MOS型六管存储器

四.设计采用的硬件和软件环境和条件

1. EDA 实验开发主系统:GW48-GK(+FPGA 开发软件, FPGA

适配板 GWAK50+);

2. 基于 Windows 操作系统的 Quantms II FPGA/CPLD 设计开发应

用软件包;

3. 基于 Unix 和 Linux 操作系统的国产华大 Zeni2003EDA 软件包

---可视设计仿真(VDE)、物理设计工具(PDT);Mentor

Graphics 版图设计工具;

4. Sun 图形工作站、台式微型计算机、万用表、示波器等。

�

五.设计步骤和各模块组成

1. 在 linx 系统下新建文件夹,即:

打开终端→输入命令“mkdir 文件夹名”。

2. 打开你的文件夹并打开画图界面,即:

输入命令 cd 文件名→“pdt” →新建工程(new library→

在文件夹中找到 techloge 文件并选中) →new cell(输入 cell 名)。

3. 按照一定的规则画版图。

4. 做验证。

在 Verify 选项中做验证,并根据提示改正错误。

5. 画电路图

画好版图后,在端口中输入命令“zse”,进入画电路的界面,

画好电路图,做验证无误后,在 check→output→CDL 中,产

生你命名的网表。

6. 做 lvs 验证

找到对应的 lvs 文件,在端口中输入命令“ldc –i inv.lvs”,

按下面的要求修改:

Primary…………你命名的 cell 名

library…………你命名的 library 名

SCH-NETLIST…………你命名的 CLD 文件名

SCH-Primary…………你命名的电路单元名

然后,点 run。

若有错,修改版图,再重复以上的步骤直到没有错误为止。

六.源代码或设计图,对设计器件或电路的模

拟、测试结果及其分析;

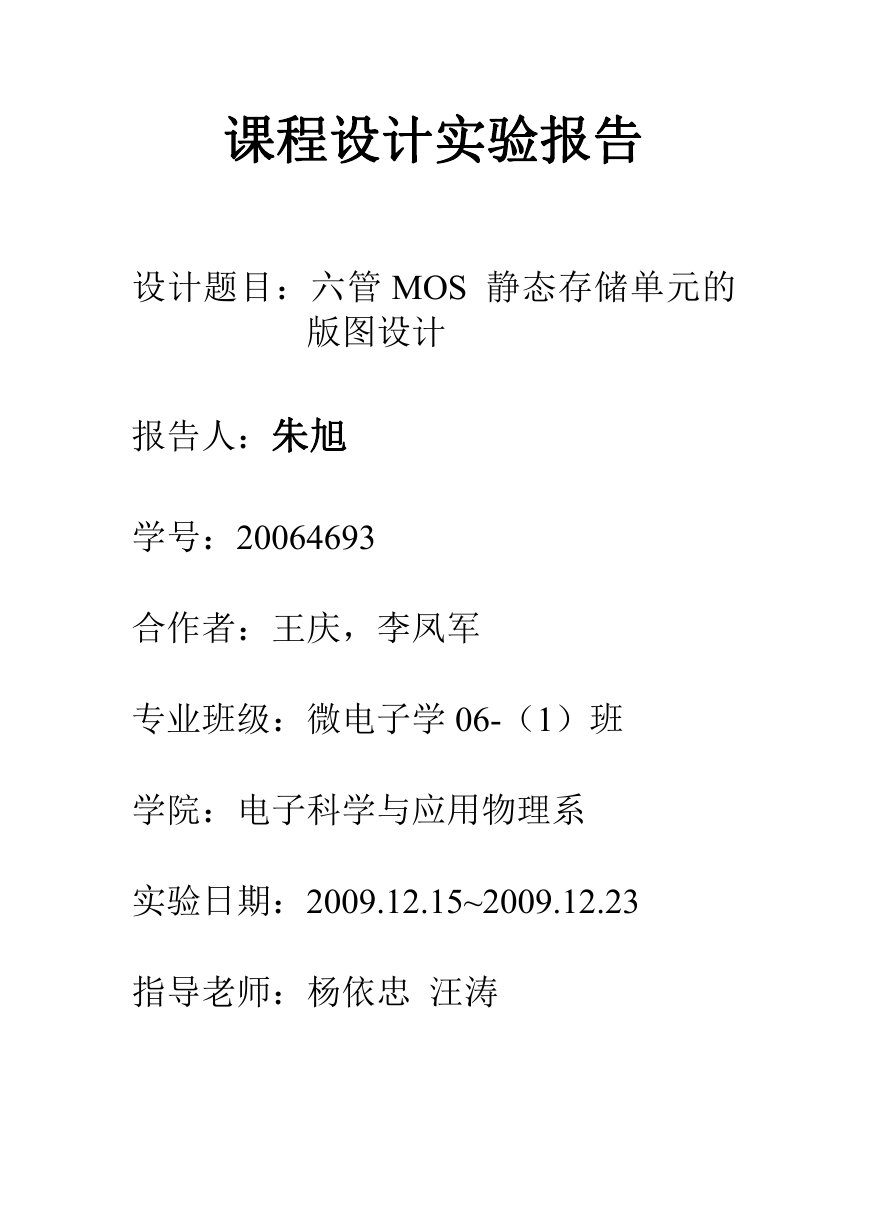

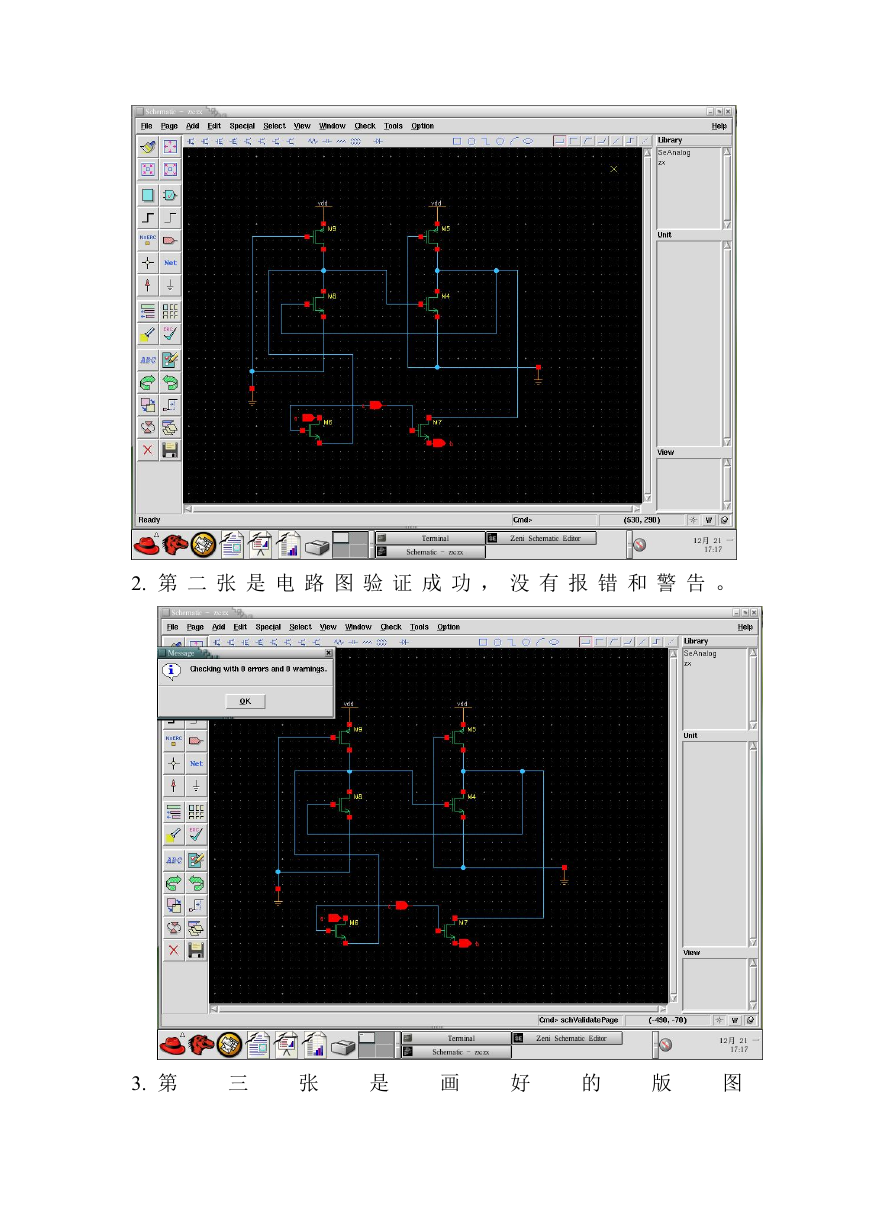

1. 第一张为画好的电路图。有六个 MOS 管连接而成的最小存储单

元

。

�

2. 第 二 张 是 电 路 图 验 证 成 功 , 没 有 报 错 和 警 告 。

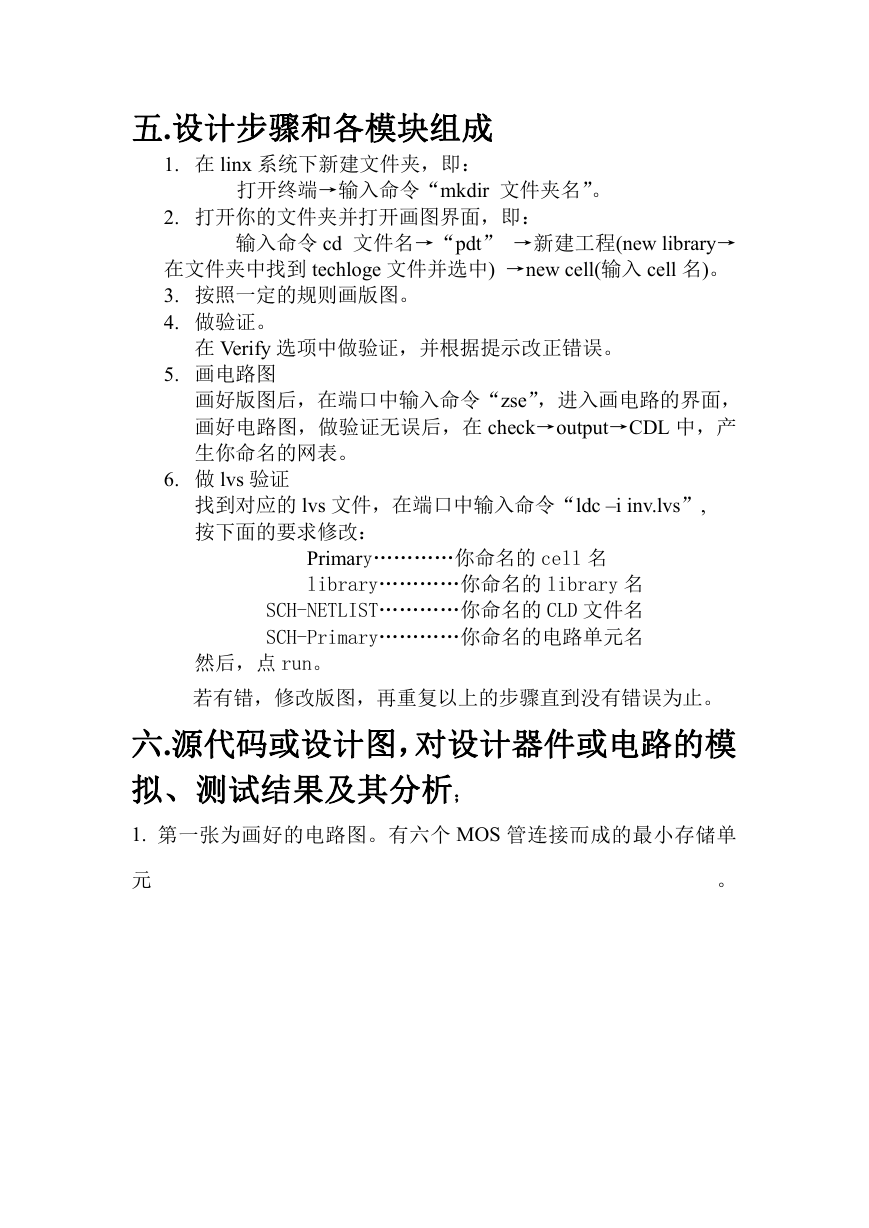

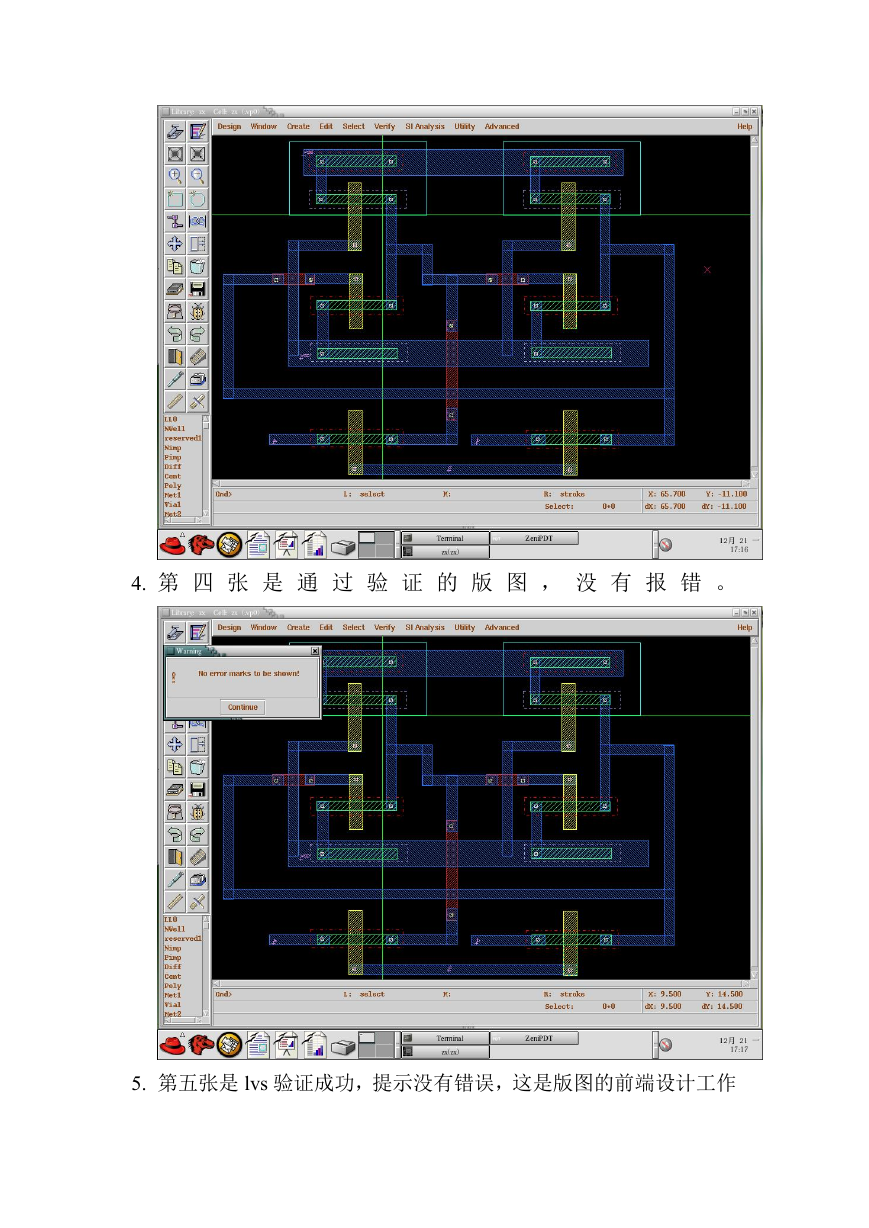

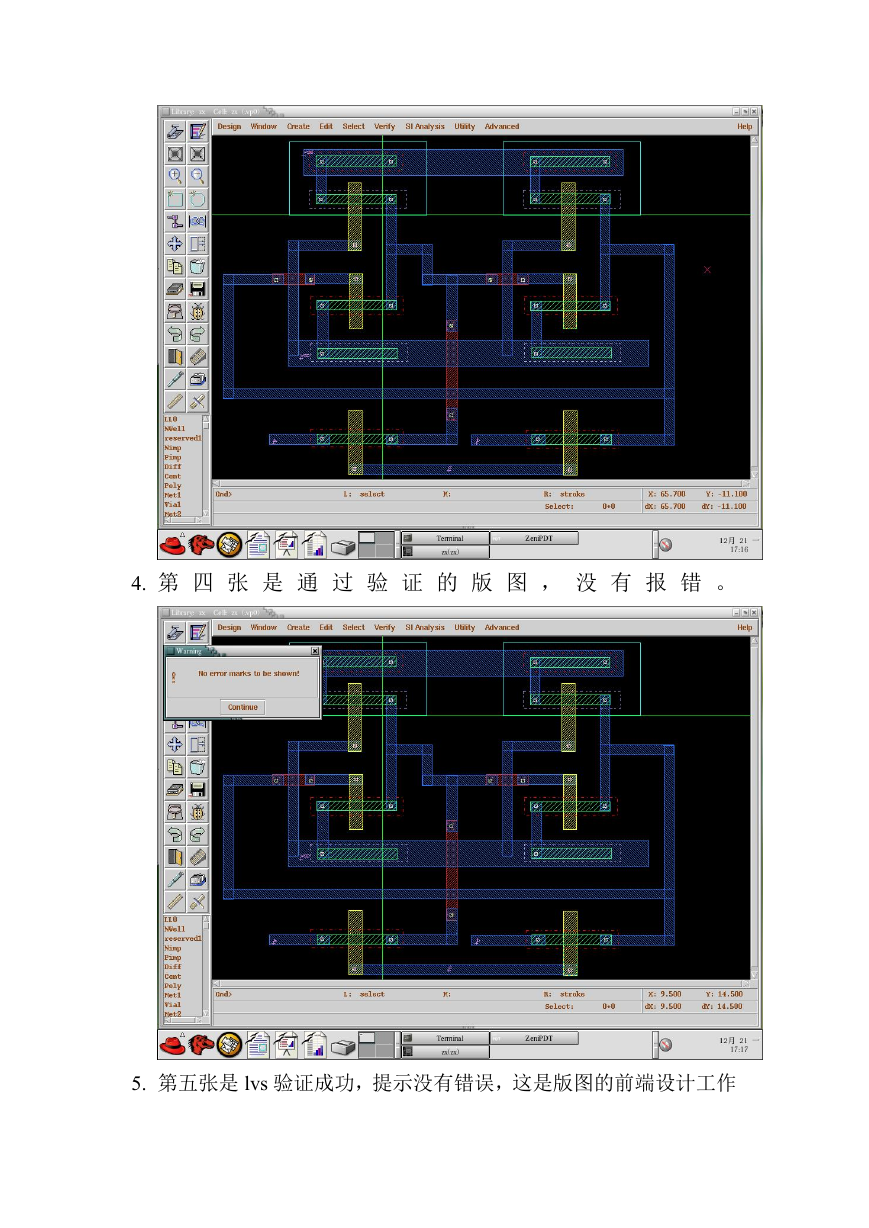

3. 第

三

张

是

画

好

的

版

图

�

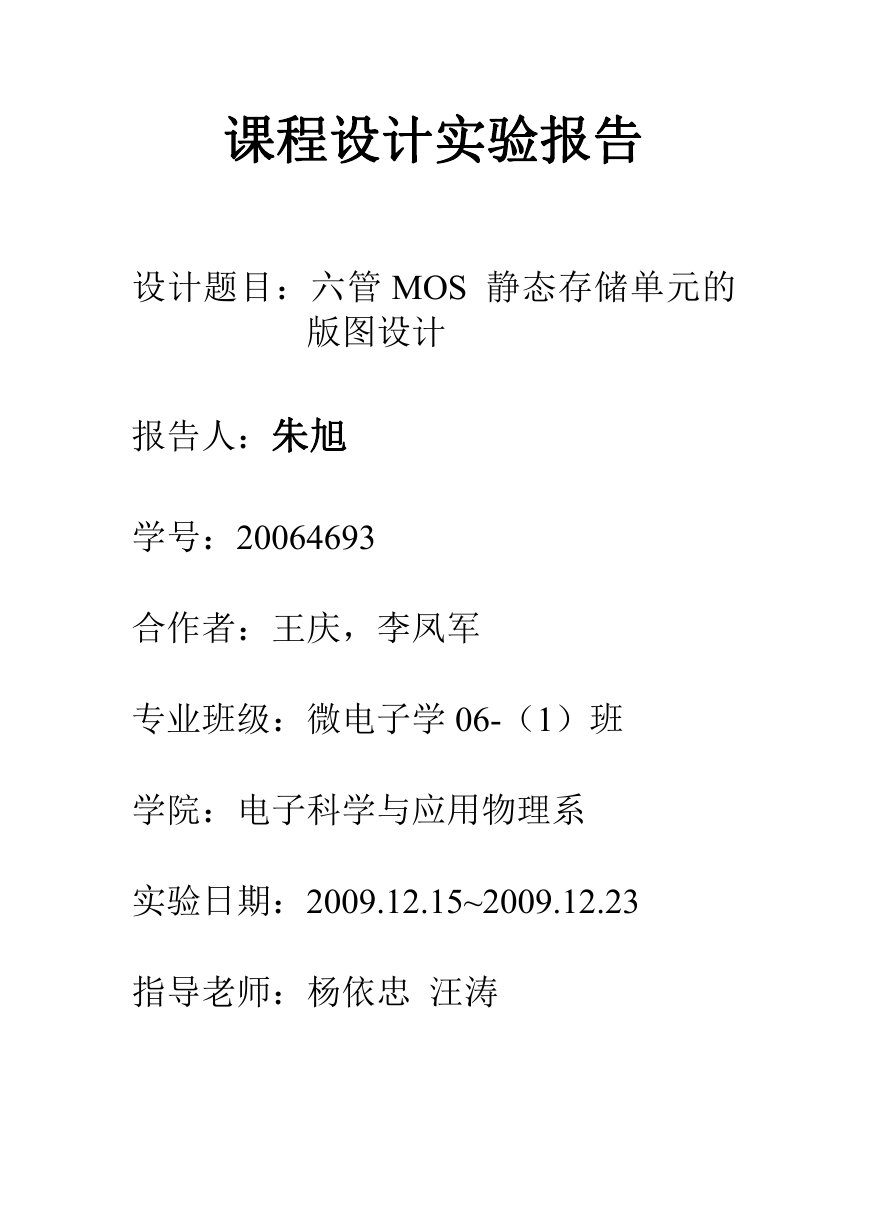

4. 第 四 张 是 通 过 验 证 的 版 图 , 没 有 报 错 。

5. 第五张是 lvs 验证成功,提示没有错误,这是版图的前端设计工作

�

基

本

完

成

。

LVS 验证相应的实验结果:

LVS 验证主要是针对于版图和电路的对比检查,发现其中的不

对应点,给予修正,使电路图和版图相互对应。在做 LVS 验证的过

程中应当将电路图生成的.cdl 网表文件和与 inv.lvs 文件放于同一个

文件下,同时修改 inv.lvs 文件中的内容,主要有四点:

1、 PRIMARY:应改为版图单元名,

2、 LIBRARY:应改为版图库名,;

3、 SCH-NETLIST:应改为网表文件名

4、 SCH-PRIMARY:应改为电路图单元名,,通过输入“vi shq.cdl”

可获得单元名;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc