Aptina Confidential and Proprietary

MT9V034: 1/3-Inch Wide-VGA Digital Image Sensor

Features

1/3-Inch Wide-VGA CMOS Digital Image Sensor

MT9V034

For the latest data sheet revision, refer to Aptina’s Web site: www.aptina.com

Features

• DigitalClarity® CMOS imaging technology

• Array format: Wide-VGA, active 752H x 480V

(360,960 pixels)

• TrueSNAP™ global shutter photodiode pixels;

simultaneous integration and readout

• Monochrome or color: NIR enhanced performance

for use with non-visible NIR illumination

• Readout modes: progressive or interlaced

• Shutter efficiency: >99%

• Simple two-wire serial interface

• Real-time exposure context switching - dual register

set

• Register lock capability

• Window size: User programmable to any smaller

format (QVGA, CIF, QCIF). Data rate can be

maintained independent of window size

• Binning: 2 x 2 and 4 x 4 of the full resolution

• ADC: On-chip, 10-bit column-parallel (option to

operate in 12-bit to 10-bit companding mode)

• Automatic controls: Auto exposure control (AEC)

and auto gain control (AGC); variable regional and

variable weight AEC/AGC

• Support for four unique serial control register IDs to

control multiple imagers on the same bus

• Data output formats:

– Single sensor mode:

10-bit parallel/stand-alone

8-bit or 10-bit serial LVDS

– Stereo sensor mode:

Interspersed 8-bit serial LVDS

• High dynamic range (HDR) mode

Applications

• Security

• High dynamic range imaging

• Unattended surveillance

• Stereo vision

• Video as input

• Machine vision

• Automation

Table 1:

Key Performance Parameters

Parameter

Optical format

Active imager size

Active pixels

Pixel size

Color filter array

Shutter type

Maximum data rate

master clock

Full resolution

Frame rate

ADC resolution

Responsivity

Dynamic range

Supply voltage

Power consumption

Value

1/3-inch

4.51mm(H) x 2.88mm(V)

5.35mm diagonal

752H x 480V

6.0 x 6.0µm

Monochrome or color RGB Bayer

pattern

TrueSNAP™�Global shutter

27 Mp/s

27 MHz

752 x 480

60 fps (at full resolution)

10-bit column-parallel

4.8 V/lux-sec (550nm)

>55dB linear;

>110dB in HDR mode

3.3V +0.3V�(all supplies)

<160mW at maximum data rate

(LVDS disabled); 120µW standby

power at 3.3V

–30°C to +70°C ambient

48-pin CLCC

Operating temperature

Packaging

Ordering Information

Table 2:

Available Part Numbers

Part Number

MT9V034C12STM

MT9V034C12STC

MT9V034C12STMD ES

MT9V034C12STMH ES

Number

of Pins

Description

CLCC (monochrome)

48-pin

48-pin

48-pin Monochrome demo kit

48-pin Monochrome head

CLCC (color)

MT9V034C12STCD ES

MT9V034C12STCH ES

48-pin

48-pin

board

Color demo kit

Color head board

PDF: 09005aef8366edcb/Source: 09005aef8366ede5

MT9V034_DS - Rev. A 10/08 EN

1

Aptina Imaging reserves the right to change products or specifications without notice.

©2008 Aptina Imaging Corporation All rights reserved.

Products and specifications discussed herein are subject to change by Aptina without notice.

�

Aptina Confidential and Proprietary

MT9V034: 1/3-Inch Wide-VGA Digital Image Sensor

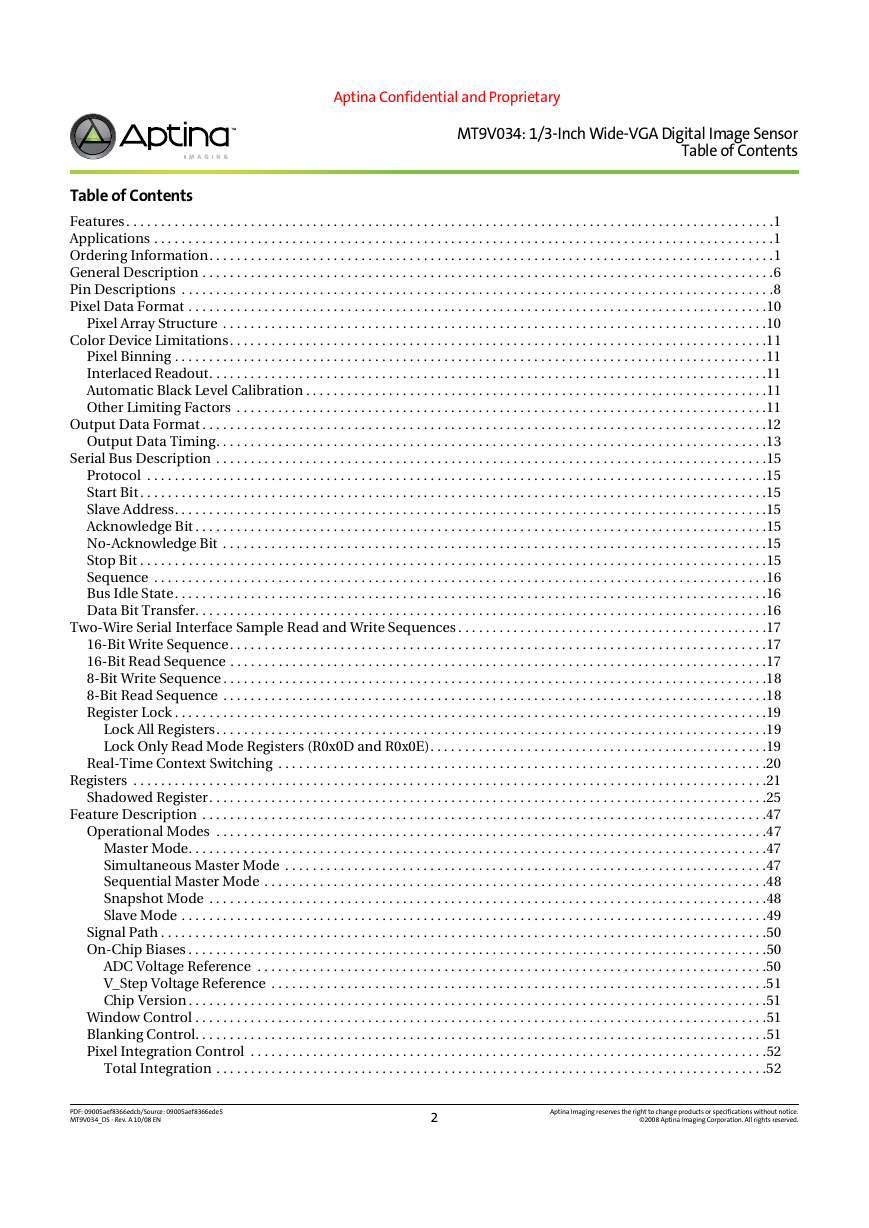

Table of Contents

Table of Contents

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Pixel Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Pixel Array Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Color Device Limitations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Pixel Binning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Interlaced Readout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Automatic Black Level Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Other Limiting Factors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Output Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Output Data Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Serial Bus Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Start Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Slave Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Acknowledge Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

No-Acknowledge Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Stop Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Bus Idle State. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Data Bit Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Two-Wire Serial Interface Sample Read and Write Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

16-Bit Write Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

16-Bit Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

8-Bit Write Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

8-Bit Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Register Lock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Lock All Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Lock Only Read Mode Registers (R0x0D and R0x0E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Real-Time Context Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Shadowed Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Feature Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Operational Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Master Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Simultaneous Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Sequential Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Snapshot Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Signal Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

On-Chip Biases . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

ADC Voltage Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

V_Step Voltage Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Chip Version . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Window Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Blanking Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Pixel Integration Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Total Integration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

PDF: 09005aef8366edcb/Source: 09005aef8366ede5

MT9V034_DS - Rev. A 10/08 EN

2

Aptina Imaging reserves the right to change products or specifications without notice.

©2008 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9V034: 1/3-Inch Wide-VGA Digital Image Sensor

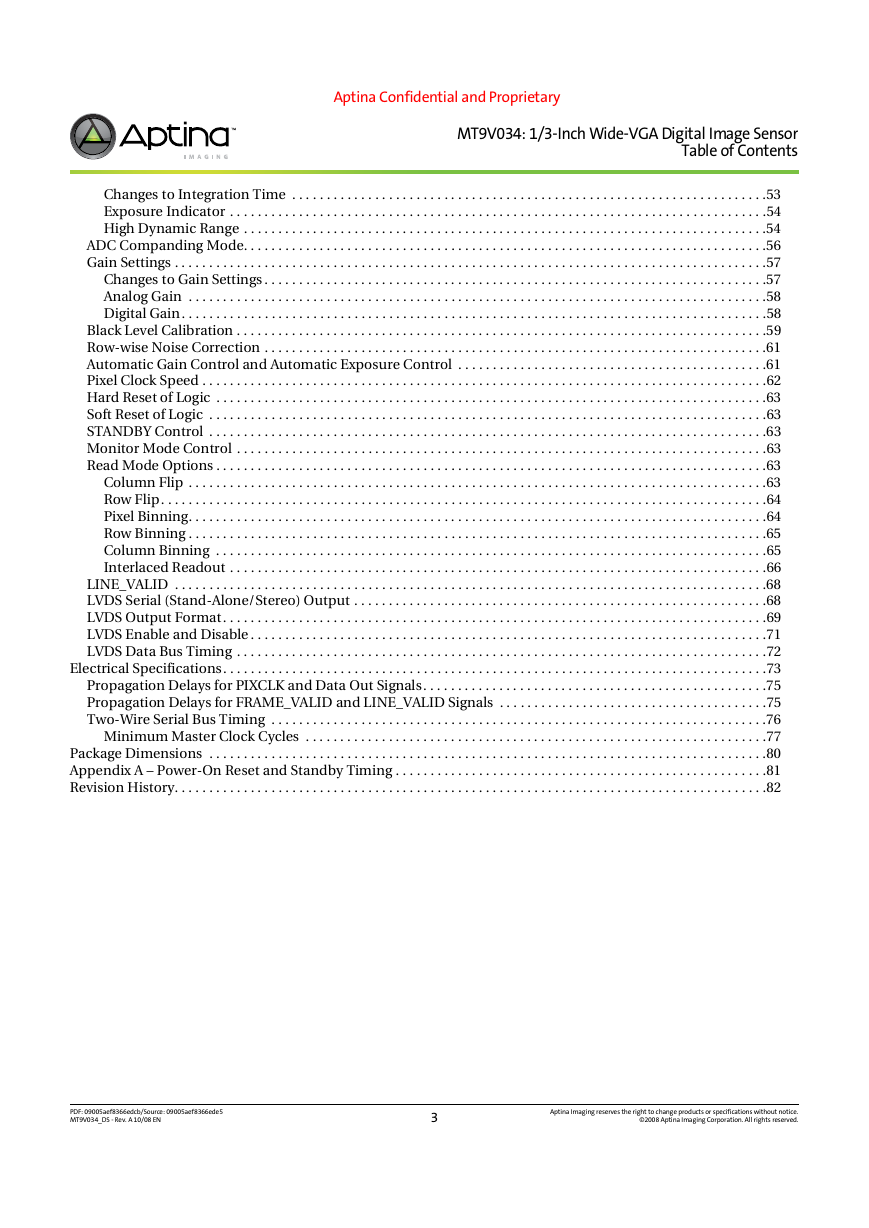

Table of Contents

Changes to Integration Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Exposure Indicator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

High Dynamic Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

ADC Companding Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Gain Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Changes to Gain Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Analog Gain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Digital Gain. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Black Level Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Row-wise Noise Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Automatic Gain Control and Automatic Exposure Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Pixel Clock Speed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Hard Reset of Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Soft Reset of Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

STANDBY Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Monitor Mode Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Read Mode Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Column Flip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Row Flip. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Pixel Binning. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Row Binning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Column Binning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Interlaced Readout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

LINE_VALID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

LVDS Serial (Stand-Alone/Stereo) Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

LVDS Output Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

LVDS Enable and Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

LVDS Data Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Propagation Delays for PIXCLK and Data Out Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Propagation Delays for FRAME_VALID and LINE_VALID Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Two-Wire Serial Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Minimum Master Clock Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

Appendix A – Power-On Reset and Standby Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

PDF: 09005aef8366edcb/Source: 09005aef8366ede5

MT9V034_DS - Rev. A 10/08 EN

3

Aptina Imaging reserves the right to change products or specifications without notice.

©2008 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9V034: 1/3-Inch Wide-VGA Digital Image Sensor

List of Figures

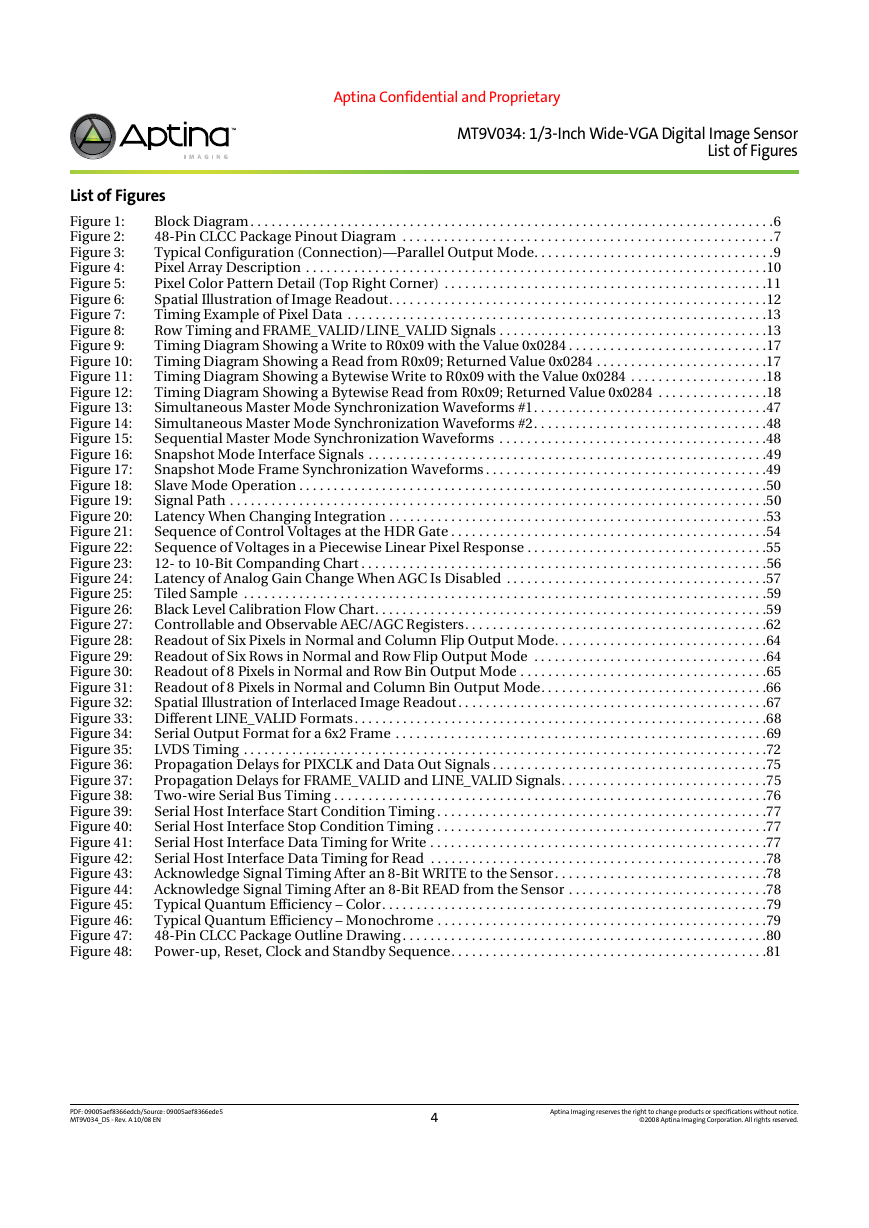

List of Figures

Figure 1:

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Figure 2:

48-Pin CLCC Package Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Figure 3:

Typical Configuration (Connection)—Parallel Output Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Figure 4:

Pixel Array Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Figure 5:

Pixel Color Pattern Detail (Top Right Corner) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Figure 6:

Spatial Illustration of Image Readout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Figure 7:

Timing Example of Pixel Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 8:

Row Timing and FRAME_VALID/LINE_VALID Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 9:

Timing Diagram Showing a Write to R0x09 with the Value 0x0284 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Figure 10:

Timing Diagram Showing a Read from R0x09; Returned Value 0x0284 . . . . . . . . . . . . . . . . . . . . . . . . .17

Figure 11:

Timing Diagram Showing a Bytewise Write to R0x09 with the Value 0x0284 . . . . . . . . . . . . . . . . . . . .18

Figure 12:

Timing Diagram Showing a Bytewise Read from R0x09; Returned Value 0x0284 . . . . . . . . . . . . . . . .18

Figure 13:

Simultaneous Master Mode Synchronization Waveforms #1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Figure 14:

Simultaneous Master Mode Synchronization Waveforms #2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Figure 15:

Sequential Master Mode Synchronization Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Figure 16:

Snapshot Mode Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Figure 17:

Snapshot Mode Frame Synchronization Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Figure 18:

Slave Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Figure 19:

Signal Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Figure 20:

Latency When Changing Integration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Figure 21:

Sequence of Control Voltages at the HDR Gate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Figure 22:

Sequence of Voltages in a Piecewise Linear Pixel Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Figure 23:

12- to 10-Bit Companding Chart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Figure 24:

Latency of Analog Gain Change When AGC Is Disabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Figure 25:

Tiled Sample . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Figure 26:

Black Level Calibration Flow Chart. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Figure 27:

Controllable and Observable AEC/AGC Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Figure 28:

Readout of Six Pixels in Normal and Column Flip Output Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Figure 29:

Readout of Six Rows in Normal and Row Flip Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Figure 30:

Readout of 8 Pixels in Normal and Row Bin Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Figure 31:

Readout of 8 Pixels in Normal and Column Bin Output Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

Figure 32:

Spatial Illustration of Interlaced Image Readout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Figure 33: Different LINE_VALID Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Serial Output Format for a 6x2 Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Figure 34:

LVDS Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Figure 35:

Propagation Delays for PIXCLK and Data Out Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Figure 36:

Figure 37:

Propagation Delays for FRAME_VALID and LINE_VALID Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Two-wire Serial Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Figure 38:

Serial Host Interface Start Condition Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Figure 39:

Serial Host Interface Stop Condition Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Figure 40:

Figure 41:

Serial Host Interface Data Timing for Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Serial Host Interface Data Timing for Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Figure 42:

Acknowledge Signal Timing After an 8-Bit WRITE to the Sensor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Figure 43:

Acknowledge Signal Timing After an 8-Bit READ from the Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Figure 44:

Typical Quantum Efficiency – Color. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Figure 45:

Figure 46:

Typical Quantum Efficiency – Monochrome . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

48-Pin CLCC Package Outline Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

Figure 47:

Figure 48:

Power-up, Reset, Clock and Standby Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

PDF: 09005aef8366edcb/Source: 09005aef8366ede5

MT9V034_DS - Rev. A 10/08 EN

4

Aptina Imaging reserves the right to change products or specifications without notice.

©2008 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9V034: 1/3-Inch Wide-VGA Digital Image Sensor

List of Tables

List of Tables

Table 1:

Table 2:

Table 3:

Table 4:

Table 5:

Table 6:

Table 7:

Table 8:

Table 9:

Table 10:

Table 11:

Table 12:

Table 13:

Table 14:

Table 15:

Table 16:

Table 17:

Table 18:

Table 19:

Table 20:

Key Performance Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Available Part Numbers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Frame Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Frame Time—Long Integration Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Slave Address Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Real-Time Context-Switchable Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Default Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

LVDS Packet Format in Stand-Alone Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

LVDS Packet Format in Stereoscopy Mode (Stereoscopy Mode Bit Asserted) . . . . . . . . . . . . . . . . . . .70

Reserved Words in the Pixel Data Stream . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

SER_DATAOUT_* state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

SHFT_CLK_* state. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

LVDS AC Timing Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

DC Electrical Characteristics Over Temperature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

AC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Two-Wire Serial Bus Timing Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

PDF: 09005aef8366edcb/Source: 09005aef8366ede5

MT9V034_DS - Rev. A 10/08 EN

5

Aptina Imaging reserves the right to change products or specifications without notice.

©2008 Aptina Imaging Corporation. All rights reserved.

�

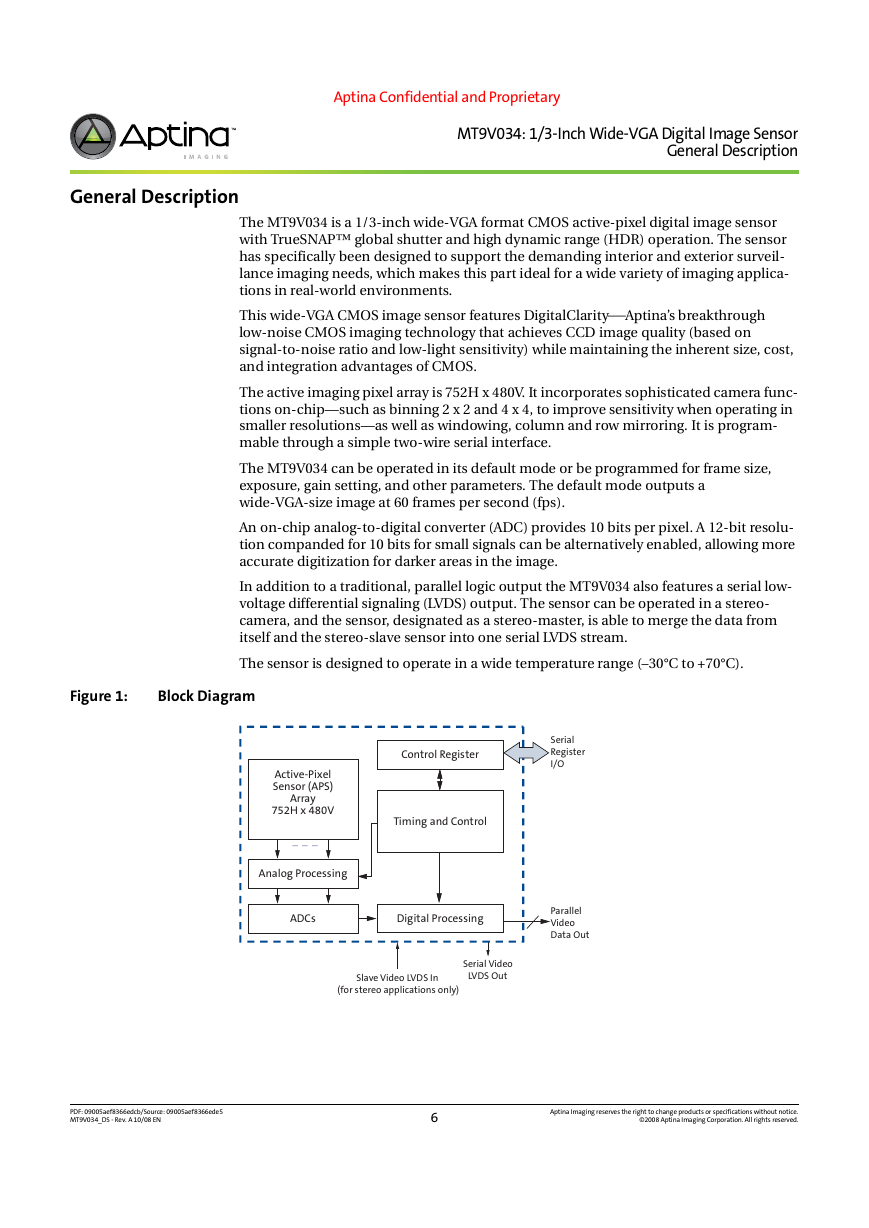

General Description

Aptina Confidential and Proprietary

MT9V034: 1/3-Inch Wide-VGA Digital Image Sensor

General Description

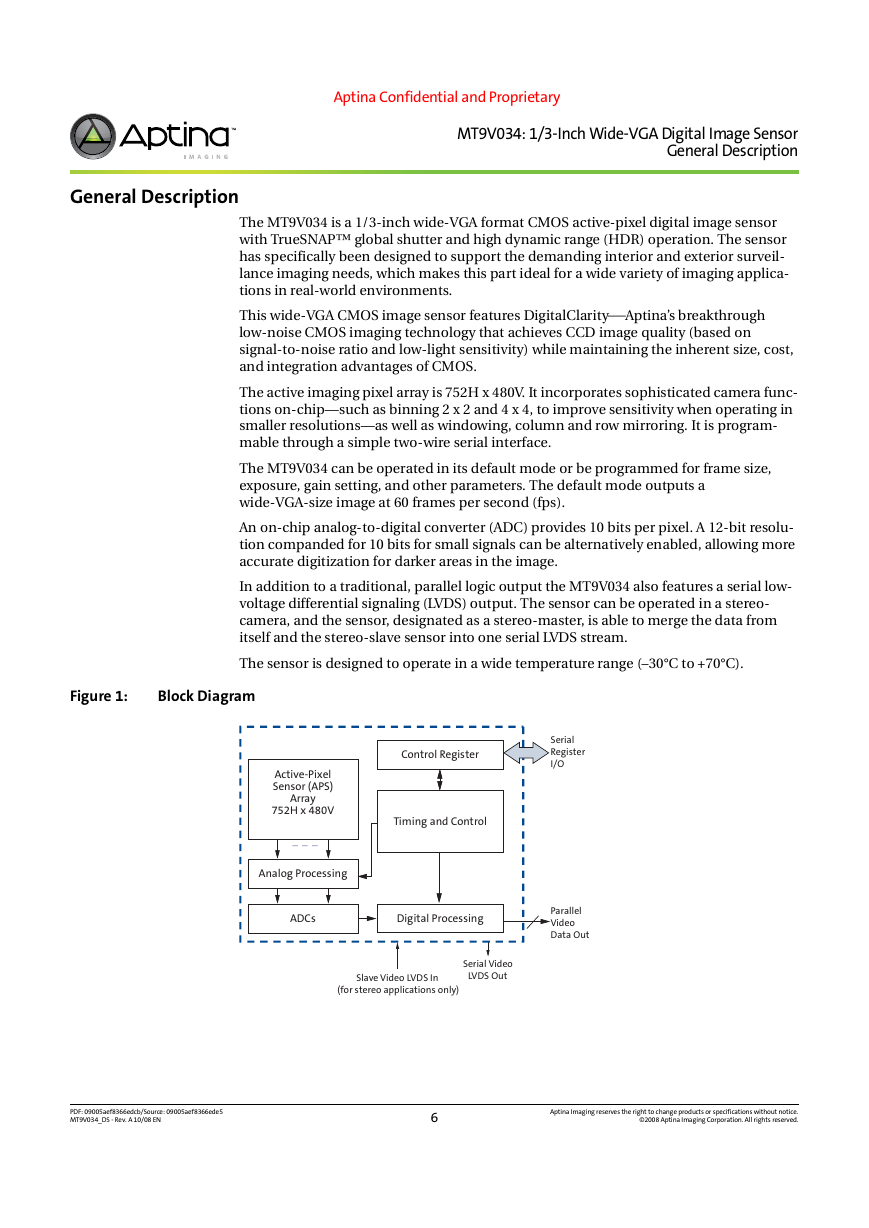

The MT9V034 is a 1/3-inch wide-VGA format CMOS active-pixel digital image sensor

with TrueSNAP™ global shutter and high dynamic range (HDR) operation. The sensor

has specifically been designed to support the demanding interior and exterior surveil-

lance imaging needs, which makes this part ideal for a wide variety of imaging applica-

tions in real-world environments.

This wide-VGA CMOS image sensor features DigitalClarity⎯Aptina’s breakthrough

low-noise CMOS imaging technology that achieves CCD image quality (based on

signal-to-noise ratio and low-light sensitivity) while maintaining the inherent size, cost,

and integration advantages of CMOS.

The active imaging pixel array is 752H x 480V. It incorporates sophisticated camera func-

tions on-chip—such as binning 2 x 2 and 4 x 4, to improve sensitivity when operating in

smaller resolutions—as well as windowing, column and row mirroring. It is program-

mable through a simple two-wire serial interface.

The MT9V034 can be operated in its default mode or be programmed for frame size,

exposure, gain setting, and other parameters. The default mode outputs a

wide-VGA-size image at 60 frames per second (fps).

An on-chip analog-to-digital converter (ADC) provides 10 bits per pixel. A 12-bit resolu-

tion companded for 10 bits for small signals can be alternatively enabled, allowing more

accurate digitization for darker areas in the image.

In addition to a traditional, parallel logic output the MT9V034 also features a serial low-

voltage differential signaling (LVDS) output. The sensor can be operated in a stereo-

camera, and the sensor, designated as a stereo-master, is able to merge the data from

itself and the stereo-slave sensor into one serial LVDS stream.

The sensor is designed to operate in a wide temperature range (–30°C to +70°C).

Figure 1:

Block Diagram

Active-Pixel

Sensor (APS)

Array

752H x 480V

Control Register

Serial

Register

I/O

Timing and Control

Analog Processing

ADCs

Digital Processing

Parallel

Video

Data Out

Slave Video LVDS In

(for stereo applications only)

Serial Video

LVDS Out

PDF: 09005aef8366edcb/Source: 09005aef8366ede5

MT9V034_DS - Rev. A 10/08 EN

6

Aptina Imaging reserves the right to change products or specifications without notice.

©2008 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9V034: 1/3-Inch Wide-VGA Digital Image Sensor

General Description

Figure 2:

48-Pin CLCC Package Pinout Diagram

N

_

T

U

O

A

T

A

D

_

R

E

S

P

_

T

U

O

A

T

A

D

_

R

E

S

P

_

T

U

O

K

L

C

_

T

F

H

S

N

_

T

U

O

K

L

C

_

T

F

H

S

S

D

V

L

D

D

V

D

N

G

D

D

D

V

K

L

C

S

Y

S

K

L

C

X

P

I

0

T

U

O

D

1

T

U

O

D

2

T

U

O

D

LVDSGND

BYPASS_CLKIN_N

BYPASS_CLKIN_P

SER_DATAIN_N

SER_DATAIN_P

LVDSGND

DGND

VDD

DOUT5

DOUT6

DOUT7

DOUT8

7

8

9

10

11

12

13

14

15

16

17

18

6

5

4

3

2

1

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

19

20

21

22

23

24

25

26

27

28

29

30

9

T

U

O

D

D

I

L

A

V

_

E

N

I

L

D

I

L

A

V

_

E

M

A

R

F

T

U

O

_

N

L

T

S

E

R

U

S

O

P

X

E

A

T

A

D

S

K

L

C

S

E

O

D

V

S

R

T

U

O

_

D

E

L

T

U

O

_

M

R

F

T

S

0

R

D

A

_

L

R

T

C

_

S

DOUT3

DOUT4

VAAPIX

VAA

AGND

NC

NC

VAA

AGND

STANDBY

RESET_BAR

S_CTRL_ADR1

PDF: 09005aef8366edcb/Source: 09005aef8366ede5

MT9V034_DS - Rev. A 10/08 EN

7

Aptina Imaging reserves the right to change products or specifications without notice.

©2008 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9V034: 1/3-Inch Wide-VGA Digital Image Sensor

Pin Descriptions

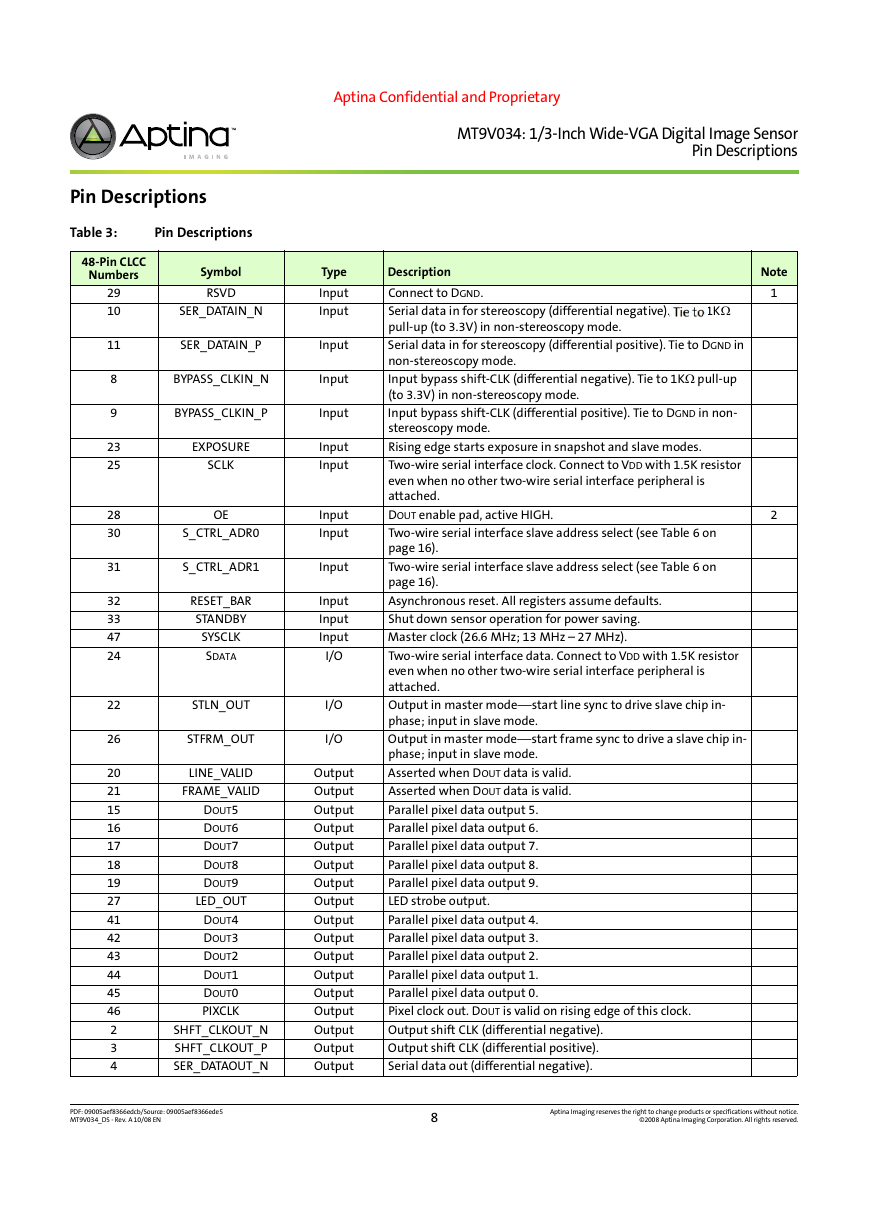

Pin Descriptions

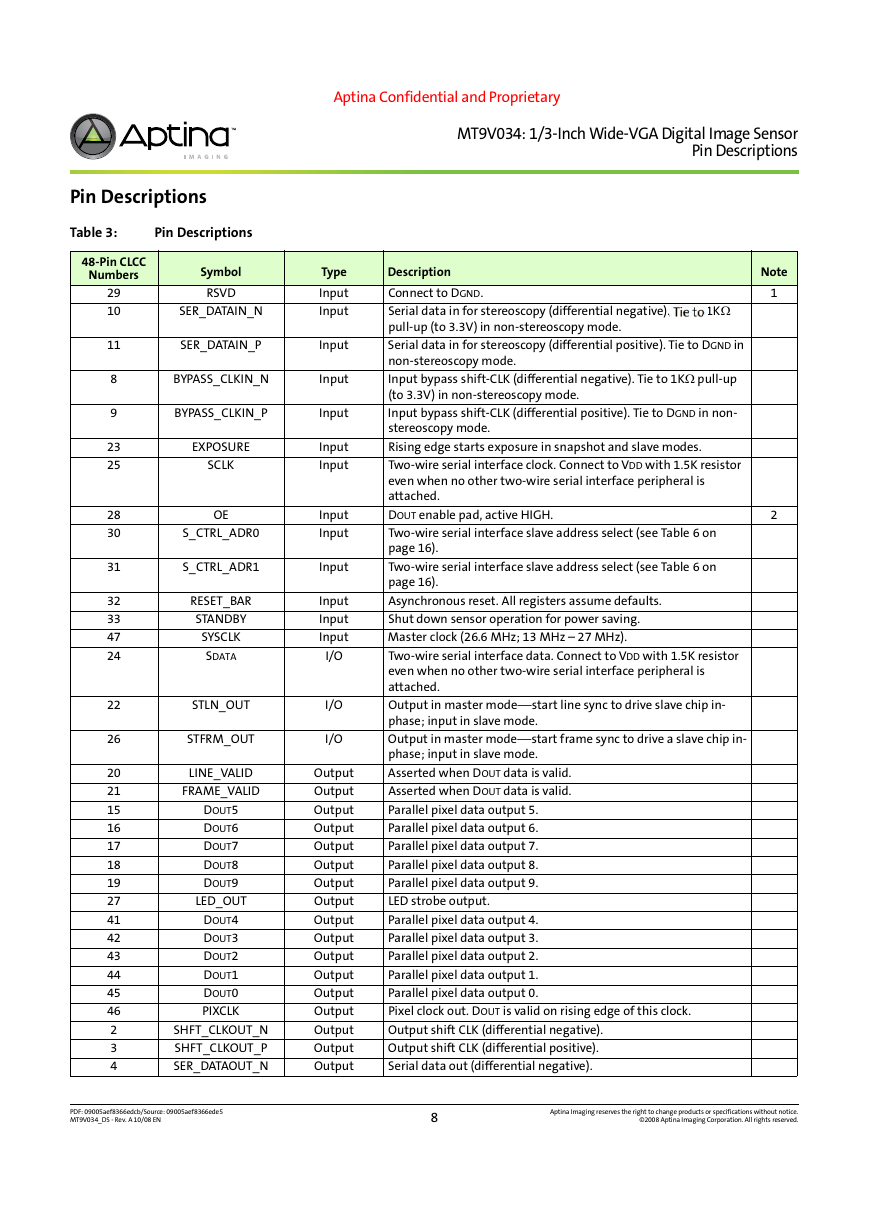

Table 3:

Pin Descriptions

48-Pin CLCC

Numbers

29

10

11

8

9

23

25

28

30

31

32

33

47

24

22

26

20

21

15

16

17

18

19

27

41

42

43

44

45

46

2

3

4

Symbol

RSVD

SER_DATAIN_N

SER_DATAIN_P

BYPASS_CLKIN_N

BYPASS_CLKIN_P

EXPOSURE

SCLK

OE

S_CTRL_ADR0

S_CTRL_ADR1

RESET_BAR

STANDBY

SYSCLK

SDATA

STLN_OUT

STFRM_OUT

LINE_VALID

FRAME_VALID

DOUT5

DOUT6

DOUT7

DOUT8

DOUT9

LED_OUT

DOUT4

DOUT3

DOUT2

DOUT1

DOUT0

PIXCLK

SHFT_CLKOUT_N

SHFT_CLKOUT_P

SER_DATAOUT_N

Type

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

I/O

I/O

I/O

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Note

1

2

Description

Connect to DGND.

Serial data in for stereoscopy (differential negative). Tie to 1KΩ

pull-up (to 3.3V) in non-stereoscopy mode.

Serial data in for stereoscopy (differential positive). Tie to DGND in

non-stereoscopy mode.

Input bypass shift-CLK (differential negative). Tie to 1KΩ pull-up

(to 3.3V) in non-stereoscopy mode.

Input bypass shift-CLK (differential positive). Tie to DGND in non-

stereoscopy mode.

Rising edge starts exposure in snapshot and slave modes.

Two-wire serial interface clock. Connect to VDD with 1.5K resistor

even when no other two-wire serial interface peripheral is

attached.

DOUT enable pad, active HIGH.

Two-wire serial interface slave address select (see Table 6 on

page 16).

Two-wire serial interface slave address select (see Table 6 on

page 16).

Asynchronous reset. All registers assume defaults.

Shut down sensor operation for power saving.

Master clock (26.6 MHz; 13 MHz – 27 MHz).

Two-wire serial interface data. Connect to VDD with 1.5K resistor

even when no other two-wire serial interface peripheral is

attached.

Output in master mode—start line sync to drive slave chip in-

phase; input in slave mode.

Output in master mode—start frame sync to drive a slave chip in-

phase; input in slave mode.

Asserted when DOUT data is valid.

Asserted when DOUT data is valid.

Parallel pixel data output 5.

Parallel pixel data output 6.

Parallel pixel data output 7.

Parallel pixel data output 8.

Parallel pixel data output 9.

LED strobe output.

Parallel pixel data output 4.

Parallel pixel data output 3.

Parallel pixel data output 2.

Parallel pixel data output 1.

Parallel pixel data output 0.

Pixel clock out. DOUT is valid on rising edge of this clock.

Output shift CLK (differential negative).

Output shift CLK (differential positive).

Serial data out (differential negative).

PDF: 09005aef8366edcb/Source: 09005aef8366ede5

MT9V034_DS - Rev. A 10/08 EN

8

Aptina Imaging reserves the right to change products or specifications without notice.

©2008 Aptina Imaging Corporation. All rights reserved.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc