Cortex™-M0+

Revision: r0p1

Technical Reference Manual

Copyright © 2012 ARM. All rights reserved.

ARM DDI 0484C (ID011713)

�

Cortex-M0+

Technical Reference Manual

Copyright © 2012 ARM. All rights reserved.

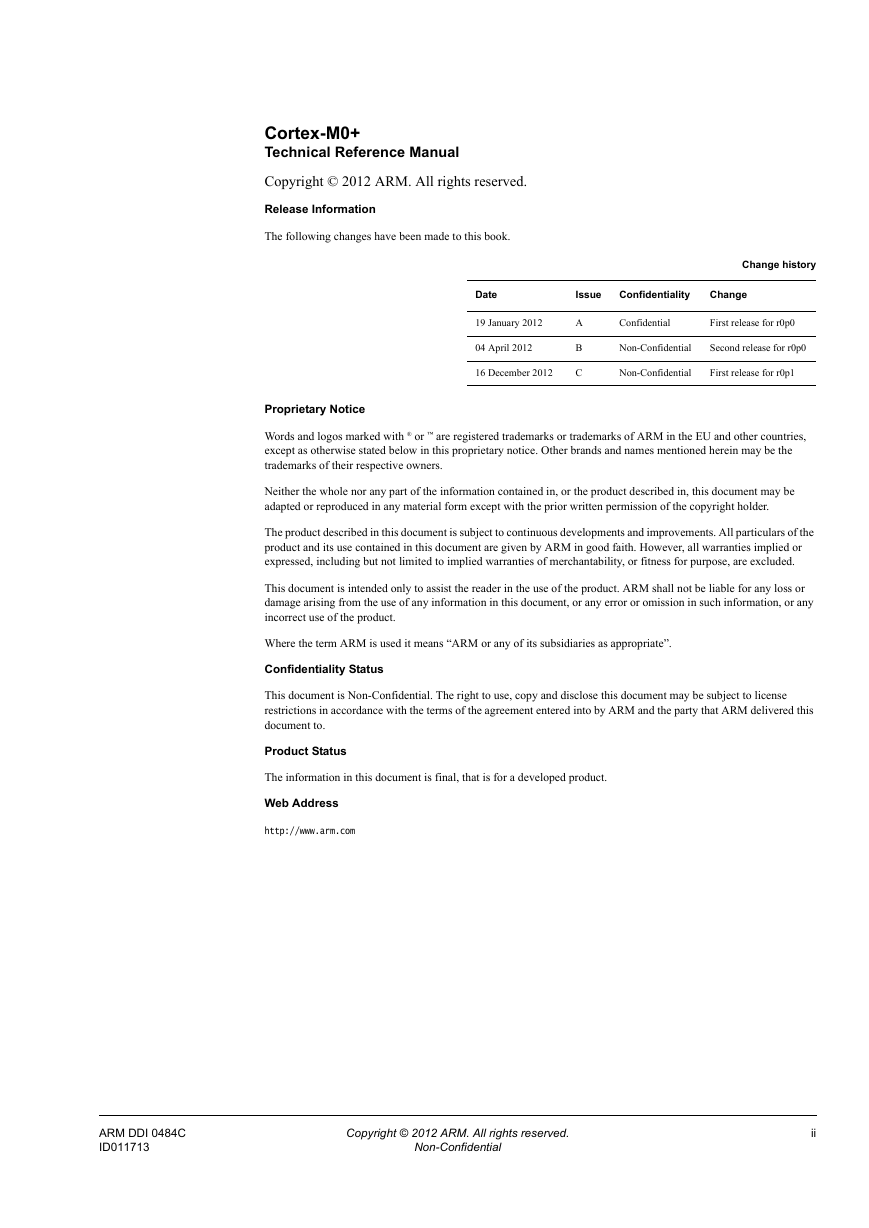

Release Information

The following changes have been made to this book.

Change history

Date

Issue

Confidentiality

Change

19 January 2012

04 April 2012

16 December 2012

A

B

C

Confidential

First release for r0p0

Non-Confidential

Second release for r0p0

Non-Confidential

First release for r0p1

Proprietary Notice

Words and logos marked with ® or ™ are registered trademarks or trademarks of ARM in the EU and other countries,

except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the

trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be

adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the

product and its use contained in this document are given by ARM in good faith. However, all warranties implied or

expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or

damage arising from the use of any information in this document, or any error or omission in such information, or any

incorrect use of the product.

Where the term ARM is used it means “ARM or any of its subsidiaries as appropriate”.

Confidentiality Status

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license

restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this

document to.

Product Status

The information in this document is final, that is for a developed product.

Web Address

http://www.arm.com

ARM DDI 0484C

ID011713

Copyright © 2012 ARM. All rights reserved.

Non-Confidential

ii

�

Contents

Cortex-M0+ Technical Reference Manual

Chapter 1

Chapter 2

Chapter 3

Preface

About this book ........................................................................................................... vi

Feedback .................................................................................................................... ix

Introduction

1.1

1.2

1.3

1.4

1.5

1.6

About the processor ................................................................................................. 1-2

Features ................................................................................................................... 1-3

Interfaces ................................................................................................................. 1-4

Configurable options ................................................................................................ 1-5

Product documentation, design flow and architecture ............................................. 1-6

Product revisions ..................................................................................................... 1-9

Functional Description

2.1

2.2

About the functions .................................................................................................. 2-2

Interfaces ................................................................................................................. 2-4

Programmers Model

3.1

3.2

3.3

3.4

3.5

3.6

About the programmers model ................................................................................ 3-2

Modes of operation and execution ........................................................................... 3-3

Instruction set summary ........................................................................................... 3-4

Memory model ......................................................................................................... 3-8

Processor core registers summary .......................................................................... 3-9

Exceptions ............................................................................................................. 3-10

Chapter 4

System Control

4.1

4.2

About system control ............................................................................................... 4-2

System control register summary ............................................................................ 4-3

ARM DDI 0484C

ID011713

Copyright © 2012 ARM. All rights reserved.

Non-Confidential

iii

�

Contents

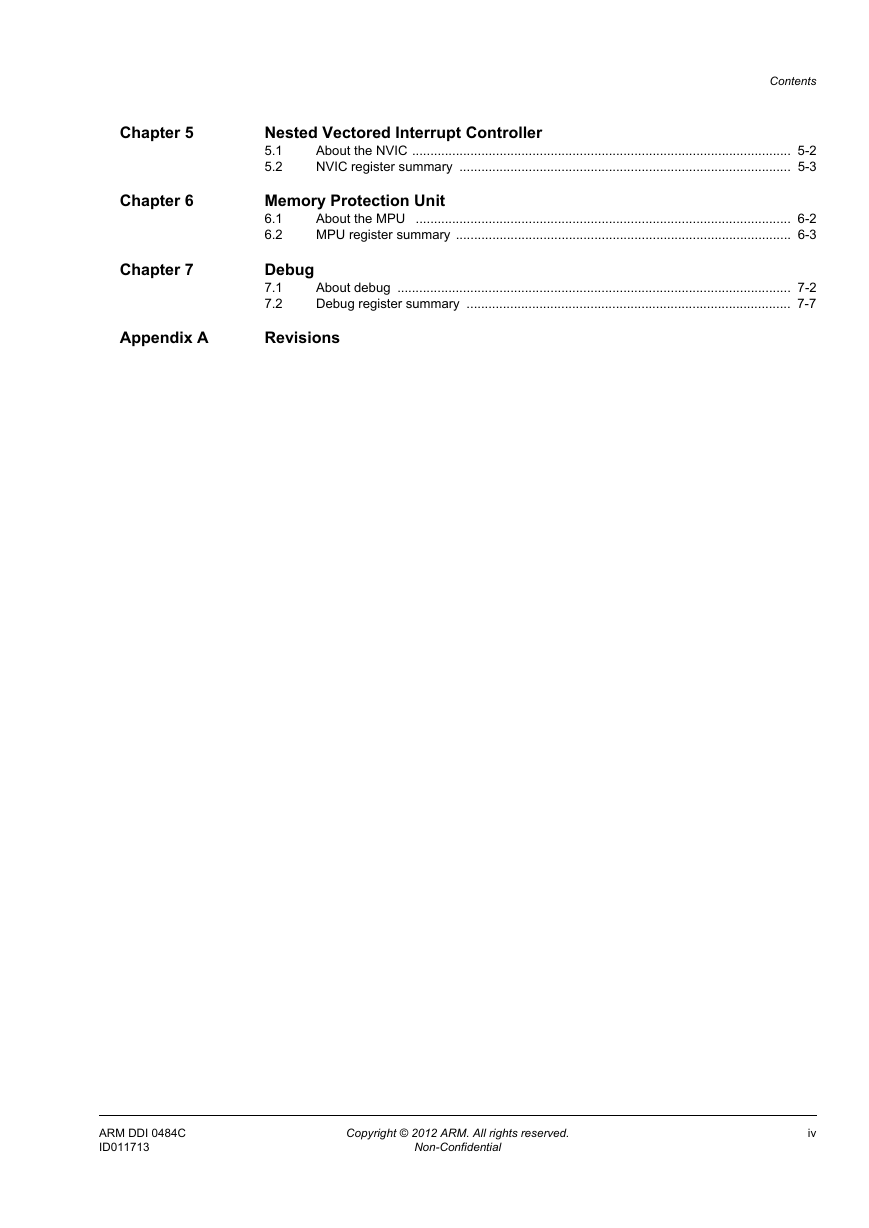

Chapter 5

Chapter 6

Chapter 7

Nested Vectored Interrupt Controller

5.1

5.2

About the NVIC ........................................................................................................ 5-2

NVIC register summary ........................................................................................... 5-3

Memory Protection Unit

6.1

6.2

About the MPU ....................................................................................................... 6-2

MPU register summary ............................................................................................ 6-3

Debug

7.1

7.2

About debug ............................................................................................................ 7-2

Debug register summary ......................................................................................... 7-7

Appendix A

Revisions

ARM DDI 0484C

ID011713

Copyright © 2012 ARM. All rights reserved.

Non-Confidential

iv

�

Preface

This preface introduces the Cortex-M0+ Technical Reference Manual. It contains the following

sections:

•

•

About this book on page vi

Feedback on page ix.

ARM DDI 0484C

ID011713

Copyright © 2012 ARM. All rights reserved.

Non-Confidential

v

�

About this book

Product revision status

Intended audience

Using this book

Glossary

Preface

This book is for the Cortex-M0+ processor.

The rnpn identifier indicates the revision status of the product described in this book, where:

rn

pn

Identifies the major revision of the product.

Identifies the minor revision or modification status of the product.

This book is written for:

•

•

system designers, system integrators, and verification engineers

software developers who want to use the processor.

This book is organized into the following chapters:

Chapter 1 Introduction

Read this chapter for an introduction to the processor and its features.

Chapter 2 Functional Description

Read this chapter for a functional overview of the processor functions.

Chapter 3 Programmers Model

Read this chapter for an overview of the application-level programmers model.

Chapter 4 System Control

Read this chapter for a summary of the system control registers and their

structure.

Chapter 5 Nested Vectored Interrupt Controller

Read this chapter for a summary of the Nested Vectored Interrupt Controller

(NVIC).

Chapter 6 Memory Protection Unit

Read this chapter for a description of the Memory Protection Unit (MPU).

Chapter 7 Debug

Read this chapter for a summary of the debug system.

Appendix A Revisions

Read this for a description of the technical changes between released issues of this

book.

The ARM Glossary is a list of terms used in ARM documentation, together with definitions for

those terms. The ARM Glossary does not contain terms that are industry standard unless the

ARM meaning differs from the generally accepted meaning.

See ARM Glossary, http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

ARM DDI 0484C

ID011713

Copyright © 2012 ARM. All rights reserved.

Non-Confidential

vi

�

Preface

Conventions

This book uses the conventions that are described in:

•

Typographical conventions.

Typographical conventions

The following table describes the typographical conventions:

Style

italic

bold

monospace

monospace

Purpose

Introduces special terminology, denotes cross-references, and citations.

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive

lists, where appropriate.

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full

command or option name.

monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

monospace bold

Denotes language keywords when used outside example code.

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

MRC p15, 0 , , ,

SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the ARM glossary.

For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

Additional reading

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

ARM publications

This book contains information that is specific to this product. See the following documents for

other relevant information:

•

•

•

•

ARMv6-M Architecture Reference Manual (ARM DDI 0419).

ARMv6-M Instruction Set Quick Reference Guide (ARM QRC 0011).

ARM AMBA® 3 AHB-Lite Protocol Specification (ARM IHI 0033).

ARM Debug Interface v5, Architecture Specification (ARM IHI 0031).

Note

•

•

•

•

A Cortex-M0+ implementation can include a Debug Access Port (DAP). This DAP is

defined in v5.1 of the ARM Debug interface specification, or in the errata document to

Issue A of the ARM Debug Interface v5 Architecture Specification.

Application Binary Interface for the ARM Architecture (The Base Standard) (IHI 0036).

CoreSight™ SoC Technical Reference Manual (ARM DDI 0480).

Cortex-M0+ Integration and Implementation Manual (ARM DII 0278).

CoreSight MTB-M0+ Technical Reference Manual (ARM DDI 0486).

ARM DDI 0484C

ID011713

Copyright © 2012 ARM. All rights reserved.

Non-Confidential

vii

�Other publications

This section lists relevant documents published by third parties:

•

IEEE Standard, Test Access Port and Boundary-Scan Architecture specification

1149.1-1990 (JTAG).

Preface

ARM DDI 0484C

ID011713

Copyright © 2012 ARM. All rights reserved.

Non-Confidential

viii

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc