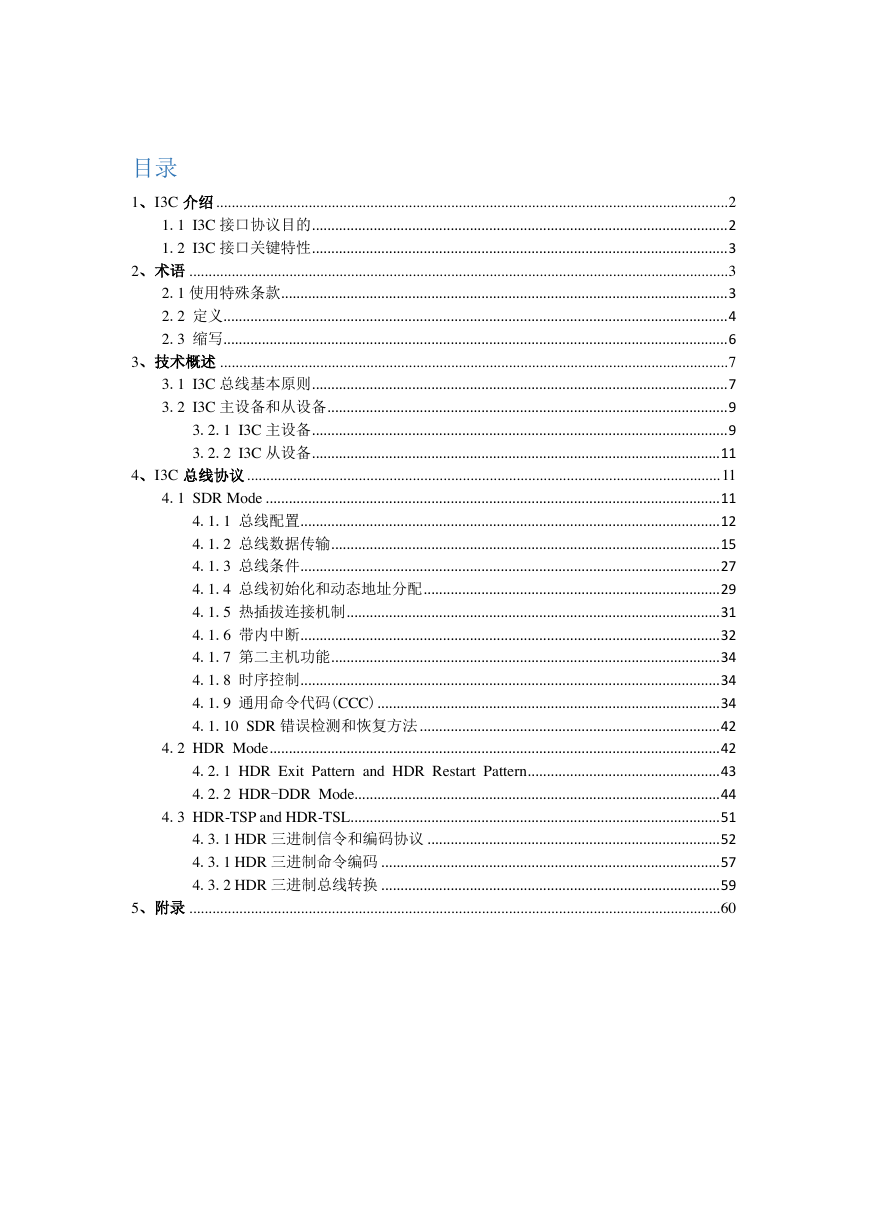

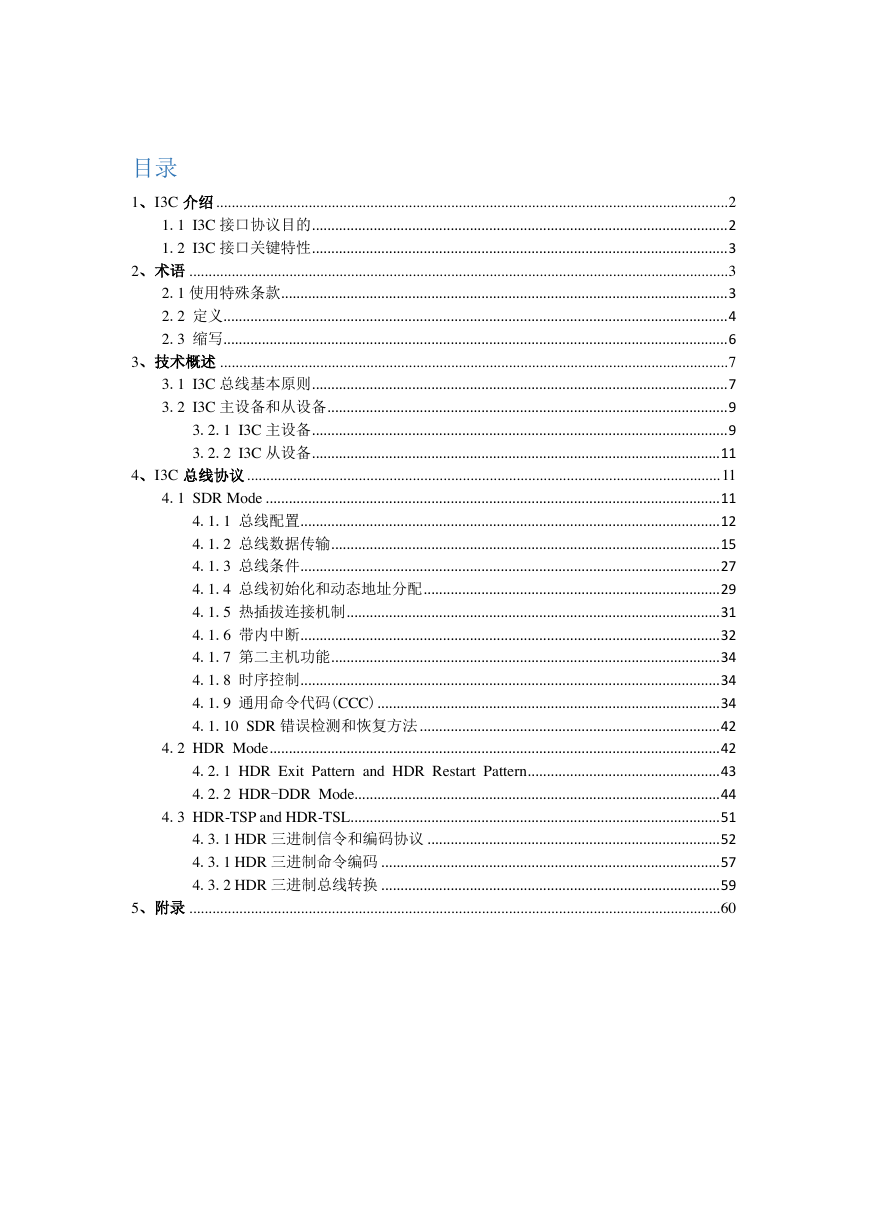

1、I3C介绍

1.1 I3C接口协议目的

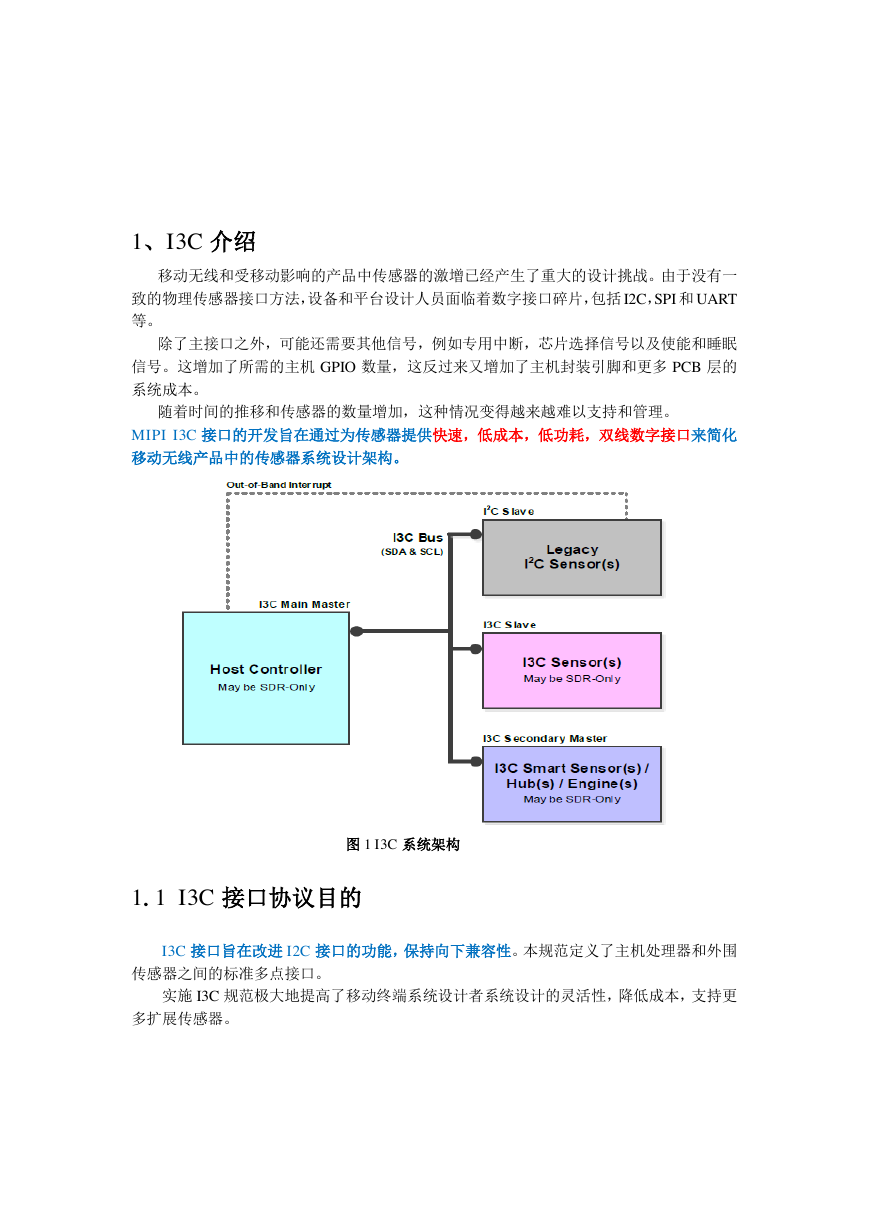

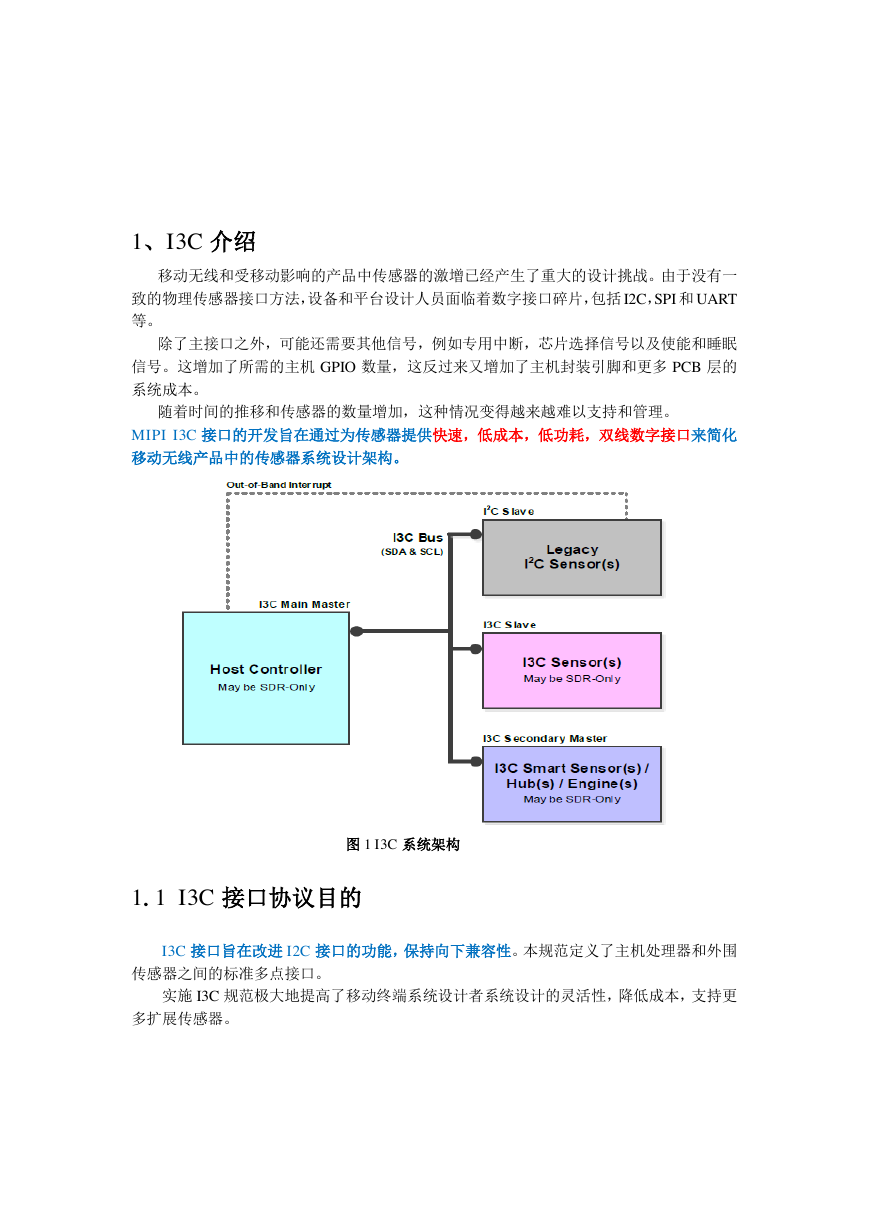

1.2 I3C接口关键特性

2、术语

2.1使用特殊条款

2.2 定义

2.3 缩写

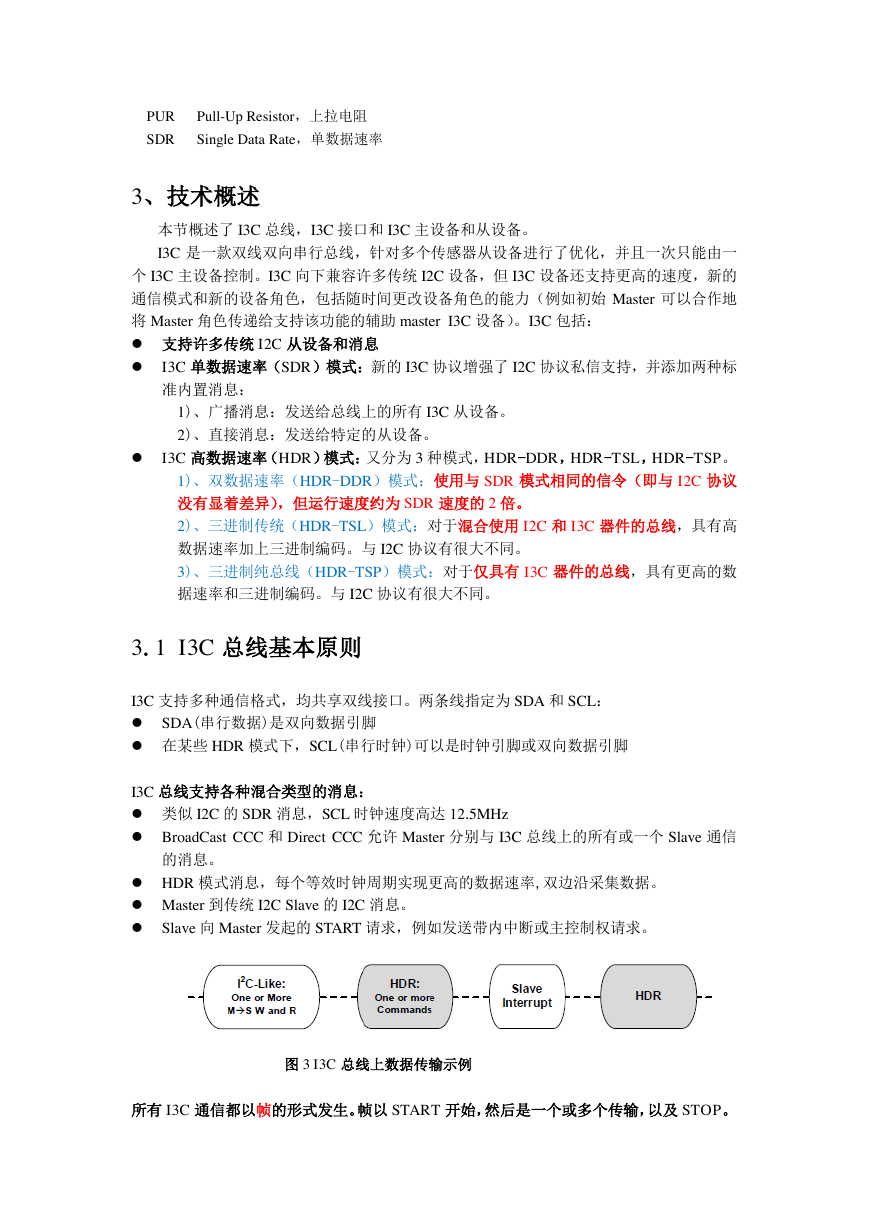

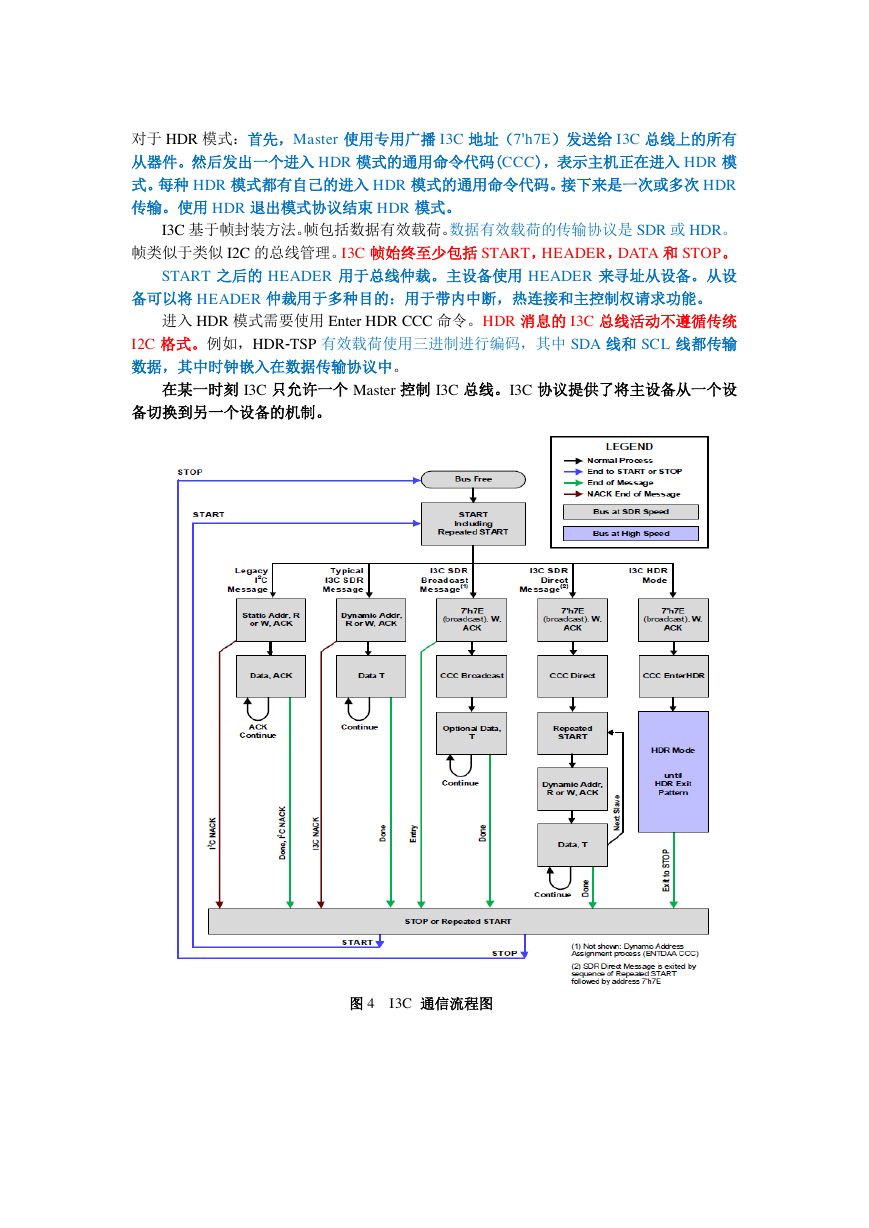

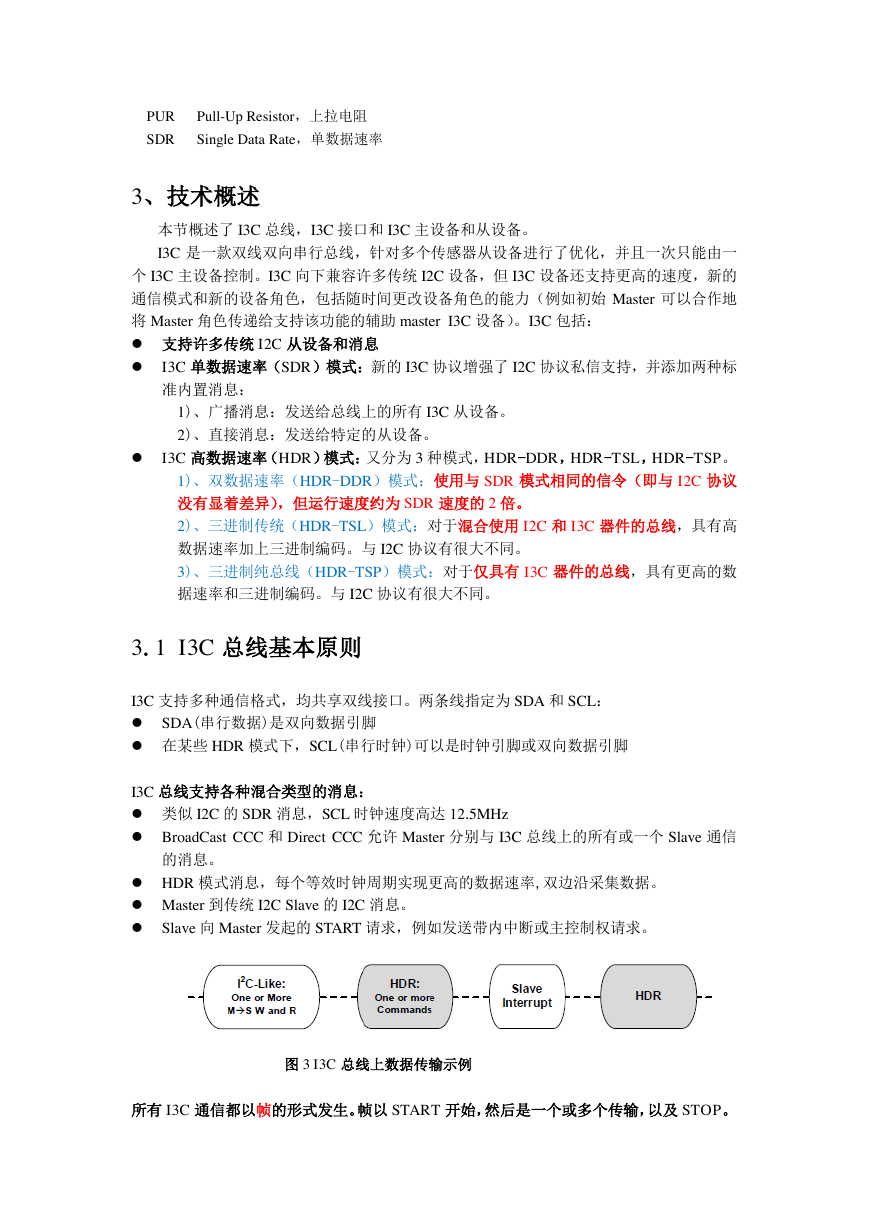

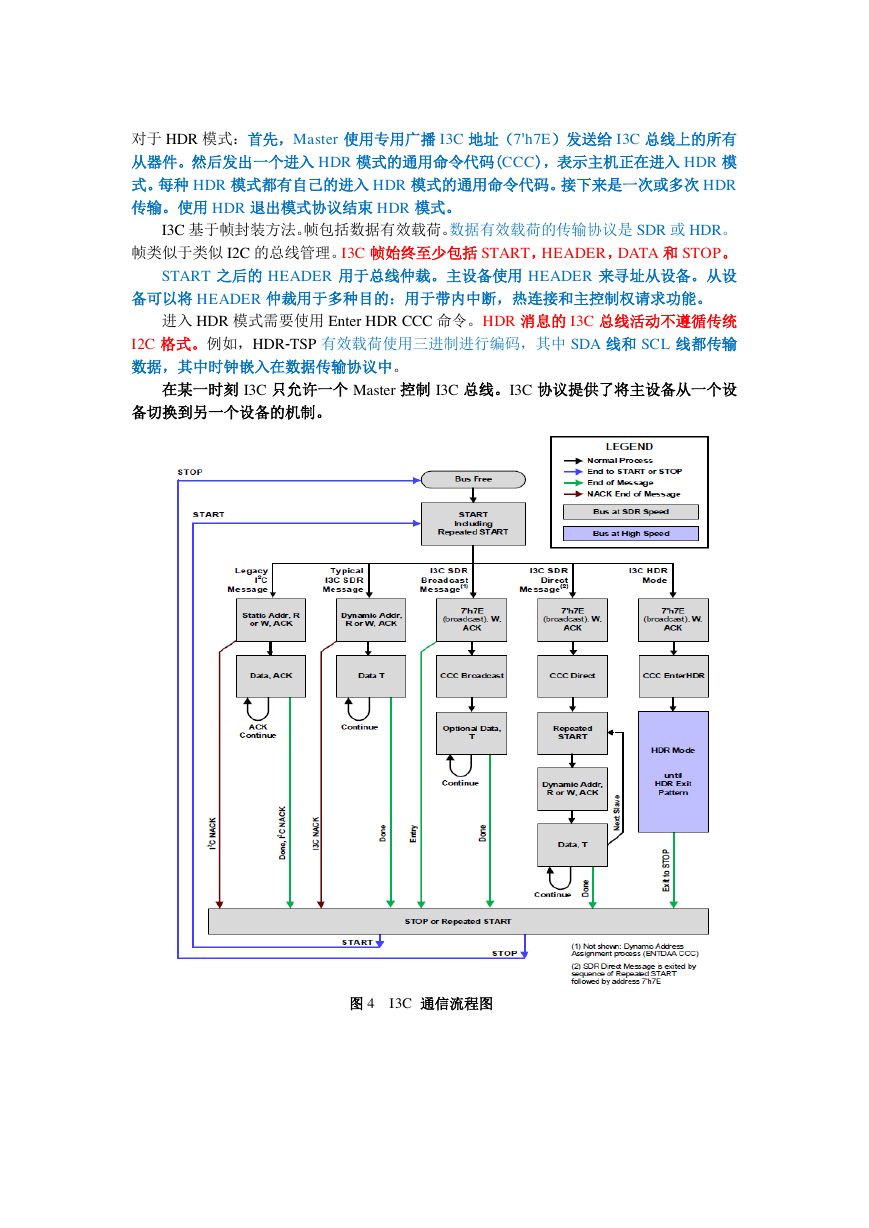

3、技术概述

3.1 I3C总线基本原则

3.2 I3C主设备和从设备

3.2.1 I3C主设备

3.2.1.1 I3C主机设备角色

3.2.2 I3C从设备

3.2.2.1 I3C从设备角色

4、I3C总线协议

4.1 SDR Mode

4.1.1 总线配置

4.1.1.1 I3C设备特性

4.1.1.2 I3C特性寄存器

4.1.1.2.1 总线特性寄存器(BCR)

4.1.1.2.3 传统虚拟寄存器(LVR)

4.1.2 总线数据传输

4.1.2.1 I3C从器件角色

4.1.2.2 I3C协议地址头

4.1.2.2.1 I3C地址仲裁

4.1.2.2.2 I3C地址仲裁优化

4.1.2.2.3 Master使用I3C从机地址启动帧的后果

4.1.2.2.4重复START后的地址头是推挽式

4.1.2.2.5 I3C从机地址限制

4.1.2.3 I3C SDR数据字

5.1.2.3.1 从地址ACK到SDR主机开始写数据切换

4.1.2.3.2 主机写数据字的第九位作为奇偶校验位

4.1.2.3.3 从机返回SDR数据的第九位作为结束位

4.1.2.4 使用时钟速度防止传统I2C器件看到I3C传输

4.1.2.5 主时钟延迟

4.1.2.5.1 I3C/I2C传输,ACK/NACK阶段

4.1.2.5.2 写数据传输,奇偶校验位

4.1.2.5.3 I3C Read Transfer, Transition Bit

4.1.2.5.4 动态地址分配,分配地址第一位

4.1.3 总线条件

4.1.3.1 Bus Free Condition

4.1.3.2 Bus Available Condition

4.1.3.3 Bus Idle Condition

4.1.3.4 Activity States

4.1.4 总线初始化和动态地址分配

4.1.4.1 设备动态地址分配请求

4.1.4.1.1 唯一的身份标识

4.1.4.1.2 具有动态地址分配的总线初始化序列

4.1.4.3 临时ID冲突与检测

4.1.5 热插拔连接机制

4.1.6 带内中断

4.1.6.1 优先级

4.1.6.2 I3C从设备中断请求

4.1.7 第二主机功能

4.1.8 时序控制

4.1.9 通用命令代码(CCC)

4.1.9.1 通用命令代码格式

4.1.9.2 广播命令和直接命令的比较

4.1.9.2.1 CCC命令结束

4.1.9.2.2直接CCC命令的帧模型

4.1.9.2.3 Direct GET CCC命令的重试模式

4.1.9.3 CCC命令定义

4.1.9.3.1启用/禁用从器件事件命令(ENEC/DISEC)

4.1.9.3.2 输入活动状态0-3(ENTAS0-ENTAS3)

4.1.9.3.3重置动态地址分配(RSTDAA)

4.1.9.3.4 enter dynamic address assignment(ENTDAA)

4.1.9.3.5 Set/Get Max Write Length(SETMWL)

4.1.9.3.6 Set/Get Max Read Length(SETMRL)

4.1.9.3.7 Define List of Slaves(DEFSLVS)

4.1.9.3.8 Enter Test Mode(ENTTM)

4.1.9.3.9 Enter HDR Mode 0-7(ENTHDR0-ENTHDR7)

4.1.9.3.10 Set Dynamic Address from Staic Address(SETDASA)

4.1.9.3.11 Set New Dynamic Address (SETNWDA)

4.1.9.3.12 Get Provisional ID(GETPID)

4.1.9.3.13 Get Bus Characteristics Regster(GETBCR)

4.1.9.3.14 Get Device Characteristics Regster(GETDCR)

4.1.9.3.15 Get Device Status (GETSTATUS)

4.1.10 SDR错误检测和恢复方法

4.1.10.1 Error Type S0

4.2 HDR Mode

4.2.1 HDR Exit Pattern and HDR Restart Pattern

4.2.1.1 HDR Exit Pattern

4.2.1.2 HDR Restart Pattern

4.2.1.3 HDR Exit Pattern Detector

4.2.2 HDR-DDR Mode

4.2.2.1 HDR-DDR 综述

4.2.2.2 HDR-DDR Command Code

4.2.2.3 HDR-DDR 总线转换

4.2.2.3.1 Command to Read Data from Slave

4.2.2.3.2 End of a Read Command Message

4.2.2.3.3 Master Termination of a Read Command Message

4.3 HDR-TSP and HDR-TSL

4.3.1 HDR三进制信令和编码协议

4.3.1.1 HDR三进制信令

4.3.1.1 HDR三进制编码协议

4.3.1 HDR三进制命令编码

4.3.2 HDR三进制总线转换

5、附录

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc